基于e1光纤的ptp网络授时系统

技术领域

1.本发明涉及一种授时方法,具体涉及一种基于e1光纤的ptp网络授时系统,属于通信和精密授时技术领域。

技术背景

2.随着智能数字电网、4g与5g高速通信网络、国防军工和工业控制等领域的高速发展,对高精度时间基准的要求也越来越高,而高精度时间基准是靠高精度时钟同步技术来获得的。在距离较远的大型系统与大型系统之间可以利用gps和北斗等卫星手段进行高精度授时同步,然而各大系统内部之间的小型系统由于成本、维护、环境因素等客观原因不能大规模应用卫星技术进行时钟同步,因此在小型系统中只能选用其他时钟同步方式如e1、irig-b码、ntp、ptp等。ntp以出现时间最早、成本最为低廉、实现难度最低等优点而应用最为广泛。但ntp授时精度仅能达到ms级别,且由于容易受到网络协议栈的抖动的影响而造成时钟同步的稳定度较差,在很多应用场景中难以满足需求。其次是irig-b码,其时钟同步精度可以达到us级别,可以满足大多数小型系统的时钟同步需求。但irig-b码也有其明显的缺点,比如需要进行专门布线使得后期维护和升级困难。近些年出现一种ptp时钟同步技术,即ieee1588时钟同步技术,使得时钟同步授时精度大幅提升和稳定性大幅提高。

3.在早期的军工产品中e1采用的是与irig-b码授时结合的方式并用贝伏线传输授时,当两台设备距离较远时,线上信号质量变差、线路延迟增大进而影响同步精度等问题。而随着对同步精度的要求越来越高,e1结合irig-b码授时技术已无法满足要求,这就需要对e1链路授时升级改造。

技术实现要素:

4.有鉴于此,本发明提供一种基于e1光纤的ptp网络授时系统,采用将e1与ptp网络授时结合的方式对外授时,以提高e1的授时精度。

5.所述基于e1光纤ptp网络授时系统,包括:arm处理器、fpga模块和e1调制解调芯片;

6.所述arm处理器用于ptp同步报文的解析和授时同步算法的实现;

7.所述fpga模块用于对ptp同步报文打时间戳和将网络接口数据转换成满足e1通信的串行接口数据;

8.所述e1调制解调芯片用于串行接口数据和hb3码之间的调制解调,实现数据光纤传输功能。具体为:所述e1调制解调芯片将所述fpga模块传输过来的串行接口数据调制成hb3码,然后连接光端机,实现光纤传输功能;此外,还将从光端机接收的hb3码解调成串行接口数据发送给fpga模块。

9.作为本发明的一种优选方式,当该网络授时系统作为主时钟时,所述fpga模块只对接收到的sync报文和delay_req报文打时间戳,其他报文均透传;具体为:

10.当所述fpga模块从arm处理器发送的报文中检测到sync报文时,记录发出sync报

文的t1时间戳信息,然后将包括t1时间戳信息的sync报文发送给从时钟端;同时通知所述arm处理器读取sync报文的t1时间戳信息,所述arm处理器获取t1时间后将其放入follow_up报文中通过所述fpga模块发送给从时钟端;当所述fpga模块接收从从时钟端发送的报文中检测到delay_req报文时,记录报文到来时刻t4时刻的时间戳信息,然后将t4时间戳信息填入delay_req报文中发送给arm处理器,所述arm处理器从接收的delay_req报文中提取t4时间戳信息,然后放入delay_resp报文中通过fpga模块发送给从时钟端;

11.当该网络授时系统作为从时钟时,所述fpga模块只对接收的sync和发出的 delay_req报文打时间戳,其他报文均透传;具体为:

12.当所述fpga模块从接收到的报文中检测到sync报文时,记录sync报文到来时刻的 t2时间戳信息,然后将t2时间戳信息填入sync报文中发送给所述arm处理器,所述arm 处理器从接收的sync报文中提取t2时间戳信息用于授时同步计算;所述fpga模块从 arm处理器发送的报文中检测delay_req报文时,记录发出delay_req报文的t3时间戳信息,然后通知arm处理器读取delay_req报文的t3时间戳信息用于计算。

13.作为本发明的一种优选方式,所述fpga模块还具备防错机制:即所述fpga模块在无网络报文传输时一直发送防错字节至e1调制解调芯片,使e1调制解调芯片一直处在非空闲状态;所述防错字节设定格式的字节。

14.作为本发明的一种优选方式,所述fpga模块在无网络报文传输时一直发送0x7e至 e1调制解调芯片。

15.作为本发明的一种优选方式,所述fpga模块还具备加密机制:所述fpga模块将接收到的网络报文中的防错字节替换为设定格式的字节,令为加密字节,由此实现报文的加密;然后转换成满足e1通信的串行接口数据发送至e1调制解调芯片;

16.当所述fpga模块接收到的e1调制解调芯片发送的串行接口数据后,并将其组成字节报文;当报文出现非防错字节时开始接收报文,同时将接收的报文中的加密字节分别对应替换为防错字节,实现报文的解密。

17.作为本发明的一种优选方式,所述fpga模块在同时收到ptp同步报文和普通以太网报文时,优先传输ptp同步报文。

18.作为本发明的一种优选方式,所述fpga模块在接收到报文时,首先进行报文类型判断,然后将ptp同步报文和普通以太网报分开存储。

19.有益效果

20.(1)采用本发明的基于e1光纤的ptp网络授时的系统,能够实现当线路变长时不影响同步精度的同时提高同步精度。

21.(2)在arm处理器和e1调制解调芯片之间设置fpga模块,fpga模块在最接近端口的位置对ptp同步报文打时间戳,保证了授时精度。

附图说明

[0022][0023]

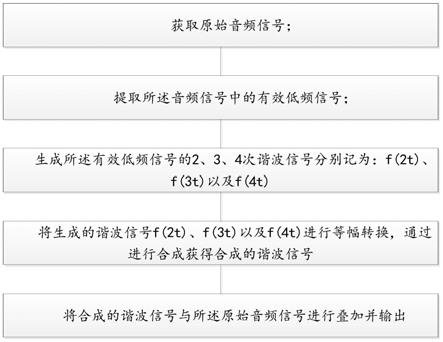

图1为该系统分别作为主、从时钟时ptp报文时间戳示意图;

[0024]

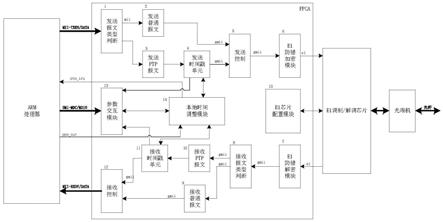

图2为本发明的功能框图。

具体实施方式

[0025]

下面结合附图和实施例,对本发明作进一步的详细说明。

[0026]

本实施例提供一种基于e1光纤的ptp网络授时系统,将e1与ptp网络授时结合对外授时,以提高e1的授时精度。

[0027]

如图1所示,基于e1光纤ptp网络授时系统采用arm处理器 fpga模块 e1芯片的框架结构实现网络授时功能,即该网络授时系统包括:arm处理器、fpga模块和e1调制解调芯片;其中arm处理器负责ptp报文的解析和授时同步算法的实现,fpga模块实现对ptp网络授时报文打时间戳的功能和将网络mii接口转换成满足e1通信的串行接口功能;e1调制解调芯片将fpga传输过来的报文调制成hb3码,然后连接光端机,实现光纤传输功能。该网络授时系统即可以作为主时钟也可以为作为从时钟。

[0028]

具体的:

[0029]

arm处理器使用现有成熟的ptp网络授时技术,实现ptp报文的解析和授时同步算法; arm处理器周期性的向fpga模块发送网络报文。该系统为主时钟模式时,arm处理器周期性向fpga模块发送sync和follow_up报文;该系统为从模式时钟时,当arm处理器接收到主时钟端发送的sync和follow_up报文后向fpga模块发送delay_req报文。

[0030]

fpga模块主要实现对ptp报文授时时间戳的处理和接口协议转换功能,其具有15个子模块,分别为:

[0031]

发送报文类型判断模块:用于判断arm处理器发出的报文类型(包括ptp同步报文和普通以太网报文,然后将ptp同步报文发送给发送ptp报文存储模块,将普通以太网报发送给发送普通报文存储模块,以实现ptp同步报文与普通以太网报文的分开存储。

[0032]

发送普通报文存储模块:用于存储普通的以太网报文,并发送给发送控制模块。

[0033]

发送ptp报文存储模块:用于存储ptp同步报文,并发送给时间戳单元。

[0034]

发送时间戳单元:用于对接收到的ptp同步报文打时间戳;如图1所示,当该网络授时系统作为主时钟时,需要打时间戳的ptp同步报文为sync报文;当该网络授时系统为从时钟时,需要打时间戳的ptp同步报文为delay_req报文;然后将打时间戳后的ptp 同步报文发送给控制模块。

[0035]

发送控制模块:用于将ptp报文和普通以太网报文传输给e1防错加密模块;同时对 ptp报文和普通以太网报文的发送优先级进行控制:当同时收到ptp报文和普通以太网报文时,优先传输ptp报文。

[0036]

e1防错加密模块:用于将网络报文(包括ptp同步报文和普通以太网报文)中的0x7e 和0x7d分别替换为0x7d5e和0x7d5d(也可以替换其他字节),然后按照符合e1传输的串行数据发送至e1调制解调芯片。同时该模块在无网络报文传输时一直发送0x7e至e1 调制解调芯片,使e1调制解调芯片一直处在非空闲状态,在一定程度上避免传输网络报文时出现信号跳变,具有一定的防错机制。

[0037]

e1防错解密模块:用于接收串行e1数据,并将其组成字节报文。当接收报文出现非 0x7e时开始接收报文,同时将接收的报文中的0x7d5e和0x7d5d分别替换为0x7e和0x7d,然后将解密后的报文转换成gmii接口发送至接收报文类型判断模块。

[0038]

接收报文类型判断模块:用于判断当前接收的报文是普通以太网报文还是ptp同步报文,然后将ptp同步报文发送给发送接收ptp报文模块,将普通以太网报发送给接收普

通报文模块。

[0039]

接收普通报文模块:用于存储接收到的普通网络报文。

[0040]

接收ptp报文模块:用于存储接收到的ptp同步报文。

[0041]

接收时间戳单元:用于对接收的ptp同步报文打时间戳,当该网络授时系统为主时钟时,需要打时间戳的报文有delay_req报文;当该网络授时系统为从时钟时,需要打时间戳的报文为sync报文。

[0042]

接收控制模块:用于将接收到的ptp报文和普通以太网报文传输给arm处理器;同时对ptp报文和普通以太网报文的发送优先级进行控制:当同时收到ptp报文和普通以太网报文时,优先传输ptp报文。

[0043]

参数交互模块:用于实现arm处理器通过mdc/mdio接口与fpga之间进行参数传输的功能,交互的参数包括:与本地时间调整模块交互的本地时间调整值、pps上升沿时间戳值、中断状态寄存器、ptp主从模式;与发送时间戳单元交互的sync报文t1时间戳、 delay_req报文t3时间戳。

[0044]

本地时间调整模块:fpga的本地时间调整模块工作在125m时钟域,上电后本地时间从0开始,以8ns间隔累计计数。检测到arm处理器发出的pps_out上升沿后锁定本地时间,并存入pps上升沿时间戳值寄存器,同时触发ptp_riq信号通知arm处理器使用 smi管理接口读取pps上升沿时间戳值,arm处理器获取pps上升沿时间戳值后与本地时间对比计算出相对时间,然后通过本地时间调整值寄存器告知fpga,fpga在接收到本地时间调整值后需立刻更新本地时间。

[0045]

e1芯片配置模块:用于配置e1调制解调芯片的工作模式,使其工作在单极性io、去抖动模式,在2.048mhz时钟下实现hdb3编解码和时钟恢复功能。

[0046]

e1调制解调芯片工作在2.048mhz时钟下,主要用于实现hdb3编解码和时钟恢复功能。

[0047]

报文时间戳工作过程如图1所示。在该系统作为主时钟时,fpga的时间戳单元只对 arm处理器发出的sync报文和接收的delay_req报文处理,其他报文均透传。具体为:发送时间戳单元从arm处理器发送的报文中检测到sync报文时,记录发出sync报文的 t1时间戳信息,然后将包括t1时间戳信息的sync报文发送给从时钟端;同时触发ptp_irq 信号通知arm处理器使用smi管理口读取sync报文的t1时间戳信息,arm处理器获取t1时间后将其放入follow_up报文中通过fpga模块发送给从时钟端。接收时间戳单元接收从时钟端发送的报文,将其从接到的报文中检测到delay_req报文时,记录报文到来时刻t4时刻的时间戳信息,然后将t4时间戳信息填入delay_req报文中发送给arm处理器,arm处理器从接收的delay_req报文中提取t4时间戳信息,然后放入delay_resp 报文中通过fpga模块发送给从时钟端。

[0048]

在该系统作为从时钟时,时间戳单元只对接收的sync和发出的delay_req报文处理,其他报文均透传。当接收时间戳单元从接收到的报文中检测到sync报文时,记录sync 报文到来时刻的t2时间戳信息,然后将t2时间戳信息填入sync报文中发送给arm处理器,arm处理器从接收的sync报文中提取t2时间戳信息用于授时同步计算。发送时间戳单元检测到arm处理器发送的delay_req报文时,记录发出delay_req报文的t3时间戳信息,然后触发ptp_irq信号,通知arm处理器使用smi管理口读取delay_req报文的 t3时间戳信息用于

计算。

[0049]

综上所述,以上仅为本发明的较佳实施例而已,并非用于限定本发明的保护范围。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。