1.本公开涉及集成电路操作和显式地调度不同集成电路硬件块的独立操作。

背景技术:

2.处理器和微控制器芯片通常由软件程序控制。这些程序包括在重复循环中依次执行的操作的列表。一些软件子例程响应于输入值的变化或者外部或内部中断信号的触发而被发起。软件程序和子例程一般由路由数据并控制芯片上的其它功能单元的中央控制电路执行以执行编程操作的部分。

技术实现要素:

3.总体地,在一些方面,本公开的主题可以在方法中实施,该方法包括如下动作:获得针对集成电路器件的第一硬件块的第一调度,其中该第一调度标识要由第一硬件块执行的第一操作集合。所述动作包括:获得针对集成电路器件的第二硬件块的第二调度,其中该第二调度标识要由第二硬件块执行的第二操作集合,并且其中,第二调度的操作与第一调度的操作相协调,使得第一调度触发第一硬件块在计数器的第一预调度值处向第二块发送数据,并且第二调度触发第二硬件块在第一预调度值之后的计数器的第二预调度值处在输入处接受数据。动作包括:由第一硬件块根据第一调度执行第一操作集合,以及由第二硬件块根据第二调度执行第二操作集合。本方面的其他实现方式包括对应的系统、装置和计算机程序,被配置为执行编码在计算机存储设备上的方法的动作。这些或其它实现方式可以各自可选地包括以下特征中的一个或多个。

4.在一些实现方式中,第一调度和第二调度各自包括由集成电路器件执行的程序的一部分。

5.在一些实现方式中,第一操作集合和第二操作集合各自包括机器学习程序的相应部分。

6.在一些实现方式中,第一操作集合中的每个操作在预定数量的时钟周期中执行。

7.在一些实现方式中,协调第一调度和第二调度的操作以允许第一硬件块和第二硬件块之间的数据交换独立于流控制信号。

8.在一些实现方式中,动作包括:由第一硬件块在执行包括在第一调度的一部分中的操作之前,解压缩第一调度的所述一部分。

9.在一些实现方式中,对于第一操作集合中的每个操作,第一调度包括调度的计数器值以及指示要由第一硬件块在调度的计数器值处执行的特定操作的数据。

10.在一些实现方式中,由第一硬件块根据第一调度执行第一操作集合包括以下的动作:从计数器接收第一计数器值,该第一计数器值等于第一操作集合中的第一操作的第一调度计数器值;响应于接收第一计数器值,使第一硬件块的一个或多个计算单元的第一集合执行第一操作;从计数器接收第二计数器值,该第二计数器值等于第一操作集合中的第二操作的第二调度计数器值;以及响应于接收第二计数器值,使第一硬件块的一个或多个

计算单元的第二集合执行第二操作。

11.在一些实现方式中,第一硬件块和第二硬件块是包括被配置为执行神经网络操作的专用电路的硬件瓦片。

12.另一总体方面可以在集成电路器件中实施,该集成电路器件包括:计数器、可通信地耦合到计数器的第一硬件块、以及可通信地耦合到计数器并耦合到第一硬件块的第二硬件块。第一硬件块被配置为根据包括第一操作集合的第一调度进行操作,第一操作集合中的每个操作被调度为由第一硬件块在计数器的第一相应值处执行。第二硬件块被配置为根据包括第二操作集合的第二调度进行操作,第二操作集合中的每个操作被调度为由第二硬件块在计数器的第二相应值处执行。第二调度的操作与第一调度的操作相协调,使得第一调度触发第一硬件块在计数器的第一预调度值处向第二硬件块发送数据,并且第二调度触发第二硬件块在第一预调度值之后的计数器的第二预调度值处在输入处接受数据。该实现方式和其它实现方式可以各自可选地包括以下特征中的一个或多个。

13.在一些实现方式中,第一操作集合和第二操作集合各自包括机器学习程序的相应部分。

14.在一些实现方式中,第一操作集合中的每个操作在预定数量的时钟周期中执行。

15.在一些实现方式中,协调第一调度和第二调度的操作以允许第一硬件块和第二硬件块之间的数据交换独立于流控制信号。

16.在一些实现方式中,集成电路器件包括多个其它硬件块,其中,第一调度的操作与其它硬件块的相应操作调度相协调,以允许在第一硬件块和其它硬件块中的一个或多个之间独立于数据流控制信号而交换数据。

17.在一些实现方式中,第一硬件块包括:被配置为存储第一调度的本地存储器,以及被耦合到本地存储器并且被配置为执行第一调度的第一操作集合的控制电路。在一些实现方式中,控制电路被配置为在执行包括在第一调度的一部分中的操作之前解压缩第一调度的所述一部分。

18.在一些实现方式中,集成电路器件是专用集成电路。

19.在一些实现方式中,第一硬件块和第二硬件块是包括被配置为执行神经网络操作的专用电路的硬件瓦片。在一些实现方式中,第一硬件块包括单元的计算阵列以及被耦合到单元的计算阵列的本地存储器。

20.在一些实现方式中,第一调度和第二调度各自包括由集成电路器件执行的程序的一部分。

21.第三总体方面可以在集成电路器件中实施,该集成电路器件包括第一硬件块、第二硬件块和编译器。第一硬件块被配置为根据第一调度进行操作,第一调度包括第一操作集合,第一操作集合中的每个操作被调度为由第一硬件块在相应的预调度时间处执行。第一硬件块包括计算阵列,计算阵列包括多个单元,多个单元中的每个单元被配置为执行乘法累加运算。第二硬件块可通信地耦合到第一硬件块。第二硬件块被配置为根据包括第二操作集合的第二调度进行操作,第二操作集合中的每个操作被调度为由第二硬件块在相应的预调度时间处执行。编译器被配置为生成第一调度和第二调度,其中第一调度的第一操作集合与第二调度的第二操作集合相协调以准许第一硬件块和第二硬件块之间的数据传送,并且其中第一调度和第二调度中的每个分别表示要由集成电路器件作为整体执行的神

经网络程序的一部分。

22.在一些实现方式中,第一操作集合和第二操作集合包括机器学习程序的相应部分。

23.在一些实现方式中,第一操作集合中的每个操作在预定数量的时钟周期中执行。

24.一些实现方式包括至少一个其它硬件块,其中第一调度的操作与至少一个其它硬件块的相应操作调度相协调,以准许第一硬件块和至少一个其它硬件块之间的数据传送。在一些实现方式中,至少一个其它硬件块包括被配置为执行标量运算的电路。在一些实现方式中,至少一个其它硬件块包括被配置为执行矢量运算的电路。

25.在一些实现方式中,第一硬件块的计算阵列包括被配置为执行矩阵运算的电路,并且第二硬件块包括被配置为执行存储器访问操作的电路。在一些实现方式中,第二硬件块存储操作的第一调度。在一些实现方式中,第一硬件块被配置为将计算阵列的输出传送到第二硬件块。

26.在一些实现方式中,第一硬件块和第二硬件块是包括被配置为执行神经网络操作的专用电路的硬件瓦片。

27.第四总体方面可以在方法中实施,该方法包括如下动作:由集成电路器件的编译器生成第一调度,第一调度包括第一操作集合,第一操作集合中的每个操作被调度为由第一硬件块在相应的预调度时间处执行。动作包括:由编译器生成第二调度,第二调度包括第二操作集合,第二操作集合中的每个操作被调度为由第二硬件块在相应的预调度时间处执行。动作包括:由第一硬件块根据第一调度执行第一操作集合,其中第一硬件块包括计算阵列,计算阵列包括多个单元,多个单元中的每个单元被配置为执行乘法累加运算。动作包括:由集成电路器件的第二硬件块根据第二调度执行第二操作集合,其中第一调度和第二调度中的每个分别表示要由集成电路器件作为整体执行的神经网络程序的一部分。

28.在一些实现方式中,第一操作集合和第二操作集合包括机器学习程序的相应部分。

29.在一些实现方式中,第一操作集合中的每个操作在预定数量的时钟周期中执行。

30.在一些实现方式中,集成电路包括至少一个其它硬件块,其中第一调度的操作与至少一个其它硬件块的相应操作调度相协调,以准许在第一硬件块和至少一个其它硬件块之间的数据传送。在一些实现方式中,至少一个其它硬件块包括被配置为执行标量运算的电路。在一些实现方式中,至少一个其它硬件块包括被配置为执行矢量运算的电路。

31.在一些实现方式中,第一硬件块的计算阵列包括被配置为执行矩阵运算的电路,并且第二硬件块包括被配置为执行存储器访问操作的电路。

32.在一些实现方式中,动作包括:由第二硬件块存储操作的第一调度。

33.在一些实现方式中,动作包括:由第一硬件块将第一硬件块的计算阵列的输出传送到第二硬件块。

34.在一些实现方式中,第一硬件块和第二硬件块是包括被配置为执行神经网络操作的专用电路的硬件瓦片。

35.各种实现方式包括以下优点中的一个或多个。例如,在一些实现方式中,显式调度的芯片操作可以提高以其写入芯片控制逻辑的效率和准确性。例如,显式调度的芯片操作使芯片操作对于计算密集型操作(诸如机器学习操作)更具确定性。当操作更具确定性时,

可以以更精确的方式执行硬件控制测试和调试。

36.作为另一示例,确定性调度的使用可以降低硬件的复杂性。例如,由于每个操作的定时通过调度事先已知,因此可以在软件中一次精确且全局地协调操作。全局知识在硬件中是不可行的,所以调度的质量是在软件中完成的;减少在硬件中传导调度操作的需要使硬件更简单。

37.确定性调度还可以改进调试过程。例如,确定性调度的使用意味着可以在知道实际硬件将以相同方式执行的模拟器上调试硬件的编程。

38.本发明的一个或多个实施例的细节在附图和以下描述中阐述。其它特征和优点将从描述、附图和权利要求中显而易见。

附图说明

39.图1是示出被配置为根据调度的操作进行操作的示例集成电路器件的示意图。

40.图2a是示出图1的集成电路器件的硬件块的操作调度之间的示例协调操作的时序图,而图2b描绘了示出在操作调度的执行期间图1的集成电路器件内的示例数据流的一系列图。

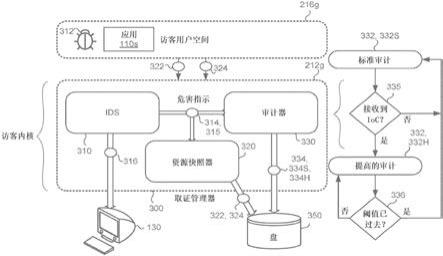

41.图3是示出可以被配置为根据调度的操作进行操作的专用逻辑电路的示例的示意图。

42.图4是示出用于在图3的asic芯片中使用的瓦片的示例的示意图。

43.图5a、图6a、图7a、图8a、图9、图10a和图11a是示出在由asic实现的示例性过程中的不同时间处通过asic的数据流的概况的示意图。

44.图5b、图6b、图7b、图8b、图10b和图11b是分别示出在与图5a、图6a、图7a、图8a、图10a和图11a相关联的时间处在asic的单个瓦片内的数据流的细节的示意图。

具体实施方式

45.一般而言,本公开涉及由半导体器件根据时间调度的操作执行操作。更具体地,本公开涉及具有独立硬件块的半导体芯片,这些独立硬件块根据个性化操作调度进行操作以执行由半导体芯片作为整体执行的协调程序。换言之,独立硬件块根据共同时钟(例如,计数器)在调度时间处执行它们相应的操作,而不是例如响应于控制信号或根据过程指令的未调度顺序列表执行操作。例如,芯片包括数个硬件块。每个硬件块表示复制逻辑的相关集合,诸如芯片上的电路(例如,逻辑电路)的子集,其被设计为独立于由其它硬件块执行的任务而执行任务的特定集合。硬件块可以被配置为执行操作,该操作包括但不限于矩阵运算、矢量运算、标量运算、逻辑运算、存储器访问操作、外部通信操作或者其组合。

46.每个硬件块执行特定于该硬件块的操作的独立调度。每个硬件块的独立调度一起表示由芯片作为整体执行的完整的程序(例如,神经网络操作)。每个调度包括一系列操作,这一系列操作被调度为由独立硬件块在特定计数器时间处执行。例如,硬件块可以各自基于芯片上共同时钟的当前计数值执行它们相应调度中的操作。

47.此外,调度被布置为协调各种硬件块之间的数据传送,而不需要流控制逻辑。例如,针对第一硬件块的第一调度的操作与针对第二硬件块的第二调度的操作相协调,使得第一硬件块向第二硬件块发送数据的第一调度中的操作被定时,以与需要第二个硬件块从

输入缓冲区中读取数据并对该数据进行操作的第二调度中的操作相对应。换言之,独立调度的操作被协调,使得硬件块之间的数据传送可以独立于传统的流控制逻辑来执行。也就是说,协调的调度本身用于排除通信错误,诸如内部总线上的数据冲突和/或数据缓冲区溢出。在一些实现方式中,硬件块操作的确定性协调和硬件块操作的预调度允许人们精确地知道某些操作将在何时在芯片上发生。确定性调度过程可能优于非确定性芯片操作,因为例如它可以提高调试操作能够被执行的容易性和效率。

48.在一些实现方式中,半导体芯片是被设计为执行机器学习操作的专用集成电路(asic)。asic包括,例如,为特定用途定制的集成电路(ic)。例如,asic可以被设计为执行机器学习模型的操作,包括例如作为深度神经网络的一部分识别图像中的对象、机器翻译、语音识别或其它机器学习算法。例如,当用作神经网络的加速器时,asic可以接收对神经网络的输入,并且计算该输入的神经网络推理。对神经网络层的数据输入,例如,对神经网络的输入或神经网络的另一层的输出,可以被称为激活输入。可以根据与神经网络的各层相关联的权重输入的相应集合来计算推理。例如,层中一些或所有可以接收激活输入的集合并根据该层的权重输入的集合来处理激活输入以生成输出。此外,用于计算神经网络推理而执行的计算操作的重复性质有助于显式调度的芯片操作。

49.图1是示出被配置为根据调度的操作进行操作的集成电路芯片10的简化示例的示意图。芯片10可以是通用集成电路或专用集成电路。例如,芯片10可以是asic、现场可编程门阵列(fpga)、图形处理单元(gpu)或任何其它合适的集成电路。芯片10包括多个硬件块12、计数器14和共享数据总线16。为了说明和讨论的目的,以简化的方式示出了芯片10,然而,在实现方式中,芯片10将包括附加组件,诸如通信接口、存储器和适合于芯片10的目的的其它电路。

50.硬件块12表示复制逻辑的相关集合,诸如芯片10上的电路(例如逻辑电路)的子集,其被设计为独立于由其它硬件块12执行的任务而执行任务的特定集合。此外,每个硬件块12可以表示不同类型的电路,例如,硬件块a可以表示被配置为在芯片10和芯片10外部的其它半导体组件之间传送数据的通信接口。硬件块b和硬件块c可以表示被设计为执行机器学习功能的专用芯片的“瓦片(tile)”(下面更详细地讨论)。例如,硬件块b和硬件块c可以表示被配置为执行矩阵运算的神经网络的计算节点。

51.计数器14根据芯片10上的共同时钟信号递增。计数器14可以是,例如,24位、32位或其它大小的同步计数器。计数器14向硬件块12输出芯片计数值,例如,“芯片时间(chip time)”,以用于同步每个独立硬件块12的显式调度的操作。在一些实现方式中,每个硬件块12具有独立计数器14,而不是用于芯片10的单个计数器14。独立计数器可以由芯片10上的共同时钟同步。此外,例如,独立计数器的计数值可以由芯片上的共同重置信号同步。

52.每个硬件块12根据其自己的个性化操作调度18进行操作。操作调度18各自表示要由芯片10作为整体执行的程序的一部分,并且每个操作调度18独立表示要由独立硬件块12执行的程序的部分。操作调度18包括要由硬件块在预定计数器值处执行的操作的集合。换言之,操作调度18可以被认为是列表定时器,其触发要由特定硬件块12在预调度的“芯片时间”处执行的特定操作。例如,每个调度18可以包括执行计数器值(例如,执行时间)的列表以及要在计数器值处执行的相关联操作。在一些示例中,操作调度18中的每个操作由调度计数器值和诸如操作代码的数据表示,该数据标识要由特定硬件块12在调度计数器值处执

行的操作。

53.每个调度18的操作与所有其它调度的操作协调,以避免诸如共享资源(例如,数据总线16)的双重预订(double booking)的错误。每个调度18的操作也被协调以准许硬件块12之间的数据传送独立于流控制逻辑(例如,诸如中断信号)。例如,两个硬件块12之间的数据传送被调度,使得接收硬件块12被调度以在计数器值处从数据总线或输入缓冲区中读取数据,该计数器值1)基于发送硬件块10的调度的发送计数值确保在读取时间处存在正确数据,以及2)通过调度接收硬件块12以在缓冲区溢出之前读取数据(例如,在附加数据被调度以被发送到接收硬件块12之前调度读取)来防止输入缓冲区溢出。

54.个性化操作调度18对于计算密集、高度重复或两者兼有的应用(诸如神经网络和图形处理计算)可能特别有用。例如,针对芯片10上的独立硬件块12使用显式定义的调度可以有助于其中调度的操作各自在预定义数量的时钟周期中执行的确定性操作。

55.芯片10的硬件块12的操作调度18可以由程序编译器生成。例如,编译器可以处理芯片的整体程序,并标识将在芯片10上在每个时间增量处发生的硬件功能,以便执行程序。编译器可以将功能解析到芯片10上的每个硬件块12的操作调度18中。操作调度18然后被加载到芯片10上并且可以存储在共同芯片10存储器中或者操作调度10可以被分布到与相应硬件块12相关联的本地存储器。

56.更详细地,每个硬件块12可以包括控制电路20、本地存储器22和一个或多个计算单元24。在实现方式中,操作调度18可以存储在硬件块12的本地存储器22中。操作单元24表示被配置为执行特定计算(例如,加法、减法、乘法、逻辑运算等)的电路。控制电路20可以被配置为读取和执行操作调度18的操作。例如,控制电路20可以包括控制元件,诸如在存储器22、输入缓冲区或总线16和适当的计算单元24之间路由数据以执行调度的操作的复用器和触发器。如上所述,操作调度18可以用作触发控制电路20以开始在特定计数器值处执行特定功能的一系列定时器。因此,操作调度18可以触发控制电路20的控制元件以将硬件块12内的数据路由到适当的计算单元24,以便在调度的时间处执行调度的操作。例如,参照“调度c”,在计数器时间030处,操作调度18可以触发控制电路20以将数据从存储器22路由到适当的计算单元24以执行操作3(“op.3”),例如,求和运算。在计数器时间043处,操作调度18将触发控制电路以将求和运算的输出数据路由到总线16,以将输出数据发送到另一硬件块12。

57.在一些实现方式中,操作调度18被压缩以节省存储器资源。在这样的实现方式中,硬件块12或芯片上的其它电路可以在执行操作调度18的一部分之前,对操作调度18的该一部分进行解压缩。例如,操作调度18可以被压缩以利用调度中的周期性。例如,特定调度可以包括在六个周期时段的不同阶段调度的操作的集合。然后,调度可以被实现为周期性计数器和延迟的组合(例如,针对阶段)。

58.图2a是示出针对图1的集成电路芯片10的硬件块12的操作调度之间的示例协调操作的时序图。具体地,时序图示出硬件块a、b和c的操作调度如何被协调,以使得数据传送操作在发送和接收硬件块之间同步。例如,参照计数器时间001-015,硬件块b被调度以在从硬件块a发送数据时起的预定数量的时钟周期内接收来自硬件块a的数据。具体地,在计数器时间001处,硬件块a根据硬件块a的操作调度开始向硬件块b发送数据30(在图2b中)。在计数器时间001和006之间,硬件块a准备并开始发送数据30。在时间006处,数据开始到达硬件

块b,其为预调度计数器时间(在硬件块b的操作调度上,当硬件块b开始访问数据时的时间)。从时间006到时间015,数据从硬件块a传播到硬件块b,以及硬件块b。此外,可以协调硬件块a和硬件块b的操作调度,使得由硬件块b在计数器时间001-0015期间接收到的数据是硬件块b将在硬件块b被预调度以在计数器时间016-062期间执行的后续操作(例如,op.1到op.3)中的一个或多个期间使用的数据,

59.在一些实现方式中,硬件块a和硬件块b之间的数据传输路径可以包括硬件块a发送数据的时间和硬件块b接收该数据的时间之间的一些不可忽略的时延变化量(例如,数据传输时间的变化)。为了考虑到这样的延迟,当硬件块a开始传输和当硬件块b开始访问数据之间的时间的一部分可以包括预定延迟时段,以确保数据在硬件块b开始访问数据时或之前已经到达硬件块b。硬件块b(以及硬件块中任何或所有硬件块)可以包括输入缓冲区以在数据被接收时收集数据,使得如果数据提前一个或多个计数器周期到达硬件块b(例如,由于时延变化),数据不会丢失而是在硬件块b开始其预调度的接收操作以从缓冲区访问数据时立即可用。

60.在硬件块b和硬件块c之间,以及在硬件块c和硬件块a之间,以类似方式执行预调度的数据传输操作。例如,参照计数器时间063-082,硬件块c被调度以在从硬件块b发送数据时起的预定数量的时钟周期内接收来自硬件块b的数据。同样,参照计数器时间131-148,硬件块a被调度以在从硬件块c发送数据时起的预定数量的时钟周期内接收来自硬件块c的数据。

61.图2b描绘了示出在操作调度18的执行期间图1的集成电路芯片10内的示例数据流的一系列图。该一系列操作可以表示神经网络的激活数据30的简化流。激活数据30由通信接口(例如,硬件块a)接收。通信接口(硬件块a)在计数器时间001-015处将激活数据30传送到神经网络的输入层(例如,硬件块b)。在计数器时间015和062之间,输入层(硬件块b)对数据执行三个调度的操作。然后,从计数器时间063开始,输入层(硬件块b)将其输出数据32发送到输出层(例如,硬件块c)。输出层(硬件块c)在计数器时间83和130之间对来自输入层(硬件块b)的输出数据32执行三个调度的操作。最后,从计数器时间131开始,输出层(硬件块c)将其输出34发送回通信接口(硬件块a),例如,用于被发送到另一芯片或其它外部资源。此外,图2b中的一系列图示出可以如何使用三个硬件块12的协调操作调度18以管理对共享资源(诸如数据总线16)的访问。使用数据总线16的每个数据传送被预调度达已知的可用时间。此外,由于数据块的操作是预调度和确定性的,涉及共享资源的错误应被最小化。

62.尽管已经参照控制单个芯片的操作描述了操作调度的使用,类似的过程可以应用于独立芯片的系统。也就是说,可以以类似方式生成独立操作调度,以控制同步芯片的集合的同时操作。例如,对于具有同步计数器的芯片的系统,每个芯片可以根据操作的显式调度来执行操作。

63.图3是示出可以被配置为根据调度的操作进行操作的专用逻辑电路的示例(特别地,asic 100)的示意图。asic 100包括可以被配置为根据独立操作调度执行asic 100的整体操作的各种不同类型的硬件块。可以根据独立操作调度进行操作的示例硬件块包括瓦片102、矢量处理单元104和通信接口108。

64.更具体地,asic 100包括多个瓦片102,其中瓦片102中的一个或多个包括被配置为执行操作(诸如,例如,乘法和加法运算)的专用电路。特别地,每个瓦片102可以包括单元

(cell)的计算阵列(例如,类似于图1的计算单元24),其中每个单元被配置为执行数学运算(参见,例如,图4所示且本文所描述的示例性瓦片200)。在一些实现方式中,瓦片102以网格图案布置,其中瓦片102沿着第一维度101(例如,行)且沿着第二维度103(例如,列)布置。例如,在图3所示的示例中,瓦片102被划分成四个不同的分区(110a、110b、110c、110d),每个分区包含288个瓦片,这些瓦片被布置在纵向为18个瓦片及横向为16个瓦片的网格中。在一些实现方式中,图3所示的asic 100可以被理解为包括被细分/布置成分开的瓦片的单元的单个脉动阵列(systolic array),其中每个瓦片包括单元的子集/子阵列、本地存储器和总线(参见,例如,图4)。

65.asic 100还可以包括矢量处理单元104。矢量处理单元104包括被配置为从瓦片102接收输出并且基于从瓦片102接收到的输出计算矢量计算输出值的电路。例如,在一些实现方式中,矢量处理单元104包括被配置为对从瓦片102接收到的输出执行累加运算的电路(例如,乘法电路、加法器电路、移位器和/或存储器)。可替代地或附加地,矢量处理单元104包括被配置为将非线性函数应用于瓦片102的输出的电路。可替代地或附加地,矢量处理单元104生成归一化值(normalized value)、池化值(pooled value)或两者。矢量处理单元的矢量计算输出可以存储在一个或多个瓦片中。例如,矢量计算输出可以存储在与瓦片102唯一相关联的存储器中。可替代地或附加地,矢量处理单元104的矢量计算输出可以被传送到asic 100外部的电路,例如,作为计算的输出。此外,瓦片102和矢量处理单元104的独立操作调度的操作协调瓦片输出到矢量处理单元104的传送。

66.在一些实现方式中,矢量处理单元104被分段,使得每个分段包括被配置为从瓦片102的对应集群中接收输出并且基于接收到的输出计算矢量计算输出的电路。例如,在图3所示的示例中,矢量处理单元104包括沿着第一维度101生成的两行,行中的每个包括布置成32列的32个分段106。如本文所述的那样,每个分段106包括被配置为基于来自瓦片102的对应列的输出(例如,累加的和)执行矢量计算的电路(例如,乘法电路、加法器电路、移位器和/或存储器)。矢量处理单元104可以定位在如图3所示的瓦片102的网格的中间。矢量处理单元104的其它定位布置也是可能的。

67.asic 100还包括通信接口108(例如,接口1010a、1010b)。通信接口108包括一组或多组串行器/解串器(serdes)接口和通用输入/输出(gpio)接口。serdes接口被配置为接收指令(例如,针对asic 100的独立硬件块的操作调度)和/或对于asic 100的输入数据,以及将来自asic 100的数据输出到外部电路。例如,serdes接口可以被配置为以32gbps、56gbps或任何合适的数据速率在通信接口108内包括的一组serdes接口上发送和接收数据(例如,操作调度和/或输入/输出数据)。例如,asic 100可以在其开启时运行引导程序(boot program)。gpio接口可以用于将操作调度加载到asic 100上以用于执行特定类型的机器学习模型。

68.asic 100可以与不像asic那样根据特定操作调度进行操作的外部电路或系统通信。例如,外部系统的操作可以与asic 100的操作不完全同步。可替代地或附加地,与外部电路和系统的数据通信可能会受到不规律延迟的影响。因此,输入数据可能以不规律的间隔到达通信接口108。通过并入以下特征中的任何一个或多个,实现方式可以解决这种潜在的不规律通信:在asic100中包括的先入先出(fifo)缓冲区、基于有界数据到达延迟实现通信接口108的调度操作、实现基于有条件地替代操作、实现输入数据填充、或者它们的任何

组合。

69.通信接口108可以包括用于从外部电路/系统接收输入数据的fifo缓冲区。例如,fifo缓冲区可以足够大以临时存储足够的输入数据用于asic 100的指定数量的操作周期,例如,100个周期、500个周期、1000个周期或10000个周期。例如,如果asic 100的每个操作周期依赖于1kb的输入数据,那么500个周期的fifo缓冲区名义上将是500kb。

70.此外,通信接口108的操作调度可以基于asic 100正在或将要从其接收输入数据的预期外部系统或特定外部系统的有界到达延迟。例如,可以基于诸如外部系统的操作变化的附加信息估计外部系统的预期通信时延且然后进行划界。通信接口108可以被调度以在外部系统的最晚预期到达延迟处从fifo缓冲区访问输入数据。例如,通信接口108可以根据指令通信接口108以与外部系统的最晚预期到达延迟相对应的时间间隔从fifo缓冲区访问数据的操作调度进行操作。假设外部系统以规律或相对规律的时间间隔发送输入数据,则在外部系统的最晚预期到达延迟处检查fifo缓冲区将提供输入数据在asic 100的每个周期期间(例如,至少在正常操作期间)可用于处理的合理保证。

71.在一些实现方式中,通信接口108可以被调度以在外部系统的最晚预期到达延迟处检查fifo缓冲区以寻找输入数据,并且如果不存在数据,则执行替代调度的操作。例如,如果fifo缓冲区中不存在输入数据,则通信接口108可以触发asic 100的挂起模式(suspend mode)。通信接口108可以用信号通知其它硬件块(例如,瓦片102)以执行替代延迟调度。延迟调度可以包括指定延迟时段的一系列无操作(no-op)指令。每个硬件块的延迟时段可以不同(例如,包括不同数量的无操作指令),以便在挂起模式结束且正常操作恢复时恰当地协调硬件块之间的操作。在一些实现方式中,如果fifo缓冲区中的输入数据下降到阈值以下,则可以触发挂起模式。例如,阈值可以是fifo缓冲区容量的百分比,例如,5%、10%、20%等。

72.在一些实现方式中,如果缓冲区是空的或落入阈值以下,则可以填充fifo缓冲区中的数据。例如,默认数据值可以被添加到任何接收到的输入数据,以允许asic 100在fifo缓冲区中可用的输入数据不足时继续操作一个周期或数个周期。例如,如果asic 100在初始化时段(例如,在开始正常操作之前),默认数据可以包括空值。在初始化时段期间,可能存在空数据将不利地影响asic 100计算的输出值的低风险。

73.可替代地,如果在正常操作期间需要填充,则可以例如基于先前的asic输出或基于先前输入的内插来计算默认值。例如,通信接口108可以被配置为在缓冲区变空之前将来自fifo缓冲区的输入数据存储为填充数据,或者根据fifo缓冲区中的输入数据内插填充数据。作为另一示例,通信接口108可以被配置为,如果fifo缓冲区中的输入数据降至阈值以下,则用信号通知其它硬件块的子集以执行调度以提供默认填充值的替代操作。例如,通信接口108可以用信号通知包含asic输出数据的硬件块以将输出数据发送到通信接口108以用作填充数据。

74.asic 100进一步包括多个可控总线线路(参见,例如,图4),其被配置为在通信接口108、矢量处理单元104和多个瓦片102之间传递数据。可控总线线路包括,例如,沿着网格的第一维度101(例如,行)和网格的第二维度103(例如,列)两者延伸的布线。沿着第一维度101延伸的可控总线线路的第一子集可以被配置为在第一方向上(例如,向图3的右侧)传送数据。沿着第一维度101延伸的可控总线线路的第二子集可以被配置为在第二方向上(例

如,向图3的左侧)传送数据。沿着第二维度103延伸的可控总线线路的第一子集可以被配置为在第三方向上(例如,向图3的顶部)传送数据。沿着第二维度103延伸的可控总线线路的第二子集可以被配置为在第四方向上(例如,向图3的底部)传送数据。如上面所讨论的,不同硬件块的独立操作调度可以协调对共享资源(诸如可控总线线路)的访问,以防止asic 100内的通信错误。

75.每个可控总线线路包括多个传送器元件,诸如触发器,其被用于根据时钟信号沿着线路传递数据。在可控总线线路上传送数据可以包括,在每个时钟周期,将来自可控总线线路的第一传送器元件的数据移位到相邻的、可控总线线路的第二传送器元件。在一些实现方式中,数据在时钟周期的上升沿或下降沿在可控总线线路上传递。例如,在第一时钟周期存在于可控总线线路的第一传送器元件(例如,触发器)上的数据可以在第二时钟周期传送到可控总线线路的第二传送器元件(例如,触发器)。在一些实现方式中,传送器元件可以以距彼此的固定距离周期性地间隔开。例如,在一些情况下,每个可控总线线路包括多个传送器元件,其中每个传送器元件定位在对应的瓦片102内或在对应的瓦片102附近。

76.每个可控总线线路还包括多个复用器和/或解复用器。可控总线线路的复用器/解复用器被配置为在总线线路和asic芯片100的组件之间传送数据。例如,可控总线线路的复用器/解复用器可以被配置为向瓦片102传送数据和/或传送来自瓦片102的数据、向矢量处理单元104传送数据和/或传送来自矢量处理单元104的数据、或者向通信接口108传送数据和/或传送来自通信接口108的数据。在瓦片102、矢量处理单元104和通信接口之间传送数据可以由操作调度来协调。操作调度可以协调在每个计数器处哪个asic 100硬件块正在发送数据到可控或正在接收来自可控的数据。在任何给定的计数器时间处调度的操作可以确定,例如,什么数据从源(例如,瓦片102内的存储器或者矢量处理单元104)传送到可控总线线路,或者可替代地,什么数据从可控总线线路传送到汇(sink)(例如,瓦片102内的存储器或者矢量处理单元104)。

77.可控总线线路被配置为在本地级别上被控制,使得每个瓦片、矢量处理单元和/或通信接口包括其自己的控制元件的集合,用于操纵通过该瓦片、矢量处理单元和/或通信接口的可控总线线路。例如,每个瓦片、1d矢量处理单元和通信接口可以包括对应的一组传送器元件、复用器和/或解复用器,用于控制去往和来自该瓦片、1d矢量处理单元和通信接口的数据传送。因此,每个瓦片、1d矢量处理单元和通信接口的操作调度可以触发相应的硬件块以向其传送器元件提供适当的控制信号,以便根据调度的操作来路由数据。

78.为了最小化与asic芯片100的操作相关联的时延,瓦片102和矢量处理单元104可以被定位以减少数据在各种组件之间传输的距离。在特定实现方式中,瓦片102和通信接口108两者可以被分离成多个分区,其中瓦片分区和通信接口分区两者被布置成使得数据在瓦片和通信接口之间传输的最大距离减小。例如,在一些实现方式中,第一组瓦片102可以布置在通信接口108的第一侧上的第一分区中,并且第二组瓦片102可以布置在通信接口的第二侧上的第二分区中。作为结果,与其中瓦片102中的所有瓦片被布置在通信接口的一侧上的单个分区中的配置相比,从通信接口到最远瓦片的距离可以被减半。

79.可替代地,瓦片可以布置在不同数量的分区中,诸如四个分区。例如,在图3所示的示例中,asic 100的多个瓦片102被布置在多个分区110(110a、110b、110c、110d)中。每个分区110包括以网格图案布置的相似数量的瓦片102(例如,每个分区110可以包括布置成16行

和16列的256个瓦片)。通信接口108也被划分成多个分区:布置在瓦片102的分区110的任一侧上的第一通信接口1010a和第二通信接口1010b。第一通信接口1010a可以通过可控总线线路耦合到asic芯片100左侧上的两个瓦片分区110a、110c。第二通信接口1010b可以通过可控总线线路耦合到asic芯片100右侧上的两个瓦片分区110b、110d。作为结果,与其中只有单个通信接口可用的布置相比,向通信接口108和/或来自通信接口108的数据传输的最大距离(并且因此,与数据传播相关联的时延)可以减半。瓦片102和通信接口108的其它耦合布置也可能减少数据时延。瓦片102和通信接口108的耦合布置可以通过向可控总线线路的传送器元件和复用器提供控制信号来编程。

80.在一些实现方式中,一个或多个瓦片102被配置为发起关于asic 100内的其它瓦片(在本文中称为“控制瓦片”)和/或可控总线线路的读取和写入操作。asic 100内的剩余瓦片可以被配置为基于输入数据执行计算(例如,用于计算层推理)。在一些实现方式中,控制瓦片包括与asic 100内的其它瓦片相同的组件和配置。控制瓦片可以作为asic 100的一个或多个额外瓦片、一个或多个额外行或者一个或多个额外列被添加。例如,对于瓦片102的对称网格(其中每个瓦片102被配置为对输入数据执行计算),可以包括一个或多个附加行的控制瓦片以处理对于对输入数据执行计算的瓦片102的读取和写入操作。例如,每个分区110包括18行瓦片,其中最后两行的瓦片可以包括控制瓦片。在一些实现方式中,提供分开的控制瓦片增加了用于执行计算的其它瓦片中可用的存储器的量。提供分开的控制瓦片还可以帮助操作调度之间的数据传输操作的协调。例如,使用控制瓦片来控制关于asic 100内的其它瓦片和/或可控总线线路的读取和写入操作可以减少需要检查调度冲突的独立调度的数量。换言之,如果控制瓦片的操作调度被协调以避免“双重预订”在同一计数器时间处的特定可控总线线路的使用,则有合理的保证在可控总线线路上将不会发生通信错误。然而,如本文所述的专用于提供控制的分开的瓦片不是必需的,并且在一些情况下,不提供分开的控制瓦片。相反,每个瓦片可以在其本地存储器中存储用于发起对该瓦片的读取和写入操作的指令。

81.此外,虽然图3中示出的每个分区110包括被布置成18行乘16列的瓦片,瓦片102的数量和它们在分区中的布置可以不同。例如,在一些情况下,分区110可以包括相等数量的行和列。

82.此外,尽管如图3所示被划分成四个分区,但是瓦片102也可以被划分成其它不同的分组。例如,在一些实现方式中,瓦片102被分组成两个不同的分区,诸如在矢量处理单元104上方的第一分区(例如,更靠近图3中示出的页面的顶部)和在矢量处理单元104下方的第二分区(例如,更靠近图3中示出的页面的底部)。在这样的布置中,每个分区可以包含,例如,被布置成纵向(沿着方向103)为18个瓦片乘横向(沿着方向101)为32个瓦片的网格的596个瓦片。分区可以包含其它总数的瓦片,并且可以以不同大小的阵列布置。在一些情况下,分区之间的划分由asic 100的硬件特征来描绘。例如,如图3所示,分区110a、110b可以通过矢量处理单元104与分区110c、110d分开。

83.如本文所解释的,在一些实现方式中,瓦片102中一个或多个瓦片可以专用于存储操作调度18。也就是说,专用于存储操作调度的瓦片102不参与对输入数据(诸如权重输入和激活输入)执行计算。例如,专用于存储操作调度的瓦片102可以存储多个瓦片102(例如,相邻瓦片102)的独立操作调度。专用于存储操作调度的瓦片102可以解压缩每个瓦片的操

作调度的相关部分并在由asic 100执行程序期间的各种间隔处提供每个瓦片的操作调度的相关部分。例如,专用于存储操作调度的瓦片102可以,在程序开始时,瓦片102它们的操作调度覆盖第一操作时间帧(例如,计数器时间000000_hex到000fff_hex)的相应第一部分,且在计数器到达后续时间帧之前,迭代地它们的操作调度覆盖后续操作时间帧的后续部分。可替代地,如本文所公开的,不使用专用控制瓦片。相反,在这种情况下,每个瓦片的本地存储器存储用于该特定瓦片的操作调度。

84.图4中示出了示出用于在asic芯片100中使用的瓦片200的示例的示意图。每个瓦片200包括本地存储器202和耦合到存储器202的计算阵列204。本地存储器202包括定位在计算阵列204附近的物理存储器。计算阵列204包括多个单元206。计算阵列204的每个单元206包括被配置为基于对单元206的数据输入(诸如激活输入和权重输入)执行计算(例如,乘法和累加运算)的电路。每个单元可以在时钟信号的周期上执行计算(例如,乘法和累加运算)。计算阵列204可以具有比列更多的行、比行更多的列或相等数量的列和行。例如,在图4所示的示例中,计算阵列204包括布置成8行和8列的64个单元。其它计算阵列大小也是可能的,诸如具有16个单元、32个单元、128个单元或256个单元等的计算阵列。每个瓦片可以包括相同数量的单元和/或相同大小的计算阵列。对于asic芯片可以并行执行的操作的总数然后取决于芯片内具有相同大小计算阵列的瓦片的总数。例如,对于图3所示的asic芯片100,其包含大约1150个瓦片,这意味着每个周期可以并行执行大约92000次计算。可以使用的时钟速度的示例包括但不限于225mhz、500mhz、950mhz、1ghz、1.25ghz、1.5ghz、1.95ghz或2ghz。如图3所示,每个独立瓦片的计算阵列204是瓦片的较大脉动阵列的子集。

85.瓦片200中包含存储器202可以包括,例如,随机存取存储器(ram),诸如sram。可以使用其它存储器来代替。每个存储器202可以被配置为存储与asic芯片的n个瓦片102相关联的总存储器中的第(1/n)个。存储器202可以被提供为单个芯片或多个芯片。例如,图4中所示的存储器202被提供为四个单端口sram,其中的每个被耦合到计算阵列204。可替代地,存储器202可以被提供为两个单端口sram或八个单端口sram,以及其它配置。在纠错编码之后,存储器的联合容量可以是但不限于,例如,16kb、32kb、64kb或128kb。通过在本地向计算阵列提供物理存储器202,在一些实现方式中,asic 100的布线密度可以极大降低。在其中存储器在asic 100内集中的替代配置中,与如本文所述的本地提供相反,可能针对存储器带宽的每个比特都需要布线。覆盖asic 100的每个瓦片所需要的布线的总数将远远超过asic 100内的可用空间。相比之下,为每个瓦片提供专用存储器,跨越asic 100的区域所需的总数可以大量地减少。

86.瓦片200也包括可控总线线路。可控总线线路可以被分类成多个不同的组。例如,可控总线线路可以包括被配置为在每个基本方向上在瓦片之间传送数据的第一组通用可控总线线路210。也就是说,第一组可控总线线路210可以包括:被配置为向沿着瓦片网格的第一维度101的第一方向(在图4中被称为“东”)传送数据的总线线路210a;被配置为向沿着瓦片网格的第一维度101的第二方向(在图4中被称为“西”)传送数据的总线线路210b,其中第二方向与第一方向相反;被配置为向沿着瓦片网格的第二维度103的第三方向(在图4中被称为“北”)传送数据的总线线路210c;以及被配置为向沿着瓦片网格的第二维度103的第四方向(在图4中被称为“南”)传送数据的总线线路210d,其中第四方向与第三方向相反。通用总线线路210可以被配置为携载控制数据、激活输入数据、来自和/或去往通信接口的数

据、来自和/或去往矢量处理单元的数据、以及要由瓦片200使用和/或存储的数据(例如,权重输入)。瓦片200可以包括用于控制可控总线线路的一个或多个控制元件221(例如,触发器和复用器),并且因此路由去往和/或来自瓦片200和/或来自存储器202的数据。

87.可控总线线路还可以包括第二组可控总线线路,在本文中被称为计算阵列部分和总线线路220。计算阵列部分和总线线路220可以被配置为携载从由计算阵列204执行的计算输出的数据。例如,总线线路220可以被配置为携载从计算阵列204中的行中获得的部分和数据,如图4所示。在这种情况下,总线线路220的数量将与阵列204中行的数量匹配。例如,对于一个8

×

8的计算阵列,将有8个部分和总线线路220,其中的每个被耦合到计算阵列204中的对应行的输出。计算阵列输出总线线路220可以被进一步配置为耦合到asic芯片内的另一瓦片,例如,作为对asic芯片内的另一瓦片的计算阵列的输入。例如,瓦片200的阵列部分和总线线路220可以被配置为接收位于距离瓦片200至少一个瓦片的第二瓦片的计算阵列的输入(例如,部分和220a)。计算阵列204的输出然后被添加到部分和线路220以产生新的部分和220b,其可以从瓦片200输出。部分和220b然后可以被传给另一瓦片,或者可替代地,传给矢量处理单元。例如,每个总线线路220可以被耦合到矢量处理单元的对应分段(诸如图3中的分段106)。

88.如关于图3所解释的,可控总线线路可以包括被配置为允许数据沿着总线传递的诸如传送器元件(例如,触发器)的电路。在一些实现方式中,对于每个瓦片,每个可控总线线路包括对应的传送器元件。如关于图3进一步解释的,可控总线线路可以包括被配置为允许数据在asic芯片的不同瓦片、矢量处理单元和通信接口之间传送的诸如复用器的电路。复用器可以位于有数据源或汇的任何地方。例如,在一些实现方式中,如图4所示,控制电路221(诸如复用器)可以位于可控总线线路的交叉处(例如,在通用总线线路210a和210d的交叉处、在通用总线线路210a和210c的交叉处、在通用总线线路210b和210d的交叉处,和/或在通用总线线路210b和210c的交叉处)。在总线线路交叉处的复用器可以被配置为在交叉处的总线之间传送数据。此外,如参照图1所解释的,控制电路221可以被配置为执行瓦片的独立操作调度。例如,控制电路221可以通过将数据路由到瓦片102内的适当组件(例如,将去往/来自sram 202的激活数据或层权重路由到计算阵列204中的适当单元206)或者将输出数据和输入数据路由到可控总线线路或路由来自可控总线线路的输出数据和输入数据,来执行操作调度的操作。

89.图5a-图11b是示出其中asic 100被用作计算神经网络推理的硬件加速器的示例过程的示意图。图5a、图6a、图7a、图8a、图9、图10a和图11a是示出在该过程中在不同时间处通过asic 100的数据流的概况的示意图。图5b、图6b、图7b、图8b、图10b和图11b是分别示出在与图5a、图6a、图7a、图8a、图10a和图11a相关联的时间处在asic 100的单个瓦片(例如,控制瓦片或其它瓦片102)内的数据流的示意图。图5a-图11b中的省略号指示图中未示出的重复特征的存在。图5a-图11b的每个图中提供的罗盘300为数据流提供定向。标签“n”、“w”、“s”和“e”不与实际的地理方向对应,而是用于指示数据可以流过网格的不同相对方向。在由标签“n”、“w”、“s”和“e”指示的方向上传递数据的可控总线线路在本文中被称为向北流动的总线线路、向西流动的总线线路、向南流动的总线线路,和向东流动的总线线路。

90.图5a-图11a中的瓦片102和矢量处理单元104的布置与图3所示的布置类似。例如,瓦片102的一半可以布置在矢量处理单元104的第一侧上,而瓦片102的另一半可以布置在

矢量处理单元104的相对的第二侧上。通信接口108在图5a-图11a中示出为整个布置在瓦片网格的右侧上,但是也可以如图3的示意图中描绘的定位在瓦片网格的任一侧上。

91.在第一步中,如图5a所示,模型(例如,神经网络模型)的第一层的输入值(例如,激活输入和/或权重输入)从通信接口108加载到asic 100内的一个或多个瓦片102(例如,所有的瓦片102)上。也就是说,根据相应的操作调度18,通信接口108读取外部输入数据(例如,激活输入和/或层权重),并将数据发送到可控总线线路。输入值遵循沿着可控总线线路(例如,诸如本文所描述的通用可控总线线路)的数据路径,从通信接口108到一个或多个控制瓦片。通过使用在不同总线线路交叉的位置处的复用器(例如,参见图4中的路由元件221),数据可以在不同总线线路之间传送。例如,如图5a所示,输入数据沿着需要在向西流动的通用可控总线线路上并且然后在向南流动的通用可控总线线路上传输的数据路径流动。通过使用在向西流动的总线线路和向南流动的总线线路交叉的位置处的复用器,输入数据可以从向西流动的总线线路传送到向南流动的总线线路。在一些实现方式中,在先前的第一推理正在由asic 100执行时,第二推理的权重输入可以被加载到一个或多个控制瓦片。换言之,控制瓦片的操作调度与正在计算推理的其它瓦片102的操作调度协调,使得在其它瓦片102正在计算第一推理的相同计数器时间处,控制瓦片102正在准备要被发送到用于下一个推理的计算的其它瓦片102的、用于下一个推理的新的激活数据和/或权重。

92.图5b是示出来自asic 100的瓦片102的示例的详细视图的示意图。如图5b所示,瓦片102可以包括其上存储了输入值的存储器302。存储器302可以包括如本文关于图4所描述的任何合适的存储器。如上面所讨论的,存储器302可以被用于存储瓦片的独立操作调度18(或在采用专用瓦片102来存储操作调度的实现方式中存储独立操作调度18的部分)。输入值是从邻近于瓦片102或通过瓦片102经过的一个或多个向南流动的通用可控总线线路310d获得的。来自向南流动的可控总线线路310d的数据可以通过使用复用器传送到存储器302。在此步骤期间不使用其它通用可控总线线路(310a、310b、310c)。

93.瓦片102还包括直接耦合到存储器302的单元306的计算阵列。如本文所解释的,单元306的计算阵列可以是构成asic的瓦片的较大脉动单元阵列的子集。以阵列布置单元306,其中在图5b中示出位置(i,j)=(0,0)处的单个单元306,其中参数i表示阵列内的单元行位置,而j表示阵列中的单元列位置。在图5b所示的示例中,计算阵列具有8行和8列,但其它大小也是可能的。计算阵列的每个单元306可以包括被配置为基于在瓦片处接收到的数据执行计算的电路。例如,每个单元306可以包括乘法器电路、加法器电路和一个或多个寄存器。每个单元306的输出可以作为部分和传给计算阵列内的相邻单元或者传给asic 100中的另一瓦片的计算阵列内的单元。单元306的计算阵列在后面的步骤中使用。

94.瓦片102还包括用于提供来自先前瓦片的数据的可控总线线路320。例如,可控总线线路320可以携载从asic 100中的先前瓦片的计算阵列获得的部分和输出数据,并且将部分和输出数据作为输入提供给瓦片102内的计算阵列的单元。在此步骤中不使用可控总线线路320。

95.瓦片102还包括用于将激活输入值作为输入提供给计算阵列的单元306的可控总线线路330。例如,激活输入值可以被提供给单元306内的乘法器电路。激活输入值可以从通信接口108或从asic 100中的另一瓦片内的单元获得。来自可控总线线路330的数据可以通过使用复用器传送到单元306。在图5a-图5b中描绘的示例步骤中不使用可控总线线路330。

96.如本文所解释的,在一些实现方式中,一个或多个瓦片102专用于存储操作调度18和/或来自矢量处理单元104的输出信息。在一些实现方式中,一个或多个控制瓦片内的计算阵列可以不被用于执行计算。可替代地,除了对输入数据(诸如接收到的权重输入和激活值)执行计算之外,一个或多个控制瓦片还可以被配置为存储操作调度18。在一些实现方式中,权重输入被加载到将在其中使用该权重输入的每个瓦片102的存储器中,而无需首先将权重输入存储在一个或多个控制瓦片的子集中。

97.在第二步中,如图6a所示,在调度的计数器值处,权重输入301被加载到瓦片102内的计算阵列的独立单元306中。将权重输入301加载到独立单元306中可以包括将数据从一个或多个控制瓦片的存储器传送到权重输入301所属于的对应瓦片102。权重输入301可以沿着通用可控总线线路传递到瓦片102,并且通过耦合到总线线路和存储器的复用器传送到存储器。图6b是瓦片102的示例的详细视图。权重输入301可以在模型执行(其可以包括多个推理的计算)的期间存储在存储器302中。作为对从一个或多个控制瓦片加载权重输入301的替代,权重输入301可能已经直接从通信接口108预加载到瓦片102的存储器中。为了准备用于执行的模型,对于每个瓦片102,权重输入301可以从瓦片102的存储器302加载到该瓦片102内的计算阵列的每个单元306中。例如,权重输入301可以被加载到单元306内的寄存器400(也被称为“后寄存器(back register)”)中。后寄存器的使用允许在下一个权重输入被加载到后寄存器中的同时由单元306对当前权重输入执行计算。尽管仅针对图6b中的一个单元306示出加载权重寄存器,但是在该步骤期间,计算阵列内其它单元的权重寄存器也可以被加载。

98.在第三步中,如图7a所示,在调度的计数器值处,激活值500被引入到瓦片102中,并且可以在那里被存储在存储器302内。激活值500可以在多个时钟周期上传送。然后,由每个瓦片102的计算阵列使用从瓦片102中的存储器302中接收到的激活值500和权重输入301来执行计算。例如,计算可以包括将激活值乘以权重输入,并且然后将该结果与不同权重输入和激活值的乘积求和。在一些实现方式中,激活值500在可控总线线路330上被传递到瓦片102以及瓦片102之间。可控总线线路330中的每个可以沿着相同的方向延伸。例如,如图7b所示,可控总线线路330沿着与可控总线线路320沿着其延伸的网格维度正交的网格维度侧向延伸。此外,如由图7a中的箭头501以及图7b中的可控总线线路330上的箭头501所指示的,激活输入数据500在总线线路330上沿相同(例如,向东流动)方向传输。可替代地,在一些实现方式中,激活输入值500中的一些在可控总线线路330中的一些上沿第一方向(例如,向东流动的方向)传输,而一些其它激活输入值500在一些其它可控总线线路330上沿相反的第二方向(例如,向西流动的方向)传输。

99.在一些实现方式中,延伸通过每个瓦片102的可控总线线路330的数量由计算阵列的大小确定。例如,延伸通过每个瓦片102的可控总线线路330的数量可以至少等于计算阵列内的单元的行的数量。在图7b所示的示例中,鉴于瓦片102的计算阵列内有8行单元306,有8个可控总线线路330穿过瓦片102。在一些实现方式中,每个分开的可控总线线路330将激活输入值500传送到计算阵列的对应行内的单元306。例如,对于瓦片102内的8

×

8计算阵列的单元306,第一可控总线线路330将激活输入值500传送到阵列的第一行内的单元306,第二可控总线线路330将激活输入值500传送到阵列的第二行内的单元306等,直到最后的可控总线线路330,其将激活输入值500传送到阵列的最后一行内的单元306。附加可控总线

线路(例如,部分和总线线路)可以穿过每个瓦片以提供来自另一瓦片的部分和、接收瓦片内的计算结果并将其组合到所提供的部分和,以及将新的部分和输出到新的瓦片或输出到矢量处理单元。

100.在一些实现方式中,可控总线线路330将激活输入值500传送到在单元306内被配置为执行计算的电路。例如,如图7b所示,可控总线线路330被配置为将激活输入值500传送到单元306内的乘法器电路502。可以通过使用可控总线线路330上的复用器将激活输入值500传送到乘法器电路502。

101.在一些实现方式中,一旦确定激活输入值500和权重输入值301就位(例如,在执行加载操作所需的预定数量的计数器周期之后),瓦片102内的计算阵列的单元306就使用从瓦片102中的存储器302接收到的激活输入值500和权重输入值301来执行计算。例如,如图7b所示,先前存储在寄存器400中的权重输入值301被传送到寄存器504(也被称为“前寄存器”)。然后,使用乘法器电路502,将权重输入值301与接收到的激活输入值500相乘。

102.如本文所解释的,激活输入值500在可控总线线路330上传递。在一些实现方式中,可控总线线路330是通用可控总线线路。在一些实现方式中,可控总线线路330可以专用于提供激活输入。例如,如图7b所示,可以通过线路330将激活输入值提供到瓦片102(例如,到瓦片102内的计算阵列的单元306),而其它通用可控总线线路310b可以用于向瓦片102提供其它数据和/或指令。

103.在第四步中,如图8b所示,在调度的计数器值处,每个单元306内的权重输入值301和激活输入值500之间的计算结果被传给单元306内的电路602以产生输出值600。在图8b的示例中,电路602包括求和电路。每个单元306内的求和电路602被配置为对乘法器电路502的乘积与从asic 100中的另一瓦片102或从计算阵列内的另一单元306获得的另一值求和。从另一瓦片102或从另一单元306获得的值可以包括,例如,累加值。因此,求和电路602的输出值600是新的累加值。求和电路602然后可以将新的累加值600发送到位于瓦片102内的计算阵列的底部(例如,在向南流动的方向)相邻单元中的另一单元。新的累加值600可以用作底部相邻单元中求和的运算对象。对于计算阵列内的最后一行单元,新的累加值600可以被传送到asic100内的另一瓦片102,如图8a所示。在另一示例中,新的累加值600可以被传送到与其中生成了新的累加值600的瓦片102相距至少一个瓦片的另一瓦片102。可替代地,还如图8a所示,来自计算阵列内最后一行单元的新的累加值600被传送到矢量处理单元104。

104.被传送到瓦片102中或从瓦片102传送出的累加值600可以沿着可控总线线路320传递。可控总线线路320中的每个沿着相同方向延伸。例如,如图8b所示,可控总线线路320沿着与可控总线线路330沿着其延伸的网格维度正交的网格维度竖直延伸。此外,如由图8a中的箭头604以及图8b中的箭头604所指示的,累加值600在可控总线线路320上沿着向北流动或向南流动的方向传输,这取决于矢量处理单元104相对于从其中生成累加值600的瓦片102的位置。例如,对于图8a中位于矢量处理单元104上方的瓦片102,累加值600在可控总线线路320上沿向南流动的方向朝矢量处理单元104传输,而对于位于矢量处理单元104下方的瓦片102,累加值600沿向北流动的方向朝矢量处理单元104传输。

105.在第五步中,如图9所示,在调度的计数器值处,由矢量处理单元104接收到的数据(例如,累加值)由矢量处理单元104处理以提供处理后的值900。矢量处理单元104处的数据的处理可以包括:向在矢量处理单元104处接收的数据施加偏差(bias)、执行附加累加操

作、和/或向接收的数据应用非线性函数(例如,神经网络系统中已知的整流(rectifier)函数或双弯曲(sigmoid)函数)。也可以由矢量处理单元104应用其它操作。矢量处理单元104可以包括布置在多个分段106中的电路,其中每个分段106被配置为处理从瓦片102的对应列接收的数据并生成对应的处理后的值900。

106.在第六步中,如图10a所示,在调度的计数器值处,来自矢量处理单元104的处理后的值900被传送到asic 100的一个或多个瓦片并存储在asic100的一个或多个瓦片中,例如,asic 100的瓦片的子集。例如,处理后的值900可以被发送到控制瓦片103,其与矢量处理单元104直接相邻定位。可替代地或附加地,处理后的值900可以被发送到asic 100内其它瓦片102中的一个或多个。处理后的值900可以通过通用可控总线线路(诸如可控总线线路310c)传送到一个或多个瓦片。在到达瓦片(例如,控制瓦片或其它瓦片102)后,处理后的值900可以存储在瓦片的存储器202中。例如,可以使用与可控总线线路310c相关联的复用器将处理后的值900传送到存储器902。存储处理后的值900的步骤可以发生在获得了每个模型层的推理之后。在一些实现方式中,可以将处理后的值900作为输入值提供给模型的下一层。

107.在第七步中,如图11a和图11b所示,在调度的计数器值处,处理后的值900能够从asic 100导出。例如,处理后的值900可以从一个或多个控制瓦片的存储器202传送到通信接口108。处理后的值900可以在可控总线线路(例如,可控总线线路310c和/或310d)上传递到通信接口108。处理后的值900可以通过与总线线路相关联的复用器传送到可控总线线路。

108.例如,如果已经获得模型的最后一层的推理,或者如果模型已经被分隔在多个asic之中且已经获得与asic 100相关联的最后一层的推理,则处理后的值900可以从asic 100导出。处理后的值900可以由通信接口108的serdes接口接收并导出到另一目的地,包括但不限于,例如,另一asic 100或现场可编程门阵列芯片。

109.关于图5a-图11b描述的示例过程可能需要激活值和权重输入在执行单元计算之前完全传播遍及每个瓦片的计算阵列,或者单元可以在所有值完全传播之前执行计算。在任一情况下,可以协调独立瓦片的操作调度,以便计算被正确定时。例如,如果特定机器学习程序需要激活值和权重输入在执行单元计算之前完全传播通过每个瓦片的计算阵列,则操作指令可以调度计算的执行达确保激活值和权重完全传播的时间。此外,尽管已经以权重输入被发送到计算阵列的列并且激活输入被发送到计算阵列的行描述了asic 100,但是在一些实现方式中,权重输入被发送到阵列的行并且激活输入被发送到阵列的列。

110.此外,尽管计算阵列已经在本文中被描述为使用每个单元内的独立求和电路,但是计算阵列内的单元的组(例如,一列内的所有单元)可以直接耦合到单个求和电路,该求和电路对来自组中的单元的接收到的输出求和,因此减少存储输出所需的求和电路的数量。

111.本说明书中描述的主题的实施例和功能操作可以在数字电子电路中、在计算机硬件(包括在本说明书中公开的结构及其结构等效物)中实现,或者在它们中的一个或多个的组合中实现。本说明书中描述的主题的实施例可以实现为一个或多个计算机程序,即,编码在有形的非暂时性程序载体上的计算机程序指令的一个或多个模块,用于由数据处理装置执行或控制数据处理装置的操作。可替代地或附加地,程序指令可以编码在人工生成的传

播信号(例如,机器生成的电、光或电磁信号)上,该人工生成的传播信号被生成以编码信息,用于传输到合适的接收器装置以由数据处理装置执行。计算机存储介质可以是机器可读存储设备、机器可读存储基板、随机或串行存取存储器设备,或者它们中的一个或多个的组合。

112.术语“数据处理装置”涵盖用于处理数据的所有种类的装置、设备和机器,包括例如可编程处理器、计算机或多个处理器或计算机。装置可以包括专用逻辑电路,例如,fpga(现场可编程门阵列)或asic。除了硬件之外,装置还可以包括为所讨论的计算机程序创建执行环境的代码,例如,构成处理器固件、协议栈、数据库管理系统、操作系统或它们中的一个或多个的组合的代码。

113.本说明书中描述的过程和逻辑流可以由一个或多个可编程计算机执行,该一个或多个可编程计算机执行一个或多个计算机程序以通过对输入数据进行操作并生成输出来执行功能。过程和逻辑流还可以由专用逻辑电路(例如,fpga、asic或gpgpu(通用图形处理单元))执行,并且装置也可以实现为专用逻辑电路。

114.尽管本说明书包含许多具体实现方式细节,但这些不应被解释为对任何发明的范围或可能要求保护的内容的范围的限制,而是作为对可能特定于特定发明的特定实施例的特征的描述。在本说明书中在分开的实施例的上下文中描述的某些特征也可以在单个实施例中组合实现。反之,在单个实施例的上下文中描述的各种特征也可以在多个实施例中分开地或以任何合适的子组合来实现。此外,尽管特征可能在上面被描述为以某些组合起作用,并且甚至最初如此要求保护,但在一些情况下,来自要求保护的组合的一个或多个特征可以从组合中删除,并且要求保护的组合可以指向子组合或子组合的变体。

115.类似地,虽然在附图中以特定顺序描绘了操作,但这不应被理解为要求这些操作以示出的特定顺序或以相继顺序执行,或者要求所有示出的操作被执行以实现期望的结果。在某些情况下,多任务和并行处理可能是有利的。此外,上述实施例中各种系统模块和组件的分离不应被理解为在所有实施例中都要求这样的分离,并且应该理解,所描述的程序组件和系统通常可以一起集成在单个软件产品中,或者封装到多个软件产品中。

116.已经描述了本主题的特定实施例。其它实施例也在所附权利要求的范围内。例如,虽然总线线路被描述为“可控的”,但并非所有总线线路都需要具有相同级别的控制。例如,可以有不同程度的可控性,其中一些总线线路只有当一些总线线路在它们可以从中获取数据或它们可以向其发送数据的瓦片数量方面受到限制时才能被控制。在另一示例中,一些总线线路可以专用于沿着单个方向提供数据,诸如本文所述的北、东、西或南。在一些情况下,权利要求中记载的动作可以以不同的顺序执行,并且仍能实现期望的结果。作为一个示例,附图中描绘的过程不一定需要所示的特定顺序或相继顺序以实现期望的结果。在某些实现方式中,多任务和并行处理可能是有利的。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。