1.本技术涉及加密技术领域,提供一种加密系统,尤其指一种能切换加密层级的可调式五阶加密系统及其发送端装置和接收端装置。

背景技术:

2.进阶加密标准(advanced encryption standard,aes),在密码学中又称rijndael加密法,是美国联邦政府采用的一种区段加密标准。这个标准用来替代原先的des,已经被多方分析且广为全世界所使用。截至2006年,针对aes唯一的成功攻击是旁道攻击或社会工程学攻击。美国国家安全局稽核了所有的参与竞选aes的最终入围者,认为他们均能够满足美国政府传递非机密档案的安全需要。

3.进阶加密标准届今已有过多次破解经历,aes中128位密钥版本有10个加密循环,192位密钥版本有12个加密循环,256位密钥版本则有14个加密循环。至2006年为止,最著名的攻击是针对aes的7次加密循环的128位密钥版本,8次加密循环的192位密钥版本、和9次加密循环的256位密钥版本所作的攻击。随着硬设备的效率增加,估计以暴力攻击法完全破解aes的日子已相去不远。

4.此外,随着硬设备的持续升级,人工智能现已足以达到商用化层级的阶段。通过硬设备的处理效能以及人工智能的强大计算能力,现今广泛使用的加密标准很有可能经由人工智能通过大量运算的方式破解。基于上述的原因,有必要针对现有的加密技术进行改良。

技术实现要素:

5.本技术的主要目的,在于提供一种可调式五阶加密系统包括发送端装置以及接收端装置。所述发送端装置包括数据生成模块以及数据加密模块。所述数据加密模块包括加密层级设定器以及五阶加密器。所述加密层级设定器用以设定所述五阶加密器的加密层级,所述数据加密模块自所述数据生成模块取得至少一个数据封包,经由所述五阶加密器所选定的所述加密层级对所述数据封包进行加密后输出加密序列。所述接收端装置包括数据目标模块以及数据解密模块。所述数据解密模块包括解密层级设定器以及五阶解密器。所述解密层级设定器用以依据所述加密层级设定所述五阶解密器的解密层级,所述数据解密模块自所述发送端装置取得所述加密序列,经由所述解密所述五阶解密器所选定的所述解密层级对所述加密序列进行解密后输出还原后的所述数据封包至所述数据目标模块。

6.本技术的另一目的,在于提供一种发送端装置,包括数据生成模块以及数据加密模块。所述数据加密模块包括加密层级设定器以及五阶加密器,所述加密层级设定器用以设定所述五阶加密器的加密层级,所述数据加密模块自所述数据生成模块取得至少一个数据封包,经由所述五阶加密器所选定的所述加密层级对所述数据封包进行加密后输出加密序列。

7.本技术的另一目的,在于提供一种接收端装置,包括数据目标模块以及数据解密模块。所述数据解密模块包括解密层级设定器以及五阶解密器。所述解密层级设定器用以

依据所述加密层级设定所述五阶解密器的解密层级,所述数据解密模块自所述发送端装置取得所述加密序列,经由所述解密所述五阶解密器所选定的所述解密层级对所述加密序列进行解密后输出还原后的所述数据封包至所述数据目标模块。

8.可见,比起现有技术,本技术可依据需要的加密程度切换加密层级,并且能经由一套硬件实现不同的加密层级防护。

附图说明

9.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其它的附图。

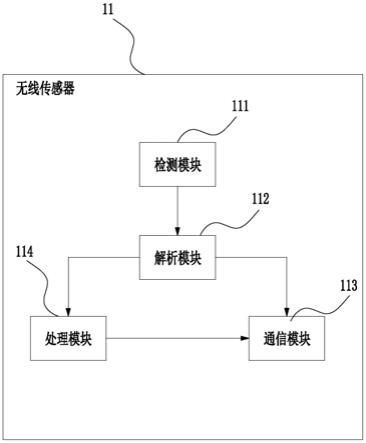

10.图1为本技术实施例提供的可调式五阶加密系统的模块示意图(一)。

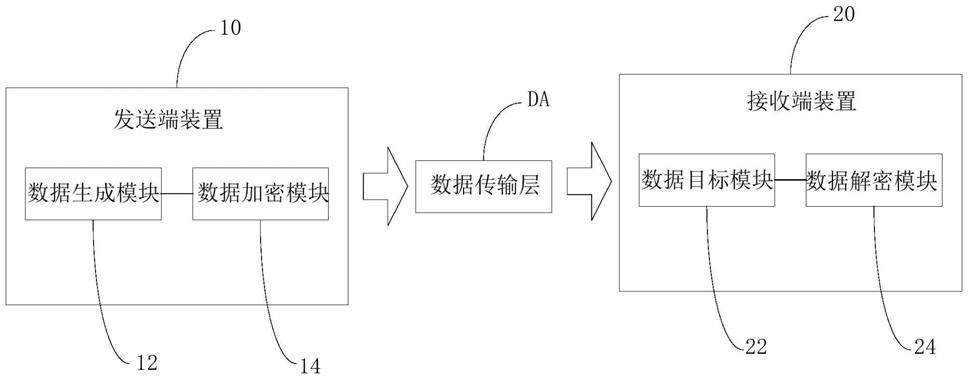

11.图2为本技术实施例提供的可调式五阶加密系统的模块示意图(二)。

12.图3为本技术实施例提供的五阶加密器的模块示意图。

13.图4为本技术实施例提供的五阶加密器的逻辑运算示意图。

14.图5为本技术实施例提供的五阶解密器的模块示意图。

15.图6为本技术实施例提供的五阶解密器的逻辑运算示意图。

16.图7为本技术实施例提供的可调式五阶加密方法的流程示意图。

17.图8为本技术实施例提供的五阶加密器的加密流程示意图。

18.图9为本技术实施例提供的五阶解密器的解密流程示意图。

19.100:可调式五阶加密系统;10:发送端装置;12:数据生成模块;14:数据加密模块;142:加密层级设定器;144:五阶加密器;1441:第一八位串流加密器;1441l:加密线性反馈移位寄存器;1441g:加密逻辑闸;1442:第二八位串流加密器;1442l:加密线性反馈移位寄存器;1442g:加密逻辑闸;1443:十六位串流加密器;1443l:加密线性反馈移位寄存器;1443g:加密逻辑闸;1444:三十二位串流加密器;1444l:加密线性反馈移位寄存器;1444g:加密逻辑闸;1445:六十四位串流加密器;1445l:加密线性反馈移位寄存器;1445g:加密逻辑闸;20:接收端装置;22:数据目标模块;24:数据解密模块;242:解密层级设定器;244:五阶解密器;2441:第一八位串流解密器;2441l:解密线性反馈移位寄存器;2441g:解密逻辑闸;2442:第二八位串流解密器;2442l:解密线性反馈移位寄存器;2442g:解密逻辑闸;2443:十六位串流解密器;2443l:解密线性反馈移位寄存器;2443g:解密逻辑闸;2444:三十二位串流解密器;2444l:解密线性反馈移位寄存器;2444g:解密逻辑闸;2445:六十四位串流解密器;2445l:解密线性反馈移位寄存器;2445g:解密逻辑闸;da:数据传输层;es1:第一加密序列;es2:第二加密序列;es3:第三加密序列;es4:第四加密序列;es5:第五加密序列;pk:数据封包;pk1:第一数据封包;pk2:第二数据封包;pk3:第三数据封包;pk4:第四数据封包;pk5:第五数据封包。

具体实施方式

20.有关本技术之详细说明及技术内容,现就配合图式说明如下。以下针对本技术的其中一较佳实施例进行说明,请参阅图1,为本技术可调式五阶加密系统的模块示意图

(一),如图所示:

21.本实施例主要提供了一种可调式五阶加密系统100,用于多个装置间相互传输数据时,对各装置所传输的数据分别进行加密及解密。各产生数据或接收数据的装置可以为计算机(computer)、服务器(server)、行动装置(mobile device)、物联网装置(例如:监视器、电视、云端硬盘、灯具等)、大量制造设备或机台等,在本技术中不予以限制。在本技术中依据信号的收发关系将各装置定义为作为数据发送源的发送端装置10以及对应于发送端装置10用以接收发送端装置10数据的接收端装置20。须特别注意的是,本技术并不以发送端装置10仅执行数据加密功能、接收端装置20仅执行数据解密功能为限,具体而言,发送端装置10及接收端装置20一般均可同时具有加密及解密的功能,以确保数据于双向传输的过程中以彼此的密钥进行加密或解密,在此必须先行说明。

22.发送端装置10及接收端装置20之间可以通过有线或无线网络传输数据。于其中一较佳实施例中,发送端装置10及接收端装置20之间可以通过因特网(internet)、局域网络、或于任意有线或无线通信端口之间传输数据,在本技术中不予以限制。为了完成数据加密、解密及传输的功能,发送端装置10及接收端装置20至少应包括处理器(processor)、储存单元、通讯单元彼此协同完成相应功能的工作,例如实体线路网卡、无线网卡、蓝牙模块(bluetooth)、紫蜂模块(zigbee)等,所述等信号的传输方式及传输接口非属本技术所欲限制的范围。

23.在一个实施例中,本技术可调式五阶加密系统100中所述的模块、器、或单元的组合及其对应执行的功能,可以由单一芯片或多个芯片的组合协同执行,上述芯片配置的数量非属本技术所欲限定的范围。此外,所述的芯片可以为但不限定于处理器、中央处理器(central processing unit,cpu)、微处理器(microprocessor)、数字信号处理器(digital signal processor,dsp)、特殊应用集成电路(application specific integrated circuits,asic)、可程序化逻辑设备(programmable logic device,pld)等可将信息或信号做处理、转换用途或特殊用途的其它类似装置或这些装置的组合,在本技术中不予以限制。

24.在一个实施例中,发送端装置10主要包括数据生成模块12以及数据加密模块14。数据生成模块12例如可以为高速缓存(cache memory)、动态随机存取内存(dram)、持续性内存(persistent memory)用以储存及管理预备传送及加密的数据。数据加密模块14自所述数据生成模块12取得至少一个数据封包,数据加密模块14可以为执行加密计算处理用的处理器或微处理器,在本技术中不予以限制。最后,数据加密模块14将加密后的数据封包输出至接收端装置20,在此定义由数据加密模块14所输出的加密后的数据封包为加密序列。

25.在一个实施例中,数据加密模块14包括加密层级设定器142以及输入端连接至加密层级设定器142的五阶加密器144,请一并参见图2以及图3,为本技术可调式五阶加密系统的模块示意图(二)、五阶加密器的模块示意图,如图所示:加密层级设定器142用以依据用户设定/自动配置去设定五阶加密器144的加密层级。五阶加密器144的输入端连接至数据生成模块12的输出端取得至少一个数据封包pk,五阶加密器144包括依序连接的第一八位串流加密器1441、第二八位串流加密器1442、十六位串流加密器1443、三十二位串流加密器1444以及六十四位串流加密器1445(在此定义第一八位串流加密器1441、第二八位串流加密器1442、十六位串流加密器1443、三十二位串流加密器1444以及六十四位串流加密器

1445的上位统称为串流加密器)。

26.具体而言,第一八位串流加密器1441的输入端连接至加密层级设定器142的输出端、另一输入端连接至数据生成模块12用以接收数据封包pk;第二八位串流加密器1442输入端连接至加密层级设定器142的输出端、另一输入端连接至第一八位串流加密器1441的输出端;十六位串流加密器1443的输入端连接至加密层级设定器142的输出端、另一输入端连接至第二八位串流加密器1442的输出端;三十二位串流加密器1444的输入端连接至加密层级设定器142的输出端、另一输入端连接至十六位串流加密器1443的输出端;六十四位串流加密器1445的输入端连接至加密层级设定器142的输出端、另一输入端连接至三十二位串流加密器1444的输出端。在本实施例中,加密层级设定器142依据加密层级(共五阶加密层级)选择要将第一八位串流加密器1441、第二八位串流加密器1442、十六位串流加密器1443、三十二位串流加密器1444、六十四位串流加密器1445中何者进行启动以及由何者输出加密后的数据封包pk,并且当位于序列后方的串流加密器被启动时,所述串流加密器前方的串流加密器也须启动。例如:加密层级设定器142设定二阶加密层级时,加密层级设定器142会启动第二八位串流加密器1442并一并启动一八位串流加密器1441,使数据封包pk依序经由第一八位串流加密器1441以及第二八位串流加密器1442进行加密,并由第二八位串流加密器1442将加密后的数据封包pk输出,由此进行二阶加密层级(相当于十六位加密装置)的加密;其余未使用到的十六位串流加密器1443、三十二位串流加密器1444以及六十四位串流加密器1445则不启动。当第一阶加密层级仅启动第一八位串流加密器1441时,加密系统将可以构成一八位加密装置;当第二阶加密层级仅启动第一八位串流加密器1441以及第二八位串流加密器1442时,加密系统将可以构成一十六位加密装置;当第三阶加密层级仅启动第一八位串流加密器1441、第二八位串流加密器1442以及十六位串流加密器1443时,加密系统将可以构成一三十二位加密装置;当第四阶加密层级仅启动第一八位串流加密器1441、第二八位串流加密器1442、十六位串流加密器1443以及三十二位串流加密器1444时,加密系统将可以构成一六十四位加密装置;当第五阶加密层级为启动全部的串流加密器时,加密系统将可以构成一一百二十八位加密装置。

27.在仅启动第一八位串流加密器1441的情况,第一八位串流加密器1441的输出为第一加密序列es1;在仅启动第一八位串流加密器1441以及第二八位串流加密器1442的情况,第二八位串流加密器1442的输出为第二加密序列es2;在仅启动第一八位串流加密器1441、第二八位串流加密器1442以及十六位串流加密器1443的情况,十六位串流加密器1443的输出为第三加密序列es3;在仅启动第一八位串流加密器1441、第二八位串流加密器1442、十六位串流加密器1443以及三十二位串流加密器1444的情况,三十二位串流加密器1444的输出为第四加密序列es4;在串流加密器皆启动的情况,六十四位串流加密器1445的输出为第五加密序列es5。最后,加密层级设定器142所选定的加密层级控制五阶加密器144将对应加密层级的第一加密序列es1、第二加密序列es2、第三加密序列es3、第四加密序列es4或第五加密序列es5经由数据传输层da输出至接收端装置20。具体而言,在任一种加密层级仅会生成前述其中一种对应所述加密层级的加密序列。

28.在一个实施例中,所述的五阶加密器144中第一八位串流加密器1441、第二八位串流加密器1442、十六位串流加密器1443、三十二位串流加密器1444以及六十四位串流加密器1445分别包括有加密线性反馈移位寄存器(linear feedback shift register,lfsr)以

及一个或者多个加密逻辑闸(logic gate),所述加密线性反馈移位寄存器具有加密密钥,所述加密密钥可以由其它装置输入至加密线性反馈移位寄存器作为预设密钥,所述的装置非属本技术所欲限制的内容,在此先行说明。所述加密线性反馈移位寄存器将所述加密密钥的多个加密位抽头进行逻辑运算后获得加密操作数,所述加密操作数与所述数据封包pk经由所述加密逻辑闸进行运算后获得加密序列,并且所述加密操作数将反馈至加密线性反馈移位寄存器的第一位作为加密密钥的更新,所述的更新指所述加密操作数会输入至所述加密线性反馈移位寄存器的加密密钥的第一位,使原先所述加密密钥的第一位移动至第二位、原先所述加密密钥的第二位移动至第三位,依此类推,原先所述加密密钥的最末位会被前一位覆盖,由此达到所述加密密钥的更新。

29.在一个实施例中,请参见图4,为本技术五阶加密器的逻辑运算示意图,如图所示:第一八位串流加密器1441包括有加密线性反馈移位寄存器1441l(存有第一加密密钥a[1]至a[8],a[n]为所述第一加密密钥的第n位)以及加密逻辑闸1441g;第二八位串流加密器1442包括有加密线性反馈移位寄存器1442l(存有第二加密密钥b[1]至b[8],b[n]为所述第二加密密钥的第n位)以及加密逻辑闸1442g;十六位串流加密器1443包括有加密线性反馈移位寄存器1443l(存有第三加密密钥c[1]至c[16],c[n]为所述第三加密密钥的第n位)以及加密逻辑闸1443g;三十二位串流加密器1444包括有加密线性反馈移位寄存器1444l(存有第四加密密钥d[1]至d[32],d[n]为所述第四加密密钥的第n位)以及加密逻辑闸1444g;六十四位串流加密器1445包括有加密线性反馈移位寄存器1445l(存有第五加密密钥e[1]至e[64],e[n]为所述第五加密密钥的第n位)以及加密逻辑闸1445g。

[0030]

在一个实施例中,加密逻辑闸1441g、1442g、1443g、1444g、1445g以及逻辑运算皆使用互斥或门(exclusive or,xor)作为运算。在其它实施例中,逻辑闸1441g、1442g、1443g、1444g、1445g以及逻辑运算可以用and闸、or闸、其它逻辑闸或多个逻辑闸的组合实现运算,在本技术中不予以限制。

[0031]

在其它实施例中,前述的五阶加密器144也可以于后端设置一多路复用器(multiplexer,mux)决定输出的加密序列,或是在五阶加密器144前端搭配设置一个控制模块(control module)用以取代加密层级设定器142决定启动的串流加密器及逻辑闸的部分功能,上述各实施方式的变化非属本技术所欲限制的范围。

[0032]

在一个实施例中,请进一步参阅图1,接收端装置20包括数据目标模块22以及数据解密模块24。数据目标模块22相同可以为高速缓存(cache memory)、动态随机存取内存(dram)、持续性内存(persistent memory)用以储存及管理所接收到的数据。数据解密模块22系可以为执行解密计算处理用的处理器或微处理器,在本技术中不予以限制。最后,数据解密模块24用以将所接收到的加密序列经由对应的加密层级进行解密处理后将还原的原始数据封包输出至所述数据目标模块22以储存。

[0033]

在一个实施例中,数据解密模块24包括解密层级设定器242以及输入端连接至所述解密层级设定器242的五阶解密器244,请一并参见图2以及图5,为本技术可调式五阶加密系统的模块示意图(二)、五阶解密器的模块示意图,如图所示:解密层级设定器242用以设定五阶解密器244的解密层级,所述的解密层级的数量对应加密层级的数量。所述的五阶解密器244经由数据传输层da自发送端装置10取得至少加密序列,五阶解密器244包括依序连接的第一八位串流解密器2441、第二八位串流解密器2442、十六位串流解密器2443、三十

二位串流解密器2444以及六十四位串流解密器2445(在此定义第一八位串流解密器2441、第二八位串流解密器2442、十六位串流解密器2443、三十二位串流解密器2444、六十四位串流解密器2445的上位统称为串流解密器)。具体而言,六十四位串流解密器2445的输入端连接至解密层级设定器242的输出端、六十四位串流解密器2445的输出端连接至三十二位串流解密器2444的输入端;三十二位串流解密器2444的另一输入端连接至解密层级设定器242的输出端、三十二位串流解密器2444的输出端连接至十六位串流解密器2443的输入端;十六位串流解密器2443的另一输入端连接至解密层级设定器242的输出端、十六位串流解密器2443的输出端连接至第二八位串流解密器2442的输入端;第二八位串流解密器2442的另一输入端连接至解密层级设定器242的输出端、第二八位串流解密器2442的输出端连接至第一八位串流解密器2441的输入端;第一八位串流解密器2441的另一输入端连接至解密层级设定器242的输出端、第一八位串流解密器2441的输出端连接至数据目标模块22的输入端。

[0034]

在本实施例中,解密层级设定器242依据解密层级选择要启动的串流解密器以及依据解密层级选择加密序列要输入的串流解密器,由此将加密序列依序解密,并且当位于序列前方的串流解密器被启动时,所述串流解密器后方的串流解密器也须启动。例如:解密层级设定器242设定对应二阶加密层级的二阶解密层级时,解密层级设定器242会启动第二八位串流解密器2442并一并启动第一八位串流解密器2441,解密层级设定器242会依据二阶解密层级将加密序列输入第二八位串流解密器2442后,加密序列经由第二八位串流解密器2442、第一八位串流解密器2441进行解密,由第一八位串流解密器2441将解密后的加密序列输出,由此进行二阶解密层级的解密(相当于十六位解密装置);其余未使用到的十六位串流解密器2443、三十二位串流解密器2444以及六十四位串流解密器2445则不启动。在此定义最后由五阶解密器244所输出的解密后加密序列为还原数据封包。当第一阶解密层级(对应第一阶加密层级)仅启动第一八位串流解密器1441时,所述解密系统将可以构成一八位解密装置;当第二阶解密层级(对应第二阶加密层级)仅启动第一八位串流解密器2441以及第二八位串流解密器2442时,所述解密系统将可以构成十六位解密装置;当第三阶解密层级(对应第三阶加密层级)为启动第一八位串流解密器2441、第二八位串流解密器2442以及十六位串流解密器2443时,所述解密系统将可以构成三十二位解密装置;当第四阶解密层级(对应第四阶加密层级)仅启动第一八位串流解密器2441、第二八位串流解密器2442、十六位串流解密器2443以及三十二位串流解密器2444时,所述解密系统将可以构成六十四位解密装置;当第五阶解密层级(对应第五阶加密层级)启动全部的串流解密器时,所述解密系统将可以构成一百二十八位解密装置。具体而言,在任一种解密层级仅会接收到一种对应所述解密层级的加密序列。

[0035]

由此定义第一八位串流解密器2441的输出为第一数据封包pk1;第二八位串流解密器2442的输出为第二数据封包pk2;十六位串流解密器2443的输出为第三数据封包pk3;三十二位串流解密器2444的输出为第四数据封包pk4;六十四位串流解密器2445的输出为第五数据封包pk5。具体而言,五阶解密器244所输出的还原数据封包为第一数据封包pk1,一并在此说明。

[0036]

在一个实施例中,前述的五阶解密器244中第一八位串流解密器2441、第二八位串流解密器2442、十六位串流解密器2443、三十二位串流解密器2444以及六十四位串流解密

器2445分别包括有解密线性反馈移位寄存器(linear feedback shift register,lfsr)以及一个或者多个解密逻辑闸(logic gate),所述解密线性反馈移位寄存器具有解密密钥,所述解密密钥对应于加密密钥并且可以由其它装置输入至解密线性反馈移位寄存器作为一预设解密密钥,所述的装置非属本技术所欲限制的内容,在此先行说明。所述解密线性反馈移位寄存器将所述解密密钥的多个解密位抽头进行逻辑运算后获得解密操作数,所述解密操作数与接收到的加密序列经由所述解密逻辑闸进行运算后获得解密序列,其中,所述加密序列将反馈至解密线性反馈移位寄存器的第一位作为解密密钥的更新,所述的更新指所述加密序列会输入至将所述解密线性反馈移位寄存器的解密密钥的第一位,使原先所述解密密钥的第一位移动至第二位、原先所述解密密钥的第二位移动至第三位,依此类推,原先所述解密密钥的最末位会被前一位覆盖,由此更新所述解密密钥。

[0037]

具体而言,请参见图6,为本技术五阶解密器的逻辑运算示意图,如图所示:第一八位串流解密器2441包括有解密线性反馈移位寄存器2441l(存有与第一加密密钥a[1]至a[8]相同的第一解密密钥,在此标号相同于第一加密密钥)以及解密逻辑闸2441g;第二八位串流解密器2442包括有解密线性反馈移位寄存器2442l(存有与第二加密密钥b[1]至b[8]相同的第二解密密钥,在此标号相同于第二加密密钥)以及解密逻辑闸2442g;十六位串流解密器2443包括有解密线性反馈移位寄存器2443l(存有与第三加密密钥c[1]至c[16]相同的第三解密密钥,在此标号相同于第三加密密钥)以及解密逻辑闸2443g;三十二位串流解密器2444包括有解密线性反馈移位寄存器2444l(存有与第四加密密钥d[1]至d[32]相同的第四解密密钥,在此标号相同于第四加密密钥)以及解密逻辑闸2444g;六十四位串流解密器2445包括有解密线性反馈移位寄存器2445l(存有与第五加密密钥e[1]至e[64]相同的第五解密密钥,在此标号相同于第五加密密钥)以及解密逻辑闸2445g。原则上,所述的五阶解密器244中的逻辑闸与逻辑运算必须与五阶加密器144执行反向逻辑运算(例如五阶加密器144为and,则五阶解密器244为nand)。

[0038]

在其它实施例中,前述的五阶解密器244也可以在前端设置多路复用器(multiplexer,mux)用于确定加密序列输入至哪路串流解密器,或是在五阶解密器244前端搭配设置一个控制模块(control module)用以取代解密层级设定器242决定启动的串流解密器及逻辑闸的部分功能,该等实施方式的变化非属本技术所欲限制的范围。

[0039]

在其它实施例中,前述的数据生成模块12与数据加密模块14之间具有一进阶加密器时(图未示),数据目标模块22以及数据解密模块24之间具有一对应所述进阶加密器的进阶解密器(图未示),所述进阶加密器对数据生成模块12的数据封包pk进行加密处理后输出至数据加密模块14;所述进阶解密器用对应所述进阶加密器的解密处理还原所述数据封包pk至数据目标模块22。前述的加密处理例如:进阶加密标准(advanced encryption standard,aes),在本技术中不予以限制。

[0040]

以上针对本技术硬件架构的一具体实施例进行说明,有关于本技术的工作程序将于下面进行更进一步的说明,请参阅图7,为本技术可调式五阶加密方法的流程示意图:

[0041]

在进行数据传输前,加密层级设定器142与解密层级设定器242将依据用户设定/自动配置去设定相同的加密/解密层级(例如:当加密层级设定器142选定五阶加密器144加密层级为五阶时,解密层级设定器242将选定五阶解密器244解密层级为五阶),先行叙明在此。

[0042]

首先,在发送端装置10中,数据封包pk由数据生成模块12输出至数据加密模块14(步骤s201)。

[0043]

数据封包pk由数据加密模块14的五阶加密器144接收并依照加密层级设定器142所设定的加密层级对所述数据封包pk进行加密(步骤s202)。

[0044]

加密后的数据封包pk由所述五阶加密器144输出加密序列至接收端装置20(步骤s203)。

[0045]

加密序列经由数据解密模块24中的五阶解密器244依照解密层级设定器242对应加密层级的解密层级将所述加密序列进行解密(步骤s204)。

[0046]

解密后的加密序列由所述五阶解密器244输出还原数据封包至数据目标模块22储存(步骤s205)。

[0047]

在一个实施例中,所述五阶加密器144具有第一八位串流解密器2441、第二八位串流解密器2442、十六位串流解密器2443、三十二位串流解密器2444以及六十四位串流解密器2445的五阶加密器144进行加密;所述五阶解密器244具有第一八位串流解密器2441、第二八位串流解密器2442、十六位串流解密器2443、三十二位串流解密器2444以及六十四位串流解密器2445的情况下,请参见图8、图9,为本技术五阶加密器144的加密流程示意图与五阶解密器244的解密流程示意图。前述步骤s202依据加密层级可以由步骤s2021-s2025之中的一个或者多个步骤替换,且所述多个步骤必须依序存在(例如:第四阶加密层级的情况下,步骤s202需替换成对应的步骤s2024,此时步骤s2021-s2023也必须一并纳入,因此,步骤s202在第四阶加密层级的情况下能替换成步骤s2021-s2024);步骤s204依据解密层级可以由步骤s2041-s2045之中的一个或者多个步骤替换,且所述多个步骤必须反向依序存在(例如:在第四阶层解密层级的情况下,步骤s204需替换成对应的步骤s2042,此时步骤s2043-s2045也必须一并纳入,因此,步骤s204能替换成步骤s2042-s2045),先前已描述过的步骤内容将不再赘述,先行叙明在此。在本实施例中,五阶加密器144所述的逻辑运算皆为xor;五阶解密器244所述的逻辑运算都为or(对应五阶加密器的逻辑运算)。在其它实施例中,前述的逻辑运算可以由and、nand等其它逻辑运算,在本技术中不予以限制;在本实施例中,加密线性反馈移位寄存器所选用的多个加密抽头位、与解密反馈移位寄存器所选用的多个解密抽头位及数量仅为一实施例,所述加密/解密抽头位能根据实际需求进行不同的选择、数量变化(例如:选择第一位、第七位做为加密/解密抽头位;选择第四位、第五位、第六位、第八位做为加密/解密抽头位;在位数更多的情况下可以选择第二位、第三十七位等),所述加密/解密抽头位的选择非属本技术所欲限制的范围。前述的解密抽头位将对应加密抽头位进行选择,以搭配进行解密。在本实施例中,所述第一八位串流加密器1441、所述十六位串流加密器1443、所述三十二位串流加密器1444的所述加密位抽头数量为两个;所述第二八位串流加密器1442、所述六十四位串流加密器1445的所述加密位抽头数量为四个;所述第一八位串流解密器2441、所述十六位串流解密器2443、所述三十二位串流解密器2444的所述解密位抽头数量为两个;所述第二八位串流解密器2442、所述六十四位串流解密器2445的所述解密位抽头数量为四个,先行叙明在此。在一个实施例中,前述的加密位抽头与解密位抽头的位数量为偶数个。

[0048]

以下说明步骤s2021-s2025,请一并参见图4、图8,为本技术五阶加密器的逻辑运算示意图、加密流程示意图。数据封包pk由五阶加密器144的第一八位串流加密器1441接

收,所述数据封包pk经由第一八位串流加密器1441加密并输出(步骤s2021)。

[0049]

在一个实施例中,第一八位串流加密器1441中的加密线性反馈移位寄存器1441l提取第二位a[2]与第七位a[7]进行逻辑运算后取得第一加密操作数,将所述数据封包pk与所述第一加密操作数经由加密逻辑闸1441g进行逻辑运算依序进行加密并由第一八位串流加密器1441输出;当加密层级设定器142设定为一阶加密时,此时第一八位串流加密器1441输出的为第一加密序列es1。

[0050]

经由第一八位串流加密器1441加密并输出的数据封包pk由第二八位串流加密器1442接收,第二八位串流加密器1442将接收到的所述数据封包pk加密并输出(步骤s2022)。

[0051]

在一个实施例中,第二八位串流加密器1442中的加密线性反馈移位寄存器1442l提取第二位b[2]、第五位b[5]、第六位b[6]、第七位b[7]进行逻辑运算后取得第二加密操作数,将所述数据封包pk与所述第二加密操作数经由加密逻辑闸1442g进行逻辑运算依序进行加密并由第二八位串流加密器1442输出;当加密层级设定器142设定为二阶加密时,此时第二八位串流加密器1442输出的为第二加密序列es2。

[0052]

经由第二八位串流加密器1442加密并输出的数据封包pk由十六位串流加密器1443接收,十六位串流加密器1443将接收到的所述数据封包pk加密并输出(步骤s2023)。

[0053]

在一个实施例中,十六位串流加密器1443中的加密线性反馈移位寄存器1443l提取第十四位c[14]、第十六位c[16]进行逻辑运算后取得第三加密操作数,将所述数据封包pk与所述第三加密操作数经由加密逻辑闸1443g进行逻辑运算依序进行加密并由十六位串流加密器1443输出;当加密层级设定器142设定为三阶加密时,此时十六位串流加密器1443输出的为第三加密序列es3。

[0054]

经由十六位串流加密器1443加密并输出的数据封包pk由三十二位串流加密器1444接收,三十二位串流加密器1444将接收到的所述数据封包pk加密并输出(步骤s2024)。

[0055]

在一个实施例中,三十二位串流加密器1444中的加密线性反馈移位寄存器1444l提取第三十位d[30]、第三十二位d[32]进行逻辑运算后取得第四加密操作数,将所述数据封包pk与所述第四加密操作数经由加密逻辑闸1444g进行逻辑运算依序进行加密并输出;当加密层级设定器142设定为四阶加密时,此时三十二位串流加密器1444输出的为第四加密序列es4。

[0056]

经由三十二位串流加密器1444加密并输出的数据封包pk由六十四位串流加密器1445接收,六十四位串流加密器1445将接收到的所述数据封包pk加密并输出(步骤s2025)。

[0057]

在一个实施例中,加密层级设定器142设定为五阶加密时,所述六十四位串流加密器1445中的加密线性反馈移位寄存器1445l提取第二位e[2]、第六十一位e[61]、第六十二位e[62]以及第六十四e[64]位进行逻辑运算后取得第五加密操作数,将所述数据封包pk与所述第五加密操作数经由加密逻辑闸1445g进行逻辑运算依序进行加密并输出,此时六十四位串流加密器1445输出的为第五加密序列es5。

[0058]

以下说明步骤s2041-s2045,请一并参见图6、图9,为本技术五阶解密器的逻辑运算示意图、解密流程示意图。第五加密序列es5由五阶解密器244的六十四位串流解密器2445接收,六十四位串流解密器2445解密所述第五加密序列es5并输出第五数据封包pk5(步骤s2041)。

[0059]

在一个实施例中,当解密层级为五阶时,六十四位串流解密器2445中的解密线性

反馈移位寄存器2445l提取第二位e[2]、第六十一位e[61]、第六十二位e[62]以及第六十四位e[64]进行逻辑运算后取得第五解密操作数,将所述第五加密序列es5与所述第五解密操作数经由解密逻辑闸2445g进行逻辑运算依序转换成第五数据封包pk5并输出至三十二位串流解密器2444。

[0060]

第五数据封包pk5由五阶解密器244的三十二位串流解密器2444接收,三十二位串流解密器2444解密所述第五数据封包pk5并输出第四数据封包pk4(步骤s2042)。

[0061]

在一个实施例中,当解密层级为五阶时,三十二位串流解密器2444中的解密线性反馈移位寄存器2444l提取第三十位d[30]以及第三十二位d[32]进行逻辑运算后取得第四解密操作数,将所述第五数据封包pk5与所述第四解密操作数经由解密逻辑闸2444g进行逻辑运算依序转换成第四数据封包pk4并输出至十六位串流解密器2443;当解密层级为四阶时,三十二位串流解密器2444所接收的为发送端装置10所输出的第四加密序列es4,此时三十二位串流解密器2444中的解密线性反馈移位寄存器2444l提取第三十位d[30]以及第三十二位d[32]进行逻辑运算后取得第四解密操作数,将所述第四加密序列es4与所述第四解密操作数经由解密逻辑闸2444g进行逻辑运算依序转换成第四数据封pk4包并输出至十六位串流解密器2443。

[0062]

第四数据封pk4包由五阶解密器244的十六位串流解密器2443接收,十六位串流解密器2443解密所述第四数据封包pk4并输出第三数据封包pk3(步骤s2043)。

[0063]

在一个实施例中,当解密层级为五阶或四阶时,十六位串流解密器2443中的解密线性反馈移位寄存器2443l提取第十四位c[14]、第十六位c[16]进行逻辑运算后取得第三解密操作数,将第四数据封包pk4与第三解密操作数经由解密逻辑闸2443g进行逻辑运算依序转换成第三数据封包pk3并输出至第二八位串流解密器2442;当解密层级为三阶时,十六位串流解密器2443所接收的为发送端装置10所输出的第三加密序列es3,此时十六位串流解密器2443中的解密线性反馈移位寄存器2443l提取第十四位c[14]以及第十六位c[16]进行逻辑运算后取得第三解密操作数,将第三加密序列es3与第三解密操作数经由解密逻辑闸2443g进行逻辑运算依序转换成第三数据封包pk3并输出至第二八位串流解密器2442。

[0064]

第三数据封包pk3由五阶解密器244的第二八位串流解密器2442接收,第二八位串流解密器2442解密第三数据封包pk3并输出第二数据封包pk2(步骤s2044)。

[0065]

在一个实施例中,当解密层级为五阶、四阶或三阶时,第二八位串流解密器2442中的解密线性反馈移位寄存器2442l提取第二位b[2]、第十三位b[13]、第十四位b[14]以及第十六位b[16]进行逻辑运算后取得第二解密操作数,将第三数据封包pk3与第二解密操作数经由解密逻辑闸2442g进行逻辑运算依序转换成第二数据封包pk2并输出至第一八位串流解密器2441;当解密层级为二阶时,第二八位串流解密器2442所接收的为发送端装置10所输出的第二加密序列es2,此时第二八位串流解密器2442中的解密线性反馈移位寄存器2442l提取第二位b[2]、第十三位b[13]、第十四位b[14]以及第十六位b[16]进行逻辑运算后取得第二解密操作数,将第二加密序列es2与第二解密操作数经由解密逻辑闸2442g进行逻辑运算依序转换成第二数据封包pk2并输出至第一八位串流解密器2441。

[0066]

第二数据封包pk2由五阶解密器244的第一八位串流解密器2441接收,第一八位串流解密器2441解密第二数据封包pk2并输出第一数据封包pk1(步骤s2045)。具体而言,当解密层级为五阶、四阶、三阶或二阶时,第一八位串流解密器2441中的解密线性反馈移位寄存

器2441l提取第二位a[2]以及第七位a[7]进行逻辑运算后取得第一解密操作数,将第二数据封包pk2与第一解密操作数经由解密逻辑闸2441g进行逻辑运算依序转换成第一数据封包pk1并输出至数据目标模块22,此时定义第一数据封包pk1为五阶解密器244输出的还原数据封包;当解密层级为一阶时,第一八位串流解密器2441所接收的为发送端装置10所输出的第一加密序列es1,此时第一八位串流解密器2441中的解密线性反馈移位寄存器2441l提取第二位a[2]以及第七位a[7]进行逻辑运算后取得第一解密操作数,将第一加密序列es1与所述第一解密操作数经由解密逻辑闸2441g进行逻辑运算依序转换成第一数据封包pk1并输出至数据目标模块22,此时定义所述第一数据封包pk1为所述五阶解密器244输出的还原数据封包。

[0067]

综上所述,比起现有技术,本技术可依据需要的加密程度切换加密层级,并且能经由一套硬件实现不同的加密层级防护。

[0068]

以上已将本技术做一详细说明,惟,以上所述者,仅为本技术之一较佳实施例而已,当不能以此限定本技术实施之范围,即凡依本技术权利要求所作之均等变化与修饰,皆应仍属本技术之专利涵盖范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。