一种抗功耗攻击的高性能ecc协处理器系统

技术领域

1.本发明属于密码电路设计技术领域,具体涉及一种抗功耗攻击的高性能ecc协处理器系统。

背景技术:

2.近年来,随着人工智能、5g和量子通信等信息技术的快速发展,信息安全正面临着严峻的挑战。非对称加密算法主要有dsa、rsa、ecc、ibc和elgamal等,而ecc比相同级别的rsa安全性更高,且密钥大小更小,与其他相比加密速度更快,节约能源、带宽和存储空间。其作为具有更高的安全强度的算法被广泛运用,同时对椭圆曲线密码系统的处理速度提出了更高的需求。ecc实现主要分为硬件实现和软件实现。现5g已成为全球研发的热点,这意味着实现密码体制需要更快的运算速度和更高的安全性能,面对这些需求,ecc硬件实现相比软件实现具有的发展前景与优势。ecc硬件实现可以用soc、asic和fpga等形式,soc实现不灵活,fpga实现可编程灵活性高、开发周期短、并行计算可编程效率高,而asic周期短速度快、适用于特定场合但成本高。因此,本文选用协处理器实现方式既满足通用性,又符合ecc的特定领域应用要求,且降低成本。在ecc协处理器的设计中,一方面标量乘作为ecc的核心要素,由于域宽大导致的循环迭代次数多和数据依赖强引发的流水延时长等问题,成为椭圆曲线密码算法实现的性能瓶颈;另一方面功耗攻击作为一种利用密码设备运行时泄露的功耗信息,对密钥进行破译的新兴攻击方法,对芯片安全构成了巨大的威胁。因此,设计一款抗dpa的高性能ecc协处理器系统显得尤其重要。

技术实现要素:

3.本发明提供了一种抗功耗攻击的高性能ecc协处理器系统,能够解决流水延时长以及功耗攻击的问题。

4.本发明采用的技术方案如下:

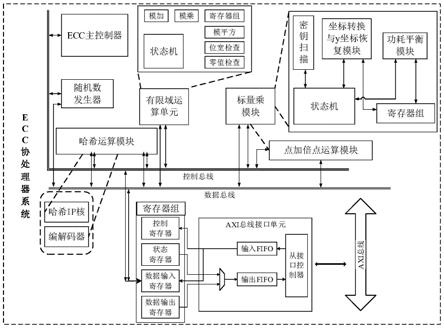

5.一种抗功耗攻击的高性能ecc协处理器系统,包括ecc主控器、有限域运算单元、标量乘模块、随机数发生器、哈希运算模块和寄存器组,所述标量乘模块包括点加倍点运算模块、密钥扫描、坐标转换与y坐标恢复模块和功耗平衡模块,分别负责执行协议层标量乘运算和点加运算,以及完成抗功耗攻击功能。

6.作为优选,ecc主控器控制着各模块协完成运算,并将状态信号反馈到寄存器组,通过调用有限域运算单元完成基本模运算后,通过控制总线和数据总线传输数据到标量乘模块中;标量乘模块接收到有限域运算单元处理后的数据后,完成以下几步:(1)密钥扫描模块检测到来自标量乘控制器的使能信号有效时,启动计数器,同时对私钥寄存器进行位扫描,记录当前已扫描的私钥比特数;其次,(2)点加倍点运算模块由状态机根据密钥扫描模块输出的密钥比特,确定每一轮运算中点加倍点模块的输入输出配置后,完成蒙哥马利阶梯算法对分支的点加倍点运算;同时,(3)坐标转换与y坐标恢复模块在蒙哥马利阶梯算法迭代运算开始前,将基点p从仿射坐标系转换到投影坐标系,同时对中间点和进行初始

化,当蒙哥马利阶梯算法迭代完成后,检测到标量乘模块输入信号有效时,标量乘模块将接收随机数发生器的输出作为随机z坐标,再恢复出在仿射坐标系下的坐标;然后,(4)功耗平衡模块利用行波动态差分逻辑技术实现电路的功耗平衡;随机数发生器用于产生标量乘模块运算中随机z坐标;哈希运算模块包括哈希ip核配置和编解码器,主要完成输入数据的预处理,将处理后的数据传入总线,再由ecc主控器调用,最终完成加解密功能和数字签名验签功能。

7.作为优选,ecc主控器根据ecdh密钥交换模式、ecdsa签名生成和认证模式、eces加密和解密模式三种模式控制各模块完成协议层运算,并将状态信号反馈到状态寄存器,使能相应的子状态机。

8.作为优选,有限域运算单元执行模加减、模乘、模平方和模逆等有限域层运算,用于实现曲线层点加模块运算,并受协议层运算控制器的调用。

9.作为优选,有限域运算单元基于模乘运算器执行模乘运算,所述模乘运算器包括有限域乘法核、累加及约简单元,采用三级流水线,分别在乘法器后、累加单元后以及数据拼接单元后插入第一、第二、第三级流水线,用于减小关键路径延时,提高数据吞吐率。

10.作为优选,将数据输入有限域运算单元后,通过有限域乘法核完成部分积分解及其运算,其后通过累加单元将部分积累加,最后完成约减运算输出计算结果;其中,有限域乘法核是基于多项式基运算的karatsub算法下乘法器的矩阵结构进行设计,利用mastrovito方法将运算产生的部分积重写成矩阵向量形式,然后再进行约减,简化计算步骤。

11.作为优选,将m位乘法器操作数作为两路输入量输入n个有限域乘法器(gf2 mul)的输入端进行乘法操作,gf2mul输出n个(m w-1)位长并储存至流水线寄存器中,每两个(m w-1)位长之间进行累加运算计算,输出(2m-1)位长的数据,最后通过约减单元将2m-1位长数据缩减为m位,最终输出m bit的结果。其中,流水线技术是通过在组合逻辑中插入寄存器来实现,为保持总电路具有最小的延时,因此均匀分割关键路径延,分别在乘法器后、累加单元后以及数据拼接单元后插入第一、第二、第三级流水线,用于提高数据吞吐率。

12.作为优选,模逆运算器使用了mita算法找出最优加法链,然后利用模乘运算器来构建模逆运算中所需的域乘法器,完成模逆运算器设计;其中,模逆运算电路使用了1个乘法器,4个平方器,2个m bit的二选一选择器mux1和mux2,两个寄存器x和t,din、x、t分别存储输入、乘法、平方结果;其中din和xsel位选信号分别连接至mux1的输入端进行乘法计算,mux1的输出端连接x模块的输入端以存储乘法结果,x模块的输出端连接至乘法器模块和mux2的输入端,分别进行模乘和模幂操作,等待寄存器t存储最后一次平方运算结果,然后读取数据。

13.作为优选,随机数发生器包含环路振荡器、亚稳态处理模块和233位lfsr,用于产生标量乘运算中随机z坐标。

14.作为优选,高性能ecc协处理器系统还包括axi总线接口单元,该单元负责ecc高性能协处理器系统电路与axi总线通信,完成明文/密文、密钥、指令的载入以及结果的输出,从接口控制器进行地址译码,通过输入fifo将指令和数据分别送到控制寄存器和数据输入寄存器,当运算完成后将状态寄存器内容和数据输出寄存器通过总线发送给主设备。

15.与现有技术相比,本发明公开的一种抗功耗攻击的高性能ecc协处理器系统,具有

以下有益效果:

16.(1)本发明具有低空间复杂度、简单、规则且易于模块化的优点,兼具性能和面积开销优势,且对不同域宽的椭圆曲线更具通用性,符合ecc的特定领域应用要求,降低设计成本。

17.(2)本发明通过在标量乘模块中添加功耗平衡模块,有效实现电路的功耗平衡,从而达到抗dpa的效果,增强系统安全性。

18.(3)本发明优化了有限域模乘单元和模逆单元,有限域是模乘单元是基于多项式基运算的karatsub算法下乘法器的矩阵结构进行设计,利用mastrovito方法将运算产生的部分积重写成矩阵向量形式,然后再进行约减,简化计算步骤;模逆单元利用了mita算法找出最优加法链,得到最高效的多项式因式分解方法,然后在此基础上进行设计;对比当前主流的模乘模逆电路,本发明拥有更高的计算性能和更低的面积消耗,满足椭圆曲线密码体制高性能设计要求。

附图说明

19.图1为本发明一个实施例的ecc协处理器系统的示意图;

20.图2为本发明一个实施例的ecc算法层次结构图;

21.图3为本发明一个实施例的有限域运算单元中模乘运算器硬件结构图;

22.图4为本发明一个实施例的有限域运算单元中模逆运算器硬件结构图;

23.图5为本发明一个实施例的ecc主控制器状态转移图;

24.图6为本发明一个实施例的ecc标量乘电路内部逻辑结构示意图;

25.图7为本发明一个实施例的随机数生成电路;

26.图8为本发明一个实施例的数字签名生成流程图;

27.图9为本发明一个实施例的数字签名验证流程图。

具体实施方式

28.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

29.如图1至图2所示,本发明公开了一种抗功耗攻击的高性能ecc协处理器系统,包括ecc主控器、有限域运算单元、标量乘模块、随机数发生器、哈希运算模块、寄存器组和axi总线接口单元。可以通过将所设计的协处理器挂载到已有基于rsic-v的soc总线上完成功能实现,也可以实现基于fpga进行原型验证,完成加解密和数字签名和验签功能。

30.ecc算法具有明显的层次结构,在整个体系中由底至顶依次调用执行,顶层为ecc协议层,完成密钥交换、数字签名或加解密功能;最底层是有限域运算层,包含模加、模减、模乘、模平方与模除等基本运算单元,依据特定的计算公式,它们能够实现不同坐标体系下的点群运算。标量乘运算控制层主要依据每比特密钥值对点群运算中的点加倍点进行循环调度,来完成整个标量乘运算。

31.ecc主控器主要实现三种功能模式,分别为ecdh密钥交换模式、ecdsa签名生成和

认证模式、eces加密和解密模式。eces和ecdh只涉及椭圆曲线运算,适合于小数据加密,ecdsa还涉及到图1中最底层有限域运算。其中,ecc主控器根据这三种功能模式控制各模块完成协议层运算,并将状态信号反馈到状态寄存器,使能相应的子状态机。有限域运算单元执行模加减、模乘、模平方和模逆等有限域层运算,用于实现点加和倍点模块运算,并受ecc主控器的调用。标量乘模块包括点加倍点运算模块、密钥扫描、坐标转换与y坐标恢复模块和功耗平衡模块,分别负责执行标量乘运算和点加别点运算以及完成抗dpa功能:(1)密钥扫描模块检测到来自标量乘控制器的使能信号有效时,启动计数器,同时对私钥寄存器进行位扫描,记录当前已扫描的私钥比特数;(2)点加倍点运算模块由状态机根据密钥扫描模块输出的密钥比特,确定每一轮运算中点加倍点模块的输入输出配置后,完成蒙哥马利阶梯算法某个分支的点加倍点运算;(3)坐标转换与y坐标恢复模块在蒙哥马利阶梯算法迭代运算开始前,将基点p从仿射坐标系转换到投影坐标系,同时对中间点和进行初始化,当蒙哥马利阶梯算法迭代完成后,检测到标量乘模块输入信号有效时,标量乘模块将接收随机数发生器的输出作为随机z坐标,再恢复出在仿射坐标系下的坐标;(4)功耗平衡模块利用wddl技术实现电路的功耗平衡,从而达到电路抗dpa的效果。随机数发生器用于产生标量乘模块中坐标转换与y坐标恢复模块所需要的随机z坐标。哈希运算模块包括哈希ip核配置和编解码器,主要完成输入数据的预处理,将处理后的数据传入总线,再由ecc主控器调用,最终完成加解密功能和数字签名验签功能。寄存器组包括数据输入寄存器,数据输出寄存器,控制状态寄存器和状态寄存器。axi总线接口单元负责ecc高性能协处理器系统电路与axi总线通信,完成明文/密文、密钥、指令的载入以及电路处理结果的输出,从接口控制器进行地址译码,通过输入fifo将指令和数据分别送到控制寄存器和数据输入寄存器,当运算完成后依次将状态寄存器内容和数据输出寄存器通过总线发送给主设备。

32.如图3所示,有限域运算单元包括模乘和模逆运算器,受ecc主控器的调用。其模乘运算器包括有限域乘法核、累加及约简单元。其中,有限域乘法核是基于多项式基运算的karatsub算法下乘法器的矩阵结构进行设计,利用mastrovito方法将运算产生的部分积重写成矩阵向量形式,然后再进行约减,简化计算步骤。同时,综合考虑延迟、频率和硬件代价,采用三级流水线用于减小关键路径延时,提高数据吞吐率,分别在乘法器后、累加单元后以及数据拼接单元后插入第一、第二、第三级流水线。数据输入后通过有限域乘法核完成部分积分解及其运算,其后通过累加单元将部分积累加,最后完成约减运算输出计算结果。在分段流水线操作中,本发明将m位乘法器操作数作为两路输入量输入n个有限域乘法器(gf2 mul)的输入端进行乘法操作,gf2mul输出n个(m w-1)位长并储存至流水线寄存器中,每两个(m w-1)位长之间进行累加运算计算,输出(2m-1)位长的数据,最后通过约减单元将2m-1位长数据缩减为m位,最终输出m bit的结果。其中,流水线技术是通过在组合逻辑中插入寄存器来实现,为保持总电路具有最小的延时,因此均匀分割关键路径延,分别在乘法器后、累加单元后以及数据拼接单元后插入第一、第二、第三级流水线,用于提高数据吞吐率。

33.有限域运算单元中模乘运算器ka算法具体为:

[0034][0035]

如图4所示,模逆运算器使用了mita算法找出最优加法链,利用图3中的乘法器来构建模逆运算中所需的域乘法器,其中,模逆运算电路使用了1个乘法器(high-speed fully parallel koa multiplier),4个平方器(exponentiation module),2个m bit的二选一选择器(mux1和mux2),两个寄存器(x和t),din、x、t分别存储输入、乘法、平方结果。其中din和xsel位选信号分别连接至mux1的输入端进行乘法计算,mux1的out端连接x模块的输入端以存储乘法结果,x模块的输出端连接至乘法器模块和mux2的输入端,分别进行模乘和模幂操作,等待寄存器t存储最后一次平方运算结果,然后读取数据。

[0036]

模逆运算器mita算法具体为:

[0037][0038]

如下表1所示,本发明的模逆单元与目前主流设计全并行乘法、qita算法、mita求逆器相比,运算性能高、面积消耗小,灵活性更高。

[0039]

表1在xilinxvirtex-4fpga上的高性能求逆器的性能对比图

[0040][0041][0042]

在面积延时积(atp)方面,对于域f2

233

,本文比qita求逆运算性能提高41.0%,比2

4-ita求逆提高了47.3%;比mita求逆提高了18.9%。在域f2

283

上,本文比2

4-ita求逆提高了61.3%;比mita求逆提高了20.8%。对于域f2

233

,本文比qita求逆面积资源消耗减少了31.6%,比2

4-ita求逆减少了16.8%;比mita求逆减少了7.5%。

[0043]

如图5所示,当执行ecdh工作模式时,ecc主控器首先进行数据初始化,当输入信号有效,进入init状态,将各子模块和子状态机等电路复位,随后进入pre_judge状态。在预判断状态下,判断基点坐标是否为零值,若为零则直接跳转到输出状态,否则回到idle状态等待具体的任务指令。ecdh、sig、ver_sig、encrypt、dencrypt五个子状态下,分别使能相应子状态机,调度电路中各模块完成密钥协商、数字签名、验证、加密和解密等功能。同一时刻只有一个子状态机在执行状态,完成协议运算后给出输出有效信号,主控制器进入output状态,将运算结果存入数据输出寄存器,下一周期回到空闲态。

[0044]

此时位于标量乘运算控制层的标量乘模块开始工作,如图6所示,利用蒙哥马利阶梯算法实现,状态机控制坐标转换、点加倍点运算、坐标恢复等模块的输入和工作状态,子模块调用有限域基本运算模块完成各自功能。标量乘电路输入包括私钥key、基点p的坐标(p

x

,py)以及输入有效信号in_valid,输出数据为标量乘运算结果q1的仿射坐标(q

1x

,q

1y

)以及输出有效信号out_valid。当in_valid为高电平,相应的输入数据保存到寄存器中,电路进行初始化配置,输入结束后标量乘电路开始工作。坐标转换模块负责在蒙哥马利阶梯算法迭代运算开始前,将基点p从仿射坐标系转换到投影坐标系,同时对中间点q1和q2进行初始化。当蒙哥马利阶梯算法迭代完成后,y坐标恢复模块负责恢复出q1在仿射坐标系下的坐标。

[0045]

如图7所示,随机数发生器包含环路振荡器、亚稳态处理模块和233位lfsr,用于产生标量乘运算中随机z坐标。其中,环路振荡器用于生成基于电路特性的随机比特,由于该电路输出电平不稳定,为避免影响lfsr的输出稳定性,增加亚稳态处理单元。对于单比特数据的亚稳态控制,采用两级d触发器完成,将环路振荡器产生的数据同步到ecc安全电路时钟域并消除亚稳态。通过将随机比特输入lfsr,提高输出伪随机序列的随机性,以保证随机数输出的有效性。当标量乘电路收到复位信号,下一周期将一个233比特数据作为lfsr的初

始值,并激活lfsr电路。当ecc标量乘电路输入信号有效时,标量乘电路接收该随机数生成模块的输出作为随机z坐标。

[0046]

如图8和图9所示,完成ecc协议层的加解密、签名验签、密钥交换功能,数字签名是通过调用哈希运算模块、和标量乘模块以及有限域运算单元来完成整个数字签名生成及验证流程。其中,在数字签名生成阶段,首先完成数字签名数据及曲线参数配置p、n、d、q,之后生成随机数k(1≤k≤n),再计算k

p

=(x1,y1),然后进行判断r=x1mod n是否为0,若为0则重新生成随机数,若不为0再对输入的消息m进行计算,最后输出消息m和签名(r,s);在数字签名验证阶段,首先接受签名信息m,r,s,然后判断s,r是否在[1,n-1]范围内,若不在则判断签名不合法;否则则根据e=h(m),u=(e r)mod n,(x2,y2)=sg-uq,r1=x2mod n计算r1的值,将计算的结果r1和r进行比较,判断是否相等,若相等则签名合法,否则签名不合法。

[0047]

通过axi总线接口单元将ecc高性能协处理器系统电路与axi总线进行通信,最终完成协处理器系统。完成明文/密文、密钥、指令的载入以及电路处理结果的输出,从接口控制器进行地址译码,通过输入fifo将指令和数据分别送到控制寄存器和数据输入寄存器,当运算完成后依次将状态寄存器内容和数据输出寄存器通过总线发送给主设备。

[0048]

上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,举凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。