技术特征:

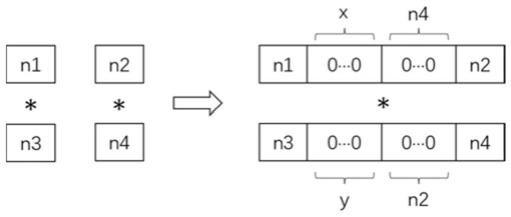

1.一种基于dsp的混合位宽加速器,其特征在于,包括第一信号输入端、第二信号输入端、第三信号输入端、第四信号输入端、第一移位单元、第一加法器、第一选择器、第三选择器、第二移位单元、第二加法器、第二选择器、第四选择器和dsp;第一信号输入端和第二信号输入端分别用于接收被乘数,第三信号输入端和第四信号输入端分别用于接收乘数;当并行度为1时,第一信号输入端的被乘数直接经第一选择器选择进入dsp,第三信号输入端的乘数直接经第二选择器选择进入dsp,被乘数和乘数在dsp中进行乘法累加运算;当并行度大于1时,第一信号输入端的被乘数在第一移位单元中进行移位操作,移位操作后进入第一加法器与第二信号输入端的被乘数进行加法运算,加法运算后得到的被乘数进入第三选择器,经第三选择器选择进入第一加法器,继续与移位操作后的第一信号输入端的被乘数进行加法运算,直至所有被乘数均完成加法运算;所有被乘数均完成加法运算之后,第一加法器得到的高位宽被乘数经第一选择器选择进入dsp;第三信号输入端的乘数在第二移位单元中进行移位操作,移位操作后进入第二加法器与第四信号输入端的乘数进行加法运算,加法运算后得到的乘数进入第四选择器,经第四选择器选择进入第二加法器,继续与移位操作后的第三信号输入端的乘数进行加法运算,直至所有乘数均完成加法运算;所有乘数均完成加法运算之后,第二加法器得到的高位宽乘数经第二选择器选择进入dsp;进入dsp的高位宽被乘数和高位宽乘数在dsp中进行乘法累加运算。2.根据权利要求1所述的基于dsp的混合位宽加速器,其特征在于,当并行度大于1时,进行移位操作时的移位数计算方法为:设第一信号输入端的被乘数位宽为n1,经第三选择器进入第一加法器的乘数位宽为n2,第三信号输入端的乘数位宽为n3,经第四选择器进入第二加法器的乘数位宽为n4;n1和n3的移位数分别为x n4和y n2,其中x、y、n1、n2、n3和n4满足如下约束:x y 2(n2 n4)≥max(n1 x n4 n2 n4,n3 y n2 n4 n2) 1

ꢀꢀꢀꢀꢀ

(1)。3.根据权利要求1所述的基于dsp的混合位宽加速器,其特征在于,在第一加法器得到的高位宽被乘数中的各被乘数之前插入冗余位宽。4.根据权利要求1所述的基于dsp的混合位宽加速器,其特征在于,冗余位宽的位数计算方法为:设每个被乘数前插入冗余位宽的位数为q,则q的计算公式如式(6)其中,m为dsp的最高位宽,d为并行度,mult1和mult2分别为第一加法器得到的高位宽被乘数和第二加法器得到的高位宽乘数的位宽。5.根据权利要求4所述的基于dsp的混合位宽加速器,其特征在于,并行度为2时,设第一信号输入端的被乘数位宽为n1,经第三选择器进入第一加法器的乘数位宽为n2,第三信号输入端的乘数位宽为n3,经第四选择器进入第二加法器的乘数位宽为n4;设冗余位宽可支持的最大累加次数为num_acc,计算公式如式(3),max_w1为高位部分积、中间部分积和低位部分积的最大位宽,计算公式如式(4),其中mp_w为中间部分积的位宽,计算公式如式(5);

max_w1=max(n1 n3,n2 n4,mp_w)

ꢀꢀꢀꢀꢀ

(4)mp_w=max(n1 n4 x n4 n2,n2 n3 y n2 n4) 1-min(x n2 n4,y n2 n4)

ꢀꢀꢀꢀꢀꢀ

(5)其中,x、y、n1、n2、n3和n4满足如下约束:x y 2(n2 n4)≥max(n1 x n4 n2 n4,n3 y n2 n4 n2) 1

ꢀꢀꢀꢀ

(1)。6.根据权利要求5所述的基于dsp的混合位宽加速器,其特征在于,并行度大于2时,将多组乘法先合并为两组乘法,然后利用处理并行度为2的方法计算最大累加次数。7.根据权利要求1所述的基于dsp的混合位宽加速器,其特征在于,当并行度大于1且为固定乘数时,第一信号输入端的被乘数在第一移位单元中进行移位操作,移位操作后进入第一加法器与第二信号输入端的被乘数进行加法运算,加法运算后得到的被乘数进入第三选择器,经第三选择器选择进入第一加法器,继续与移位操作后的第一信号输入端的被乘数进行加法运算,直至所有被乘数均完成加法运算;所有被乘数均完成加法运算之后,第一加法器得到的高位宽被乘数经第一选择器选择进入dsp;第三信号输入端的固定乘数直接经第二选择器选择进入dsp;进入dsp的高位宽被乘数和固定乘数在dsp中进行乘法累加运算。8.根据权利要求7所述的基于dsp的混合位宽加速器,其特征在于,移位操作具体是:在被乘数之后插入乘数位宽个0。9.根据权利要求7所述的基于dsp的混合位宽加速器,其特征在于,在第一加法器得到的高位宽被乘数中的各被乘数之前插入冗余位宽;设并行度为d,固定乘数位宽为n,冗余位宽能支持的最大累加次数num_acc的计算公式如式(9);其中max_w2表示被乘数中最大位宽与乘数位宽之和;q是每个被乘数前插入冗余位宽的位数,计算公式如式(10),其中n

i

表示被乘数位宽;被乘数位宽;10.一种基于dsp的混合位宽融合计算方法,其特征在于,基于权利要求1所述的加速器,当并行度为1时,第一信号输入端的被乘数直接经第一选择器选择进入dsp,第三信号输入端的乘数直接经第二选择器选择进入dsp,被乘数和乘数在dsp中进行乘法累加运算;当并行度大于1时,第一信号输入端的被乘数在第一移位单元中进行移位操作,移位操作后进入第一加法器与第二信号输入端的被乘数进行加法运算,加法运算后得到的被乘数进入第三选择器,经第三选择器选择进入第一加法器,继续与移位操作后的第一信号输入端的被乘数进行加法运算,直至所有被乘数均完成加法运算;所有被乘数均完成加法运算之后,第一加法器得到的高位宽被乘数经第一选择器选择进入dsp;第三信号输入端的乘数在第二移位单元中进行移位操作,移位操作后进入第二加法器与第四信号输入端的乘数进行加法运算,加法运算后得到的乘数进入第四选择器,经第四选择器选择进入第二加法器,继续与移位操作后的第三信号输入端的乘数进行加法运算,直至所有乘数均完成加法运

算;所有乘数均完成加法运算之后,第二加法器得到的高位宽乘数经第二选择器选择进入dsp;进入dsp的高位宽被乘数和高位宽乘数在dsp中进行乘法累加运算。

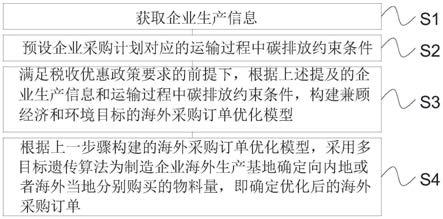

技术总结

本发明提供一种基于高位宽DSP的混合位宽加速器及融合计算方法,以DSP作为主要计算单元,对乘数和被乘数分别连接,并分别进行移位即插入不同的隔离位宽,可以实现多组任意低位宽乘累加运算。本发明加速器支持任意乘法并行度,最大化DSP计算性能;支持任意位宽的乘数和被乘数,支持乘数固定和不固定两种情况,通用性更好,适用范围广。适用范围广。

技术研发人员:杨晨 王佳兴 席嘉蔚

受保护的技术使用者:西安交通大学

技术研发日:2021.12.24

技术公布日:2022/3/25

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。