1.本发明涉及一种三维(3d)存储器元件。

背景技术:

2.传统平面型存储器单元通常经由改良制作工艺技术、电路设计、程序演算法以及制作过程的改良等比例缩小尺寸。然而在存储器单元的特征尺寸缩小接近至一极限时,制备平面型存储器元件的制作工艺技术即渐渐产生难度并使成本增加,最终使平面型存储器单元的存储容量或密度达到一上限。

3.一般而言3d存储器架构可处理前述平面型存储器单元所面临的种种上限瓶颈,其中3d存储器架构通常包含一存储器阵列以即周边元件用来控制传送至存储器阵列以及接受由存储器阵列所回传的信号。

技术实现要素:

4.本发明一实施例揭露一种3d存储器元件,其主要包含一通道结构沿着一第一方向延伸以及一控制栅极结构沿着一第二方向延伸并环绕通道结构,其中通道结构包含一负电容绝缘层、一电荷存储结构以及一通道层。

5.依据本发明一实施例,负电容绝缘层包含二氧化锆铪(hfzro2)。

6.依据本发明一实施例,其中该电荷存储结构包含一阻挡层、一电荷存储层以及一隧穿层。

7.依据本发明一实施例,其中该阻挡层包含氧化硅。

8.依据本发明一实施例,其中该电荷存储层包含氮化硅。

9.依据本发明一实施例,其中该隧穿层包含氧化硅。

10.依据本发明一实施例,其中该控制栅极结构包含多个控制栅极层沿着该第二方向延伸于该通道结构两侧。

11.依据本发明一实施例,另包含一下选择栅极设于该控制栅极结构下方并环绕该通道结构。

12.依据本发明一实施例,另包含一上选择栅极设于该控制栅极结构上方并环绕该通道结构。

附图说明

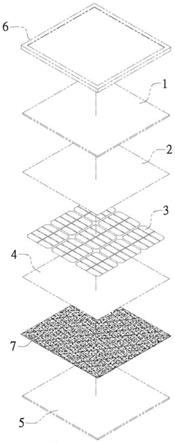

13.图1为本发明一实施例的一3d存储器元件的结构示意图;

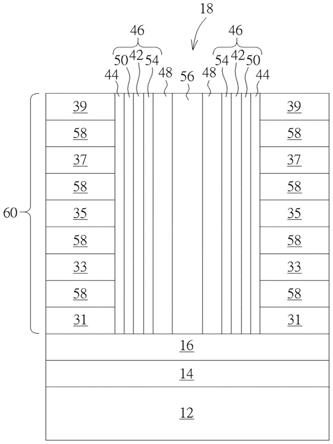

14.图2至图5为本发明一实施例制作图1中通道结构的方法示意图;

15.图6为本发明一实施例的一3d存储器元件的结构示意图。

16.主要元件符号说明

17.12:基底

18.14:源极线

19.16:下选择栅极

20.18:通道结构

21.20:控制栅极结构

22.22:上选择栅极

23.24:位线

24.26:金属内连线

25.28:接触插塞

26.30:介电交替堆叠结构

27.31:介电层

28.32:介电层

29.33:介电层

30.34:介电层

31.35:介电层

32.36:介电层

33.37:介电层

34.38:介电层

35.39:介电层

36.42:通道开口

37.44:负电容绝缘层

38.46:电荷存储结构

39.48:通道层

40.50:阻挡层

41.52:电荷存储层

42.54:隧穿层

43.56:绝缘层

44.58:控制栅极层

45.60:控制栅极结构

具体实施方式

46.请参照图1至图5,图1为本发明一实施例的一3d存储器元件的结构示意图,而图2至图5则为本发明一实施例制作图1中通道结构的方法示意图。如图1至图5所示,3d存储器元件主要包含一通道结构18沿着一第一方向例如y方向延伸于一基底12上,一控制栅极结构20沿着一第二方向例如x方向延伸并环绕通道结构18,一源极线14以及下选择栅极16设于控制栅极结构20下方,一上选择栅极22、位线24以及上层的金属内连线26设于控制栅极结构20上方以及多个接触插塞28连接源极线14、下选择栅极16以及上层的金属内连线26。

47.在本实施例中,形成基底12的步骤可包含形成一底层基底,形成至少一周边电路于基底上,形成至少一内连线结构电连接该至少一周边电路,再形成一外延基底于至少一周边电路上。底层基底可包含任何半导体材料,如硅(例如单晶硅或多晶硅)、锗化硅(sige)、砷化镓(gaas)、锗(ge)、硅覆绝缘(soi)基底、锗覆绝缘(goi)基底或其组合。在一些

实施例中,形成底层基底的方法可包含薄化制作工艺,其又细部包含研磨(grinding)、干/湿蚀刻制作工艺、化学机械研磨(cmp)或其组合。

48.一个或以上的周边电路可包含任何数字、模拟、以及/或混合信号周边电路,例如但不局限于页面缓冲器、解码器以及锁存器等。在一些实施例中,一个或以上内连线结构可包含任何适用的导电结构例如但不局限于接触、单层/多层接触洞、导电层、插塞等等。

49.外延基底可利用沉积制作工艺形成于周边电路上,其中沉积制作工艺可包含但不局限于例如化学气相沉积(cvd)、物理气相沉积(pvd)、原子层沉积(ald)或其组合。外延基底可为一单层基底或多层基底,例如可包含单晶硅单层基底、多晶硅单层基底、或由多晶硅以及金属所构成的多层基底等。

50.然后如图2所示,形成一介电交替堆叠结构30于基底12上。在一些实施例中,多个介电层31、32、33、34、35、36、37、38、39可形成于基底12上构成介电交替堆叠结构30。在一些实施例中,奇数层的介电层31、33、35、37、39材料较佳不同于偶数层的介电层32、34、36、38材料,各介电层31、32、33、34、35、36、37、38、39可包含介电材料例如但不局限于氧化硅、氮化硅、氮氧化硅或其组合。本实施例中奇数层的介电层31、33、35、37、39较佳包含氧化硅而偶数层的介电层32、34、36、38则包含氮化硅,但不局限于此顺序。介电交替堆叠结构30可由一道或多道薄膜沉积制作工艺所形成,例如化学气相沉积(cvd)、物理气相沉积(pvd)、原子层沉积(ald)或其任何组合。另外本实施例介电交替堆叠结构30中的介电层虽以九层为例,但其层数均不局限于此而可视产品需求调整。

51.然后形成多个通道结构18于介电交替堆叠结构30内,其中各通道结构18可沿着垂直方向延伸并贯穿介电交替堆叠结构30。如图3所示,在一些实施例中,形成通道结构18的方式包括利用例如湿蚀刻以及/或干蚀刻形成一通道开口42沿着垂直方向穿过介电交替堆叠结构30。

52.接着如图4所示,依序形成一负电容绝缘层44、一电荷存储结构46以及一通道层48于通道开口42内。在本实施例中,负电容绝缘层44较佳可包含但不局限于二氧化锆铪(hafnium zirconium oxide,hfzro2)、锆钛酸铅(lead zirconate titanate,pbzrtio3,pzt)、铁酸铋(bismuth ferrite,bifeo3)、聚偏二氟乙烯-三氟乙烯共聚物(p(vdf-trfe))或其组合。在一实施例中负电容绝缘层44可由一道或多道薄膜沉积制作工艺所形成例如但不局限于原子层沉积制作工艺、外延成长制作工艺或旋转涂布(spin coating)制作工艺。

53.电荷存储结构46可包含介电材料例如但不局限于氧化硅、氮化硅、氮氧化硅(oxide-nitride-oxide,ono)或其组合。从细部来看本实施例的电荷存储结构46包含一阻挡层50、一电荷存储层52以及一隧穿层54,其中阻挡层50包含氧化硅,电荷存储层52包含氮化硅,隧穿层54包含氧化硅,但均不局限于此。通道层48可包含半导体材料例如但不局限于硅、锗或其组合。

54.之后如图5所示,可先形成一绝缘层56填满通道开口42使绝缘层56、通道层48、电荷存储结构46以及负电容绝缘层44形成通道结构18。随后利用蚀刻去除介电交替堆叠结构30中偶数层例如包含氮化硅的介电层32、34、36、38,再进行一道或多道沉积制作工艺形成导电层于原本偶数层介电层32、34、36、38的位置成为控制栅极层58,其中控制栅极层58与单数层的介电层31、33、35、37、39可一同构成一控制栅极结构60。在本实施例中,绝缘层56可包含但不局限于氧化硅,控制栅极层58则可包含导电材料例如但不局限于钨(w)、钴

(co)、铜(cu)、铝(al)、多晶硅、掺杂硅、硅化物或其任何组合。

55.需注意的是,本实施例虽于通道层48形成后再另外形成一绝缘层56填满通道开口42,但不局限于此,如图6所示,依据本发明其他实施例又可在形成通道层48时便直接填满通道开口42,如此即可于通道层48形成后省略另外形成绝缘层56的步骤,此变化型也属本发明所涵盖的范围。此外从剖面来看通道层48、电荷存储结构46以及负电容绝缘层44虽分别设于绝缘层56两侧,但从立体角度来看通道层48、电荷存储结构46以及负电容绝缘层44实际上是从里到外环绕设于中心的绝缘层56。

56.随后可于通道结构18完成后依据制作工艺需求进行后续元件例如上选择栅极22、位线24、金属内连线26以及接触插塞28的制作工艺。在本实施例中上选择栅极22、位线24、金属内连线26以及接触插塞28等元件可包含导电材料例如但不局限于钨(w)、钴(co)、铜(cu)、铝(al)、多晶硅、掺杂硅、硅化物或其任何组合。

57.综上所述,本发明较佳于三维反及(3d nand)存储器元件中的控制栅极结构及通道层之间额外形成一负电容绝缘层,并通过此负电容绝缘层来达到电压放大(voltage amplification)以及功率降低(power reduction)的效果进而提升元件效能。

58.以上所述仅为本发明的优选实施例,凡依本发明权利要求所做的均等变化与修饰,都应属本发明的涵盖范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。