1.本实用新型实施例涉及半导体技术领域,尤其涉及一种扇出型封装结构和射频模组。

背景技术:

2.随着芯片技术的快速发展,人们对芯片的集成度要求越来越高,尺寸要求越来越小。

3.射频模组的组成芯片包含滤波器,硅基半导体(silicon on insulator,soi)芯片(例如,天线开关,低噪声放大器等)。目前,市面上针对此类芯片的封装多为2d的晶圆级封装,其所对应的射频模组占比空间较大,无法满足高集成度和小型化的要求。

技术实现要素:

4.本实用新型实施例提供一种扇出型封装结构和射频模组,以实现小尺寸、高集成度的封装结构。

5.第一方面,本实用新型实施例提供了一种扇出型封装结构,包括:第一晶圆、第二晶圆和重布线层,所述第一晶圆和所述第二晶圆均包括相对设置的第一表面和第二表面;

6.所述重布线层包括设置于所述第一晶圆第一表面的第一绝缘层和设置于所述第二晶圆第一表面的第二绝缘层,所述第一晶圆的第一表面以扇出方式与所述第二晶圆的第二表面结合为一体,且所述第一晶圆与所述第二晶圆之间通过所述第一绝缘层形成密封空腔;

7.所述第一晶圆通过贯穿所述第一绝缘层、所述第二晶圆和所述第二绝缘层的通孔实现电性连接。

8.可选地,所述第一晶圆上设置有第一焊垫,所述第二晶圆上设置有第二焊垫,所述第一绝缘层包括至少一个暴露出所述第一焊垫的第一通孔,所述第二绝缘层包括至少一个暴露出所述第二焊垫的第二通孔和至少一个暴露出所述第二晶圆的第三通孔,所述第一通孔和所述第三通孔贯穿所述第二晶圆形成第四通孔;

9.所述第四通孔和所述第二通孔内填充有导电材料,并通过金属走线实现第一焊垫和所述第二焊垫的电性连接。

10.可选地,所述重布线层还包括设置于所述第二绝缘层远离所述第二晶圆一侧的第三绝缘层,所述第三绝缘层覆盖所述金属走线。

11.可选地,还包括金属凸点;

12.所述金属凸点设置于所述第三绝缘层远离所述第二绝缘层一侧,并通过导电柱与所述金属走线连接。

13.可选地,所述第一绝缘层覆盖所述第一焊垫,所述第二绝缘层覆盖所述第二焊垫。

14.可选地,还包括塑封结构,所述塑封结构包覆在所述第一晶圆的第二表面和侧表面。

15.可选地,所述塑封结构包括相对设置的顶面和底面,所述塑封结构的底面与所述第一晶圆的第二表面接触,所述塑封结构的顶面与所述第一绝缘层远离所述第一晶圆一侧的表面平齐,并与所述第二晶圆的第二表面接触。

16.可选地,所述第一晶圆包括声表滤波器晶圆。

17.可选地,所述第一晶圆的基材材料包括钽酸锂或铌酸锂,所述第二晶圆的基材材料包括硅。

18.第二方面,本实用新型实施例还提供了一种射频模组,该射频模组包括本实用新型任意实施例所提供的扇出型封装结构。

19.本实用新型实施例提供一种扇出型封装结构和射频模组,该扇出型封装结构包括第一晶圆、第二晶圆和重布线层,第一晶圆和第二晶圆均包括相对设置的第一表面和第二表面;重布线层包括设置于第一晶圆第一表面的第一绝缘层和设置于第二晶圆第一表面的第二绝缘层,第一晶圆的第一表面通过晶圆键合,并以扇出方式与第二晶圆的第二表面结合为一体,且第一晶圆与第二晶圆之间通过第一绝缘层形成密封空腔;第一晶圆通过贯穿第一绝缘层、第二晶圆和第二绝缘层的通孔实现电性连接。相对与现有技术,本实用新型实施例提供的技术方案通过扇出方式将第一晶圆与第二晶圆键合在一起形成扇出型三维晶圆,使得晶圆的尺寸灵活性较高,可以使适应不同尺寸的晶圆键合,大大提高了晶圆封装的集成度,能够减小晶圆封装的占用面积,从而提升了晶圆的利用率。

附图说明

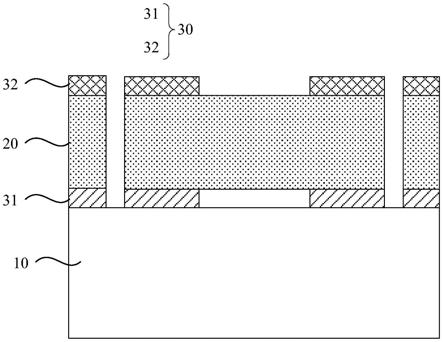

20.图1为本实用新型实施例提供的一种扇出型封装结构的结构示意图;

21.图2为本实用新型实施例提供的另一种扇出型封装结构的结构示意图;

22.图3为本实用新型实施例提供的另一种扇出型封装结构的结构示意图;

23.图4为本实用新型实施例提供的另一种扇出型封装结构的俯视图;

24.图5为本实用新型实施例提供的另一种扇出型封装结构的结构示意图;

25.图6为本实用新型实施例提供的另一种扇出型封装结构的结构示意图;

26.图7-图17为本实用新型实施例提供的一种扇出型封装结构的制作流程对应的结构示意图。

具体实施方式

27.下面结合附图和实施例对本实用新型作进一步的详细说明。可以理解的是,此处所描述的具体实施例仅仅用于解释本实用新型,而非对本实用新型的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与本实用新型相关的部分而非全部结构。

28.如背景技术所述,现有的射频模组的组成芯片的封装多为2d的晶圆级封装。射频模组的组成芯片通常包括滤波器和soi芯片,其中滤波器可以为声表滤波器。声表滤波器工作原理是声波在芯片表面传输,因此声表滤波器的封装形式要求其叉指换能器表面必须保证足够的空腔,否则影响信号传输。现有技术通常是在滤波器芯片的叉指换能器上形成密封的空腔,再依次贴装在射频模组基板上,形成2d封装结构,现有技术的方案对于模组的尺寸要求很大,不利于芯片往高集成度及小尺寸的发展。

29.针对上述问题,本实用新型实施例提供了一种扇出型封装结构,通过晶圆与晶圆

直接键合的方式进行芯片封装,以实现芯片的高集成度及小尺寸。图1为本实用新型实施例提供的一种扇出型封装结构的结构示意图,参考图1,本实用新型实施例提供的扇出型封装结构包括第一晶圆10、第二晶圆20和重布线层30,第一晶圆10和第二晶圆20均包括相对设置的第一表面和第二表面;

30.重布线层30包括设置于第一晶圆10第一表面的第一绝缘层31和设置于第二晶圆20第一表面的第二绝缘层32,第一晶圆10的第一表面以扇出方式与第二晶圆20的第二表面结合为一体,且第一晶圆10与第二晶圆20之间通过第一绝缘层31形成密封空腔;

31.第一晶圆10通过贯穿第一绝缘层31、第二晶圆20和第二绝缘层32的通孔实现电性连接。

32.具体地,第一晶圆10可以为滤波器晶圆,第二晶圆20可以为soi晶圆,第一晶圆10以扇出的方式与第二晶圆20直接键合在一起,形成更大尺寸的三维晶圆。在本实施例中,扇出型封装结构还包括重布线层30,重布线层30上设置有多个贯穿第二晶圆20的通孔,该通孔用于通过重布线工艺实现第一晶圆10与第二晶圆20的电路连接。

33.第一晶圆10的第一表面可以为正面,第一晶圆10的第二表面可以为背面;第二晶圆20的第一表面为正面,第二晶圆20的第二表面为背面。重布线层30包括设置于第一晶圆10第一表面的第一绝缘层31和设置于第二晶圆20第一表面的第二绝缘层32。通过将第一晶圆10的第一表面与第二晶圆20的第二表面键合在一起,也即在第二晶圆20的背面以扇出方式键合第一晶圆10。在本实施例中,第一晶圆10和第二晶圆20可以采用贴装方式键合在一起,例如,通过键合胶进行键合。重布线层30还包括未贯穿第二晶圆20的通孔,以便第一晶圆10的第一表面和第二晶圆20的第二表面之间通过第一绝缘31上未贯穿第二晶圆20的通孔形成密封空腔,以保证声波在无干扰情况下传播。需要说明的是,本实用新型实施例所提到的贯穿第二晶圆20的通孔指的是该通孔暴露出第二晶圆20,并未刻蚀第二晶圆20所形成的通孔。

34.本实用新型实施例提供的扇出型封装结构,包括第一晶圆、第二晶圆和重布线层,第一晶圆和第二晶圆均包括相对设置的第一表面和第二表面;重布线层包括设置于第一晶圆第一表面的第一绝缘层和设置于第二晶圆第一表面的第二绝缘层,第一晶圆的第一表面通过晶圆键合,并以扇出方式与第二晶圆的第二表面结合为一体,且第一晶圆与第二晶圆之间通过第一绝缘层形成密封空腔;第一晶圆通过贯穿第一绝缘层、第二晶圆和第二绝缘层的通孔实现电性连接。相对与现有技术,本实用新型实施例提供的技术方案通过扇出方式将第一晶圆与第二晶圆键合在一起形成扇出型三维晶圆,使得晶圆的尺寸灵活性较高,可以使适应不同尺寸的晶圆键合,大大提高了晶圆封装的集成度,能够减小晶圆封装的占用面积,从而提升了晶圆的利用率。

35.在本实施例中,第一晶圆10包括声表滤波器晶圆,其基材材料包括钽酸锂或铌酸锂,第二晶圆20的基材材料包括硅。小尺寸的钽酸锂或铌酸锂基材的第一晶圆10以扇出方式与硅基材的第二晶圆20重构成更大尺寸的三维晶圆,打破了以钽酸锂或铌酸锂为基材的第一晶圆10的小尺寸限制,大大提升了晶圆的生产效率,并有利于降低生产成本。

36.可选地,图2为本实用新型实施例提供的另一种扇出型封装结构的结构示意图,参考图2,在上述技术方案的基础上,第一晶圆10上设置有第一焊垫101,第二晶圆20上设置有第二焊垫201,第一绝缘层31包括至少一个暴露出第一焊垫101的第一通孔311,第二绝缘层

32包括至少一个暴露出第二焊垫201的第二通孔321和至少一个暴露出第二晶圆20的第三通孔322,第一通孔311和第三通孔322贯穿第二晶圆20形成第四通孔33,第四通孔33和第二通孔321内填充有导电材料,并通过金属走线40实现第一焊垫101和第二焊垫201的电性连接。

37.具体地,位于第一绝缘层31上的第一通孔311与位于第二绝缘层32上的第三通孔322相互贯通第二晶圆20,并整体形成第四通孔33。第一焊垫101位于第一晶圆10的第一表面,第二焊垫201位于第二晶圆20的第一表面。第一焊垫101和第二焊垫201通过第四通孔33实现电连接,其中,第四通孔33中填充有导电材料。在本实施例中,导电材料可以填满第四通孔33,也可以沿第四通孔33的内壁涂覆,并在导电材料的外层设置一层保护层(如,绿油)。第二绝缘层32上方设置有金属走线40,金属走线40沿第二绝缘层32的表面布置,并与第四通孔33和第二通孔321内的导电材料连接,实现第一焊垫101和第二焊垫201的电性连接,从而实现第一晶圆10与第二晶圆20上的电路连接。

38.可选地,图3为本实用新型实施例提供的另一种扇出型封装结构的结构示意图,参考图3,在上述技术方案的基础上,重布线层30还包括设置于第二绝缘层32远离第二晶圆20一侧的第三绝缘层34,第三绝缘层34覆盖金属走线40。其中,第三绝缘层34主要起到保护作用,防止外界环境对金属走线40的侵蚀。

39.可选地,图4为本实用新型实施例提供的另一种扇出型封装结构的俯视图,图3为图4所示扇出型封装结构沿切割线aa’的剖面图,参考图3和图4,该扇出型封装结构还包括金属凸点50;金属凸点50设置于第三绝缘层34远离第二绝缘层32一侧,并通过导电柱60与金属走线40连接。其中,第三绝缘层34上设置有开孔,在开孔内形成导电柱60,用于引出金属走线40。金属凸点50设置于导电柱60上,并裸露在第三绝缘层34上,用于实现与其他器件的电连接。

40.可选地,图5为本实用新型实施例提供的另一种扇出型封装结构的结构示意图,参考图5,在上述技术方案的基础上,沿晶圆的厚度方向,第一焊垫101的表面高出第一晶圆10的第一表面,第二焊垫201同样高出第二晶圆20的第一表面,便于焊接。第一绝缘层31覆盖第一焊垫101,第二绝缘层32覆盖第二焊垫201,增大了第一绝缘层31与第一焊垫101之间的接触面积,以及增大了第二绝缘层32与第二焊垫201之间的接触面积,有利于提高第一绝缘层31与第一晶圆10之间的粘附力,以及第二绝缘层32与第二晶圆20之间的粘附力,从而有利于提高第一晶圆10和第二晶圆20之间的键合可靠性。

41.可选地,图6为本实用新型实施例提供的另一种扇出型封装结构的结构示意图,参考图6,在上述技术方案的基础上,该扇出型封装结构还包括塑封结构70,塑封结构70包覆在第一晶圆10的第二表面和侧表面。

42.具体地,塑封结构70包括相对设置的顶面和底面,塑封结构70的底面与第一晶圆10的第二表面接触,塑封结构70的顶面与第一绝缘层31远离第一晶圆10一侧的表面平齐,并与第二晶圆20的第二表面接触。其中,塑封结构70的顶面成开口状,并与第一绝缘层31远离第一晶圆10一侧的表面平齐,也即与第二晶圆20的第二表面抵接,且塑封结构70的地面与第一晶圆10的第二表面抵接。换句话说,塑封结构70包裹第一晶圆10的第二表面和侧面,结合第一绝缘层31,塑封结构70能够完全包裹住第一晶圆10,为第一晶圆10提供保护。

43.可选地,图7-图17为本实用新型实施例提供的一种扇出型封装结构的制作流程对

应的结构示意图,在上述各技术方案的基础上,参考图7-图17,本实用新型实施例提供的扇出型封装结构的具体制作流程如下:

44.如图7-图10所示,提供一片第一晶圆10,其中,第一晶圆10为声表滤波器晶圆,第一晶圆10的第一表面设置有第一焊垫101。在第一晶圆10的第一表面形成第一绝缘层31,第一绝缘层31覆盖第一晶圆10的第一表面。之后在第一绝缘层31上涂覆一层光阻层80,在光照的条件下进行曝光显影,以形成掩膜图案,按照掩膜图案刻蚀第一绝缘层31,形成第一通孔311,并刻蚀掉光阻层80。然后进行第一晶圆10的切割制程,形成单颗第一晶圆10。

45.如图11-图13所示,提供一片第二晶圆20,第二晶圆10为soi(如,集成电感电容、天线开关,低噪声放大器等)晶圆,第二晶圆20的第一表面设置有第二焊垫201。在第二晶圆20的第一表面键合第一载板41,并研磨减薄第二晶圆20的第二表面,采用硅穿孔工艺刻蚀出贯穿第二晶圆20的通孔。在第二晶圆20的第二表面涂覆一层键合胶,将切割后的第一晶圆10贴附在第二晶圆20的第二表面,从而完成第一晶圆10和第二晶圆20的键合。其中,第一通孔311与第二晶圆20上的通孔相对应,第一晶圆10以扇出方式贴附在第二晶圆20的第二表面。在本实施例中,第一晶圆10的基材为钽酸锂或铌酸锂,由于其材料的特殊性,在键合过程中,容易出现晶圆翘曲的现象。因此,在键合之前,在第二晶圆20的第一表面键合第一载板41,以提供支撑保护作用。第一载板41为临时键合载板,用于防止晶圆在制程中出现卷曲的现象,并能够降低晶圆断裂的风险。

46.如图14所示,在完成第一晶圆10和第二晶圆20的键合后,使用塑封工艺在第一晶圆10的第二表面和侧面形成塑封结构70,使得第一晶圆10和第二晶圆20形成一个扇出型的三维重构晶圆。

47.如图15-图17所示,对第二晶圆20第一表面的第一载板41进行解键合,并在重构晶圆的塑封面上键合第二载板42,以降低晶圆在制程中出现翘曲的现象,保证后续制程的顺利进行。

48.之后,在第二晶圆20的第一表面沉积第二绝缘层32,并在第二绝缘层32对应第一通孔311的位置刻蚀第三通孔322,以及在对应第二焊垫201的位置刻蚀第二通孔321。其中,第一绝缘层31和第二绝缘层32共同形成重布线层30。位于第一绝缘层31上的第一通孔311与位于第二绝缘层32上的第三通孔322相互贯通第二晶圆20,并整体形成第四通孔33。第一焊垫101位于第一晶圆10的第一表面,第二焊垫201位于第二晶圆20的第一表面。第一焊垫101和第二焊垫201通过第四通孔33实现电连接,其中,第四通孔33中填充有导电材料。在本实施例中,导电材料可以填满第四通孔33,也可以沿第四通孔33的内壁涂覆,并在导电材料的外层设置一层保护层(如,绿油)。采用重布线工艺在第二绝缘层32上方形成金属走线40,金属走线40沿第二绝缘层32的表面布置,并与第四通孔33和第二通孔321内的导电材料连接,实现第一焊垫101和第二焊垫201的电性连接,从而实现第一晶圆10与第二晶圆20上的电路连接。

49.在形成金属走线40之后,在金属走线40上形成第三绝缘层34,第三绝缘层34主要起到保护作用,防止外界环境对金属走线40的侵蚀。然后,在第三绝缘层34上继续作业凸点工艺,形成金属凸点50,金属凸点50设置于第三绝缘层34远离第二绝缘层32一侧,并通过导电柱60与金属走线40连接,导电柱60用于引出金属走线40。在本实施例中,导电柱60和金属凸点50可以采用相同材料制成。

50.最后,对第二载板42进行解键合,完成扇出型封装结构。

51.本实用新型实施例提供的技术方案通过扇出方式将第一晶圆与第二晶圆键合在一起形成扇出型三维晶圆,使得晶圆的尺寸灵活性较高,可以使适应不同尺寸的晶圆键合,大大提高了晶圆封装的集成度,能够减小晶圆封装的占用面积,从而提升了晶圆的利用率。此外,第一晶圆10以扇出方式与硅基材的第二晶圆20重构成更大尺寸的三维晶圆,打破了小尺寸晶圆的限制,大大提升了晶圆的生产效率,并有利于降低生产成本。并且在制程中,采用多道临时键合载板,为重构晶圆提供支撑保护,可以有效改善晶圆的翘曲并降低裂片风险。

52.可选地,本实用新型实施例还提供了一种射频模组,包括本实用新型任意实施例所提供的扇出型封装结构,因此,本实用新型实施例提供的射频模组也具备上述任意实施例所描述的有益效果,在此不再赘述。

53.注意,上述仅为本实用新型的较佳实施例及所运用技术原理。本领域技术人员会理解,本实用新型不限于这里所述的特定实施例,对本领域技术人员来说能够进行各种明显的变化、重新调整和替代而不会脱离本实用新型的保护范围。因此,虽然通过以上实施例对本实用新型进行了较为详细的说明,但是本实用新型不仅仅限于以上实施例,在不脱离本实用新型构思的情况下,还可以包括更多其他等效实施例,而本实用新型的范围由所附的权利要求范围决定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。