1.本发明涉及一种用于形式验证的宇航通用门级逻辑建模方法,属于航天器控制软件评测领域。

背景技术:

2.逻辑单元是构成宇航级超大规模集成电路的基本单元。通过对宇航级大规模集成电路的基于逻辑模型的安全性能评价,可以完成逻辑设计不完整、逻辑漏洞甚至设计后门的发掘、评测和改进,避免了流片后暴露问题再解决的周期和流片费用成本。为了保证宇航大规模集成电路的安全可靠在轨应用,需要对逻辑模型进行建模,并基于此模型对器件安全属性进行测量和评估。

3.航天器用大规模集成电路作为航天器核心关键元器件的组成部分,其安全性威胁着天基基础国防设施的可靠运行。目前在金融、密码领域的形式验证评价中所用的逻辑模型,不能全面充分表征在宇航集成电路中的抗辐射性能和应用条件。

技术实现要素:

4.本发明解决的技术问题是:针对目前现有技术中,传统形式验证用逻辑模型无法满足宇航级集成电路的评测使用要求的问题,提出了一种用于形式验证的宇航通用门级逻辑建模方法。

5.本发明解决上述技术问题是通过如下技术方案予以实现的:

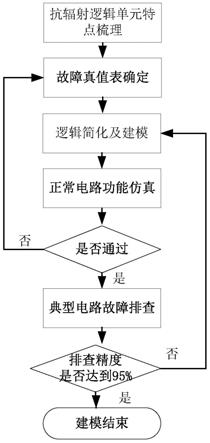

6.一种用于形式验证的宇航通用门级逻辑建模方法,步骤如下:

7.(1)对待验证的宇航级大规模集成电路的抗辐射加固策略进行梳理分析,获取宇航级大规模集成电路逻辑门典型特征;

8.(2)根据步骤(1)所得宇航级大规模集成电路逻辑门典型特征、宇航环境污染标签,进行梳理分析,获取故障真值表;

9.(3)根据所得故障真值表,进行逻辑简化,并基于eda兼容语言进行逻辑门建模;

10.(4)获取逻辑门模型,对常用宇航级大规模集成电路的正常功能进行仿真测试;

11.(5)根据仿真测试结果进行判断,若逻辑门模型对宇航级大规模集成电路的正常功能有影响,则对逻辑门模型进行修改调制,直至逻辑门模型对宇航级大规模集成电路的正常功能无影响;否则,对宇航级大规模集成电路进行故障情况排查;

12.(6)通过外部仿真工具,对逻辑门模型进行仿真遍历及故障数排查,并与宇航级大规模集成电路本身故障数进行对比;

13.(7)获取故障数对比结果,若一致性大于指定标准,则逻辑门模型精度满足要求,进入步骤(8);若一致性不大于指定标准,则对逻辑门模型进行修改调制直至故障数对比结果一致性大于指定标准;

14.(8)基于逻辑门模型进行宇航级大规模集成电路的基于形式验证的安全属性评价。

15.所述步骤(2)中,故障真值表中包括宇航级大规模集成电路的逻辑变量、逻辑函数、污染标签、污染跟踪函数,污染跟踪函数分别基于固定故障传播模型、随机故障传播模型或位翻转故障传播模型分别构建。

16.所述步骤(3)中,逻辑简化为基于故障真值表数据,可选用abc、sis、espresso工具完成逻辑最简表示。

17.所述步骤(4)中,常用宇航级大规模集成电路可替换为各种规模的宇航级集成电路。

18.所述步骤(1)中,宇航环境包括极端温度、或空间辐射条件导致的位翻转故障模式。

19.所述步骤(7)中,故障数对比结果一致性的指定标准为95%。

20.本发明与现有技术相比的优点在于:

21.本发明提供的一种用于形式验证的宇航通用门级逻辑建模方法,通过对宇航级集成电路用逻辑门级电路特点及宇航抗辐射应用条件的分析研究,形成的逻辑模型可用于航天器用集成电路的安全属性分析,充分保证了其空间环境下的安全性与适应性,充分保证了宇航级大规模集成电路在系统集成环境下的安全可靠性。

附图说明

22.图1为发明提供的基于形式验证的宇航通用门级逻辑建模流程示意图;

23.图2为发明提供的宇航应用污染标签的二进制真值表示意图;

24.图3为发明提供的基于verilog的逻辑门级建模示意图;

25.图4为发明提供的典型电路故障数仿真结果示意图;

具体实施方式

26.一种用于形式验证的宇航通用门级逻辑建模方法,用于解决空间辐射环境和航天器高可靠应用条件下的集成电路安全属性评测难题,具体方法步骤如下:

27.(1)对待验证的宇航级大规模集成电路的抗辐射加固策略进行梳理分析,获取宇航级大规模集成电路逻辑门典型特征;

28.其中,宇航环境包括极端温度、或空间辐射条件导致的位翻转故障模式;

29.(2)根据步骤(1)所得宇航级大规模集成电路逻辑门典型特征、宇航环境污染标签,进行梳理分析,获取故障真值表;

30.其中,故障真值表中包括宇航级大规模集成电路的逻辑变量、逻辑函数、污染标签、污染跟踪函数,污染跟踪函数应分别基于固定故障传播模型、随机故障传播模型或位翻转故障传播模型分别构建;

31.(3)根据所得故障真值表,进行逻辑简化,并基于eda兼容语言进行逻辑门建模;

32.其中,逻辑简化为基于故障真值表数据,可选用abc、sis、espresso工具完成逻辑最简表示。

33.(4)获取逻辑门模型,对常用宇航级大规模集成电路的正常功能进行仿真测试;

34.其中,常用宇航级大规模集成电路可替换为各种规模的宇航级集成电路;

35.(5)根据仿真测试结果进行判断,若逻辑门模型对宇航级大规模集成电路的正常

功能有影响,则对逻辑门模型进行修改调制,直至逻辑门模型对宇航级大规模集成电路的正常功能无影响;否则,对宇航级大规模集成电路进行故障情况排查;

36.(6)通过外部仿真工具,对逻辑门模型进行仿真遍历及故障数排查,并与宇航级大规模集成电路本身故障数进行对比;

37.(7)获取故障数对比结果,若一致性大于指定标准,则逻辑门模型精度满足要求,进入步骤(8);若一致性不大于指定标准,则对逻辑门模型进行修改调制直至故障数对比结果一致性大于指定标准;

38.其中,故障数对比结果一致性的指定标准为95%;

39.(8)基于逻辑门模型进行宇航级大规模集成电路的基于形式验证的安全属性评价。

40.下面根据具体实施例进行进一步说明:

41.在当前实施例中,如图1所示,用于形式验证的宇航通用门级逻辑建模方法,具体步骤如下:

42.(1)获取宇航级大规模集成电路逻辑门典型特点,具体为:

43.以宇航用二输入异或门逻辑为例,两个输入可能由于阈值电压偏移或单粒子打翻引起输入逻辑翻转,均为宇航级大规模集成电路逻辑门典型特点;

44.(2)根据步骤(1)所得的宇航级大规模集成电路逻辑门典型特点,以及宇航环境可导致的污染标签,梳理确定形成故障真值表;

45.包含上述污染标签的故障真值表如图2所示;

46.(3)根据步骤(2)所得的故障真值表,基于位翻转故障传播模型进行逻辑简化,并基于verilog语言进行逻辑门建模,建模文件如图3所示,其中:

[0047][0048]

式中,参数结束补充一下;

[0049]

(4)基于步骤(3)中形成的逻辑门模型,对典型电路的正常功能进行仿真测试;

[0050]

(5)根据结果表明电路功能正确无误,证明该逻辑模型不影响电路正常功能;

[0051]

(6)在iwis电路库中选取大规模典型电路,基于骤(3)所得逻辑门建模在synopsys工具中进行综合,基于modelsim工具,对综合后的网表进行故障数排查,并与典型电路本身的故障数进行比对,仿真结果如图4所示;

[0052]

(7)如图4所示的仿真结果显示总故障数为32’h832c8a06,与典型电路自有故障数32’585v356h2v0相比,比对精度大于98%,说明该模型精度可满足形式验证安全属性排查仿真要求。

[0053]

对于本领域技术人员而言,显然本发明不限于上述示范性实施例的细节,而且在不背离本发明的精神或基本特征的情况下,能够以其他的具体形式实现本发明。因此,无论从哪一点来看,均应将实施例看作是示范性的,而且是非限制性的,本发明的范围由所附权利要求而不是上述说明限定,因此旨在将落在权利要求的等同要件的含义和范围内的所有变化囊括在本发明内。不应将权利要求中的任何附图标记视为限制所涉及的权利要求。

[0054]

本发明说明书中未作详细描述的内容属于本领域技术人员的公知技术。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。