一种异构众核架构上cpu共享数组引导维选取策略

技术领域

1.本发明涉及一种异构众核架构上cpu共享数组引导维选取策略,属于高性能计算技术领域。

背景技术:

2.异构众核处理器最突出的优势是高性能,尤其适用于高性能计算领域,主要应用于超大规模并行机等大型实用系统中,同时它也存在着访存带宽受限的问题。科学计算中,矩阵运算是常见的工具,在基于异构众核处理器的超算上,矩阵运算时,从核通常需要通过带跨步dma实现ldm与芯片共享空间之间数据的批量交换;但是,不合适的跨步大小会极大降低访存性能,这也成为限制异构众核处理器性能指标的瓶颈。

3.矩阵运算由于其计算量巨大,耗时长,往往通过并行算法提高效率;同时,为了减少通信,会将一部分数据放在共享内存上。在异构众核处理器上,通过将矩阵分块后分配给各个从核运算实现并行;芯片共享空间中的数据可以整个处理器共享,通过将数据放在芯片共享空间可以减少通信。从核往往通过带跨步dma实现ldm与芯片共享空间之间矩阵数据的批量交换,来获取所需要的矩阵分块,跨步的选取会影响各个存控的利用率,并且不合适的跨步大小会导致体冲突,极大影响访存性能,跨步大小由矩阵分块大小及矩阵引导维共同决定。

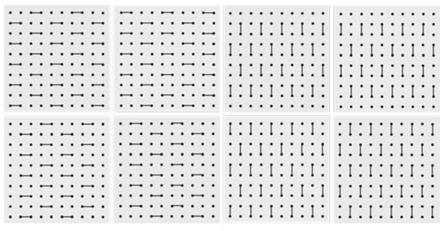

4.现有技术的缺点:1、芯片共享空间地址的编址方式导致,根据跨步特点,各个存控访存量会存在不均衡的问题;2、当两次访存地址满足特定条件时,会造成体冲突;3、dma参数不合适比如源地址、跨步未128b对界导致性能下降。

5.异构众核芯片集成了多个核组,每个核组包括1个通用主核核心、存储控制器、协议处理部件、8x8从核阵列。主存采用虚地址,分核组私有空间和核组共享空间,共享空间地址的编址方式如附图2所示:以芯片包含四个核组为例,共享空间地址以512为单位,由不同核组存控管理,即共享空间地址根据除以2048的余数,由不同核组存控管理。示例中,余数为0-511,由核组0存控管理;余数为512-1023,由核组1存控管理;余数为1024-1535,由核组2存控管理;余数为1536-2047,由核组3存控管理。访存时所利用的存控数越多,则带宽利用越饱满。

6.实际运算中,根据dma跨步大小特点,部分存控可能没有参与其中。举例如下,考虑dma时,芯片共享空间编址方式如图1所示,访存地址从0开始,数据量足够大,向量块大小为512字节,根据跨步大小,存控具体的利用情况如下表所示:跨步mod(512*4)存控利用数0451221024415361方便起见,考虑跨步512b对界的情况,当跨步除以2048的余数为1536时,所有的访

存过程都只利用到了一个存控;当跨步被2048整除时,访存过程利用到了所有四个存控;这两种情况下访存带宽会有接近四倍差距。

7.不同的异构众核芯片上,核组数会有所不同,可以按照如上例子做类似推导。作如下标记:记共享空间地址以k为单位,由不同核组存控管理;记核组数为n。考虑dma时,芯片共享空间编址类似图1,访存地址从0开始,数据量足够大,向量块大小为k字节,为尽可能利用所有存控,跨步被(k * n)整除是一种理想的情况。

8.dram中最核心的部件是存储阵列,它是由基本动态存储单元构成的一个阵列(2m行

×ꢀ

2n列),由于物理实现的考虑,对于大容量存储器,不能使用单一的超大阵列来实现,而是要使用多个较小的阵列实现,这样一个阵列称之为一个体(bank),ddr3颗粒里面有8个bank,ddr4中有8或16个bank。而且,ddr4较之前的ddr存储器,在bank的层次之上增加了bank group(简称bg)的结构,4个bank构成1个bg。bank group主要影响访存时序参数,group内的命令延迟适用一种参数(较大),group间的命令延迟适用另一种时序参数。附图3为存储阵列示意图。

9.ddr4的地址分为行地址row、列地址col、体地址bank,体地址进一步分为bank group的地址bg和bank group内的bank地址ba。考虑连续两次访存时,存控通过某个映射将物理地址转换为ddr4地址,映射后的两次ddr4地址如果在同一个体中不同行,则访存操作无法并行,只能串行,从而导致访存性能下降,称之为体冲突。在上述问题情形中,当行主序矩阵引导维为31的倍数时,对矩阵某个分块的dma取会产生体冲突,造成性能下降。

技术实现要素:

10.本发明的目的是提供一种异构众核架构上cpu共享数组引导维选取策略,使得从核dma取矩阵分块数据时性能最佳。

11.为达到上述目的,本发明采用的技术方案是:提供一种异构众核架构上cpu共享数组引导维选取策略,对于大小为m

×

n的双精度矩阵,nd == 0,m%m == 0,行主序,引导维为ld,分块大小为m

×

64;运算时,从核每次dma获取某个分块运算,并按下表约定下列标记:标记含义k=512芯片共享空间地址以k字节为单位,由不同存控管理n=6核组数stride=(ld-64)*8bdma时跨步大小,单位为字节block=64*8bdma时跨步向量块大小,单位为字节src矩阵首地址dispdma时源地址相对于矩阵首地址偏移量,单位为字节ld矩阵引导维大小,单位为(矩阵元素)个数;对矩阵引导维进行如下调整后,将矩阵根据调整后获得的引导维参数存储于cpu共享空间指定地址中,供从核dma访存取用:s1、申请cpu共享空间时,控制申请空间的首地址即src 128b对界,使得从核dma取时源地址始终128b对界;

s2、选取 ld = 64 * (6a 1),a为满足64 * (6a 1) 》= n的最小整数值,使得从核dma访存时存控利用率最高且dma跨步满足128b对界;s3、如果s2中取得的ld1==0,取a=a 1,使得体冲突问题得到规避;s4、m

×

n双精度矩阵,行主序,以s3中取得的ld作为引导维,以src为首地址,存储在cpu共享空间中。

12.由于上述技术方案的运用,本发明与现有技术相比具有下列优点:本发明提出一种适用于异构众核架构的处理器的引导维选取策略,通过调整矩阵引导维,平衡从核dma取数据时各个存控上的访存量,实现负载均衡,且规避存控体冲突,同时优化dma参数,使得对芯片共享空间数组的dma访存能够达到理论带宽,从而减少从核获取矩阵分块数据的等待时间,提高运算效率。

附图说明

13.附图1为对主存带跨步的dma读写示意图;附图2为四核组芯片-共享空间编址方式示例图;附图3为存储阵列示意图;附图4为矩阵数据传输示意图。

具体实施方式

14.实施例:本发明提供一种异构众核架构上cpu共享数组引导维选取策略,对于大小为m

×

n的双精度矩阵,nd == 0,m%m == 0,行主序(矩阵以一维数组形式存储),引导维为ld,分块大小为m

×

64;运算时,从核每次dma获取某个分块运算,并按下表约定下列标记:标记含义k=512芯片共享空间地址以k字节为单位,由不同存控管理n=6核组数stride=(ld-64)*8bdma时跨步大小,单位为字节block=64*8bdma时跨步向量块大小,单位为字节src矩阵首地址dispdma时源地址相对于矩阵首地址偏移量,单位为字节ld矩阵引导维大小,单位为(矩阵元素)个数;对矩阵引导维进行如下调整后,将矩阵根据调整后获得的引导维参数存储于cpu共享空间指定地址中,供从核dma访存取用:s1、申请cpu共享空间时,控制申请空间的首地址即src 128b对界,此时,由于分块大小为64,使得从核dma取时源地址始终128b对界;s2、为了提升存控利用率,选取 ld = 64 * (6a 1),a为满足64 * (6a 1) 》= n的最小整数值,使得从核dma访存时存控利用率最高且dma跨步满足128b对界;s3、为规避体冲突,如果s2中取得的ld1==0,取a=a 1,使得体冲突问题得到规避;

s4、m

×

n双精度矩阵,行主序,以s3中取得的ld作为引导维,以src为首地址,存储在cpu共享空间中。

15.对上述实施例的进一步解释如下:实际问题情形如下:双精度矩阵大小为mxn,nd == 0,m%m == 0,行主序(矩阵以一维数组形式存储),引导维为ld,分块大小为mx64;运算时,从核每次dma获取某个分块运算。

16.按下表约定下列标记:标记含义k=512芯片共享空间地址以k字节为单位,由不同存控管理n=6核组数stride=(ld-64)*8bdma时跨步大小,单位为字节block=64*8bdma时跨步向量块大小,单位为字节src矩阵首地址dispdma时源地址相对于矩阵首地址偏移量,单位为字节ld矩阵引导维大小,单位为(矩阵元素)个数相关硬件条件如下:1、异构众核芯片每个cpu包含6个核组,cpu共享空间以512b为单位,由不同存控管理。

17.2、从核dma取时,当源地址与目的地址为128b对界,跨步为128b倍数时性能最佳。

18.3、在上述问题情形中,当行主序矩阵引导维为31的倍数时,对矩阵某个分块的dma取会产生体冲突,造成性能下降。

19.示意如附图4。

20.对矩阵引导维进行如下调整后,将矩阵根据调整后获得的引导维参数存储于cpu共享空间指定地址中,供从核dma访存取用:1、申请cpu共享空间时,控制申请空间的首地址即src 128b对界,使得从核dma取时源地址始终128b对界;2、选取 ld = 64 * (6a 1),a为满足64 * (6a 1) 》= n的最小整数值,使得从核dma访存时存控利用率最高且dma跨步满足128b对界;3、如果步骤2中取得的ld1==0,取a=a 1,使得体冲突问题得到规避;4、m

×

n双精度矩阵,行主序,以s3中取得的ld作为引导维,以src为首地址,存储在cpu共享空间中。

21.此时,从核每次dma取该矩阵某个分块,性能最佳。

22.采用上述一种异构众核架构上cpu共享数组引导维选取策略时,其提出一种适用于异构众核架构的处理器的引导维选取策略,通过调整引导维长度,平衡各个存控上的访存量,实现负载均衡,且规避存控体冲突,同时优化dma参数,使得对芯片共享空间数组的dma访存能够达到理论带宽。

23.为了便于更好的理解本发明,下面将对本文中使用的术语进行简要的解释:异构众核芯片:将少量承担管理、通信和运算功能的通用主核核心和大量承担运算功能的精简从核核心集成在一颗完整芯片上的高性能异构中央处理器;一颗芯片上集成

了多个核组,每个核组包括1个通用主核核心、存储控制器、协议处理部件、8x8从核阵列;通用主核核心运行通用的操作系统,主要承担整个芯片的管理和控制功能,也承担一定的运算功能和芯片与外部的通信功能;从核核心起到加速计算的功能。

24.芯片共享空间:异构众核芯片上,主存地址空间采用虚地址,分核组私有空间和核组共享空间;不同核组间,相同的私有空间地址映射向不同的内存空间,相同的共享空间地址映射向相同的内存空间。

25.引导维:矩阵在内存中实际存储时第一维的大小,列优先存储时为矩阵的行数,行优先存储时为矩阵的列数。

26.ldm(local data memory):异构众核芯片上,从核的本地存储空间。

27.从核dma(direct memory access):dma机制实现ldm与主存之间数据的批量交换;dma有如下几个关键参数:dma行为,数据的源地址、目的地址,向量块大小(单位:字节),跨步大小(单位:字节),数据量(单位:字节)等,附图 1简单描述了对主存带跨步的dma读写。

28.padding:对矩阵进行边界填充,在矩阵的边界上填充一些值,以增加矩阵的大小。

29.体冲突:体(bank)是指共享内存按照固定大小划分为若干的存储模块,若一个存储器请求的2个地址落入同一个存储体内,就会出现存储体冲突。

30.dram(dynamic random access memory):动态随机存储器。

31.ddr:全称为double data-rate synchronous dram,通过使用两个时钟沿作为控制信号,从而使dram的速度翻倍。

32.pa(physical address):物理地址。

33.上述实施例只为说明本发明的技术构思及特点,其目的在于让熟悉此项技术的人士能够了解本发明的内容并据以实施,并不能以此限制本发明的保护范围。凡根据本发明精神实质所作的等效变化或修饰,都应涵盖在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。