1.本发明涉及一种针对百量子级方形量子网格随机电路模拟方法,属于量子模拟技术领域。

背景技术:

2.随着量子计算机的快速发展,在量子物理设备上实现的量子计算规模不断增大,这也使得人们对于在经典计算机上模拟验证量子计算的要求也变高。谷歌在2016年提出了随机量子电路(rqc)来衡量量子计算设备的性能。人们认为rqc是一个适用于nisq硬件的理想问题,原因是:1)rqc通常由单量子比特门和最近邻量子之间的双量子比特门操作的交错组成,这对当前的量子计算硬件非常友好;2)高达几百上千个双量子比特门操作,rqc可能已经形成了高度纠缠的量子态,这是现在最快的超级计算机也难以模拟的。

3.因此,rqc成为了证明量子霸权的一个重要基准,该算法既可以作为问题经典复杂性的基准,也可以是量子设备输出的验证工具。

4.随机量子电路的制备方式如下:

•

首先将hadamard门应用于每个量子位。

5.•

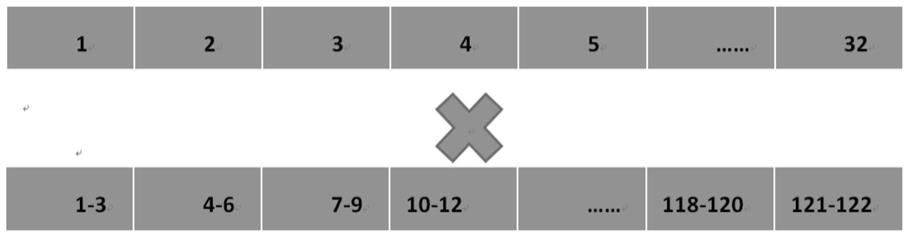

其次,重复施加八种不同配置的受控z门(cz),直到获得所需的电路深度。对于10

×

10的一百个量子比特电路,受控z门的配置参见图1中的8种不同的cz模式,其中cz门由两个量子位之间的线表示。这种模式确保每一个周期,每个量子比特都会和它最近邻的量子比特之间执行一次cz门。

6.•

除了cz门之外,单量子门还应用于在前一个周期中执行cz门的所有量子位。单量子位门随机选择t门,x^1/2门或y^1/2门中的一种。

7.•

最后再将hadamard门应用于每个量子位。

8.对于一个给定的量子电路,总是可以用矩阵来代表门操作,对于一个n量子比特的门操作,可以表示成一个2^n*2^n的矩阵。随着量子比特增多,这种网络收缩的计算和存储成本与比特的数量成指数增加,受到内存的限制,当前功能最强大的超级计算机只能存储约50量子比特。对于超过50比特的量子随机电路,全部振幅的存储达到了pb 级别,因此,只能采用单振幅模拟或者部分振幅模拟的方法,即计算2^50个振幅中的一个结果。

9.近年来,受到量子信息理论中量子纠缠研究的启发,人们提出了包括矩阵乘积状态、纠缠投影态等的张量网络(tns)方法。

10.从每一个量子比特出发,将量子比特视为一个一阶张量(向量),用(0,1)和(1,0)表示其处在0态或者1态。对于每一个单量子比特门,我们将其视为一个二阶张量,即一个2*2的矩阵((a,b),(c,d)),每个量子比特在演化过程中遇到单量子比特门,进行向量矩阵乘即可,不影响其大小。对于每一个双量子比特门,我们一般用4*4的矩阵进行表示,在张量网络方法中,我们将其svd分解为两个2*2*2的张量,并分别乘在两个量子比特的演化张量上,

该量子比特的大小也会随之翻倍。每一个量子比特经过演化之后,可以视为一个四阶张量(和上下左右的邻居节点之间分别有一条键),对于一个l层电路(l是8的倍数),该张量的每一阶的维数是2^(l/8)。将这个10*10个(量子比特个数)张量组成的张量网络通过张量收缩的方式最后会得到一个标量,也就是我们所需要的单振幅模拟的结果。

11.现有的单振幅量子模拟中的张量收缩算法,主要的方法是通过沿张量网格逐行/逐列收缩的方法进行张量收缩,缺点是随着量子比特数量的增加,存储的量子网络拓扑结构阶数变高,存储困难增大。比如对于一百量子比特的方形量子网格电路,此时的量子模拟的最高阶数是十一阶,一旦量子随机电路层数超过24层,就会产生超过p级的内存需求,这是普通计算机无法做到的。也就是说单振幅模拟算法在量子比特数目固定为100量子比特,随着随机量子电路层数增加,内存呈指数增长,到24层模拟时,已经达到了一般计算机可承受的阈值。

12.现有的单振幅量子模拟一般都采用张量收缩算法,主要的方法是通过沿张量网格逐行/逐列收缩的方法进行张量收缩,缺点是随着量子比特数量的增加,存储的量子网络拓扑结构阶数变高,存储困难增大。比如对于一百量子比特的方形量子网格电路,此时的量子模拟的最高阶数是十一阶,一旦量子随机电路层数超过24层,就会产生超过p级的内存需求,这是普通计算机无法做到的。

技术实现要素:

13.本发明的目的是在百量子级电路模拟过程中,提出一种降低内存需求的张量收缩方法,以解决大规模量子网格模拟的内存需求不足的问题。

14.为达到上述目的,本发明采用的技术方案是:提供一种针对百量子级方形量子网格随机电路模拟方法,在利用张量网络方法对量子随机电路进行模拟的过程中,于是将张量网络切割成较小的张量片,存在不同的节点上;包括以下步骤:s1、将张量网络沿中线切割m次,以降低张量收缩路径中产生的最大张量片的阶数;s2、沿张量网络中线每切割1次,生成2^(l/8)个,独立的并行任务,将这些独立的任务分在不同的进程上并行计算,每个任务通过计算,得到一个标量结果,其中,l表示电路的层数;s3、将s2中获得的每个任务得到的标量结果相加,得到了张量的单振幅模拟结果。

15.由于上述技术方案的运用,本发明与现有技术相比具有下列优点:本发明一种针对百量子级方形量子网格随机电路模拟方法,主要针对量子模拟中常用的方形结构网格,可以降低模拟过程的内存需要,从而满足百量子比特以上量级量子随机电路的模拟需求。

附图说明

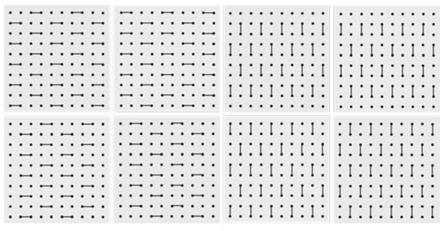

16.附图1为100比特方形随机量子电路的受控z门的配置示意图;附图2为本发明一种随机电路模拟方法的示意图;附图3为本发明一种随机电路模拟方法的示意图。

具体实施方式

17.实施例:本发明提供一种针对百量子级方形量子网格随机电路模拟方法,在利用张量网络方法对量子随机电路进行模拟的过程中,于是将张量网络切割成较小的张量片,存在不同的节点上;包括以下步骤:s1、将张量网络沿中线切割m次,以降低张量收缩路径中产生的最大张量片的阶数,增大m的值使得收缩中产生的最大张量片能够在单节点上存储;s2、沿张量网络中线每切割1次,生成2^(l/8)个,独立的并行任务,将这些独立的任务分在不同的进程上并行计算,每个任务通过计算,得到一个标量结果,其中,l表示电路的层数;s3、将s2中获得的每个任务得到的标量结果相加,得到了张量的单振幅模拟结果。

18.对上述实施例的进一步解释如下:本发明针对百量子比特以上量级的量子模拟可能存在的因为张量阶数太高导致内存不够而无法进行张量收缩的问题,在张量收缩方面,提出基于切割的低内存收缩方法,解决了针对百量子级方形量子网格随机电路模拟的内存需求不足的问题;本发明的切割方法可以降低模拟过程的内存需要,从而模拟更多数量的量子比特随机电路。

19.如图2所示,将一个十阶的张量从中切开分成了两个五阶张量,从而降低了内存需求,但是另一方面计算的时间增加了,增加的倍数就是被切开的张量阶的维数。

20.针对100量子比特方形网格的张量收缩,从中间由上到下进行张量边的切割:切一刀,需要存储的最大规模张量网络拓扑结构为10阶;切两刀,需要存储的最大规模张量网络拓扑结构为9阶;切三刀,需要存储的最大规模张量网络拓扑结构为9阶;切四刀,需要存储的最大规模张量网络拓扑结构为8阶;切五刀,需要存储的最大规模张量网络拓扑结构为7阶;切六刀,需要存储的最大规模张量网络拓扑结构为6阶;切七刀,需要存储的最大规模张量网络拓扑结构为6阶;切八刀,需要存储的最大规模张量网络拓扑结构为5阶;切九刀,需要存储的最大规模张量网络拓扑结构为5阶;切十刀,需要存储的最大规模张量网络拓扑结构为5阶。

21.当每一阶的维数为n时,切两刀就可以降低n^2倍内存需求,切四刀,降低n^3倍内存需求,切六刀,降低n^5倍内存需求;通过这种张量切割的方式,达到了平衡时间和空间上需求的目的,从而模拟更多的量子比特随机电路。

22.采用上述一种针对百量子级方形量子网格随机电路模拟方法时,其主要针对量子模拟中常用的方形结构网格,可以降低模拟过程的内存需要,从而满足百量子比特以上量级量子随机电路的模拟需求。

23.为了便于更好的理解本发明,下面将对本文中使用的术语进行简要的解释:量子随机电路:英文为quantum random circuits,指在量子电路中随机添加单比特门和按照谷歌提出的随机电路双比特门添加方法构成的量子电路。

24.上述实施例只为说明本发明的技术构思及特点,其目的在于让熟悉此项技术的人士能够了解本发明的内容并据以实施,并不能以此限制本发明的保护范围。凡根据本发明精神实质所作的等效变化或修饰,都应涵盖在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。