1.本发明涉及多元量子逻辑领域高性能可逆电路的设计领域,具体地,涉及四元量子可逆半加器、全加器、并行全加器和并行加/减器电路,可应用于量子计算机、算术处理器及复杂电路的设计。

背景技术:

2.能量耗散是硬件设计中的一个重要方面。landauer已经证明,对于逻辑计算中丢失的每一位信息,能量耗散量至少为ktln2焦耳,其中k是玻耳兹曼常数,t是执行计算时的绝对温度。bennett指出,对于量子电路,要耗散零能量,计算必须是信息无损或可逆的。如果可以从输出向量中具体地检索输入向量并且在输入和输出之间存在一一对应的关系,则门是可逆的。此外,在可逆逻辑设计的综合中,不允许扇出和反馈。量子技术是未来计算系统最有前途的技术之一,量子系统本质上是可逆的。

3.在过去的几年里,研究人员关注的一个主要方面是多元量子逻辑,因为这种逻辑比二进制量子逻辑有更多的优点,例如量子密码的安全性更好,量子信息处理更强大,功耗更低和容错性更高。三元和四元量子逻辑都是一种多元量子逻辑。许多文献介绍了基于三元量子逻辑的重要工作。然而,它的局限性在于经典的二元逻辑函数不能很容易地用三元基来表示,所提出的方法只适用于三元逻辑函数。四元量子逻辑是一种很有前途的技术,除了使用四元逻辑函数外,经典的二元逻辑函数是通过将2个量子位组合成四元量子值来表示的。在四元量子逻辑中,一个信息单元称为量子数,四元逻辑值为|0》,|1》,|2》,和|3》。利用离子阱量子技术可以实现四元量子电路。

4.加法器是电路系统中产生数的和的装置,常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。若加数和被加数为输入,和数与进位为输出,则为半加器。若加数、被加数与低位的进位数为输入,和数与进位为输出,则为全加器。加法器电路是构成复杂硬件的主要电路之一,是设计其它算术运算电路的基础。

5.在设计可逆电路时,有一些重要的指标可以评价可逆电路的性能,定义如下:

6.量子代价:量子代价是指一个电路的代价,它是通过构建该电路所需的量子门的数量来计算的。

7.硬件复杂度:硬件复杂度是指电路的复杂度,其中ε表示一个四元1-qudit门计算复杂性,γ表示四元2-qudit muthukrishnan stroud门计算复杂性。

8.恒定输入数:恒定输入数是指分配给常量值(如0、1、2或3)以合成给定逻辑函数的输入数。

9.垃圾输出数:垃圾输出数是指在给定逻辑函数的合成中未使用的输出数。

10.这些重要参数的最小化使得四元量子可逆逻辑设计具有更高的效率。

11.四元量子逻辑

12.四元量子逻辑是一种多元量子逻辑。与经典的二元量子逻辑相比,四元量子逻辑

除了可以使用四元逻辑函数外,还可以使用二元逻辑函数,因此其量子信息处理更强大、功耗更低、容错性更高。

13.在四元量子系统中,存储信息的单位称为量子数(quantum digit),可以用0、1、2或3值来表示,这些值由4

×

1向量表示。这些量化矢量中的每一个都按以下方式表示:

[0014][0015]

qudit的四种可能状态是:|0》,|1》,|2》或|3》。量子存在于基态的线性叠加中,这种技术称为叠加ψ。在四元量子逻辑中,叠加的符号是ψ=α|0》 β|1》 γ|2》 δ|3》,也写为向量(α,β,γ,δ),其中α,β,γ以及δ是复数。状态|0》发生的概率是|α|2、状态|1》是|β|2、状态|2》是|γ|2、状态|3》是|δ|2。这些概率之和是1,|α|2 |β|2 |γ|2 |δ|2=1。通常,n-qudit系统表示4n个不同的计算基态。这些基态可以用|000

…

0》,|000

…

1》,

…

,|333

…

3》来描述。n-qudit系统的所有可能状态均由n qudit的张力产表示。

[0016]

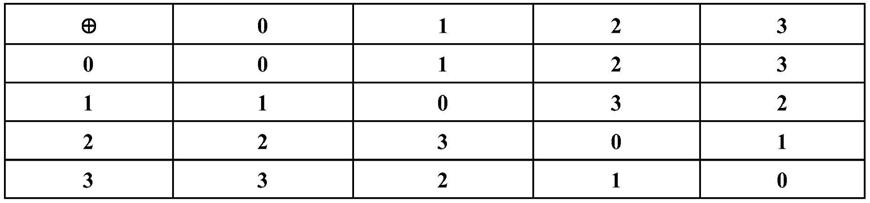

1、四元galois field逻辑

[0017]

四元galois field 4(gf4)由一组元素t={0,1,2,3}和两个基本的二进制运算组成。这些运算是加法模4和乘法模4,分别用以及

⊙

表示。gf4运算如表1和表2所示。此外,这些运算是交换的和结合的。乘法运算是分配给加法运算的。

[0018]

表1 gf4加法运算真值表

[0019][0020]

表2 gf4乘法运算的真值表

[0021]

⊙

012300000101232023130312

[0022]

2、四元1-qudit量子门

[0023]

有4!=24个可能排列的0、1、2和3,由4

×

4个单矩阵表示。下面显示了四元1-qudit单体排转换。

[0024]

[0025][0026][0027][0028][0029][0030]

每一个四元1-qudit单体排列转换都可以使用量子技术构建为一个四元1-qudit门。四元1-qudit门的符号表示如图1所示。门的输入是a,门的输出是p,其中p等于a的z变换。四元一次门的真值表如表3所示。

[0031]

表3四元一次门的真值表

[0032][0033]

每个门都有相应的单反门,用于恢复输入信号以便在电路中重用。如果级联中的两个四进制1-qudit门x和y导致到门x的输入信号在门y的输出处被恢复,那么门y被称为门x的逆门。在四元单量子门中,z( 1)、z( 2)、z( 3)、z(23)、z(01)、z(12)、z(03)、z(13)和z(02)是自反门。

[0034]

3、四元2-qudit muthukrishnan

–

stroud门

[0035]

muthukrishnan和stroud提出了一系列2-qudit多值门,可以使用量子技术(如液体离子阱)作为基本门来实现。四元2-qudit muthukrishnan-stroud(m-s)门的符号表示如图2所示。门的输入是a和b,其中输入a是控制输入,输入b是控制输入。门的输出是p和q,其中输出p等于a,如果输入a等于3,则输出q等于b的z变换。

[0036]

4、四元2-qudit feynman门

[0037]

h.a.khan提出四元2-qudit feynman门。图3显示了四元2-qudit feynman门的符号表示。如图3所示,门的输入是a和b,门的输出是p和q,其中输出p等于a,输出q等于feyman门由3个1-qudit门和3个2-qudit ms门级联实现,量子代价为6,硬件复杂度为3γ 3ε。

[0038]

文献:khan,m.h.(2008).a recursive method for synthesizing quantum/

reversible quaternary parallel adder/subtractor with look-ahead carry.journal of systems architecture,54(12),1113-1121和文献:mandal,s.b.,chakrabarti,a.,&sur-kolay,s.(2012).a synthesis method for quaternary quantum logic circuits.in progress in vlsi design and test(pp.270-280).springer berlin heidelberg公开了两种四元可逆加法器电路,但是该两个文献公开的四元可逆加法器电路具有较高的量子成本、硬件复杂度、恒定输入和垃圾输出,电路的可扩展性和性能较差。因此,如何从根本上解决现有设计的四元可逆加法器电路性能较差成为一种亟需解决的问题。

技术实现要素:

[0039]

本发明所要解决的技术问题在于如何降低现有四元可逆加法器电路的硬件复杂度、恒定输入、垃圾输出和量子代价从而提高电路性能。

[0040]

本发明通过以下技术手段实现解决上述技术问题的:

[0041]

一种四元可逆半加器电路,该电路将两个四进制数a、b作为输入,相加产生的和s以及和进位c作为输出,包括以下电路:

[0042]

第一部分电路:a、b是电路输入,电路输出进位c为0;

[0043]

第二部分电路:输入a经过2个四元1-qudit门级联 2变换后输出为a;输入b直接输出b;第一恒定输入0和输入a经过1个四元1-qudit门 2变换后级联1个四元2-qudit m-s门 1变换,再和输入b级联2个四元2-qudit m-s门 2变换后,再和输入a经过1个四元2-qudit m-s门 1变换后得到垃圾输出o;输出进位c1由输入a经过1个四元1-qudit门 2变换后和恒定输入0级联1个四元2-qudit m-s门 1变换,再和输入b级联1个四元2-qudit m-s门 2变换后级联1个四元2-qudit m-s门 1变换后得到;

[0044]

第三部分电路:输入a经过2个四元1-qudit门 1变换后级联输出为a;输入b经过2个四元1-qudit门 1变换后级联输出为b;输入a经过1个四元1-qudit门 1变换后和第一恒定输入0级联1个四元2-qudit m-s门 1变换,再和输入b级联1个四元2-qudit m-s门 2变换,再和输入b经过1个四元1-qudit门 1变换后级级联1个四元2-qudit m-s门 2变换,再经过1个四元1-qudit输出 1变换后得到垃圾输出o;输入a经过1个四元1-qudit门 1变换后和第一恒定输入0级联1个四元2-qudit m-s门 1变换,再和输入b级联联1个四元2-qudit m-s门 2变换,再和输入b经过1个四元1-qudit门 1变换后级联1个四元2-qudit m-s门 2变换,再和第二恒定输入0级联1个四元2-qudit m-s门 1变换得到输出进位c2;

[0045]

第四部分电路:输入a直接输出a;输入b经过4个四元1-qudit门分别 1变换、 3变换、 3变换、 1变换后级联输出b;第一恒定输入0和输入a经过1个四元2-qudit m-s门 1变换后再和输入b级联1个四元2-qudit m-s门 2变换,再和输入b经过1个四元1-qudit门 1变换后级联1个四元2-qudit m-s门 2变换,再和输入b经过第2个四元1-qudit门 3变换后级联2个四元2-qudit m-s门 2变换,再和输入b经过第3个四元1-qudit门 3变换后级联1个四元2-qudit m-s门 2变换,再和输入b经过第4个四元1-qudit门 1变换后串联1个四元2-qudit m-s门 2变换,再和输入a串联1个四元2-qudit m-s门 1变换得到垃圾输出o;输出进位c3是由垃圾输出o的前半部分和第二恒定输入0级联1个四元2-qudit m-s门 1变换得到;

[0046]

上述四部分的电路按序依次级联组合再和一个四元量子feyman门级联实现四元

可逆半加器电路,其中前一部分的输出作为下一部分的输入。

[0047]

作为进一步优化的技术方案,其中a、b为输入变量,c、s为输出变量,对于等式c=a1.b3 a2.b2 a2.b3 a3.b1 a3.b2 a3.b3中所示的六种输入组合,进位输出的值为1,对于其余的输入组合,进位输出的值为0。

[0048]

作为进一步优化的技术方案,在第一部分中,对于所有的输入组合,输入a=0,输出进位(c0)=0,等式c0=0说明了这部分的输出进位;

[0049]

在第二部分中,输入a=1,当输入b=3时,输出进位(c1)=1,对于其余的输入组合,输出进位(c1)=0,等式c1=a1.b3描述了该部分的输出进位;

[0050]

在第三部分中,输入a=2,当输入b=2或3时,输出进位(c2)=1,对于其他输入组合,输出进位(c2)=0,等式c2=a2.b2 a2.b3=a2(b2 b3)描述了该部分的输出进位;

[0051]

在第四部分中,输入a=3。当输入b=1、2或3时,输出进位(c3)=1,对于其他输入组合输出进位(c3)=0,等式c3=a3.b1 a3.b2 a3.b3=a3(b1 b2 b3)描述了该部分的输出进位。

[0052]

作为进一步优化的技术方案,第二部分电路中使用了2个四元1-qudit门和5个四元2-qudit muthukrishnan-stroud门,这部分的量子代价为7,硬件复杂度为5γ 2ε;

[0053]

第三部分电路中使用了4个四元1-qudit门和7个四元2-qudit muthukrishnan-stroud门,这部分的量子代价为11,硬件复杂度为7γ 4ε;

[0054]

第四部分电路中使用了4个四元1-qudit门和9个四元2-qudit muthukrishnan-stroud门,这部分的量子代价是13,硬件复杂度是9γ 4ε;

[0055]

整个四元可逆半加器电路中使用了13个1-qudit门和24个muthukrishnan stroud门,其硬件复杂度为24γ 13ε,量子代价为37。

[0056]

本发明还提供一种基于上述任一方案所述的四元可逆半加器电路的四元可逆全加器电路,包括两个四元可逆半加器电路,前半加器的输出作为后半加器的输入。

[0057]

作为进一步优化的技术方案,该四元可逆全加器电路的目标输入是a、b和c,目标输出是s和c

out

,使用了26个1qudit门和48个muthukrishnan-stroud门,该电路的硬件复杂度为48γ 26ε,量子代价为74。

[0058]

本发明还提供一种基于上述的四元可逆全加器电路的四元可逆并行全加器电路,包括两个四元可逆全加器电路,两个四元可逆全加器电路串联组合。

[0059]

作为进一步优化的技术方案,该四元可逆并行全加器电路,使用了52个1-qudit门和96个muthukrishnan-stroud门,该电路的硬件复杂度为96γ 52ε,量子代价为148。

[0060]

本发明还提供一种基于上述的四元可逆并行全加器电路的四元可逆并行加法/减法器电路,其特征在于:包括一个四元可逆并行全加器电路和4的补码电路,四元可逆并行全加器电路和4的补码电路串联组合。

[0061]

作为进一步优化的技术方案,该电路使用了52个1-qudit门和99个muthukrishnan-stroud门,该电路的硬件复杂度为99γ 52ε,量子代价是151。

[0062]

本发明的优点在于:与现有设计相比,本发明提出的四元可逆半加器、全加器、并行全加器和并行加/减器电路具有更少的量子成本、硬件复杂度和更少的恒定输入、垃圾输出,这些参数的最小化使得四元可逆加法器电路的性能更好,更加有利于可逆逻辑设计的有效应用。

[0063]

与现有设计相比,本发明提出的四元可逆加法器电路具有较少的硬件复杂度、具有更少的常数输入、具有较少的垃圾输出、具有更少的量子开销,因此,在量子成本、硬件复杂度、恒定输入和垃圾输出方面,与现有设计相比,本研究中提出的加法器电路的性能更好。从而具有更好的可扩展性和性能,可应用于量子计算机、算术处理器及复杂电路的设计。

附图说明

[0064]

图1是现有四元1-qudit门的符号表示;

[0065]

图2是现有四元2-qudit muthukrishnan

–

stroud门的符号表示;

[0066]

图3是现有四元2-qudit feynman门的符号表示;

[0067]

图4本发明实施例四元半加器的真值表;

[0068]

图5本发明实施例四元进位输出的半加器电路第二部分实现;

[0069]

图6本发明实施例四元进位输出的半加器电路第二部分的符号表示;

[0070]

图7本发明实施例四元进位输出的半加器电路第三部分实现;

[0071]

图8本发明实施例四元进位输出的半加器电路第三部分的符号表示;

[0072]

图9本发明实施例四元进位输出的半加器电路第四部分实现;

[0073]

图10本发明实施例四元进位输出的半加器电路第四部分的符号表示;

[0074]

图11本发明实施例四元可逆半加器电路的进位输出的符号表示;

[0075]

图12是本发明实施例四元可逆半加器电路的实现;

[0076]

图13本发明实施例四元可逆半加器电路的符号表示;

[0077]

图14本发明实施例四元可逆全加器电路的符号表示;

[0078]

图15本发明实施例四元可逆并行全加器电路的符号表示;

[0079]

图16本发明实施例四元可逆并行加法/减法器电路的符号表示。

具体实施方式

[0080]

为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0081]

本发明中提出了四元可逆电路的新设计。

[0082]

首先,提出了一种新的四元可逆半加器电路,整体电路图如图12所示。该电路将两个四进制数a、b作为输入,相加产生的和s以及和进位c作为输出。

[0083]

其中四元半加器的真值表如图4所示,其中a、b为输入变量,c、s为输出变量。根据图5,对于等式c=a1.b3 a2.b2 a2.b3 a3.b1 a3.b2 a3.b3中所示的六种输入组合,进位输出的值为1,对于其余的输入组合,进位输出的值为0。

[0084]

为构造四元半加器电路的输出进位,可将真值表分为四部分。

[0085]

在第一部分中,对于所有的输入组合,输入a=0,输出进位(c0)=0,等式c0=0说明了这部分的输出进位,a、b是电路输入,电路输出进位c为0。

[0086]

在第二部分中,输入a=1,当输入b=3时,输出进位(c1)=1,对于其余的输入组

合,输出进位(c1)=0,等式c1=a1.b3描述了该部分的输出进位。第二部分四元进位输出的实现如图5所示,输入a经过2个四元1-qudit门级联 2变换后输出为a;输入b直接输出b;第一恒定输入0和输入a经过1个四元1-qudit门 2变换后级联1个四元2-qudit m-s门 1变换,再和输入b级联2个四元2-qudit m-s门 2变换后,再和输入a经过1个四元2-qudit m-s门 1变换后得到垃圾输出o;输出进位c1由输入a经过1个四元1-qudit门 2变换后和恒定输入0级联1个四元2-qudit m-s门 1变换,再和输入b级联1个四元2-qudit m-s门 2变换后级联1个四元2-qudit m-s门 1变换后得到。该部分使用了2个四元1-qudit门(图1)和5个四元2-qudit muthukrishnan-stroud门(图2),因此这部分的量子代价为7,硬件复杂度为5γ 2ε,所提出的第二部分四元进位输出的符号表示如图6所示。

[0087]

在第三部分中,输入a=2,当输入b=2或3时,输出进位(c2)=1,对于其他输入组合,输出进位(c2)=0,等式c2=a2.b2 a2.b3=a2(b2 b3)描述了该部分的输出进位。第三部分四元进位输出的实现如图7所示,输入a经过2个四元1-qudit门 1变换后级联输出为a;输入b经过2个四元1-qudit门 1变换后级联输出为b;输入a经过1个四元1-qudit门 1变换后和第一恒定输入0级联1个四元2-qudit m-s门 1变换,再和输入b级联1个四元2-qudit m-s门 2变换,再和输入b经过1个四元1-qudit门 1变换后级级联1个四元2-qudit m-s门 2变换,再经过1个四元1-qudit输出 1变换后得到垃圾输出o;输入a经过1个四元1-qudit门 1变换后和第一恒定输入0级联1个四元2-qudit m-s门 1变换,再和输入b级联联1个四元2-qudit m-s门 2变换,再和输入b经过1个四元1-qudit门 1变换后级联1个四元2-qudit m-s门 2变换,再和第二恒定输入0级联1个四元2-qudit m-s门 1变换得到输出进位c2。该部分使用了4个四元1-qudit门和7个四元2-qudit muthukrishnan-stroud门,因此这部分的量子代价为11,硬件复杂度为7γ 4ε,所提出第三部分四元进位输出的符号表示如图8所示。

[0088]

在第四部分中,输入a=3。当输入b=1、2或3时,输出进位(c3)=1,对于其他输入组合输出进位(c3)=0,等式c3=a3.b1 a3.b2 a3.b3=a3(b1 b2 b3)描述了该部分的输出进位。第四部分四元进位输出的实现如图9所示,输入a直接输出a;输入b经过4个四元1-qudit门分别 1变换、 3变换、 3变换、 1变换后级联输出b;第一恒定输入0和输入a经过1个四元2-qudit m-s门 1变换后再和输入b级联1个四元2-qudit m-s门 2变换,再和输入b经过1个四元1-qudit门 1变换后级联1个四元2-qudit m-s门 2变换,再和输入b经过第2个四元1-qudit门 3变换后级联2个四元2-qudit m-s门 2变换,再和输入b经过第3个四元1-qudit门 3变换后级联1个四元2-qudit m-s门 2变换,再和输入b经过第4个四元1-qudit门 1变换后串联1个四元2-qudit m-s门 2变换,再和输入a串联1个四元2-qudit m-s门 1变换得到垃圾输出o;输出进位c3是由垃圾输出o的前半部分和第二恒定输入0级联1个四元2-qudit m-s门 1变换得到。该部分使用了4个四元1-qudit门和9个四元2-qudit muthukrishnan-stroud门,因此这部分的量子代价是13,硬件复杂度是9γ 4ε,所提出的第四部分四元进位输出的符号表示如图10所示。

[0089]

等式carry(进位)(a,b)=c0 c1 c2 c3描述了所提出的四元半加器的输出进位。如图6、8和10所示,可使用10个四元1-qudit门和21个四muthukrishnan-stroud门来设计所提出的四元半加器电路的输出进位,因此该电路的总量子代价是31,所提出的半加器电路进位输出的符号表示如图11所示。当输入ab=13时,最左边的 1变换应用于第二行,输入为0常量时,其余两个 1变换;当ab=22或23时,仅应用中间的 1变换;当ab=31、32或33时,仅

应用最右边的 1变换。应注意,当输入a=0时,不应用变换,并且恒定输入0将是输出进位。

[0090]

此外,根据图4,当输入a=0时,输出和为b。同样,当输入a=1时,输出和为b 1。如果输入a=2和3,输出和分别为b 2和b 3,输出和如等式果输入a=2和3,输出和分别为b 2和b 3,输出和如等式所示,可使用四元feyman门(图3)来构造四元半加器电路的输出和。

[0091]

最终,所提出的四元可逆半加器电路的整体电路实现如图12所示,目标输出是可逆半加器电路的整体电路实现如图12所示,目标输出是和c(carry(进位)(a,b)=c0 c1 c2 c3)。如果输入a和b=13、22、23、31、32或33,则输出c为1,否则输出c为0。利用前面提出的四元进位输出半加器电路级联组合再和一个四元量子feyman门级联实现四元可逆半加器电路,其中前一部分的输出作为下一部分的输入。在该电路中使用了13个1-qudit门和24个muthukrishnan stroud门,其硬件复杂度为24γ 13ε,量子代价为37,所提出的四元可逆半加器的符号表示如图13所示。

[0092]

在此基础上,本发明继续提出了四元可逆全加器、四元可逆并行加法器和四元可逆并行加/减器电路的新设计。

[0093]

四元可逆全加器电路是产生三个四元1-qudit之和的组合电路,本发明提出的四元可逆全加器电路的实现如图14所示。根据等式和等式和等式本发明在所提出的四元可逆半加器的结构中使用了两个四元可逆半加器电路,图14所示第一个方框显示了前半加器,第二个方框显示了后半加器,前半加器的输出作为后半加器的输入。该电路的目标输入是a、b和c,目标输出是s(sum)和c

out

(carry),使用了26个1qudit门和48个muthukrishnan-stroud门,因此,该电路的硬件复杂度为48γ 26ε,量子代价为74。

[0094]

四元可逆并行全加器电路是产生n个四进制数之和的组合电路。本发明提出的四元可逆并行全加器电路的实现如图15所示。根据等式等式等式等式和等式本发明使用了两个四元可逆全加器电路串联组合,使用了52个1-qudit门和96个muthukrishnan-stroud门,因此,该电路的硬件复杂度为96γ 52ε,量子代价为148。

[0095]

四元可逆并行加法/减法器电路是一种组合电路,它具有一个控制输入,用于在加法和减法运算之间进行切换。本发明提出的四元可逆并行加法/减法器电路的实现如图16所示,使用了四元可逆并行全加器电路和4的补码电路串联组合实现,其中4的补码电路是通过3的补码加1实现,3的补码是通过2-qudit ms门 3变换得到。如果找到一个数的3的补码,然后用最小有效量加1,我们就可以得到4的补码,一个qudit的3的补码等于它的z( 3)变换。四元可逆并行加法/减法器电路的输入m是控制输入,当输入m=0时,该电路将作为加法器工作;当输入m=3时,该电路将作为减法器工作。使用了52个1-qudit门和99个muthukrishnan-stroud门,因此,该电路的硬件复杂度为99γ 52ε,量子代价是151。

[0096]

工作原理

[0097]

四元可逆半加器电路是一种用于两个数相加的组合运算电路。本发明提出的四元可逆半加器电路,其目标输出是和c(carry(进位)(a,b)=c0 c1 c2 c3)。当输入a和b=13、22、23、31、32或33,则输出c为1,否则输出c为0。

[0098]

四元可逆全加器电路是产生三个四元1-qudit之和的组合电路。根据等式

progress in vlsi design and test(pp.270-280).springer berlin heidelberg中的四元可逆半加器和全加器需要4个和5个常数输入,因此,与上述2个文献中现有的设计相比,所提出的四元可逆加法器电路具有更少的常数输入。

[0108]

表7不同四元可逆加法器电路恒定输入的比较

[0109][0110]

根据表8,提出的四元可逆半加器、全加器、并行加法器和加法减法器电路分别需要2、3、5和6个垃圾输出,而文献khan,m.h.(2008).a recursive method for synthesizing quantum/reversible quaternary parallel adder/subtractor with look-ahead carry.journal of systems architecture,54(12),1113-1121中的四元可逆半加器、全加器、并行加法器和加法减法器电路分别需要3、7、14和15个垃圾输出。文献mandal,s.b.,chakrabarti,a.,&sur-kolay,s.(2012).asynthesis method for quaternary quantum logic circuits.in progress in vlsi design and test(pp.270-280).springer berlin heidelberg中的四元可逆半加器和四元可逆全加器需要4个和6个常数输入,因此与上述两篇文献中现有的设计相比,所提出的四元可逆加法器电路具有较少的垃圾输出,这是设计可逆逻辑电路的另一个主要因素。

[0111]

表8不同四元可逆加法器电路垃圾输出的比较

[0112][0113]

量子代价是设计可逆逻辑电路的主要依据之一。如表9所示,四元可逆半加器、全加器、并行加法器和加法减法器电路的量子成本分别为37、74、148和151,而在文献khan,m.h.(2008).arecursive method for synthesizing quantum/reversible quaternary parallel adder/subtractor with look-ahead carry.journal of systems architecture,54(12),1113-1121中,量子成本分别为114、304、684和687。此外,文献mandal,s.b.,chakrabarti,a.,&sur-kolay,s.(2012).asynthesis method for quaternary quantum logic circuits.in progress in vlsi design and test(pp.270-280).springer berlin heidelberg中的四元可逆半加器和全加器产生了46和128的量子开销,因此,与上述两篇文献中现有的设计相比,所提出的四元可逆加法器电路具有更少的量子开销。

[0114]

表9不同四元可逆加法器电路量子代价的比较

[0115][0116]

值得注意的是,与上述两篇文献中现有设计相比,提出的四元可逆加法器电路具有更少的量子成本、硬件复杂度和更少的恒定输入和垃圾输出,因此,参数的最小化使得可逆逻辑设计的应用更加有效。因此,可以推断,在量子成本、硬件复杂度、恒定输入和垃圾输出方面,与现有设计相比,本研究中提出的加法器电路的性能更好。

[0117]

以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。