半导体装置

1.关联申请

2.本技术享受以日本专利申请2020—157674号(申请日:2020年9月18日)为基础申请的优先权。本技术通过参照该基础申请而包含基础申请的全部内容。

技术领域

3.实施方式涉及半导体装置。

背景技术:

4.使用了gan(氮化镓)的功率器件与使用了si(硅)的mosfet(metal-oxide-semiconductor field-effect transistor)相比,具有切换的速度快、恢复损失低、输出电容的充放电快等优点。虽然利用了gan的晶体管一般大多是常通(normally on)型,但是正广泛地进行用于利用这些优点作为常断(normally off)型晶体管的开发。

5.但是,转换为这样的常断型的电路,根据其转换电路存在以下问题:不能调整栅极驱动能力、需要专用的负电源电路和专用的栅极驱动器、栅极电流环经由n型mosfet而变长,或者栅极驱动器电源的切断时的防止误开和待机电力的权衡较大。

技术实现要素:

6.实施方式提供一种能够进行常通动作的半导体装置。

7.根据一实施方式,半导体装置是使常通驱动的第1晶体管进行常断驱动的半导体装置,具有第1电路、第2电路和第1二极管。第1电路与电源电压和接地电压连接,检测所述电源电压,输出所述电源电压的转变状态。第2电路与所述电源电压、所述接地电压、所述第1电路和所述第2晶体管连接,基于所述第1电路的输出,输出与所述第1晶体管串联连接的第2晶体管的驱动电压。第1二极管的阳极与所述第1晶体管的驱动端子连接,阴极与所述第2晶体管的输出端子连接。

附图说明

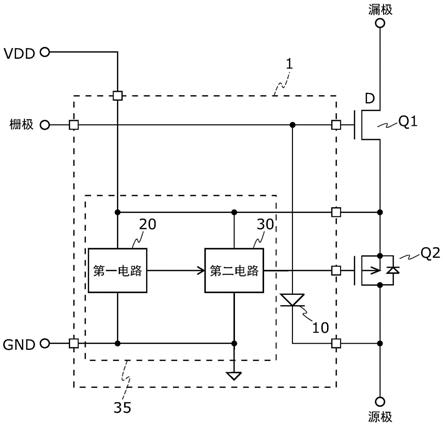

8.图1是示出一实施方式的半导体装置的一例的电路图。

9.图2是示出一实施方式的半导体装置的一安装例的电路图。

10.图3是示出一实施方式的晶体管的导通/截止状态的图。

11.图4是示出一实施方式的半导体装置的一安装例的电路图。

12.图5是示出一实施方式的晶体管的导通/截止状态的图。

13.图6是示出一实施方式的半导体装置的一安装例的电路图。

14.图7是示出一实施方式的半导体装置的一安装例的电路图。

15.图8是示出一实施方式的半导体装置的一安装例的电路图。

16.图9是示出一实施方式的半导体装置的一安装例的电路图。

17.图10是示出一实施方式的半导体装置的一例的电路图。

18.图11是示出一实施方式的半导体装置的一安装例的电路图。

19.图12是示出一实施方式的半导体装置的一安装例的电路图。

20.图13是示出一实施方式的半导体装置的一安装例的电路图。

具体实施方式

21.以下,参照附图来说明实施方式。在图中,只要没有特别的否定,则d表示漏极的位置。

22.(第一实施方式)

23.图1是示出一实施方式的半导体装置的位置例的电路图。半导体装置1是用于对常通型第1晶体管q1进行常断驱动的电路。

24.第1晶体管q1是例如使用了gan的功率器件,是进行常通动作的fet。

25.第2晶体管q2是与第1晶体管q1共有源极而串联连接的p型mosfet,根据该第2晶体管q2的特性,第1晶体管q1进行常断动作。

26.以下,将第1晶体管q1和第2晶体管q2的漏极分别定义为分别进行常断动作的晶体管的漏极和源极。半导体装置1通过控制对该源极和各个晶体管的栅极施加的电压,从而解决在对第1晶体管q1进行常断动作时的各种问题。

27.当第1晶体管q1经由半导体装置1进行常断动作时,第1晶体管q1在施加到栅极的电压下驱动,并且基于漏极端子drain和源极端子source的电位差,从源极端子source输出漏极电流。例如,外部负载连接到漏极端子drain即第1晶体管q1的漏极侧,第1晶体管q1基于施加到栅极的电压,作为进行对该负载的开关的电路而工作。

28.半导体装置1是控制第1晶体管q1的栅极、第2晶体管q2的栅极以及第2晶体管q2的漏极的电压的电路,与电源电压端子vdd、栅极电压施加端子gate以及接地端子gnd连接。该半导体装置1具有第1二极管10、第1电路20和第2电路30。另外,栅极电压施加端子gate与第1晶体管q1的栅极连接。

29.电源电压端子vdd经由半导体装置1连接到第1晶体管q1的源极和第2晶体管q2的源极所共有的节点上,将电源电压施加到半导体装置1。接地端子gnd设定半导体装置1的接地电位。另外,在附图中,在半导体装置1内与接地点连接,但不限于此方式,也可以在半导体装置1的外部接地。该接地端子gnd不限于实际接地,也可以连接到ov的电位,还可以连接到装置内的规定的接地电位上。以下说明中的接地端子gnd希望理解为都进行同样的解释。

30.第1二极管10是第1晶体管q1和第2晶体管q2的保护电路。第1二极管10的阳极与第1晶体管q1的栅极连接,并且其阴极与第2晶体管q2的漏极连接。

31.第1电路20是检测电源电压的电压的电路。第1电路20连接在电源电压端子vdd和接地端子gnd之间。该第1电路20比较电源电压的状态,更具体地说将电源电压与第1晶体管q1的阈值电压进行比较,检测其电压差,并输出到第2电路30。

32.第2电路30是低待机电力的电路,并且是输出驱动第2晶体管q2适当地工作的电压的电路。第2电路30连接到电源电压端子vdd、接地电压gnd、第1电路20和第2晶体管q2的栅极上。该第2电路30是当从第1电路20接收到检测出电压的状态的信号时,适当地使第2晶体管q2驱动的电路。另外,也可以设为将第1电路20和第2电路30合并的电路35。电路35不需要外部信号的输入。

33.在电源电压上升的情况下,第1电路20检测电压高于第1晶体管q1的阈值电压的绝对值、即第1晶体管q1成为截止状态的情况。第1回路20将该电压的变动向第2回路30输出。当接收到该信号时,第2电路30在第1晶体管q1截止之后向第2晶体管q2的栅极施加使第2晶体管q2导通的驱动电压。

34.相反,在电源电压下降的情况下,第1电路20在电源电压比第1晶体管q1的阈值电压的绝对值高的状态、即在第1晶体管q1截止的状态下,向第2电路30输出电压正在降低这一意思。当接收到该信号时,第2电路30在第1晶体管q1导通之前将使第2晶体管q2截止的驱动电压施加到第2晶体管q2的栅极。

35.通过使用这样的第1电路20和第2电路30,即使在施加到电源电压端子的电压以高的转换速率(slewrate)上升或下降的情况下,也能够避免在第1晶体管q1导通的状态下第2晶体管q2导通。另外,即使在电源电压在第1晶体管q1的阈值电压附近振动那样的电压变动的状态下,也同样能够避免第1晶体管q1和第2晶体管q2都导通的状态。并且,这样,电路35通过具有连接有电源的无源电路,从而能够不需要外部信号输入而使第1晶体管q1进行常断动作。在本实施方式中,电路35对应于第1电路20和第2电路30。

36.下面,对半导体装置1的具体安装例进行一些说明。

37.(安装例1)

38.图2是示出一安装例的半导体器件1的电路图。半导体装置1具有第1电阻200、第2二极管201、第3晶体管202、第2电阻203、第4晶体管300和第3电阻301。如图所示,作为一例,第1电阻200、第2二极管201、第3晶体管202和第2电阻203被配置为第1电路20的一部分,第4晶体管300和第3电阻301被配置为第2电路30的一部分。

39.第1电阻200连接在电源电压端子vdd与第2二极管201之间。

40.第2二极管201的阳极与接地端子gnd连接,阴极经由第1电阻200与电源电压端子vdd连接。该第2二极管201是齐纳二极管,该齐纳二极管具有与第1晶体管q1的阈值电压的绝对值为同等以上、且比电源电压的恒定值vdd(例如,施加到电源的电压的最大值、15v左右)低的齐纳电压。

41.在第2二极管201的齐纳电压以上的电压被施加到电源端子vdd的情况下,该第1电阻200和第2二极管201作为从连接节点输出恒定电压(齐纳电压)的电路而工作,否则作为基于施加到电源电压端子vdd上的电压而输出电压的电路来进行工作。

42.第3晶体管202例如是p型mosfet,源极与电源电压端子vdd连接,漏极经由第2电阻203与接地端子gnd连接,栅极与第2二极管201的阴极连接。该第3晶体管202是具有如下特性的晶体管:阈值电压是负值,其绝对值比(电源电压的恒定值vdd)-(第2二极管201的齐纳电压)低。

43.第2电阻203连接在第3晶体管202的漏极与接地端子gnd之间。根据流过第3晶体管202的电流,第3晶体管的漏极的电位由该第2电阻203的电阻值定义。例如,第1电路20输出该第3晶体管202的漏极的电压。

44.第4晶体管300例如是p型mosfet,源极与电源电压端子vdd连接,漏极经由第3电阻301与接地端子gnd连接,栅极与第3晶体管202的漏极连接。该第4晶体管300是具有如下特性的晶体管:阈值电压是负值,其绝对值比电源电压的恒定值vdd低。

45.第3电阻301设置在第4晶体管300的漏极与接地端子gnd之间。

46.根据该结构,第1电路20输出基于施加到电源电压端子vdd的电压而得到的电压,第2电路30将基于第1电路20输出的电压而得到的电压输出到第2晶体管q2的栅极。

47.这里,对在施加到电源电压端子vdd的电压变动的情况下的第1晶体管q1和第2晶体管q2的动作进行说明。

48.首先,说明施加到电源电压端子vdd的电压从0上升到电压vdd的情况。当施加到电源电压端子vdd的电压超过第1晶体管q1的阈值电压时,第1晶体管q1截止。在该定时,由于没有超过第2二极管201的齐纳电压,所以电流不流过第1电阻200,第3晶体管202的栅极-源极间电压变为0,第3晶体管202继续截止的状态。并且,由于电流没有流过第2电阻203,第4晶体管300变为导通,由其漏极电流和第3电阻301产生的电压被施加到第2晶体管q2的栅极,第2晶体管q2继续截止的状态。

49.此外,当施加到电源电压端子vdd的电压变高,并且比第2二极管201的齐纳电压高时,第3晶体管202的栅极-源极间电压变为第1电阻200的端子之间的电压。在该状态下,在施加到电源电压端子vdd的电压比齐纳电压与第3晶体管202的阈值电压的绝对值之和低的状态的情况下,第3晶体管202和第4晶体管300的状态没有变化。即,第3晶体管202为截止的状态,第4晶体管300为导通的状态,第2晶体管q2为截止的状态。

50.此外,当施加到电源电压端子vdd的电压变高,并且超过了齐纳电压与第3晶体管202的阈值电压的绝对值之和时,第3晶体管202的栅极-源极间电压低于第3晶体管202的阈值电压,第3晶体管202导通。当第3晶体管202导通时,对第4晶体管300的栅极施加由第3晶体管202的漏极电流和第2电阻203产生的电压。

51.在这种状态下,施加到第4晶体管300的栅极的电压随着施加到电源电压端子vdd的电压增高而上升,使第4晶体管300逐渐截止。当施加到电源电压端子vdd的电压超过第4晶体管300的阈值的绝对值时,第4晶体管300截止。即,施加到第2晶体管q2的栅极的电压随着施加到电源电压端子vdd的电压增高而减小,在低于第2晶体管q2的阈值电压的定时,第2晶体管q2导通。

52.若总结以上的状况,则例如当施加到电源电压端子vdd的电压从0上升到电压vdd时,首先,第1晶体管q1从导通转变为截止,经过第3晶体管202和第4晶体管300的状态的转变,第2晶体管q2从截止转变为导通。这样,能够构成为,从第1晶体管q1的截止到第2晶体管q2的导通为止产生时间裕度,这两个晶体管不同时导通。

53.接着,说明施加到电源电压端子vdd的电压从电压vdd下降到0的情况。

54.当施加到电源电压端子vdd的电压下降直到vdd-(第2二极管201的齐纳电压)即第1电阻200的端子间的电压低于第3晶体管202的阈值电压时,第3晶体管202从导通状态转变为截止状态。

55.其结果是,第4晶体管300转变为导通状态,在由第4晶体管300的漏极电流和第3电阻301形成的电压超过第2晶体管q2的阈值电压时,第2晶体管q2转变为截止状态。

56.之后,施加到电源电压端子vdd的电压进一步下降,当低于第1晶体管q1的阈值电压时,第1晶体管q1变为导通。

57.若总结以上的状况,则例如当施加到电源电压端子vdd的电压从电压vdd下降到0时,首先,经过第3晶体管202和第4晶体管300的状态的转变,第2晶体管q2从导通转变为截止,然后第1晶体管q1转变为导通状态。这样,能够构成为,从第2晶体管q2的截止到第1晶体

管q1的导通为止产生时间裕度,这两个晶体管不同时导通。

58.电源电压端子vdd所施加的电压的上升时和下降时的第2晶体管q2的接通和切断的驱动力分别由第3电阻301的值和第4晶体管300的导通电阻值决定。通过将该第3电阻301的电阻值设为大于第4晶体管300的导通电阻的值,从而第2晶体管q2的切断能够比接通更高速。

59.图3是示出图2的电路中的构成要素的电压的图。实线表示电源电压端子vdd所施加的电压,点线表示第1晶体管q1的栅极-源极间电压vgs1,虚线表示第2晶体管q2的栅极-源极间电压vgs2。

60.另外,vth1是第1晶体管q1的阈值电压,vth2是第2晶体管q2的阈值电压。vref是第1电路20中成为检测对象的电压,即第2二极管201的齐纳电压。

61.关于下方的导通(on)、截止(off),其中上段表示第1晶体管q1的导通/截止状态,下段表示第2晶体管q2的导通/截止状态。

62.如该图3所示,不管对电源电压端子vdd施加的电压是上升的情况下还是下降的情况下,在使第1晶体管q1和第2晶体管q2导通或截止的定时,都经过两个晶体管变为截止的状态进而转变。因此,这两个晶体管不会在相同的定时导通。

63.在图2的电路构成中,在第1晶体管q1为截止状态的恒常状态下,电压vdd被施加到第2晶体管q2的栅极,因此可以由低导通电阻来驱动第2晶体管q2。

64.如上所述,即使在施加到电源电压端子vdd的电压的转换速率高或施加到电源电压端子vdd的电压振动那样的情况下,也能够避免第1晶体管q1和第2晶体管q2同时成为导通状态。

65.另外,在电源电压上升后的恒常状态下,由于第4晶体管300处于截止状态,所以不流过待机电流,能够兼顾用于防止第1晶体管q1与第2晶体管q2同时导通的驱动力差和低功耗。其结果是,该电路整体的待机电力由第1电阻200和流过第2电阻203的电流定义,通过将这两个电阻值设为较大的值,整体上也能够成为低功耗。所谓将电阻值设为较大的值,例如可以是设为几十kω的电阻值,在这种情况下,电源电压在15v左右时成为~1ma左右的耗电,作为晶体管的驱动电路可以设为低消耗电流。

66.(安装例2)

67.图4是示出与上述安装例1不同的安装例2的半导体装置1的构成的电路图。半导体装置1具有第5晶体管210和第3二极管211。该第5晶体管210和第3二极管211形成图1中的第1电路20和第2电路30。

68.第5晶体管210例如是进行常通动作的晶体管,漏极与电源电压端子vdd连接,源极经由第3二极管211与接地端子gnd连接,栅极与接地端子gnd连接。该第5晶体管具有如下特征:例如阈值电压为负,其绝对值为第1晶体管q1的阈值电压的绝对值以上,并且比电压vdd低。

69.第3二极管211例如是齐纳二极管,阳极与接地端子gnd连接,阴极与第5晶体管210的源极连接。第3二极管211的齐纳电压为第1晶体管q1的阈值电压的绝对值以上,并且低于电压vdd-(第2晶体管q2的阈值电压的绝对值)。

70.第5晶体管210的源极和第3二极管211的阴极的连接节点与第2晶体管q2的栅极连接,该节点的电压成为第2晶体管q2的驱动电压。

71.这里,对施加到电源电压端子vdd的电压变动的情况下的第1晶体管q1和第2晶体管q2的动作进行说明。

72.首先,说明施加到电源电压端子vdd的电压从0上升到电压vdd的情况。当施加到电源电压端子vdd的电压超过第1晶体管q1的阈值电压时,第1晶体管q1截止。在该定时,由于第5晶体管210导通,因此第2晶体管q2维持截止状态。

73.当施加到电源电压端子vdd的电压进一步上升,并且超过第5晶体管210的阈值电压的绝对值以及第3二极管211的齐纳电压时,第5晶体管210截止,并且第2晶体管q2的栅极电压被提升为齐纳电压(或齐纳电压以下的电压)。

74.当施加到电源电压端子vdd的电压进一步上升,并且第2晶体管q2的栅极-源极间的电压低于阈值电压时,第2晶体管q2导通。

75.若总结以上的状况,则例如当施加到电源电压端子vdd的电压从0上升到电压vdd时,首先,第1晶体管q1从导通转变为截止,通过第5晶体管210和第3二极管211,第2晶体管q2的栅极上成为第3二极管211的齐纳电压(或齐纳电压以下的电压),然后第2晶体管q2从截止转变为导通。这样,能够构成为,从第1晶体管q1的截止到第2晶体管q2的导通为止产生时间裕度,这两个晶体管不同时导通。

76.接着,说明施加到电源电压端子vdd的电压从电压vdd下降到0的情况。

77.首先,当施加到电源电压端子vdd的电压低于第5晶体管210的阈值电压时,第5晶体管210导通。由于第5晶体管210导通,通过漏极电流,第2晶体管q2的栅极的电位超过阈值电压,第2晶体管q2截止。

78.之后,施加到电源电压端子vdd的电压超过第1晶体管q1的阈值,从而第1晶体管q1变为导通。

79.若总结以上的状况,则例如当施加到电源电压端子vdd的电压从电压vdd下降到0时,首先,第5晶体管210变为导通,随之第2晶体管q2从导通转变为截止。之后,第1晶体管q1从截止转变为导通。这样,能够构成为,从第1晶体管q1的截止到第2晶体管q2的导通为止产生时间裕度,这两个晶体管不同时导通。

80.施加到电源电压端子vdd的电压的上升时和下降时的第2晶体管q2的接通和切断的驱动力分别由第5晶体管210的导通电阻值和第3二极管211的动作电阻决定。通过使第3二极管211的动作电阻构成为具有比第5晶体管210的导通电阻大的值,第2晶体管q2的切断能够比接通更高速。

81.图5是示出图4的电路中的构成要素的电压的图。实线表示施加到电源电压端子vdd的电压,点线表示第1晶体管q1的栅极-源极间电压vgs1,虚线表示第2晶体管q2的栅极-源极间电压vgs2。

82.另外,vth1是第1晶体管q1的阈值电压,vth2是第2晶体管q2的阈值电压。vref是第3二极管211的齐纳电压。

83.关于下方的接通(on)、切断(off),其中上段表示第1晶体管q1的导通/截止状态,下段表示第2晶体管q2的导通/截止状态。

84.如该图5所示,不管施加到电源电压端子vdd的电压是上升还是下降,使第1晶体管q1和第2晶体管q2导通或截止的定时,都经过双方的晶体管成为截止的状态而进行转变。因此,这两个晶体管不会在相同的定时成为导通。

85.在第1晶体管q1成为截止状态的恒常状态下,电源电压端子vdd的电压与第3二极管211的齐纳电压之差的电压被施加到第2晶体管q2的栅极,因此,与图2的电路结构相比,在图4的电路构成中,第2晶体管q2的导通电阻变高。

86.另外,在vdd电压上升后的恒常状态下,由于第1晶体管q1处于截止状态,所以不流过待机电流,能够同时兼顾用于防止导通的驱动力差和低功耗。与安装例1相比,具备如下特征:由于用于接通第2晶体管q2的施加电压变低,因此第2晶体管q2的导通电阻有增大的趋势,但其电路部件比安装例1少,且实现更低的功耗。

87.如上所述,即使在施加到电源电压端子vdd的电压的转换速率高或施加到电源电压端子vdd的电压振动那样的情况下,也能够避免第1晶体管q1和第2晶体管q2同时成为导通状态。

88.另外,在电源电压上升后的恒常状态下,由于第5晶体管210处于截止状态,因此不流过待机电流,能够兼顾用于防止第1晶体管q1和第2晶体管q2同时导通的驱动力差与低功耗。图4所示的结构与图2所示的结构相比,用于导通第2晶体管q2的施加电压变低,因此第2晶体管q的导通电阻有增大的趋势,但是能够实现比安装例1少的电路部件和更低功耗。

89.(安装例3)

90.图6是示出安装例3的半导体器件1的构成的电路图。第1电路20具有基准电压生成电路21和电压比较电路22。第2电路30具有输出缓冲器31。

91.基准电压生成电路21生成基准电压vref。图6示出了一个例子,但不限于该例子,只要是作为能够输出基准电压vref的电路而构成的电路即可。

92.电压比较电路22将基准电压生成电路21所生成的电压与施加到电源电压端子vdd的电压进行比较。例如,相对于一般的比较器的输入,通过输入了基准电压生成电路21的输出和将电源电压端子vdd和接地端子gnd之间以规定比例分配的多个电阻间的电压而被形成。电压比较电路22检测比第1晶体管q1的阈值电压的绝对值大的电压,并输出到输出缓冲器31。

93.输出缓冲器31控制电压比较电路22的输出,并施加到第2晶体管q2的栅极。

94.图7是示出一安装例的输出缓冲器31的电路。输出缓冲器31例如具有第6晶体管m1、第7晶体管m2、第4电阻r1和第5电阻r2。

95.第6晶体管m1是p型mosfet,源极与电源电压端子vdd连接,栅极与电压比较电路22的输出连接。

96.第7晶体管m2是n型mosfet,源极与接地端子gnd连接,栅极与电压比较电路22的输出连接。

97.第4电阻r1连接在第6晶体管m1的漏极与输出端之间。

98.第5电阻r2连接在第7晶体管m2的漏极与输出端之间。

99.第5电阻r2的电阻值具有比第4电阻r1的电阻值更大的值。通过这样设定第4电阻r1和第5电阻r2的电阻值,能够使接通第2晶体管q2时的电流路径中的电阻值大于切断第2晶体管q2时的电流路径中的电阻值。其结果是,能够使第2晶体管q2的切断的驱动力比接通的驱动力高。

100.通过这样的电阻的构成,即使在施加到电源电压端子vdd的电压的转换速率高的情况或电压振动那样的情况下,也能够避免第1晶体管q1和第2晶体管q2同时导通。

101.图8是示出输出缓冲器31的另一安装例的电路。输出缓冲器31例如具有第8晶体管m3和第9晶体管m4。

102.第8晶体管m3是p型mosfet,源极与电源电压端子vdd连接,栅极与电压比较电路22的输出连接。

103.第9晶体管m4是n型mosfet,源极与接地端子gnd连接,栅极与电压比较电路22的输出连接,漏极与第8晶体管m8的漏极连接。

104.如上述可知,第8晶体管m3和第9晶体管m4形成cmos(compulementary mosfet:互补型mos)。在本安装例中,作为一例,使第8晶体管m3的栅极宽度形成得比第9晶体管m4的栅极宽度宽。

105.通过形成这样的cmos,能够使第2晶体管q2接通的路径中的导通电阻值大于第二晶体管q2切断的路径中的导通电阻值。其结果是,能够使第2晶体管q2的切断的驱动力比第2晶体管q2的接通的驱动力高。

106.通过这样的构成,即使在施加到电源电压端子vdd的电压的转换速率高的情况或电压振动那样的情况下,也能够避免第1晶体管q1和第2晶体管q2同时导通。

107.图9是示出电压比较电路22的另一安装例的图。如该图所示,也可以使用迟滞比较器作为电压比较电路。

108.(安装例4)

109.图10是示出安装例3的半导体器件1的结构的电路图。除了图1的第1电路20和第2电路30之外,半导体装置1还具有第3电路40。

110.第3电路40是如下的电路,即:在vdd电源启动前且漏极端子drain-源极端子source之间施加了电压的情况下,兼顾防止向电容器50的充电电流和防止施加到第1晶体管q1的栅极的过电压,该电容器50在半导体装置1的外部连接在电源电压与接地电压之间。

111.当向电容器50充电时,基于该被充电的电压,使电流流过半导体装置1的各构成元件。例如,该电流按照漏极端子drain、第1晶体管q1、电源电压端子vdd、电容器50、接地端子gnd、第3电路40内的进行第1晶体管q1的切换的元件的体二极管、第1二极管10、源极端子source的顺序流过。第3电路40防止该电流。

112.图11是示出第3电路40的一安装例的电路图。第3电路40具有第1开关400、第2开关401、第6电阻402、第4二极管403和第5二极管404。

113.第1开关400例如是p型mosfet,源极与电源电压端子vdd连接,栅极与反相器输出连接,反相器输入与栅极电压施加端子gate连接。

114.第2开关401例如是n型mosfet,源极与接地端子gnd连接,栅极与反相器输出连接,反相器输入与栅极电压施加端子gate连接。

115.第6电阻402的一端连接到第1开关400的漏极,另一端连接到第1晶体管q1的栅极。第6电阻402作为控制第1晶体管q1的栅极电流的栅极电阻而工作。

116.第4二极管403的阳极与第1二极管10的阳极和第1晶体管q1的栅极连接,阴极与电源电压端子vdd连接。

117.第5二极管404的阳极与第1开关400的漏极连接,并且经由第6电阻402与第1晶体管q1的栅极连接,其阴极与第2开关401的漏极连接。

118.根据该构成,能够通过连接在第2开关401与第2开关400以及第6电阻402之间的第

5二极管404来防止用于切断第1晶体管q1的第2开关401的体二极管中通过的电流。另外,通过该第5二极管404的连接,当第1晶体管q1的栅极电压成为比接地电压gnd低的电压时,虽然不能通过第2开关401的体二极管而钳位,但是能够通过将第4二极管403连接到第1晶体管q1的栅极和电源电压端子vdd之间来防止第1晶体管q1的栅极的过电压。

119.如上所述,根据本安装例的第3电路40,能够兼顾防止向电容器50的充电电流和防止第1晶体管q1的栅极电压的过电压。

120.(安装例5)

121.图12是示出第3电路40的另一安装例的电路图。第3电路40具有第1开关400、第2开关401、第6电阻402、第4二极管403和第6二极管405。

122.第1开关400例如是p型mosfet,源极与电源电压端子vdd连接,栅极与反相器的输出连接,反相器的输入与栅极电压施加端子gate连接。

123.第2开关401例如是n型mosfet,源极与接地端子gnd连接,栅极与反相器的输出连接,反相器的输入与栅极电压施加端子gate连接。

124.第6电阻402的一端与第1开关400的漏极连接,另一端与第1晶体管q1的栅极连接。第6电阻402作为控制第1晶体管q1的栅极电流的栅极电阻而工作。

125.第4二极管403的阳极与第1二极管10的阳极和第1晶体管q1的栅极连接,阴极与电源电压端子vdd连接。

126.第6二极管405的阳极与第1晶体管q1的栅极连接,阴极与第2开关401的漏极连接。

127.能够通过连接在第2开关401和第1晶体管q1的栅极之间的第6二极管405来防止用于切断第1晶体管q1的第2开关401的体二极管中通过的电流。在安装例4中,由于栅极电阻处于第1晶体管q1的接通和切断这双方的栅极电流路径中,因此难以独立地调整驱动力,但是根据本安装例,能够通过第6二极管405单体使第1晶体管q1的接通和切断的栅极电流路径独立来调整驱动力,并且,与上述安装例同样地能够防止电容器的充电电流。

128.(安装例6)

129.图13是示出第3电路40的另一安装例的电路图。第3电路40具有第1开关400、第2开关401、第6电阻402、第4二极管403和第3开关406。

130.第1开关400例如是p型mosfet,源极与电源电压端子vdd连接,栅极与反相器输出连接,反相器输入与栅极电压施加端子gate连接。

131.第2开关401例如是n型mosfet,源极与第3开关406背对背连接,栅极与反相器输出连接,反相器输入与栅极电压施加端子gate连接。

132.第6电阻402的一端与第1开关400的漏极连接,另一端与第1晶体管q1的栅极连接。第6电阻402作为控制第1晶体管q1的栅极电流的栅极电阻而工作。

133.第4二极管403的阳极与第1二极管10的阳极和第1晶体管q1的栅极连接,阴极与电源电压端子vdd连接。

134.第3开关406例如是n型mosfet,漏极与接地端子gnd连接,栅极与栅极电压施加端子gate连接,源极与第2开关401的源极背对背连接。

135.通过连接在第2开关401和接地电位之间的第3开关406形成双向开关,从而能够防止在切断第1晶体管q1的第2开关401中通过的电流。在上述安装例5中,在切断第1晶体管q1的情况下,切断的驱动力仅减弱栅极电流路径中的第6二极管405的正向电压的量,但是,根

据本安装例的结构,在将第1晶体管q1切断的情况下,由于该电压是第3开关406的导通电阻与栅极电流之积,因此通过使用低导通电阻的开关元件作为第3开关406,从而能够增强切断的驱动力。

136.由此,即使在第1晶体管q1的漏极-源极之间被施加了高电压转换速率的情况下,也通过将由第2开关401和第3开关406形成的切断电流路径的阻抗抑制得低,从而能够防止第1晶体管q1的误导通。

137.根据以上说明的各实施方式,能够不增大用于驱动第1晶体管q1的栅极电流的回路(loop)地、适当地进行第1晶体管q1和第2晶体管q2的控制、使常通驱动的第1晶体管q1成为常断驱动。根据该半导体装置1,能够形成应对高耐压并且安全地进行进行常断驱动的开关,所述高耐压针对外部负荷例如施加140v~400v左右这样的高电压的情况。

138.另外,在上述各实施方式中,第2晶体管q2虽然被配置在半导体装置1的外部,但是在半导体装置1中也可以具有第2晶体管q2。在这种情况下,半导体器件1可以具有与第1晶体管q1的栅极和源极连接,并且输出第1晶体管q1的漏极电流的输出端。

139.对本发明的几个实施方式进行了说明,但这些实施方式是作为例子提示的,并不意欲限定发明的范围。这些新的实施方式能够以其他各种形态实施,在不脱离发明主旨的范围内,能够进行各种省略、替换、变更。这些实施方式及其变形包含在发明的范围及主旨中,并且包含在权利要求记载的发明及其等同范围中。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。