1.本发明的技术涉及一种成像元件、摄像装置、成像元件的工作方法及程序。

背景技术:

::2.国际公开第2014/007004号中公开了一种固体成像元件,其具备:信号处理部,包含将从像素阵列部的各像素读出到信号线的模拟像素信号数字化的ad转换器,以比帧速率快的第1速度传送数字化后的像素数据;存储器部,保持从信号处理部传送的像素数据;数据处理部,以比第1速度慢的第2速度从存储器部读出像素数据;及控制部,在从存储器部读出像素数据时,进行停止与信号线连接的电流源的动作及信号处理部的至少ad转换器的动作的控制。3.在国际公开第2014/007004号中记载的固体成像元件中,信号处理部、存储器部、数据处理部及控制部具有形成在与形成有像素阵列部的芯片不同的至少一个芯片上,并且形成有像素阵列部的芯片和其他至少一个芯片层叠而成的结构。并且,在国际公开第2014/007004号中记载的固体成像元件中,数据处理部具有对存储器部指定列地址的解码器和读出所指定的地址的像素数据的读出放大器,通过读出放大器及解码器从存储器部读出像素数据。4.国际公开第2013/145765号中公开了一种摄像单元,其具备:摄像部,具有包含一个以上的像素的第1组和包含一个以上与构成第1组的像素不同的像素的第2组;及控制部,在使第1组执行1次电荷积蓄的期间,使第2组执行与第1组不同次数的电荷积蓄而输出各个像素信号。5.在国际公开第2013/145765号中记载的摄像单元中,包含摄像部的成像芯片与包含处理像素信号的处理电路的信号处理芯片通过层叠结构电连接。并且,包含存储像素信号的像素存储器的存储器芯片也通过层叠结构电连接。并且,在国际公开第2013/145765号中记载的摄像单元中,控制部按照来自外部电路的针对包含第2组的组群中的指定组的交付请求,从像素存储器读出指定组的像素信号并交付给图像处理部。并且,国际公开第2013/145765号中记载的摄像单元具备按照交付请求传输像素信号的数据传送接口。利用数据传送接口的像素信号的传输采用双数据速率方式、地址指定方式、短脉冲传送方式、总线方式、串行方式中的至少任一种。此外,在国际公开第2013/145765号中记载的摄像单元中,在针对多次电荷积蓄的各个像素信号存储于像素存储器的情况下,控制部将各个像素信号交付给图像处理部。技术实现要素:6.本发明的技术所涉及的一个实施方式提供能够从成像元件选择性地获取需要的图像数据的成像元件、摄像装置、成像元件的工作方法及程序。7.用于解决技术课题的手段8.本发明的技术所涉及的第1方式是一种成像元件,其包含:存储部,存储通过拍摄而得到的图像数据,且内置于成像元件;控制部,控制图像数据向存储部的存储,将图像数据的属性信息存储于存储部,且内置于成像元件;输出部,输出存储于存储部的图像数据,且内置于成像元件;及接收部,接收与属性信息有关的指示,输出部输出与由接收部接收到的指示对应的属性信息。9.本发明的技术所涉及的第2方式是第1方式所涉及的成像元件,其中,输出部在由接收部接收到指示的定时输出属性信息。10.本发明的技术所涉及的第3方式是第1方式或第2方式所涉及的成像元件,其中,指示是来自外部的帧同步信号。11.本发明的技术所涉及的第4方式是第1方式至第3方式中任一项所述的成像元件,其中,输出部输出与存储于存储部的图像数据中的最新的图像数据有关的属性信息。12.本发明的技术所涉及的第5方式是第4方式所涉及的成像元件,其中,输出部在由接收部接收到指示的定时输出与最新的图像数据有关的属性信息。13.本发明的技术所涉及的第6方式是第1方式至第5方式中任一项所述的成像元件,其中,输出部能够输出多个图像数据各自的属性信息,属性信息由输出部按照摄像顺序输出。14.本发明的技术所涉及的第7方式是第1方式至第6方式中任一项所述的成像元件,其中,属性信息是包含地址、图像尺寸、摄像时刻及摄像条件中的至少一个的信息。15.本发明的技术所涉及的第8方式是第1方式至第7方式中任一项所述的成像元件,其中,在伴随下一次摄像而从存储部中擦除图像数据的情况下,从输出部输出的属性信息是包含表示伴随下一次摄像而从存储部中擦除图像数据的擦除信息的信息。16.本发明的技术所涉及的第9方式是第8方式所涉及的成像元件,其中,在从存储部中擦除图像数据的情况下,控制部从存储部中擦除与作为存储部内的成为擦除对象的图像数据的擦除对象图像数据有关的属性信息,从存储部中擦除擦除对象图像数据。17.本发明的技术所涉及的第10方式是第1方式至第9方式中任一项所述的成像元件,其包含压缩图像数据的压缩电路,控制部将规定的帧数的图像数据存储于存储部,将通过由压缩电路压缩图像数据而得到的压缩图像数据存储于存储部,且将与压缩图像数据有关的属性信息和能够确定图像数据被压缩的压缩确定信息与压缩图像数据建立对应关联。18.本发明的技术所涉及的第11方式是第10方式所涉及的成像元件,其中,在存储部中存储压缩图像数据的情况下,从输出部输出的属性信息是包含表示预定在存储部中存储压缩图像数据的压缩预定信息的信息。19.本发明的技术所涉及的第12方式是第10方式或第11方式所涉及的成像元件,其中,从输出部输出的属性信息是包含能够确定压缩图像信息的压缩形式的信息的信息。20.本发明的技术所涉及的第13方式是第1方式至第12方式中任一项所述的成像元件,其中,指示包含基于输出部的属性信息的输出量,输出部以输出量输出属性信息。21.本发明的技术所涉及的第14方式是第13方式所涉及的成像元件,其中,输出量由图像数据的帧数规定。22.本发明的技术所涉及的第15方式是第1方式至第14方式中任一项所述的成像元件,其还具备接收部,该接收部接收从位于成像元件的后级的后级电路发送的属性信息,控制部根据由接收部接收到的属性信息从存储部获取图像数据,并使输出部向后级电路输出所获取的图像数据。23.本发明的技术所涉及的第16方式是第1方式至第15方式中任一项所述的成像元件,其中,输出部具有第1输出部及第2输出部,第1输出部输出图像数据,第2输出部输出属性信息。24.本发明的技术所涉及的第17方式是第1方式至第16方式中任一项所述的成像元件,其是至少将光电转换元件和存储部单芯片化而成的。25.本发明的技术所涉及的第18方式是第17方式所述的成像元件,其中,成像元件是存储部层叠于光电转换元件上的层叠型成像元件。26.本发明的技术所涉及的第19方式是一种摄像装置,其包含:第1方式至第18方式中任一项所述的成像元件;及控制装置,进行使显示部显示基于由输出部输出的图像数据的图像的控制及将由输出部输出的图像数据存储于存储装置的控制中的至少一者。27.本发明的技术所涉及的第20方式是一种成像元件的工作方法,该成像元件内置有存储通过拍摄而得到的图像数据的存储部,该成像元件的工作方法包括:控制图像数据向存储部的存储;将图像数据的属性信息存储于存储部;输出存储于存储部的图像数据;接收与属性信息有关的指示;及输出与所接收到的指示对应的属性信息。28.本发明的技术所涉及的第21方式是一种程序,其用于使计算机执行处理,该计算机适用于内置有存储通过拍摄而得到的图像数据的存储器的成像元件,该处理包括:控制图像数据向存储部的存储;将图像数据的属性信息存储于存储部;输出存储于存储部的图像数据;接收与属性信息有关的指示;及输出与所接收到的指示对应的属性信息。附图说明29.图1是表示实施方式所涉及的摄像装置的外观的一例的立体图。30.图2是表示图1所示的摄像装置的背面侧的外观的一例的后视图。31.图3是表示实施方式所涉及的摄像装置的结构的一例的框图。32.图4是表示实施方式所涉及的摄像装置中包含的摄像装置主体的电气系统的硬件结构的一例的框图。33.图5是用于说明实施方式所涉及的摄像装置中包含的成像元件的帧速率的概念图。34.图6是表示实施方式所涉及的成像元件的层叠结构的一例的概念图。35.图7是表示实施方式所涉及的成像元件中包含的存储器的结构的一例的框图。36.图8是表示实施方式所涉及的摄像装置中包含的成像元件的电气系统的硬件结构的一例的框图,是用于由成像元件进行摄像,且从成像元件输出属性信息的方式例的说明的框图。37.图9是表示由实施方式所涉及的成像元件进行的摄像工序及输出工序的内容的一例的概念图。38.图10是表示实施方式所涉及的摄像装置中包含的成像元件中的处理内容的一例的时序图。39.图11a是表示在第1帧~第4帧从成像元件的输出i/f输出的属性信息的内容的一例的概念图。40.图11b是表示在第5帧及第6帧从成像元件的输出i/f输出的属性信息的内容的一例的概念图。41.图12是表示实施方式所涉及的摄像装置中包含的成像元件的电气系统的硬件结构的一例的框图,是用于从成像元件输出数字图像数据的方式例的说明的框图。42.图13是表示实施方式所涉及的属性信息输出处理的流程的一例的流程图。43.图14是表示实施方式所涉及的数据擦除处理的流程的一例的流程图。44.图15是表示在对数字图像数据进行压缩处理的情况下向存储器存储数字图像数据及压缩图像数据的处理内容的一例的时序图。45.图16a是表示在对第4帧以后的数字图像数据进行压缩处理时的第1帧~第4帧从成像元件的输出i/f输出的属性信息的内容的一例的概念图。46.图16b是表示在对第4帧以后的数字图像数据进行压缩处理时的第5帧及第6帧从成像元件的输出i/f输出的属性信息的内容的一例的概念图。47.图17a是表示包含表示是否预定伴随下一次摄像而压缩1帧量的数字图像数据的压缩预定标志的属性信息,即在第1帧~第4帧从成像元件的输出i/f输出的属性信息的内容的一例的概念图。48.图17b是表示包含表示是否预定伴随下一次摄像而压缩1帧量的数字图像数据的压缩预定标志的属性信息,即在第5帧~第6帧从成像元件的输出i/f输出的属性信息的内容的一例的概念图。49.图18a是表示包含表示是否预定伴随下一次摄像而压缩1帧量的数字图像数据的压缩预定标志且包含压缩形式确定信息的属性信息,即在第4帧~第5帧从成像元件的输出i/f输出的属性信息的内容的一例的概念图。50.图18b是表示包含表示是否预定伴随下一次摄像而压缩1帧量的数字图像数据的压缩预定标志且包含压缩形式确定信息的属性信息,即在第6帧从成像元件的输出i/f输出的属性信息的内容的一例的概念图。51.图19是表示在由成像元件的接收i/f接收到与属性信息有关的指示(例如,垂直同步信号)的定时由成像元件的输出i/f输出属性信息时的成像元件中的处理内容的一例的时序图。52.图20是表示在按每一帧输出的属性信息是与1帧量的数字图像数据有关的属性信息时的在第1帧~第6帧输出的属性信息的内容的一例的概念图。53.图21是表示在按每一帧输出的属性信息是与1帧量的数字图像数据有关的属性信息时的在第1帧~第6帧输出的属性信息,即不包含擦除标志及压缩预定标志的属性信息的内容的一例的概念图。54.图22是表示实施方式所涉及的属性信息输出处理的流程的变形例的流程图。55.图23是表示实施方式所涉及的摄像装置中包含的成像元件的电气系统的硬件结构的变形例的框图。56.图24是表示实施方式所涉及的智能器件的背面侧的外观的一例的后视立体图。57.图25是表示图24所示的智能器件的前面侧的外观的一例的前视立体图。58.图26是表示从存储有实施方式所涉及的成像元件侧程序的存储介质将成像元件侧程序安装于成像元件内的计算机中的方式的一例的概念图。具体实施方式59.以下,按照附图对本发明的技术所涉及的摄像装置的实施方式的一例进行说明。60.首先,对在以下说明中使用的术语进行说明。61.cpu是指“centralprocessingunit:中央处理单元”的简称。gpu是指“graphicsprocessingunit:图形处理单元”的简称。ram是指“randomaccessmemory:随机存取存储器”的简称。rom是指“readonlymemory:只读存储器”的简称。dram是指“dynamicrandomaccessmemory:动态随机存取存储器”的简称。sram是指“staticrandomaccessmemory:静态随机存取存储器”的简称。lsi是指“large-scaleintegratedcircuit:大规模集成电路”的简称。asic是指“applicationspecificintegratedcircuit:专用集成电路”的简称。pld是指“programmablelogicdevice:可编程逻辑器件”的简称。fpga是指“field-programmablegatearray:现场可编程门阵列”的简称。soc是指“system-on-a-chip:片上系统”的简称。ssd是指“solidstatedrive:固态驱动器”的简称。usb是指“universalserialbus:通用串行总线”的简称。hdd是指“harddiskdrive:硬盘驱动器”的简称。eeprom是指“electricallyerasableandprogrammablereadonlymemory:带电可擦可编程只读存储器”的简称。ccd是指“chargecoupleddevice:电荷耦合元件”的简称。cmos是指“complementarymetaloxidesemiconductor:互补型金属氧化物半导体”的简称。el是指“electro-luminescence:电致发光”的简称。a/d是指“analog/digital:模拟/数字”的简称。i/f是指“interface:接口”的简称。ui是指“userinterface:用户界面”的简称。lvds是指“lowvoltagedifferentialsignaling:低压差分信号”的简称。pci-e是指“peripheralcomponentinterconnectexpress:外围组件互连标准”的简称。sata是指“serialadvancedtechnologyattachment:串行高级技术附件”的简称。slvs-ec是指“scalablelowsignalingwithembeddedclock:带有嵌入式时钟的可扩展低压信号”的简称。mipi是指“mobileindustryprocessorinterface:移动行业处理器接口”的简称。fps是指“framepersecond:每秒帧数”的简称。fifo是指“firstin,firstout:先进先出”的简称。mpeg是指“movingpictureexpertsgroup:动态影像专家小组”的简称。jpeg是指“jointphotographicexpertsgroup:联合图像专家小组”的简称。tiff是指“taggedimagefileformat:标签图像文件格式”的简称。bmp是指“bitmap:位图”的简称。png是指“portablenetworkgraphics:便携式网络图形”的简称。gif是指“graphicsinterchangeformat:图形交换格式”的简称。62.作为一例,如图1所示,摄像装置10是镜头可换式且省略了反光镜的数码相机。摄像装置10具备摄像装置主体12和可更换地安装于摄像装置主体12上的可更换镜头14。另外,在此,作为摄像装置10的一例,举出了镜头可换式且省略了反光镜的数码相机,但本发明的技术并不限定于此,摄像装置10可以是镜头固定式等其他种类的数码相机。63.在摄像装置主体12上设置有成像元件38。在可更换镜头14安装于摄像装置主体12上的情况下,表示被摄体的被摄体光透过可更换镜头14在成像元件38上成像,由成像元件38生成表示被摄体的图像的图像数据(例如,参考图4及图5)。64.在摄像装置主体12上设置有混合式取景器(注册商标)16。这里所说的混合式取景器16是指例如选择性地使用光学取景器(以下,称为“ovf”)及电子取景器(以下,称为“evf”)的取景器。另外,ovf是指“opticalviewfinder:光学取景器”的简称。并且,evf是指“electronicviewfinder:电子取景器”的简称。65.在摄像装置主体12的前表面上设置有取景器切换杆18。通过使取景器切换杆18沿箭头sw方向转动,从而切换能够用ovf视觉辨认的光学像和能够用evf视觉辨认的电子图像即即时预览图像。这里所说的“即时预览图像”是指基于通过由成像元件38拍摄而得到的图像数据的显示用动态图像。即时预览图像通常也被称为实时取景图像。在摄像装置主体12的上表面设置有释放按钮20及转盘23。在设定摄像系统的动作模式及回放系统的动作模式等时操作转盘23,由此在摄像装置10中,选择性地设定拍摄模式和回放模式作为动作模式。66.释放按钮20作为摄像准备指示部及摄像指示部而发挥功能,并能够检测摄像准备指示状态和摄像指示状态这两个阶段的按压操作。摄像准备指示状态例如是指从待机位置被按下至中间位置(半按位置)的状态,摄像指示状态是指被按下至超过中间位置的最终按下位置(全按位置)的状态。另外,以下,将“从待机位置被按下至半按位置的状态”称为“半按状态”,将“从待机位置被按下至全按位置的状态”称为“全按状态”。67.作为一例,如图2所示,在摄像装置主体12的背面上设置有触摸面板显示器24、指示键27及取景器目镜部30。68.触摸面板显示器24具备显示器26及触摸面板28(也参考图4)。作为显示器26的一例,可举出液晶显示器。显示器26也可以不是液晶显示器,而是有机el显示器或无机el显示器等其他种类的显示器。另外,显示器26及evf是本发明的技术所涉及的“显示部(显示器)”的一例。关于evf的显示,由于等同于显示器26的显示,因此省略以后的记载,在本说明书中,能够将对显示器26的显示替换为对evf的显示。69.显示器26显示图像及字符信息等。显示器26用于显示当摄像装置10为拍摄模式时通过连续拍摄而得到的即时预览图像。并且,显示器26也用于显示当被赋予静止图像用拍摄的指示时通过拍摄而得到的静止图像。此外,显示器26也用于显示当摄像装置10为回放模式时的回放图像及菜单画面等。70.触摸面板28是透射型触摸面板,与显示器26的显示区域的表面重叠。触摸面板28通过检测基于手指或手写笔等指示体的接触来接收来自用户的指示。71.指示键27接收各种指示。这里所说的“各种指示”例如是指能够选择各种菜单的菜单画面的显示指示、一个或多个菜单的选择指示、选择内容的确定指示、选择内容的擦除指示、放大、缩小及帧传送等各种指示等。72.作为一例,如图3所示,可更换镜头14具有成像透镜40。成像透镜40具备物镜40a、聚焦透镜40b及光圈40c。物镜40a、聚焦透镜40b及光圈40c从被摄体侧(物体侧)到摄像装置主体12侧(像侧),沿着光轴l1,按照物镜40a、聚焦透镜40b及光圈40c的顺序配置。聚焦透镜40b及光圈40c通过受到来自马达等驱动源(省略图示)的动力而进行工作。即,聚焦透镜40b及光圈40c根据所施加的动力沿着光轴l1移动。并且,光圈40c通过根据所施加的动力而进行工作来调节曝光。73.摄像装置主体12具备后级电路13、ui系统器件17、机械快门41及成像元件38。后级电路13是位于成像元件38的后级的电路。后级电路13具有控制器15及信号处理电路34。控制器15与ui系统器件17、信号处理电路34及成像元件38连接,控制摄像装置10的整个电气系统。74.成像元件38具备具有受光面42a的光电转换元件42。在本实施方式中,成像元件38是cmos图像传感器。并且,在此,作为成像元件38而例示出cmos图像传感器,但本发明的技术并不限定于此,例如即使成像元件38是ccd图像传感器等其他种类的图像传感器,本发明的技术也成立。75.机械快门41通过受到来自马达等驱动源(省略图示)的动力而进行工作。在可更换镜头14安装于摄像装置主体12的情况下,表示被摄体的被摄体光透过成像透镜40,经由机械快门41在受光面42a上成像。76.ui系统器件17是向用户提示信息或接收来自用户的指示的器件。控制器15从ui系统器件17获取各种信息,并控制ui系统器件17。77.成像元件38与控制器15连接,通过在控制器15的控制下拍摄被摄体,生成表示被摄体的图像的图像数据。78.成像元件38与信号处理电路34连接。信号处理电路34是lsi,具体而言,是包含asic及fpga的器件。控制器15从信号处理电路34获取各种信息,并控制成像元件38。成像元件38在控制器15的控制下,将由光电转换元件42生成的图像数据输出到信号处理电路34。79.信号处理电路34对从成像元件38输入的图像数据进行各种信号处理。由信号处理电路34进行的各种信号处理例如包括白平衡调整、清晰度调整、伽马校正、颜色空间转换处理及色差校正等公知的信号处理。80.另外,由信号处理电路34进行的各种信号处理也可以由信号处理电路34和成像元件38分散进行。即,也可以设为使成像元件38的处理电路110承担由信号处理电路34进行的各种信号处理中的至少一部分。81.另外,在本实施方式中,作为信号处理电路34例示了包含asic及fpga的器件,但本发明的技术并不限定于此,信号处理电路34也可以是包含asic、fpga和/或pld的器件。82.并且,信号处理电路34也可以是包含cpu、储存器(storage)及存储器(memory)的计算机。这里所说的“储存器”是指ssd或hdd等非易失性存储装置,这里所说的“存储器)”是指dram或sram等易失性存储装置。计算机中包含的cpu可以是单个,也可以是多个。并且,可以使用gpu来代替cpu。并且,信号处理电路34可以通过硬件结构及软件结构的组合来实现。83.作为一例,如图4所示,控制器15具备cpu15a、储存器15b、存储器15c、输出i/f15d及接收i/f15e。cpu15a、储存器15b、存储器15c、输出i/f15d及接收i/f15e经由总线100连接。在图4所示的例子中,为了便于图示,作为总线100图示了1条总线,但总线100包括数据总线、地址总线及控制总线等。84.储存器15b存储各种参数及各种程序。储存器15b是非易失性存储装置。在此,作为储存器15b的一例,采用了eeprom,但并不限于此,也可以是掩模rom、hdd或ssd等。存储器15c是易失性存储装置。存储器15c中临时存储各种信息。存储器15c被cpu15a用作工作存储器。在此,作为存储器15c的一例,采用了dram,但并不限于此,也可以是sram等其他种类的易失性存储装置。另外,cpu15a是本发明的技术所涉及的“控制装置”的一例,储存器15b是本发明的技术所涉及的“存储装置”的一例。85.储存器15b中存储有各种程序。cpu15a从储存器15b读出各种程序,将所读出的各种程序扩展到存储器15c。cpu15a根据扩展到存储器15c的各种程序来控制整个摄像装置10。86.输出i/f15d与成像元件38连接。cpu15a经由输出i/f15d控制成像元件38。例如,cpu15a经由输出i/f15d对成像元件38提供规定进行摄像的定时的摄像定时信号,由此控制由成像元件38进行的摄像定时。87.接收i/f15e与信号处理电路34连接。cpu15a经由接收i/f15e在与信号处理电路34之间进行各种信息的授受。88.从成像元件38向信号处理电路34输入图像数据。信号处理电路34对从成像元件38输入的图像数据进行各种信号处理(详细内容将后述)。信号处理电路34将进行各种信号处理的图像数据输出到接收i/f15e。接收i/f15e接收来自信号处理电路34的图像数据,并将所接收到的图像数据传送到cpu15a。89.外部i/f104与总线100连接。外部i/f104是由电路构成的通信器件。另外,在此,作为外部i/f104采用了由电路构成的器件,但这仅为一例。外部i/f104也可以是包括asic、fpga和/或pld的器件。并且,外部i/f104可以通过硬件结构及软件结构的组合来实现。90.作为外部i/f104的一例有usb接口,能够与其连接存储卡控制器、智能器件、个人计算机、服务器、usb存储器和/或存储卡等外部装置(省略图示)。外部i/f104控制cpu15a与外部装置之间的各种信息的授受。另外,与外部i/f104直接或间接连接的外部装置,即智能器件、个人计算机、服务器、usb存储器和/或存储卡等外部装置是本发明的技术所涉及的“存储装置”的一例。91.ui系统器件17具备触摸面板显示器24及接收器件84。显示器26及触摸面板28连接于总线100。因此,cpu15a使显示器26显示各种信息,并按照由触摸面板28接收到的各种指示进行动作。92.接收器件84具备硬键部25。硬键部25是多个硬键,具有释放按钮20(参考图1)、转盘23(参考图1及图2)及指示键22(参考图2)。硬键部25连接于总线100,cpu15a获取由硬键部25接收到的指示,按照所获取的指示进行动作。93.作为一例,如图5所示,从控制器15向成像元件38输入摄像定时信号。摄像定时信号包括垂直同步信号及水平同步信号。垂直同步信号是规定从光电转换元件42的每1帧的图像数据的读出开始定时的同步信号。水平同步信号是规定从光电转换元件42的每个水平线的图像数据的读出开始定时的同步信号。成像元件38按照根据从控制器15输入的垂直同步信号确定的帧速率,从光电转换元件42读出图像数据。另外,垂直同步信号是本发明的技术所涉及的“与属性信息有关的指示”及“来自外部的帧同步信号”的一例,控制器15是本发明的技术所涉及的“外部”的一例。94.在图5所示的例子中,作为成像元件38的帧速率,示出了在期间t内从光电转换元件42进行8帧量的读出的帧速率。作为具体的帧速率的一例,可举出120fps,但并不限于此,可以是超过120fps的帧速率(例如,240fps),也可以是小于120fps的帧速率(例如,60fps)。95.作为一例,如图6所示,在成像元件38中内置有光电转换元件42、处理电路110及存储器112。成像元件38是将光电转换元件42、处理电路110及存储器112单芯片化而成的成像元件。即,光电转换元件42、处理电路110及存储器112被封装在一起。在成像元件38中,处理电路110及存储器112层叠于光电转换元件42上。具体而言,光电转换元件42及处理电路110通过铜等具有导电性的凸块(省略图示)彼此电连接,处理电路110及存储器112也通过铜等具有导电性的凸块(省略图示)彼此电连接。96.处理电路110例如是lsi。存储器112是写入定时与读出定时不同的存储器。在此,作为存储器112的一例,采用了dram。97.处理电路110是包括asic及fpga的器件,按照上述控制器15的指示控制整个成像元件38。另外,在此,举出了处理电路110通过包含asic及fpga的器件来实现的例子,但本发明的技术并不限定于此,例如也可以是包含asic、fpga和/或pld的器件。并且,作为处理电路110,也可以采用包含cpu、作为非易失性存储装置的eeprom等储存器、及作为易失性存储装置的ram等存储器的计算机。计算机中包含的cpu可以是单个,也可以是多个。使用gpu来代替cpu。并且,处理电路110可以通过硬件结构及软件结构的组合来实现。98.光电转换元件42具有配置成矩阵状的多个光电二极管。作为多个光电二极管的一例,可举出“4896×3265”像素量的光电二极管。99.在光电转换元件42中包含的各光电二极管中配置有滤色器。滤色器包含最有助于用于得到亮度信号的与g(绿色)对应的g滤色器、与r(红色)对应的r滤色器及与b(蓝色)对应的b滤色器。100.光电转换元件42具有r像素、g像素及b像素。r像素是与配置有r滤色器的光电二极管对应的像素,g像素是与配置有g滤色器的光电二极管对应的像素,b像素是与配置有b滤色器的光电二极管对应的像素。r像素、g像素及b像素在行方向(水平方向)及列方向(垂直方向)上分别以规定的周期性配置。在本实施方式中,r像素、g像素及b像素以与x-trans(注册商标)排列对应的周期性排列。另外,在此,例示了x-trans排列,但本发明的技术并不限定于此,r像素、g像素及b像素的排列也可以是拜耳排列或蜂窝排列等。101.成像元件38具有所谓的电子快门功能,在控制器15的控制下,通过启动电子快门功能而控制光电转换元件42内的各光电二极管的电荷积蓄时间。电荷积蓄时间是指所谓的快门速度。102.在成像元件38中,以滚动快门方式选择性地进行静止图像用拍摄和即时预览图像用拍摄。静止图像用拍摄通过启动电子快门功能且使机械快门(省略图示)工作来实现,即时预览图像用拍摄通过不使机械快门工作而启动电子快门功能来实现。另外,在此,例示出滚动快门方式,但本发明的技术并不限于此,可以适用全局快门方式来代替滚动快门方式。103.另外,存储器112是本发明的技术所涉及的“存储部(存储器)”的一例。在本实施方式中,作为存储器112采用了dram,但即使存储器112是其他种类的存储器,本发明的技术也成立。并且,成像元件38是本发明的技术所涉及的“层叠型成像元件”的一例。104.作为一例,如图7所示,存储器112具有第1存储区域112a、第2存储区域112b、第3存储区域112c、第4存储区域112d、第5存储区域112e及第6存储区域112f。另外,在此,为了便于说明,例示了6个存储区域,但这仅为一例,存储器112只要具有能够存储多个帧量的图像数据的多个存储区域即可。105.在图7所示的例子中,对第1存储区域112a、第2存储区域112b、第3存储区域112c、第4存储区域112d、第5存储区域112e及第6存储区域112f分别赋予存储器112内的地址。对第1存储区域112a赋予地址“0x00000000”。对第2存储区域112b赋予地址“0x00100000”。对第3存储区域112c赋予地址“0x00200000”。对第4存储区域112d赋予地址“0x00300000”。对第5存储区域112e赋予地址“0x00400000”。对第6存储区域112f赋予地址“0x00500000”。106.作为一例,如图8所示,处理电路110具备接收i/f110d1及输出i/f110d2。在此,接收i/f110d1是本发明的技术所涉及的“接收部”及“接收部”的一例,输出i/f110d2是本发明的技术所涉及的“输出部(输出接口)”的一例。另外,接收部例如表示接受器(acceptor),接收部例如表示接收器(receiver)。107.控制器15的输出i/f15d与处理电路110的接收i/f110d1连接,并将摄像定时信号输出到接收i/f110d1。接收i/f110d1接收从输出i/f15d输出的摄像定时信号。108.信号处理电路34具备接收i/f34a及输出i/f34b。接收i/f34a与成像元件38的输出i/f110d2连接。处理电路110的输出i/f110d2将图像数据等各种信息(以下,也简称为“各种信息”)输出到信号处理电路34的接收i/f34a,接收i/f34a接收从输出i/f110d2输出的各种信息。信号处理电路34根据需要对由接收i/f34a接收到的各种信息实施信号处理。输出i/f34b与控制器15的接收i/f15e连接,并将各种信息输出到控制器15的接收i/f15e。接收i/f15e接收从输出i/f34b输出的各种信息。109.在成像元件38中,处理电路110除了接收i/f110d1及输出i/f110d2以外,还具备读出电路110a、数字处理电路110b、控制电路110c、图像处理电路110e。另外,控制电路110c是本发明的技术所涉及的“控制部(控制电路)”的一例。110.读出电路110a分别与光电转换元件42、数字处理电路110b及控制电路110c连接。数字处理电路110b连接于控制电路110c。控制电路110c分别与存储器112、接收i/f110d1、输出i/f110d2及图像处理电路110e连接。111.作为一例,如图8所示,上述图像数据大致分为模拟图像数据70a和数字图像数据70b。另外,以下,为了便于说明,在不需要区分说明模拟图像数据70a和数字图像数据70b的情况下,不标注符号而称为“图像数据”。112.处理电路110的接收i/f110d1及输出i/f110d2分别是具有fpga的通信器件。并且,控制器15的输出i/f15d及接收i/f15e分别也是具有fpga的通信器件。此外,信号处理电路34的接收i/f34a及输出i/f34b分别也是具有fpga的通信器件。113.处理电路110的接收i/f110d1与控制器15的输出i/f15d之间按照pci-e的连接标准连接。并且,处理电路110的输出i/f110d2与信号处理电路34的接收i/f34a之间也按照pci-e的连接标准连接。此外,信号处理电路34的输出i/f34b与控制器15的接收i/f15e之间也按照pci-e的连接标准连接。另外,以下,在不需要区分说明接收i/f110d1、输出i/f110d2、接收i/f34a、输出i/f34b、接收i/f15e及输出i/f15d的情况下,不标注符号而称为“通信i/f”。114.在此,作为通信i/f采用了由电路(asic、fpga和/或pld等)构成的通信器件,但这仅为一例。通信i/f也可以是包含cpu、eeprom等储存器、及ram等存储器的计算机。在该情况下,计算机中包含的cpu可以是单个,也可以是多个。使用gpu来代替cpu。并且,通信i/f可以通过硬件结构及软件结构的组合来实现。115.接收i/f110d1接收从控制器15的输出i/f15d1输出的摄像定时信号,并将所接收到的摄像定时信号传送到控制电路110c。116.读出电路110a在控制电路110c的控制下控制光电转换元件42,从光电转换元件42读出模拟图像数据70a。从光电转换元件42的模拟图像数据70a的读出按照从控制器15输入到处理电路110的摄像定时信号进行。117.具体而言,首先,接收i/f110d1从控制器15接收摄像定时信号,并将所接收到的摄像定时信号传送到控制电路110c。接着,控制电路110c将从接收i/f110d1传送的摄像定时信号传送到读出电路110a。即,垂直同步信号及水平同步信号被传送到读出电路110a。并且,读出电路110a按照从控制电路110c传送的垂直同步信号开始从光电转换元件42以帧单位读出模拟图像数据70a。并且,读出电路110a按照从控制电路110c传送的水平同步信号开始以水平线单位的模拟图像数据70a的读出。118.读出电路110a对从光电转换元件42读出的模拟图像数据70a进行模拟信号处理。模拟信号处理包括噪声消除处理及模拟增益处理等公知的处理。噪声消除处理是消除由光电转换元件42中包含的像素之间的特性的偏差引起的噪声的处理。模拟增益处理是对模拟图像数据70a施加增益的处理。并且,读出电路110a对模拟图像数据70a进行相关双采样。在由读出电路110a对模拟图像数据70a进行相关双采样后,模拟图像数据70a输出到数字处理电路110b。119.数字处理电路110b具备a/d转换器110b1。a/d转换器110b1对模拟图像数据70a进行a/d转换。120.数字处理电路110b对从读出电路110a输入的模拟图像数据70a进行数字信号处理。数字信号处理例如包括相关双采样、基于a/d转换器110b1的a/d转换及数字增益处理。121.对于从读出电路110a输入的模拟图像数据70a,由a/d转换器110b1进行a/d转换,由此模拟图像数据70a被数字化,作为raw数据得到数字图像数据70b。并且,通过数字处理电路110b对数字图像数据70b进行数字增益处理。数字增益处理是指对数字图像数据70b施加增益的处理。如此通过进行数字信号处理而得到的数字图像数据70b由数字处理电路110b输出到控制电路110c。122.控制电路110c将从数字处理电路110b输入的数字图像数据70b输出到图像处理电路110e。图像处理电路110e对从控制电路110c输入的数字图像数据70b进行图像处理,将图像处理后的数字图像数据70b输出到控制电路110c。这里所说的“图像处理”例如可举出去马赛克处理和/或数字间隔剔除处理等。123.去马赛克处理是根据与滤色器的排列对应的马赛克图像对每个像素计算所有颜色信息的处理。例如,若成像元件38是适用rgb3色滤色器的成像元件,则根据rgb马赛克图像对每个像素进行所有rgb的颜色信息。数字间隔剔除处理是以行单位间隔剔除图像数据中包含的像素的处理。线单位例如是指水平线单位和/或垂直线单位。124.存储器112是能够存储多个帧的数字图像数据的存储器。存储器112具有像素单位的存储区域(参考图7),数字图像数据70b通过控制电路110c以像素单位存储于存储器112中的对应的存储区域中。控制电路110c将从图像处理电路110e输入的数字图像数据70b存储于存储器112。125.控制电路110c能够随机访问存储器112。控制电路110c根据来自控制器15的指示,获取存储于存储器112中的数字图像数据70b的属性信息。属性信息是表示存储于存储器112中的数字图像数据70b的属性的信息。在此,属性信息例如是指包含地址、图像尺寸、摄像时刻、曝光时间、成像元件灵敏度及擦除标志的信息。126.地址是指存储器112中以帧单位确定数字图像数据70b的存储位置的信息(记录地址)。图像尺寸是指1帧量的数字图像数据70b的水平线方向的尺寸(水平尺寸)及1帧量的数字图像数据70b的垂直线方向的尺寸(垂直尺寸)。摄像时刻是指由成像元件38进行摄像的时刻(例如,年月日时分秒)。这里所说的“进行摄像的时刻”例如是指1帧量的数字图像数据70b存储于存储器112中的时刻。但是,这仅为一例,进行摄像的时刻也可以是完成1帧量的曝光的时刻或完成1帧量的a/d转换的时刻等。127.曝光时间是指得到1帧量的数字图像数据70b所需的曝光时间。成像元件灵敏度例如是指光电转换元件42的灵敏度(传感器增益)。擦除标志是指表示伴随下一次摄像而是否从存储器112中擦除数字图像数据70b的标志。在擦除标志为关闭的情况下,不伴随下一次摄像而从存储器112中擦除数字图像数据70b,在擦除标志为开启的情况下,伴随下一次摄像而从存储器112中擦除数字图像数据70b。作为从存储器112擦除的数字图像数据70b的一例,可举出从存储器112擦除的1帧量的数字图像数据70b。128.另外,曝光时间及成像元件灵敏度是本发明的技术的“摄像条件”的一例,开启状态的擦除标志是本发明的技术所涉及的“擦除信息”的一例。129.在此,作为本发明的技术所涉及的“摄像条件”的一例,举出了曝光时间及成像元件灵敏度,但本发明的技术并不限定于此,代替曝光时间和/或成像元件,或除了曝光时间和/或成像元件以外,也可以采用成像透镜40的种类、被摄体距离、焦距、视角和/或抖动校正的有无等。130.控制电路110c根据来自控制器15的与属性信息有关的指示生成属性信息,将所生成的属性信息输出到输出i/f110d2。与属性信息有关的指示例如是指控制器15请求处理电路110输出属性信息的指示。在本实施方式中,作为与属性信息有关的指示的一例,采用了垂直同步信号。输出i/f110d2将从控制电路110c输入的属性信息输出到信号处理电路34。131.具体而言,首先,接收i/f110d1从控制器15接收垂直同步信号作为与属性信息有关的指示。接着,控制电路110c生成与存储于存储器112中的数字图像数据70b中最早存储的数字图像数据70b有关的属性信息,作为与由接收i/f110d1接收到的垂直同步信号对应的属性信息。并且,输出i/f110d2将由控制电路110c生成的属性信息输出到信号处理电路34。132.作为一例,如图9所示,由成像元件38进行的工序包括摄像工序和输出工序。133.在摄像工序中,依次进行曝光、模拟图像数据70a的读出、对光电转换元件42的复位、模拟信号处理、数字信号处理、第1次存储、数字图像数据70b的获取、图像处理及第2次存储。134.由光电转换元件42进行曝光。由读出电路110a进行模拟图像数据70a的读出、对光电转换元件42的复位及模拟信号处理。模拟图像数据70a的读出以垂直同步信号由接收i/f110d1接收为条件而开始。由光电转换元件42进行曝光的期间是未进行模拟图像数据70a的读出及对光电转换元件42的复位的期间。对光电转换元件42的复位是指消除光电转换元件42内的各像素的残余电荷的动作。在从进行对光电转换元件42的基于读出电路110a的上一次复位到进行读出为止的期间进行基于光电转换元件42的曝光。135.由数字处理电路110b进行数字信号处理。第1次存储是指通过进行数字信号处理而得到的数字图像数据70b向存储器112的存储。数字图像数据70b的获取是指从存储器112获取数字图像数据70b。由控制电路110c进行第1次存储及数字图像数据70b的获取。由图像处理电路110e对由控制电路110c获取的数字图像数据70b进行图像处理。第2次存储是指进行了图像处理的数字图像数据70b向存储器112的存储。由控制电路110c进行第2次存储。136.在输出工序中,进行属性信息的生成和属性信息的输出。属性信息的生成是指与存储于存储器112中的数字图像数据70b有关的每1帧的属性信息的生成。由控制电路110c进行属性信息的生成。属性信息的输出是指利用输出i/f110d2输出由控制电路110c生成的属性信息。137.图10示出第1帧(1f)~第6帧(6f)的图像数据的读出到向存储器112的存储为止的流程和每1帧的属性信息的输出定时的一例。图10所示的1f~6f的“f”是指“frame:帧”的简称。在图10所示的例子中,为了便于说明,示出了分别在存储器112的第1存储区域112a、第2存储区域112b、第3存储区域112c、第4存储区域112d、第5存储区域112e及第6存储区域112f中存储1帧量的数字图像数据70b的方式。138.作为一例,如图10所示,每当由接收i/f110d1接收垂直同步信号时,开始从光电转换元件42读出1帧量的模拟图像数据70a。在图10所示的例子中,由接收i/f110d1依次接收第1次~第6次垂直同步信号,开始第1帧~第6帧模拟图像数据70a的读出。139.对从光电转换元件42的第1行的水平线到最终行的水平线按照水平同步信号按每一行进行模拟图像数据70a的读出,当对每一行的读出结束时,结束读出的水平线的各像素被复位。模拟图像数据70a被转换为数字图像数据70b,按照所读出的模拟图像数据70a的帧的顺序(摄像顺序),数字图像数据70b以1帧单位可区分地且以fifo方式存储于存储器112。具体而言,对第1存储区域112a、第2存储区域112b、第3存储区域112c、第4存储区域112d、第5存储区域112e及第6存储区域112f依次以1帧单位覆盖保存最新的数字图像数据70b。覆盖保存按照第1存储区域112a、第2存储区域112b、第3存储区域112c、第4存储区域112d、第5存储区域112e及第6存储区域112f的顺序反复进行。140.输出i/f110d2将与存储于存储器112中的数字图像数据70b中的最新的数字图像数据70b有关的属性信息输出到信号处理电路34。在该情况下,首先,控制电路110c每当在由接收i/f110d1接收到垂直同步信号的定时完成1帧量的最新的数字图像数据70b向存储器112的存储时,生成与存储于存储器112中的数字图像数据70b中的最新的数字图像数据70b有关的属性信息。并且,输出i/f110d2将由控制电路110c生成的属性信息输出到信号处理电路34。141.作为一例,如图11a及图11b所示,各帧(在图11a及图11b所示的例子中,第1帧~第6帧)的属性信息由输出i/f110d2输出到信号处理电路34。并且,信号处理电路34将所输入的属性信息输出到控制器15。142.作为一例,如图11a所示,在第1帧输出的属性信息是与存储于第1存储区域112a中的数字图像数据70b有关的属性信息。在图11a所示的例子中,作为与存储于第1存储区域112a中的数字图像数据70b有关的属性信息的一例,可举出包含第1存储区域112a的地址、第1存储区域112a内的数字图像数据70b的水平尺寸、第1存储区域112a内的数字图像数据70b的垂直尺寸、与第1存储区域112a内的数字图像数据70b有关的摄像时刻、与第1存储区域112a内的数字图像数据70b有关的曝光时间、与第1存储区域112a内的数字图像数据70b有关的成像元件灵敏度及擦除标志_关闭的信息。在此,“擦除标志_关闭”是指表示擦除标志为关闭的状态的信息。143.在第2帧输出的属性信息是与存储于第1存储区域112a中的数字图像数据70b有关的属性信息及与存储于第2存储区域112b中的数字图像数据70b有关的属性信息。在图11a所示的例子中,作为与存储于第2存储区域112b中的数字图像数据70b有关的属性信息的一例,可举出包含第2存储区域112b的地址、第2存储区域112b内的数字图像数据70b的水平尺寸、第2存储区域112b内的数字图像数据70b的垂直尺寸、与第2存储区域112b内的数字图像数据70b有关的摄像时刻、与第2存储区域112b内的数字图像数据70b有关的曝光时间、与第2存储区域112b内的数字图像数据70b有关的成像元件灵敏度及擦除标志_关闭的信息。144.在第3帧输出的属性信息是与存储于第1存储区域112a中的数字图像数据70b有关的属性信息、与存储于第2存储区域112b中的数字图像数据70b有关的属性信息及与存储于第3存储区域112c中的数字图像数据70b有关的属性信息。在图11a所示的例子中,作为与存储于第3存储区域112c中的数字图像数据70b有关的属性信息的一例,可举出包含第3存储区域112c的地址、第3存储区域112c内的数字图像数据70b的水平尺寸、第3存储区域112c内的数字图像数据70b的垂直尺寸、与第3存储区域112c内的数字图像数据70b有关的摄像时刻、与第3存储区域112c内的数字图像数据70b有关的曝光时间、与第3存储区域112c内的数字图像数据70b有关的成像元件灵敏度及擦除标志_关闭的信息。145.在第4帧输出的属性信息是与存储于第1存储区域112a中的数字图像数据70b有关的属性信息、与存储于第2存储区域112b中的数字图像数据70b有关的属性信息、与存储于第3存储区域112c中的数字图像数据70b有关的属性信息及与存储于第4存储区域112d中的数字图像数据70b有关的属性信息。在图11a所示的例子中,作为与存储于第4存储区域112d中的数字图像数据70b有关的属性信息的一例,可举出包含第4存储区域112d的地址、第4存储区域112d内的数字图像数据70b的水平尺寸、第4存储区域112d内的数字图像数据70b的垂直尺寸、与第4存储区域112d内的数字图像数据70b有关的摄像时刻、与第4存储区域112d内的数字图像数据70b有关的曝光时间、与第4存储区域112d内的数字图像数据70b有关的成像元件灵敏度及擦除标志_关闭的信息。在此,在第4帧输出的属性信息中包含的与存储于第1存储区域112a中的数字图像数据70b有关的属性信息内的“擦除标志_关闭”由控制电路110c变更为“擦除标志_开启”。“擦除标志_开启”是指表示擦除标志为开启的状态的信息。146.如此,与存储于第1存储区域112a中的数字图像数据70b有关的属性信息内的“擦除标志_关闭”由控制电路110c变更为“擦除标志_开启”。这表示从输出i/f110d2在第4帧输出的属性信息是包含表示伴随下一次摄像而从存储器112中擦除第1存储区域112a内的数字图像数据70b的信息的信息。147.当在第4帧输出的属性信息中包含“擦除标志_开启”时,伴随下一次摄像(例如,第5帧摄像开始的时刻或当前时刻到第5帧摄像开始为止的期间),由控制电路110c擦除与作为存储器112内的成为擦除对象的数字图像数据70b的擦除对象图像数据有关的属性信息,即与第1存储区域112a有关的属性信息。并且,数字图像数据70b也由控制电路110c从第1存储区域112a擦除。在该情况下,例如,伴随下一次摄像,首先,由控制电路110c擦除与第1存储区域112a有关的属性信息,接着,由控制电路110c从第1存储区域112a擦除数字图像数据70b。另外,在此,举出了擦除数字图像数据70b及属性信息的方式例,但本发明的技术并不限定于此,“擦除”实际上除了擦除数字图像数据70b及属性信息以外,还包括释放区域,并能够将其覆盖的处理。148.作为一例,如图11b所示,在第5帧输出的属性信息是与存储于第2存储区域112b中的数字图像数据70b有关的属性信息、与存储于第3存储区域112c中的数字图像数据70b有关的属性信息、与存储于第4存储区域112d中的数字图像数据70b有关的属性信息及与存储于第5存储区域112e中的数字图像数据70b有关的属性信息。在图11b所示的例子中,作为与存储于第5存储区域112e中的数字图像数据70b有关的属性信息的一例,可举出包含第5存储区域112e的地址、第5存储区域112e内的数字图像数据70b的水平尺寸、第5存储区域112e内的数字图像数据70b的垂直尺寸、与第5存储区域112e内的数字图像数据70b有关的摄像时刻、与第5存储区域112e内的数字图像数据70b有关的曝光时间、与第5存储区域112e内的数字图像数据70b有关的成像元件灵敏度及擦除标志_关闭的信息。在此,在第5帧输出的属性信息中包含的与存储于第2存储区域112b中的数字图像数据70b有关的属性信息内的“擦除标志_关闭”由控制电路110c变更为“擦除标志_开启”。149.如此,当与存储于第2存储区域112b中的数字图像数据70b有关的属性信息内的“擦除标志_关闭”由控制电路110c变更为“擦除标志_开启”时,伴随下一次摄像(例如,第6帧摄像开始的时刻或当前时刻到第6帧摄像开始为止的期间),由控制电路110c擦除与作为存储器112内的成为擦除对象的数字图像数据70b的擦除对象图像数据有关的属性信息,即与第2存储区域112b有关的属性信息。并且,数字图像数据70b也由控制电路110c从第2存储区域112b擦除。在该情况下,例如,伴随下一次摄像,首先,由控制电路110c擦除与第2存储区域112b有关的属性信息,接着,由控制电路110c从第2存储区域112b擦除数字图像数据70b。150.在第6帧输出的属性信息是与存储于第3存储区域112c中的数字图像数据70b有关的属性信息、与存储于第4存储区域112d中的数字图像数据70b有关的属性信息、与存储于第5存储区域112e中的数字图像数据70b有关的属性信息及与存储于第6存储区域112f中的数字图像数据70b有关的属性信息。在图11b所示的例子中,作为与存储于第6存储区域112f中的数字图像数据70b有关的属性信息的一例,可举出包含第6存储区域112f的地址、第6存储区域112f内的数字图像数据70b的水平尺寸、第6存储区域112f内的数字图像数据70b的垂直尺寸、与第6存储区域112f内的数字图像数据70b有关的摄像时刻、与第6存储区域112f内的数字图像数据70b有关的曝光时间、与第6存储区域112f内的数字图像数据70b有关的成像元件灵敏度及擦除标志_关闭的信息。在此,在第6帧输出的属性信息中包含的与存储于第3存储区域112c中的数字图像数据70b有关的属性信息内的“擦除标志_关闭”由控制电路110c变更为“擦除标志_开启”。151.如此,当与存储于第3存储区域112c中的数字图像数据70b有关的属性信息内的“擦除标志_关闭”由控制电路110c变更为“擦除标志_开启”时,伴随下一次摄像(例如,第7帧摄像开始的时刻或当前时刻到第7帧摄像开始为止的期间),由控制电路110c擦除与作为存储器112内的成为擦除对象的数字图像数据70b的擦除对象图像数据有关的属性信息,即与第3存储区域112c有关的属性信息。并且,数字图像数据70b也由控制电路110c从第3存储区域112c擦除。在该情况下,例如,伴随下一次摄像,首先,由控制电路110c擦除与第3存储区域112c有关的属性信息,接着,由控制电路110c从第3存储区域112c擦除数字图像数据70b。152.如此,当属性信息按每一帧由输出i/f110d2发送到信号处理电路34时,信号处理电路34将属性信息传送到控制器15。从信号处理电路34传送到控制器15的属性信息由控制器15的接收i/f15e接收。控制器15根据需要从由接收i/f15e接收到的属性信息中获取地址。153.作为一例,如图12所示,控制器15经由输出i/f15d将从属性信息获取的地址输出到成像元件38的接收i/f110d1。成像元件38的接收i/f110d1接收来自控制器15的地址。控制电路110c按照由接收i/f110d1接收到的地址从存储器112获取数字图像数据70b,并使输出i/f110d2向信号处理电路34输出所获取的数字图像数据70b。154.另外,在此,举出从控制器15的输出i/f15d向成像元件38输出地址的方式例进行了说明,但本发明的技术并不限定于此。例如,控制器15还可以具备发送i/f,可以从发送i/f向成像元件38发送地址。155.并且,在此,举出由接收i/f110d1接收地址的方式例进行了说明,但本发明的技术并不限定于此。例如,成像元件38还可以具备接收i/f,可以由成像元件38的接收i/f接收从控制器15发送的地址。156.接着,对摄像装置10的作用进行说明。157.首先,参考图13对由成像元件38的处理电路110执行的属性信息输出处理的流程进行说明。158.在图13所示的属性信息输出处理中,首先,在步骤st10中,控制电路110c判定是否由接收i/f110d1接收到垂直同步信号。在步骤st10中,在接收i/f110d1未接收到垂直同步信号的情况下判定为“否”,属性信息输出处理转移到步骤st22。在步骤st10中,在由接收i/f110d1接收到垂直同步信号的情况下判定为“是”,属性信息输出处理转移到步骤st12。159.在步骤st12中,控制电路110c将通过拍摄而得到的数字图像数据70b存储于存储器112,然后,属性信息输出处理转移到步骤st14。160.在步骤st14中,控制电路110c生成关于在步骤st12中存储于存储器112中的数字图像数据70b的属性信息,保持所生成的属性信息,然后,属性信息输出处理转移到步骤st16。161.在步骤st16中,控制电路110c判定通过进行下一次摄像,数字图像数据70b能够存储于存储器112内的帧数是否到达上限数。在本实施方式中,存储器112具有第1存储区域112a、第2存储区域112b、第3存储区域112c、第4存储区域112d、第5存储区域112e及第6存储区域112f这6个存储区域,因此这里所说的“上限数”是“6”。另外,上限数并不限定于此,只要是能够存储于存储器112中的帧数即可。162.在步骤st16中,在通过进行下一次摄像,数字图像数据70b能够存储于存储器112内的帧数未到达上限数的情况下判定为“否”,属性信息输出处理转移到步骤st20。在步骤st16中,在通过进行下一次摄像,数字图像数据70b能够存储于存储器112内的帧数到达上限数的情况下判定为“是”,属性信息输出处理转移到步骤st18。163.在步骤st18中,控制电路110c将存储于存储器112中的全部帧量的数字图像数据70b中的关于最早存储于存储器112中的1帧量的数字图像数据70b的属性信息中包含的擦除标志开启,然后,属性信息输出处理转移到步骤st20。164.在步骤st20中,控制电路110c使输出i/f110d2向信号处理电路34输出在当前时刻保持的属性信息,然后,属性信息输出处理转移到步骤st22。165.在步骤st22中,控制电路110c判定是否满足结束属性信息输出处理的条件(以下,称为“属性信息输出处理结束条件”)。作为属性信息输出处理结束条件的一例,可举出由接收器件84(参考图4)接收到结束属性信息输出处理的指示的条件。在步骤st22中,在不满足属性信息输出处理结束条件的情况下判定为“否”,属性信息输出处理转移到步骤st10。在步骤st22中,在满足属性信息输出处理结束条件的情况下判定为“是”,属性信息输出处理结束。166.接着,参考图14对由成像元件38的处理电路110执行的数据擦除处理的流程进行说明。167.在图14所示的数据擦除处理中,首先,在步骤st50中,控制电路110c判定是否由输出i/f110d2输出属性信息。在步骤st50中,在输出i/f110d2未输出属性信息的情况下判定为“否”,数据擦除处理转移到步骤st60。在步骤st50中,在由输出i/f110d2输出属性信息的情况下判定为“是”,数据擦除处理转移到步骤st52。168.在步骤st52中,控制电路110c判定是否由接收i/f110d1接收到垂直同步信号。在步骤st52中,在接收i/f110d1未接收到垂直同步信号的情况下判定为“否”,再次进行步骤st52的判定。在步骤st52中,在由接收i/f110d1接收到垂直同步信号的情况下判定为“是”,属性信息输出处理转移到步骤st54。169.在步骤st54中,控制电路110c判定是否保持擦除标志被开启的属性信息。在步骤st54中,在未保持擦除标志被开启的属性信息的情况下判定为“否”,数据擦除处理转移到步骤st60。在步骤st54中,在保持擦除标志被开启的属性信息的情况下判定为“是”,数据擦除处理转移到步骤st56。170.在步骤st56中,控制电路110c首先根据在当前时刻保持的所有的属性信息中擦除标志被开启的属性信息中包含的地址来确定数字图像数据70b。接着,控制电路110c擦除在当前时刻保持的所有的属性信息中擦除标志被开启的属性信息。并且,控制电路110c从存储器112中擦除根据地址确定的数字图像数据70b,然后,数据擦除处理转移到步骤st60。171.在步骤st60中,控制电路110c判定是否满足结束数据擦除处理的条件(以下,称为“数据擦除处理结束条件”)。作为数据擦除处理结束条件的一例,可举出由接收器件84(参考图4)接收到结束数据擦除处理的指示的条件。在步骤st60中,在不满足数据擦除处理结束条件的情况下判定为“否”,数据擦除处理转移到步骤st50。在步骤st60中,在满足数据擦除处理结束条件的情况下判定为“是”,数据擦除处理结束。172.如以上说明,在摄像装置10中,由接收i/f110d1接收与属性信息有关的指示,由输出i/f110d2将与所接收到的指示对应的属性信息输出到后级电路13。由此,后级电路13能够通过使用属性信息请求成像元件38提供数字图像数据70b。因此,后级电路13能够从成像元件38选择性地获取需要的数字图像数据70b。并且,与同时输出数字图像数据70b和属性信息中包含的至少一部分这两者的情况相比,能够减少利用成像元件38的输出所需的耗电量。173.并且,在摄像装置10中,由控制电路110c生成与来自控制器15的垂直同步信号对应的属性信息,由输出i/f110d2将所生成的属性信息输出到信号处理电路34。因此,后级电路13能够从成像元件38获取属性信息,而无需新生成与垂直同步信号不同的信号来使用。174.并且,在摄像装置10中,由输出i/f110d2输出与存储于存储器112中的所有的数字图像数据70b中的最新的数字图像数据70b有关的属性信息。因此,后级电路13能够获取与最新的数字图像数据70b有关的属性信息。175.并且,在摄像装置10中,由输出i/f110d2输出与在由接收i/f110d1接收到垂直同步信号的定时的最新的数字图像数据70b有关的属性信息。因此,后级电路13能够获取与在由接收i/f110d1接收到垂直同步信号的定时的最新的数字图像数据70b有关的属性信息。176.并且,在摄像装置10中,输出i/f110d2能够输出多个帧的数字图像数据70b各自的属性信息,属性信息由输出i/f110d2按照摄像顺序输出。因此,后级电路13能够从成像元件38按拍摄顺序获取数字图像数据70b。177.并且,在摄像装置10中,作为属性信息,采用了包含地址、图像尺寸、摄像时刻及摄像条件的信息。因此,与属性信息中不包含地址、图像尺寸、摄像时刻及摄像条件中的任一个的情况相比,能够扩大后级电路13从成像元件38获取的数字图像数据70的用途的范围。178.并且,在摄像装置10中,在伴随下一次摄像而从存储器112中擦除数字图像数据70b的情况下,从输出i/f110d2输出的属性信息中包含标志被开启的擦除标志。因此,能够防止由后级电路13指示输出未存储于存储器112中的数字图像数据70b。179.并且,在摄像装置10中,在伴随下一次摄像而从存储器112中擦除数字图像数据70b的情况下,由控制电路110c从存储器112中擦除擦除标志被开启的属性信息,由控制电路110c从存储器112中擦除根据擦除标志被开启的属性信息中包含的地址来确定的数字图像数据70b。因此,能够在不同的定时擦除属性信息和与属性信息有关的数字图像数据70b这两者。180.并且,在摄像装置10中,由接收i/f110d1接收从控制器15发送的属性信息。在控制电路110c中,根据由接收i/f110d1接收到的属性信息从存储器112获取数字图像数据70b,由输出i/f110d2将所获取的数字图像数据70b输出到信号处理电路34。因此,成像元件38能够将后级电路13请求的数字图像数据70b输出到后级电路13。181.并且,在摄像装置10中,作为成像元件38,采用了将光电转换元件42、处理电路110及存储器112单芯片化而成的成像元件。由此,与未将光电转换元件42、处理电路110及存储器112单芯片化而成的成像元件相比,成像元件38的便携性提高。并且,与未将光电转换元件42、处理电路110及存储器112单芯片化而成的成像元件相比,能够提高设计的自由度。此外,与未将光电转换元件42、处理电路110及存储器112单芯片化而成的成像元件相比,也能够有助于摄像装置10的小型化。182.并且,如图6所示,作为成像元件38,采用了在光电转换元件42上层叠有存储器112的层叠型成像元件。由此,与未层叠光电转换元件42和存储器112的情况相比,能够提高从光电转换元件42向存储器112的图像数据的传送速度。传送速度的提高也有助于整个处理电路110中的处理的高速化。并且,与未层叠光电转换元件42和存储器112的情况相比,也能够提高设计的自由度。此外,与未层叠光电转换元件42和存储器112的情况相比,也能够有助于摄像装置10的小型化。183.并且,在摄像装置10中,基于由输出i/f110d2输出的数字图像数据70b的即时预览图像等由cpu15a显示在显示器26上。由此,能够使用户视觉辨认基于由输出i/f110d2输出的数字图像数据70b的即时预览图像等。184.此外,在摄像装置10中,由输出i/f110d2输出的数字图像数据70b由cpu15a存储于储存器15b、智能器件、个人计算机、服务器、usb存储器和/或存储卡等中。由此,能够管理由输出i/f110d2输出的数字图像数据70b。185.另外,在上述实施方式中,举出多个帧量的数字图像数据70b存储于存储器112中的方式例进行了说明,但本发明的技术并不限定于此。例如,存储器112中,除了多个帧量的数字图像数据70b以外,还可以存储压缩图像数据。压缩图像数据能够通过由图像处理电路110e进行压缩处理而得到。压缩处理是指压缩数字图像数据70b的处理。即,存储器112中,除了多个帧量的数字图像数据70b以外,还可以存储通过由作为本发明的技术所涉及的“压缩电路”的一例的图像处理电路110e压缩数字图像数据70b而得到的压缩图像数据。186.具体而言,控制电路110c将规定的帧数(在图15所示的例子中,4帧量)的数字图像数据70b存储于存储器112。并且,控制电路110c将通过由图像处理电路110e压缩数字图像数据而得到的压缩图像数据存储于存储器112。此外,控制电路110c将与压缩图像数据有关的属性信息和能够确定图像数据被压缩的压缩确定信息与压缩图像数据建立对应关联。187.在该情况下,作为一例,如图15所示,存储器112除了在上述实施方式中说明的地址以外,还具有地址“0x00540000”、“0x00580000”、及“0x005c0000”,按每个地址具有1帧量的存储区域。在图15所示的例子中,在第4帧数字图像数据70b存储于第4存储区域112d(“0x00300000”的地址的存储区域)中的情况下,由图像处理电路110e对第4帧数字图像数据70b进行压缩处理。由控制电路110c将通过压缩第4帧数字图像数据70b而得到的压缩图像数据(图15所示的例子的“压缩数据”)存储于第5存储区域112e(“0x00400000”的地址的存储区域)。188.并且,在图15所示的例子中,伴随第4帧摄像的完成,由控制电路110c从第1存储区域112a(“0x00000000”的地址的存储区域)中擦除第1帧数字图像数据70b,由控制电路110c将第5帧数字图像数据70b存储于第1存储区域112a。并且,在第5帧数字图像数据70b存储于第1存储区域112a中的情况下,由图像处理电路110e对第5帧数字图像数据70b进行压缩处理。由控制电路110c将通过压缩第5帧数字图像数据70b而得到的压缩图像数据存储于第6存储区域112f(“0x00500000”的地址的存储区域)。189.此外,在图15所示的例子中,伴随第5帧摄像的完成,由控制电路110c从第2存储区域112b(“0x00100000”的地址的存储区域)中擦除第2帧数字图像数据70b,由控制电路110c将第6帧数字图像数据70b存储于第2存储区域112b。并且,在第6帧数字图像数据70b存储于第2存储区域112b中的情况下,由图像处理电路110e对第6帧数字图像数据70b进行压缩处理。由控制电路110c将通过压缩第6帧数字图像数据70b而得到的压缩图像数据存储于第7存储区域112g(“0x00540000”的地址的存储区域)。190.如此,第4帧以后的数字图像数据70b被图像处理电路110e压缩,由控制电路110c将通过压缩而得到的压缩图像数据存储于存储器112的空闲存储区域。191.并且,在第4帧以后的数字图像数据70b被压缩,并作为压缩图像数据存储于存储器112的情况下,作为一例,如图16a及图16b所示,由控制电路110c生成属性信息。192.作为一例,如图16a所示,在第1帧~第3帧输出的属性信息是与图11a相同的属性信息。在第4帧输出的属性信息中包含与第4帧数字图像数据70b有关的属性信息。在图16a所示的例子中,作为与第4帧数字图像数据70b有关的属性信息,示出了能够确定第4存储区域112d的“0x00300000”的地址、图像尺寸、摄像时刻、摄像条件及擦除标志_关闭。并且,在第4帧输出的属性信息中包含的第1帧属性信息的擦除标志被开启。由此,伴随第5帧摄像而从第1存储区域112a中擦除第1帧数字图像数据70b。并且,在第4帧输出的属性信息还包含与第5帧数字图像数据70b的压缩图像数据有关的属性信息。在图16a所示的例子中,作为与第5帧数字图像数据70b的压缩图像数据有关的属性信息,示出了能够确定第5存储区域112e的“0x00400000”的地址、图像尺寸、摄像时刻、摄像条件及压缩确定信息。193.作为一例,如图16b所示,在第5帧输出的属性信息中包含与第5帧数字图像数据70b有关的属性信息。在图16b所示的例子中,作为与第5帧数字图像数据70b有关的属性信息,示出了能够确定第1存储区域112a的“0x00000000”的地址、图像尺寸、摄像时刻、摄像条件及擦除标志_关闭。并且,在第5帧输出的属性信息中包含的第2帧属性信息的擦除标志被开启。由此,伴随第6帧摄像而从第2存储区域112b中擦除第2帧数字图像数据70b。并且,在第5帧输出的属性信息中还包含与第5帧数字图像数据70b的压缩图像数据有关的属性信息及与第6帧数字图像数据70b的压缩图像数据有关的属性信息。在图16b所示的例子中,作为与第6帧数字图像数据70b的压缩图像数据有关的属性信息,示出了能够确定第6存储区域112f的“0x00500000”的地址、图像尺寸、摄像时刻、摄像条件及压缩确定信息。194.作为一例,如图16b所示,在第6帧输出的属性信息中包含与第6帧数字图像数据70b有关的属性信息。在图16b所示的例子中,作为与第6帧数字图像数据70b有关的属性信息,示出了能够确定第2存储区域112b的“0x01000000”的地址、图像尺寸、摄像时刻、摄像条件及擦除标志_关闭。并且,在第6帧输出的属性信息中包含的第3帧属性信息的擦除标志被开启。由此,伴随第7帧摄像而从第3存储区域112c中擦除第3帧数字图像数据70b。并且,在第5帧输出的属性信息中还包含与第5帧数字图像数据70b的压缩图像数据有关的属性信息、与第6帧数字图像数据70b的压缩图像数据有关的属性信息及与第6帧数字图像数据70b的压缩图像数据有关的属性信息。在图16b所示的例子中,作为与第7帧数字图像数据70b的压缩图像数据有关的属性信息,示出了“0x00540000”的地址、图像尺寸、摄像时刻、摄像条件及压缩确定信息。195.如此,由控制电路110c将规定的帧数的数字图像数据70b存储于存储器112,由控制电路110c还将压缩图像数据存储于存储器112,且由控制电路110c将与压缩图像数据有关的属性信息和压缩确定信息建立对应关联(在图16a及图16b所示的例子中,属性信息中包含压缩确定信息)。因此,即使在存储器112中存储有数字图像数据70b和压缩图像数据的情况下,也能够可区分地确定数字图像数据70b和压缩图像数据。196.在图16a及图16b所示的例子中,示出了与数字图像数据70b有关的属性信息中包含地址、图像尺寸、摄像时刻、摄像条件及擦除标志的方式例,但本发明的技术并不限定于此。例如,在压缩图像数据存储于存储器112的情况下,作为一例,如图17a及图17b所示,与数字图像数据70b有关的属性信息中除了地址、图像尺寸、摄像时刻、摄像条件及擦除标志以外,还可以包含表示是否预定在存储器112中存储压缩图像数据的压缩预定标志。被开启的压缩预定标志是本发明的技术所涉及的“压缩预定信息”的一例,表示预定伴随下一次摄像而在存储器112中存储压缩图像数据。被关闭的压缩预定标志表示没有预定伴随下一次摄像而在存储器112中存储压缩图像数据。197.当压缩预定标志被开启时,与压缩预定标志被开启的属性信息有关的数字图像数据70b伴随下一次摄像而被图像处理电路110e压缩。例如,如图17a所示,与在第3帧输出的属性信息中包含的第1帧数字图像数据70b有关的属性信息中包含表示压缩预定标志被开启的状态的“压缩预定标志_开启”。在该情况下,伴随下一次摄像(第4帧摄像)而第1帧数字图像数据70b被图像处理电路110e压缩,通过压缩而得到的压缩图像数据存储于第5存储区域112e。与此相伴,在第4帧输出的属性信息中包含与存储于第5存储区域112e(“0x00400000”的地址的存储区域)中的压缩图像数据有关的属性信息。与存储于第5存储区域112e中的压缩图像数据有关的属性信息中包含压缩确定信息,由此,后级电路13能够确定第5存储区域112e中存储有压缩图像数据。198.另外,擦除标志及压缩预定标志被开启的定时同步,作为一例,如图17a及图17b所示,当由控制电路110c开启擦除标志时,与此相伴,由控制电路110c也开启压缩预定标志。由此,即使从存储器112中擦除数字图像数据70b,通过压缩擦除前的数字图像数据70b而得到的压缩图像数据也由存储器112保持。199.如此,在存储器112中存储压缩图像数据的情况下,在从输出i/f110d2输出的属性信息中包含开启的压缩预定标志,因此能够对压缩图像数据的输出目的地(例如,后级电路13)赋予压缩图像数据的接受的准备宽限。200.另外,作为数字图像数据70b被压缩为压缩图像数据时的压缩形式,例如可举出mpeg、jpeg、tiff、png、gif及bmp等。在压缩图像数据存储于存储器112中的情况下,作为一例,如图18a及图18b所示,也可以在从输出i/f110d2输出的属性信息中包含能够确定压缩图像数据的压缩形式的压缩形式确定信息。在图18a及图18b所示的例子中,压缩形式确定信息与压缩确定信息一起包含在属性信息中。由此,能够使压缩图像数据的输出目的地(例如,后级电路13)根据压缩形式进行处理。201.并且,在上述实施方式中,举出在存储器112中存储1帧量的数字图像数据70b之后由输出i/f110d2输出属性信息的方式例进行了说明,但本发明的技术并不限定于此。例如,如图19所示,可以在由接收i/f110d1接收到与属性信息有关的指示(例如,垂直同步信号)的定时由输出i/f110d2输出属性信息。由此,能够根据与属性信息有关的指示即时地将属性信息提供给后级电路13。202.在上述实施方式中,举出在按每一帧输出的属性信息中包含多个帧量的属性信息的方式例进行了说明,但本发明的技术并不限定于此,例如,如图20所示,按每一帧输出的属性信息可以仅为与所对应的帧的数字图像数据70b有关的属性信息。在该情况下,与在按每一帧输出的属性信息中包含多个帧量的属性信息的情况相比,能够减少按每一帧输出到信号处理电路34的属性信息的信息量。203.另外,在图20所示的例子中,在按每一帧输出的属性信息中包含擦除标志及压缩预告标志,但本发明的技术并不限定于此,例如,如图21所示,在按每一帧输出的属性信息中可以不包含擦除标志及压缩预告标志。并且,也可以在按每一帧输出的属性信息中不包含擦除标志而包含压缩预告标志。204.并且,在上述实施方式中,举出由输出i/f110d2输出与全部帧的每一个有关的属性信息的方式例进行了说明,但本发明的技术并不限定于此,也可以从后级电路13侧向成像元件38指示使输出i/f110d2输出多少帧量的属性信息。205.在该情况下,例如,代替图13所示的属性信息输出处理,作为一例,由成像元件38的处理电路110执行图22所示的属性信息输出处理。206.图22所示的属性信息输出处理与图13所示的属性信息输出处理相比,不同点在于,具有步骤st10a来代替步骤st10,具有步骤st18a来代替步骤st18,及具有步骤st20a来代替步骤st20。控制器15经由输出i/f15d向成像元件38输出属性信息请求指示。属性信息请求指示包含垂直同步信号和输出量信息。输出量信息是指表示利用成像元件38的输出i/f110d2的属性信息的输出量的信息。这里所说的“输出量”例如由帧数规定。207.在图22所示的属性信息输出处理中,在步骤st10a中,控制电路110c判定是否由接收i/f110d1接收到从控制器15输出的属性信息请求指示。在步骤st10a中,在接收i/f110d1未接收到属性信息请求指示的情况下判定为“否”,属性信息输出处理转移到步骤st22。在步骤st10a中,在由接收i/f110d1接收到属性信息请求指示的情况下判定为“是”,属性信息输出处理转移到步骤st12。208.在步骤st18a中,控制电路110c按照由属性信息请求指示中包含的输出量信息表示的输出量选定在当前时刻保持的属性信息中使输出i/f110d2向信号处理电路34输出的属性信息。例如,若由输出量信息表示的输出量为1帧,则控制电路110c选择1帧量的与最新的数字图像数据70b有关的属性信息,若由输出量信息表示的输出量为2帧,则选择2帧量的与最新的数字图像数据70b有关的属性信息。209.在步骤st20a中,控制电路110c使输出i/f110d2向信号处理电路34输出在步骤st18a中选定的属性信息。由此,能够避免从输出i/f110d2输出必要以上的较多的属性信息。并且,由于输出量由帧数规定,因此后级电路13能够以帧单位处理属性信息。210.并且,在上述实施方式中,举出由输出i/f110d2向信号处理电路34输出属性信息及数字图像数据70b的方式例进行了说明,但本发明的技术并不限定于此。例如,如图23所示,可以由输出i/f110d2及输出i/f110d3向信号处理电路34输出属性信息及数字图像数据70b。在图23所示的例子中,处理电路110具有输出i/f110d2及输出i/f110d3。输出i/f110d3是本发明的技术所涉及的“第1输出部”的一例,输出i/f110d2是本发明的技术所涉及的“第2输出部”的一例。211.输出i/f110d3与控制电路110c连接。并且,信号处理电路34具备接收i/f34c。输出i/f110d2将属性信息输出到信号处理电路34。由信号处理电路34的接收i/f34a接收由输出i/f110d2输出的属性信息。并且,输出i/f110d3在控制电路110c的控制下将数字图像数据70b输出到信号处理电路34。由信号处理电路34的接收i/f34c接收由输出i/f110d3输出的数字图像数据70b。212.根据图23所示的结构,由输出i/f110d2输出属性信息,由输出i/f110d3输出数字图像数据70b,因此能够并行输出属性信息和数字图像数据70b。213.在上述实施方式中,例示了镜头可换式摄像装置10,但本发明的技术并不限定于此。例如,如图24所示,也可以在智能器件200上搭载有摄像装置主体214,该摄像装置主体214具有与在上述实施方式中说明的摄像装置主体12相当的结构及功能。214.作为示例,如图24所示,智能设备200具备框体212,并且摄像装置主体214容纳于框体212中。作为智能器件200的一例,可举出智能手机。在此,作为智能器件200,例如可举出作为带有摄像功能的电子设备的智能手机或平板终端等。215.成像透镜216安装于框体212上。在图24所示的例子中,成像透镜216在使智能器件200处于垂直放置的状态时的框体212的背面212a的左上部从背面212a露出。成像透镜216的中心位于光轴l1上。在摄像装置主体214上内置有成像元件38。摄像装置主体214从成像透镜216取入被摄体光。取入到摄像装置主体214内的被摄体光在成像元件38上成像,如在上述实施方式中说明的那样进行摄像。216.作为一例,如图25所示,在框体212的前表面212b设置有指示键222及触摸面板显示器224。在将智能器件200垂直放置的状态时的前表面212b的下部配置有指示键222,在指示键222的上方配置有触摸面板显示器224。触摸面板显示器224具备显示器226及触摸面板228,在显示器226上重叠有触摸面板228。触摸面板显示器224及指示键222具有与在上述实施方式中说明的ui系统器件17相同的功能。即,触摸面板显示器224及指示键222对用户提示信息,或接收来自用户的指示。来自用户的指示例如通过对显示于触摸面板显示器224上的软键(例如,与释放按钮20等相当的软键)进行触摸操作来实现。217.另外,显示器226是本发明的技术所涉及的“显示部(显示器)”的一例。并且,智能器件200是本发明的技术所涉及的“摄像装置”的一例。并且,在图24所示的例子中,示出了仅摄像装置主体214内置于智能器件200中的方式例,但本发明的技术并不限定于此,可以在智能器件200内置有多台数码相机,在该情况下,只要在至少1台数码相机中搭载有摄像装置主体214即可。218.并且,在上述实施方式中,作为成像元件38,例示了将光电转换元件42、处理电路110及存储器112单芯片化而成的成像元件,但本发明的技术并不限定于此。例如,只要将光电转换元件42、处理电路110及存储器112中的至少光电转换元件42及存储器112单芯片化即可。219.并且,在上述实施方式中,例示了属性信息是包含地址、图像尺寸、摄像时刻及摄像条件的信息,但本发明的技术并不限定于此。例如,属性信息可以是包含地址、图像尺寸、摄像时刻及摄像条件中的地址的信息,也可以是包含地址、图像尺寸、摄像时刻和/或摄像条件的信息。220.并且,在上述实施方式中,通信i/f之间按照pci-e的连接标准连接,但本发明的技术并不限定于此。也可以采用lvds、sata、slvs-ec或mipi等其他连接标准来代替pci-e连接标准。221.并且,在上述实施方式中,成像元件38与信号处理电路34之间的通信、控制器15与成像元件38的通信、及信号处理电路34与控制器15的通信均为有线形式的通信。然而,本发明的技术并不限定于此。成像元件38与信号处理电路34之间的通信、控制器15与成像元件38的通信和/或信号处理电路34与控制器15的通信也可以是无线形式的通信。222.并且,在上述实施方式中,举出ui系统器件17组装在摄像装置主体12中的方式例进行了说明,但ui系统器件17中包含的多个构成要件中的至少一部分可以外置在摄像装置主体12上。并且,ui系统器件17中包含的多个构成要件中的至少一部分也可以作为分体与外部i/f104连接来使用。223.并且,在上述实施方式中,作为帧速率例示了120fps,但本发明的技术并不限定于此,也可以将摄像用帧速率(例如,在图9所示的摄像工序中适用的帧速率)和输出用帧速率(例如,在图9所示的输出工序中适用的帧速率和/或数字图像数据70b的输出用帧速率)设为不同的帧速率。摄像用帧速率和/或输出用帧速率可以是固定的帧速率,也可以是可变的帧速率。在可变的帧速率的情况下,例如可以在满足规定条件(例如,由接收器件84接收到变更帧速率的指示的条件和/或作为变更帧速率的定时而事先确定的定时到来的条件)的情况下变更帧速率。在可变的帧速率的情况下,帧速率的具体的数值例如可以根据由接收器件84接收到的指示来变更,也可以根据后级电路13和/或成像元件38的运转率来变更。224.并且,在上述实施方式中,例示了信号处理电路34,但本发明的技术并不限定于此,除了信号处理电路34以外,还可以使用一个以上的信号处理电路。在该情况下,只要将成像元件38与多个信号处理电路分别直接连接即可。225.并且,在上述实施方式中,举出处理电路110由包含asic及fpga的器件来实现的方式例进行了说明,但本发明的技术并不限定于此。例如,也可以通过基于计算机的软件结构来实现处理电路110中包含的多个器件中的至少控制电路110c。226.在该情况下,例如,如图26所示,在成像元件38中内置有计算机852,将用于使计算机852执行上述实施方式所涉及的属性信息输出处理的属性信息输出程序902和用于使计算机852执行上述实施方式所涉及的数据擦除处理的数据擦除程序904存储于存储介质900中。作为存储介质900的一例,可举出作为非临时存储介质的ssd或usb存储器等任意的便携式存储介质。以下,为了便于说明,在不需要区分说明属性信息输出处理及数据擦除处理的情况下,称为“成像元件侧处理”,在不需要区分说明属性信息输出程序902及数据擦除程序904的情况下,称为“成像元件侧程序”。227.计算机852具备cpu852a、储存器852b及存储器852c。储存器852b是eeprom等非易失性存储装置,存储器852c是ram等易失性存储装置。存储于存储介质900中的成像元件侧程序安装于计算机852。cpu852a根据成像元件侧程序执行成像元件侧处理。228.成像元件侧程序可以不存储于存储介质900中而存储于储存器852b中。在该情况下,cpu852a从储存器852b中读出成像元件侧程序,将所读出的成像元件侧程序扩展到存储器852c。并且,cpu852a根据扩展到存储器852c的成像元件侧程序来执行成像元件侧处理。229.并且,在此,举出了属性信息输出程序902及数据擦除程序904存储于储存器852b中的方式例,但并不限于此,也可以将属性信息输出程序902及数据擦除程序904中的一者存储于储存器852b中,将另一者存储于存储介质900中。230.并且,也可以在经由通信网络(省略图示)与计算机852连接的其他计算机或服务器装置等存储部中存储成像元件侧程序,根据上述摄像装置10或智能器件200的请求下载成像元件侧程序并安装于计算机852。231.另外,不需要在与计算机852连接的其他计算机或服务器装置等存储部中存储全部成像元件侧程序,可以存储成像元件侧程序的一部分(例如,属性信息输出程序902或数据擦除程序904)。232.在图26所示的例子中,例示了成像元件38中内置有计算机852的方式例,但本发明的技术并不限定于此,例如计算机852可以设置在成像元件38的外部。233.在图26所示的例子中,cpu852a是单个cpu,但也可以是多个cpu。并且,也可以适用gpu来代替cpu852a。234.在图26所示的例子中,例示了计算机852,但本发明的技术并不限定于此,也可以适用包含asic、fpga和/或pld的器件来代替计算机852。并且,也可以使用硬件结构及软件结构的组合来代替计算机852。235.作为执行在上述实施方式中说明的成像元件侧处理的硬件资源,能够使用以下所示的各种处理器。作为处理器,例如可举出通用的处理器即cpu,如上所述,通过执行软件即程序,作为执行成像元件侧处理的硬件资源而发挥功能。并且,作为处理器,例如可举出作为处理器的专用电路,所述处理器具有fpga、pld、或asic等为了执行特定的处理而专门设计的电路结构。任何处理器中都内置或连接有存储器,通过任何处理器都使用存储器来执行信息处理装置侧处理。236.执行成像元件侧处理的硬件资源可以由这些各种处理器中的一个构成,也可以由相同种类或不同种类的两个以上的处理器的组合(例如,多个fpga的组合、或cpu与fpga的组合)构成。并且,执行成像元件侧处理的硬件资源可以是一个处理器。237.作为由一个处理器构成的例子,第一,存在如下方式:如以客户端及服务器等计算机为代表,由一个以上的cpu和软件的组合来构成一个处理器,该处理器作为执行成像元件侧处理的硬件资源而发挥功能。第二,存在如下方式:如以soc等为代表,使用由一个ic芯片来实现包括执行成像元件侧处理的多个硬件资源的整个系统的功能的处理器。如此,成像元件侧处理通过使用一个以上上述各种处理器作为硬件资源来实现。238.此外,作为这些各种处理器的硬件结构,更具体而言,能够使用将半导体元件等电路元件进行了组合的电路。239.并且,在图1所示的例子中例示摄像装置10,在图24所示的例子中例示了智能器件200,但本发明的技术并不限定于此。即,本发明的技术也能够适用于内置有具有与在上述实施方式中说明的摄像装置主体12相当的结构及功能的摄像装置的各种电子设备(例如,镜头固定式相机、个人计算机或可穿戴终端装置等),并且即使在这些电子设备中,也能够得到与摄像装置10及智能器件200相同的作用及效果。240.并且,在上述各实施方式中,例示了显示器26及226,但本发明的技术并不限定于此。例如,可以将附接到摄像装置的单独的显示器用作本发明的技术所涉及的“显示部”。241.并且,上述各种处理仅为一例。因此,在不脱离主旨的范围内,当然可以删除不必要的步骤,或者追加新的步骤,或者切换处理顺序。242.以上所示的记载内容及图示内容是关于本发明的技术所涉及部分的详细说明,只是本发明的技术的一例。例如,与上述结构、功能、作用及效果有关的说明是与本发明的技术所涉及部分的结构、功能、作用及效果的一例有关的说明。因此,在不脱离本发明的技术的主旨的范围内,当然可以对以上所示的记载内容及图示内容删除不必要的部分,或者追加新的要素,或者进行替换。并且,为了避免复杂化,并且为了容易理解本发明的技术所涉及的部分,在以上所示的记载内容及图示内容中,省略了在能够实施本发明的技术的方面不需要特别说明的与技术常识等有关的说明。243.在本说明书中,“a和/或b”与“a及b中的至少一个”的含义相同。即,“a和/或b”是指可以只是a,可以只是b,也可以是a及b的组合。并且,在本说明书中,附加“和/或”来表现3个以上的事项的情况下,也可以适用与“a和/或b”相同的概念。244.本说明书中所记载的所有文献、专利申请及技术标准,以与具体且分别记载通过参考而援用各文献、专利申请及技术标准的情况相同程度,通过参考而援用于本说明书中。245.关于以上实施方式,进一步公开以下附记。246.(附记1)247.一种成像元件,其内置有:248.处理器;及249.存储器,存储通过拍摄而得到的图像数据,且内置于上述成像元件中,250.上述处理器进行如下:251.控制上述图像数据向上述存储器的存储,252.将上述图像数据的属性信息存储于上述存储器,253.输出存储于上述存储器中的上述图像数据,254.接收与上述属性信息有关的指示,255.输出与所接收到的上述指示对应的上述属性信息。当前第1页12当前第1页12

背景技术:

::2.国际公开第2014/007004号中公开了一种固体成像元件,其具备:信号处理部,包含将从像素阵列部的各像素读出到信号线的模拟像素信号数字化的ad转换器,以比帧速率快的第1速度传送数字化后的像素数据;存储器部,保持从信号处理部传送的像素数据;数据处理部,以比第1速度慢的第2速度从存储器部读出像素数据;及控制部,在从存储器部读出像素数据时,进行停止与信号线连接的电流源的动作及信号处理部的至少ad转换器的动作的控制。3.在国际公开第2014/007004号中记载的固体成像元件中,信号处理部、存储器部、数据处理部及控制部具有形成在与形成有像素阵列部的芯片不同的至少一个芯片上,并且形成有像素阵列部的芯片和其他至少一个芯片层叠而成的结构。并且,在国际公开第2014/007004号中记载的固体成像元件中,数据处理部具有对存储器部指定列地址的解码器和读出所指定的地址的像素数据的读出放大器,通过读出放大器及解码器从存储器部读出像素数据。4.国际公开第2013/145765号中公开了一种摄像单元,其具备:摄像部,具有包含一个以上的像素的第1组和包含一个以上与构成第1组的像素不同的像素的第2组;及控制部,在使第1组执行1次电荷积蓄的期间,使第2组执行与第1组不同次数的电荷积蓄而输出各个像素信号。5.在国际公开第2013/145765号中记载的摄像单元中,包含摄像部的成像芯片与包含处理像素信号的处理电路的信号处理芯片通过层叠结构电连接。并且,包含存储像素信号的像素存储器的存储器芯片也通过层叠结构电连接。并且,在国际公开第2013/145765号中记载的摄像单元中,控制部按照来自外部电路的针对包含第2组的组群中的指定组的交付请求,从像素存储器读出指定组的像素信号并交付给图像处理部。并且,国际公开第2013/145765号中记载的摄像单元具备按照交付请求传输像素信号的数据传送接口。利用数据传送接口的像素信号的传输采用双数据速率方式、地址指定方式、短脉冲传送方式、总线方式、串行方式中的至少任一种。此外,在国际公开第2013/145765号中记载的摄像单元中,在针对多次电荷积蓄的各个像素信号存储于像素存储器的情况下,控制部将各个像素信号交付给图像处理部。技术实现要素:6.本发明的技术所涉及的一个实施方式提供能够从成像元件选择性地获取需要的图像数据的成像元件、摄像装置、成像元件的工作方法及程序。7.用于解决技术课题的手段8.本发明的技术所涉及的第1方式是一种成像元件,其包含:存储部,存储通过拍摄而得到的图像数据,且内置于成像元件;控制部,控制图像数据向存储部的存储,将图像数据的属性信息存储于存储部,且内置于成像元件;输出部,输出存储于存储部的图像数据,且内置于成像元件;及接收部,接收与属性信息有关的指示,输出部输出与由接收部接收到的指示对应的属性信息。9.本发明的技术所涉及的第2方式是第1方式所涉及的成像元件,其中,输出部在由接收部接收到指示的定时输出属性信息。10.本发明的技术所涉及的第3方式是第1方式或第2方式所涉及的成像元件,其中,指示是来自外部的帧同步信号。11.本发明的技术所涉及的第4方式是第1方式至第3方式中任一项所述的成像元件,其中,输出部输出与存储于存储部的图像数据中的最新的图像数据有关的属性信息。12.本发明的技术所涉及的第5方式是第4方式所涉及的成像元件,其中,输出部在由接收部接收到指示的定时输出与最新的图像数据有关的属性信息。13.本发明的技术所涉及的第6方式是第1方式至第5方式中任一项所述的成像元件,其中,输出部能够输出多个图像数据各自的属性信息,属性信息由输出部按照摄像顺序输出。14.本发明的技术所涉及的第7方式是第1方式至第6方式中任一项所述的成像元件,其中,属性信息是包含地址、图像尺寸、摄像时刻及摄像条件中的至少一个的信息。15.本发明的技术所涉及的第8方式是第1方式至第7方式中任一项所述的成像元件,其中,在伴随下一次摄像而从存储部中擦除图像数据的情况下,从输出部输出的属性信息是包含表示伴随下一次摄像而从存储部中擦除图像数据的擦除信息的信息。16.本发明的技术所涉及的第9方式是第8方式所涉及的成像元件,其中,在从存储部中擦除图像数据的情况下,控制部从存储部中擦除与作为存储部内的成为擦除对象的图像数据的擦除对象图像数据有关的属性信息,从存储部中擦除擦除对象图像数据。17.本发明的技术所涉及的第10方式是第1方式至第9方式中任一项所述的成像元件,其包含压缩图像数据的压缩电路,控制部将规定的帧数的图像数据存储于存储部,将通过由压缩电路压缩图像数据而得到的压缩图像数据存储于存储部,且将与压缩图像数据有关的属性信息和能够确定图像数据被压缩的压缩确定信息与压缩图像数据建立对应关联。18.本发明的技术所涉及的第11方式是第10方式所涉及的成像元件,其中,在存储部中存储压缩图像数据的情况下,从输出部输出的属性信息是包含表示预定在存储部中存储压缩图像数据的压缩预定信息的信息。19.本发明的技术所涉及的第12方式是第10方式或第11方式所涉及的成像元件,其中,从输出部输出的属性信息是包含能够确定压缩图像信息的压缩形式的信息的信息。20.本发明的技术所涉及的第13方式是第1方式至第12方式中任一项所述的成像元件,其中,指示包含基于输出部的属性信息的输出量,输出部以输出量输出属性信息。21.本发明的技术所涉及的第14方式是第13方式所涉及的成像元件,其中,输出量由图像数据的帧数规定。22.本发明的技术所涉及的第15方式是第1方式至第14方式中任一项所述的成像元件,其还具备接收部,该接收部接收从位于成像元件的后级的后级电路发送的属性信息,控制部根据由接收部接收到的属性信息从存储部获取图像数据,并使输出部向后级电路输出所获取的图像数据。23.本发明的技术所涉及的第16方式是第1方式至第15方式中任一项所述的成像元件,其中,输出部具有第1输出部及第2输出部,第1输出部输出图像数据,第2输出部输出属性信息。24.本发明的技术所涉及的第17方式是第1方式至第16方式中任一项所述的成像元件,其是至少将光电转换元件和存储部单芯片化而成的。25.本发明的技术所涉及的第18方式是第17方式所述的成像元件,其中,成像元件是存储部层叠于光电转换元件上的层叠型成像元件。26.本发明的技术所涉及的第19方式是一种摄像装置,其包含:第1方式至第18方式中任一项所述的成像元件;及控制装置,进行使显示部显示基于由输出部输出的图像数据的图像的控制及将由输出部输出的图像数据存储于存储装置的控制中的至少一者。27.本发明的技术所涉及的第20方式是一种成像元件的工作方法,该成像元件内置有存储通过拍摄而得到的图像数据的存储部,该成像元件的工作方法包括:控制图像数据向存储部的存储;将图像数据的属性信息存储于存储部;输出存储于存储部的图像数据;接收与属性信息有关的指示;及输出与所接收到的指示对应的属性信息。28.本发明的技术所涉及的第21方式是一种程序,其用于使计算机执行处理,该计算机适用于内置有存储通过拍摄而得到的图像数据的存储器的成像元件,该处理包括:控制图像数据向存储部的存储;将图像数据的属性信息存储于存储部;输出存储于存储部的图像数据;接收与属性信息有关的指示;及输出与所接收到的指示对应的属性信息。附图说明29.图1是表示实施方式所涉及的摄像装置的外观的一例的立体图。30.图2是表示图1所示的摄像装置的背面侧的外观的一例的后视图。31.图3是表示实施方式所涉及的摄像装置的结构的一例的框图。32.图4是表示实施方式所涉及的摄像装置中包含的摄像装置主体的电气系统的硬件结构的一例的框图。33.图5是用于说明实施方式所涉及的摄像装置中包含的成像元件的帧速率的概念图。34.图6是表示实施方式所涉及的成像元件的层叠结构的一例的概念图。35.图7是表示实施方式所涉及的成像元件中包含的存储器的结构的一例的框图。36.图8是表示实施方式所涉及的摄像装置中包含的成像元件的电气系统的硬件结构的一例的框图,是用于由成像元件进行摄像,且从成像元件输出属性信息的方式例的说明的框图。37.图9是表示由实施方式所涉及的成像元件进行的摄像工序及输出工序的内容的一例的概念图。38.图10是表示实施方式所涉及的摄像装置中包含的成像元件中的处理内容的一例的时序图。39.图11a是表示在第1帧~第4帧从成像元件的输出i/f输出的属性信息的内容的一例的概念图。40.图11b是表示在第5帧及第6帧从成像元件的输出i/f输出的属性信息的内容的一例的概念图。41.图12是表示实施方式所涉及的摄像装置中包含的成像元件的电气系统的硬件结构的一例的框图,是用于从成像元件输出数字图像数据的方式例的说明的框图。42.图13是表示实施方式所涉及的属性信息输出处理的流程的一例的流程图。43.图14是表示实施方式所涉及的数据擦除处理的流程的一例的流程图。44.图15是表示在对数字图像数据进行压缩处理的情况下向存储器存储数字图像数据及压缩图像数据的处理内容的一例的时序图。45.图16a是表示在对第4帧以后的数字图像数据进行压缩处理时的第1帧~第4帧从成像元件的输出i/f输出的属性信息的内容的一例的概念图。46.图16b是表示在对第4帧以后的数字图像数据进行压缩处理时的第5帧及第6帧从成像元件的输出i/f输出的属性信息的内容的一例的概念图。47.图17a是表示包含表示是否预定伴随下一次摄像而压缩1帧量的数字图像数据的压缩预定标志的属性信息,即在第1帧~第4帧从成像元件的输出i/f输出的属性信息的内容的一例的概念图。48.图17b是表示包含表示是否预定伴随下一次摄像而压缩1帧量的数字图像数据的压缩预定标志的属性信息,即在第5帧~第6帧从成像元件的输出i/f输出的属性信息的内容的一例的概念图。49.图18a是表示包含表示是否预定伴随下一次摄像而压缩1帧量的数字图像数据的压缩预定标志且包含压缩形式确定信息的属性信息,即在第4帧~第5帧从成像元件的输出i/f输出的属性信息的内容的一例的概念图。50.图18b是表示包含表示是否预定伴随下一次摄像而压缩1帧量的数字图像数据的压缩预定标志且包含压缩形式确定信息的属性信息,即在第6帧从成像元件的输出i/f输出的属性信息的内容的一例的概念图。51.图19是表示在由成像元件的接收i/f接收到与属性信息有关的指示(例如,垂直同步信号)的定时由成像元件的输出i/f输出属性信息时的成像元件中的处理内容的一例的时序图。52.图20是表示在按每一帧输出的属性信息是与1帧量的数字图像数据有关的属性信息时的在第1帧~第6帧输出的属性信息的内容的一例的概念图。53.图21是表示在按每一帧输出的属性信息是与1帧量的数字图像数据有关的属性信息时的在第1帧~第6帧输出的属性信息,即不包含擦除标志及压缩预定标志的属性信息的内容的一例的概念图。54.图22是表示实施方式所涉及的属性信息输出处理的流程的变形例的流程图。55.图23是表示实施方式所涉及的摄像装置中包含的成像元件的电气系统的硬件结构的变形例的框图。56.图24是表示实施方式所涉及的智能器件的背面侧的外观的一例的后视立体图。57.图25是表示图24所示的智能器件的前面侧的外观的一例的前视立体图。58.图26是表示从存储有实施方式所涉及的成像元件侧程序的存储介质将成像元件侧程序安装于成像元件内的计算机中的方式的一例的概念图。具体实施方式59.以下,按照附图对本发明的技术所涉及的摄像装置的实施方式的一例进行说明。60.首先,对在以下说明中使用的术语进行说明。61.cpu是指“centralprocessingunit:中央处理单元”的简称。gpu是指“graphicsprocessingunit:图形处理单元”的简称。ram是指“randomaccessmemory:随机存取存储器”的简称。rom是指“readonlymemory:只读存储器”的简称。dram是指“dynamicrandomaccessmemory:动态随机存取存储器”的简称。sram是指“staticrandomaccessmemory:静态随机存取存储器”的简称。lsi是指“large-scaleintegratedcircuit:大规模集成电路”的简称。asic是指“applicationspecificintegratedcircuit:专用集成电路”的简称。pld是指“programmablelogicdevice:可编程逻辑器件”的简称。fpga是指“field-programmablegatearray:现场可编程门阵列”的简称。soc是指“system-on-a-chip:片上系统”的简称。ssd是指“solidstatedrive:固态驱动器”的简称。usb是指“universalserialbus:通用串行总线”的简称。hdd是指“harddiskdrive:硬盘驱动器”的简称。eeprom是指“electricallyerasableandprogrammablereadonlymemory:带电可擦可编程只读存储器”的简称。ccd是指“chargecoupleddevice:电荷耦合元件”的简称。cmos是指“complementarymetaloxidesemiconductor:互补型金属氧化物半导体”的简称。el是指“electro-luminescence:电致发光”的简称。a/d是指“analog/digital:模拟/数字”的简称。i/f是指“interface:接口”的简称。ui是指“userinterface:用户界面”的简称。lvds是指“lowvoltagedifferentialsignaling:低压差分信号”的简称。pci-e是指“peripheralcomponentinterconnectexpress:外围组件互连标准”的简称。sata是指“serialadvancedtechnologyattachment:串行高级技术附件”的简称。slvs-ec是指“scalablelowsignalingwithembeddedclock:带有嵌入式时钟的可扩展低压信号”的简称。mipi是指“mobileindustryprocessorinterface:移动行业处理器接口”的简称。fps是指“framepersecond:每秒帧数”的简称。fifo是指“firstin,firstout:先进先出”的简称。mpeg是指“movingpictureexpertsgroup:动态影像专家小组”的简称。jpeg是指“jointphotographicexpertsgroup:联合图像专家小组”的简称。tiff是指“taggedimagefileformat:标签图像文件格式”的简称。bmp是指“bitmap:位图”的简称。png是指“portablenetworkgraphics:便携式网络图形”的简称。gif是指“graphicsinterchangeformat:图形交换格式”的简称。62.作为一例,如图1所示,摄像装置10是镜头可换式且省略了反光镜的数码相机。摄像装置10具备摄像装置主体12和可更换地安装于摄像装置主体12上的可更换镜头14。另外,在此,作为摄像装置10的一例,举出了镜头可换式且省略了反光镜的数码相机,但本发明的技术并不限定于此,摄像装置10可以是镜头固定式等其他种类的数码相机。63.在摄像装置主体12上设置有成像元件38。在可更换镜头14安装于摄像装置主体12上的情况下,表示被摄体的被摄体光透过可更换镜头14在成像元件38上成像,由成像元件38生成表示被摄体的图像的图像数据(例如,参考图4及图5)。64.在摄像装置主体12上设置有混合式取景器(注册商标)16。这里所说的混合式取景器16是指例如选择性地使用光学取景器(以下,称为“ovf”)及电子取景器(以下,称为“evf”)的取景器。另外,ovf是指“opticalviewfinder:光学取景器”的简称。并且,evf是指“electronicviewfinder:电子取景器”的简称。65.在摄像装置主体12的前表面上设置有取景器切换杆18。通过使取景器切换杆18沿箭头sw方向转动,从而切换能够用ovf视觉辨认的光学像和能够用evf视觉辨认的电子图像即即时预览图像。这里所说的“即时预览图像”是指基于通过由成像元件38拍摄而得到的图像数据的显示用动态图像。即时预览图像通常也被称为实时取景图像。在摄像装置主体12的上表面设置有释放按钮20及转盘23。在设定摄像系统的动作模式及回放系统的动作模式等时操作转盘23,由此在摄像装置10中,选择性地设定拍摄模式和回放模式作为动作模式。66.释放按钮20作为摄像准备指示部及摄像指示部而发挥功能,并能够检测摄像准备指示状态和摄像指示状态这两个阶段的按压操作。摄像准备指示状态例如是指从待机位置被按下至中间位置(半按位置)的状态,摄像指示状态是指被按下至超过中间位置的最终按下位置(全按位置)的状态。另外,以下,将“从待机位置被按下至半按位置的状态”称为“半按状态”,将“从待机位置被按下至全按位置的状态”称为“全按状态”。67.作为一例,如图2所示,在摄像装置主体12的背面上设置有触摸面板显示器24、指示键27及取景器目镜部30。68.触摸面板显示器24具备显示器26及触摸面板28(也参考图4)。作为显示器26的一例,可举出液晶显示器。显示器26也可以不是液晶显示器,而是有机el显示器或无机el显示器等其他种类的显示器。另外,显示器26及evf是本发明的技术所涉及的“显示部(显示器)”的一例。关于evf的显示,由于等同于显示器26的显示,因此省略以后的记载,在本说明书中,能够将对显示器26的显示替换为对evf的显示。69.显示器26显示图像及字符信息等。显示器26用于显示当摄像装置10为拍摄模式时通过连续拍摄而得到的即时预览图像。并且,显示器26也用于显示当被赋予静止图像用拍摄的指示时通过拍摄而得到的静止图像。此外,显示器26也用于显示当摄像装置10为回放模式时的回放图像及菜单画面等。70.触摸面板28是透射型触摸面板,与显示器26的显示区域的表面重叠。触摸面板28通过检测基于手指或手写笔等指示体的接触来接收来自用户的指示。71.指示键27接收各种指示。这里所说的“各种指示”例如是指能够选择各种菜单的菜单画面的显示指示、一个或多个菜单的选择指示、选择内容的确定指示、选择内容的擦除指示、放大、缩小及帧传送等各种指示等。72.作为一例,如图3所示,可更换镜头14具有成像透镜40。成像透镜40具备物镜40a、聚焦透镜40b及光圈40c。物镜40a、聚焦透镜40b及光圈40c从被摄体侧(物体侧)到摄像装置主体12侧(像侧),沿着光轴l1,按照物镜40a、聚焦透镜40b及光圈40c的顺序配置。聚焦透镜40b及光圈40c通过受到来自马达等驱动源(省略图示)的动力而进行工作。即,聚焦透镜40b及光圈40c根据所施加的动力沿着光轴l1移动。并且,光圈40c通过根据所施加的动力而进行工作来调节曝光。73.摄像装置主体12具备后级电路13、ui系统器件17、机械快门41及成像元件38。后级电路13是位于成像元件38的后级的电路。后级电路13具有控制器15及信号处理电路34。控制器15与ui系统器件17、信号处理电路34及成像元件38连接,控制摄像装置10的整个电气系统。74.成像元件38具备具有受光面42a的光电转换元件42。在本实施方式中,成像元件38是cmos图像传感器。并且,在此,作为成像元件38而例示出cmos图像传感器,但本发明的技术并不限定于此,例如即使成像元件38是ccd图像传感器等其他种类的图像传感器,本发明的技术也成立。75.机械快门41通过受到来自马达等驱动源(省略图示)的动力而进行工作。在可更换镜头14安装于摄像装置主体12的情况下,表示被摄体的被摄体光透过成像透镜40,经由机械快门41在受光面42a上成像。76.ui系统器件17是向用户提示信息或接收来自用户的指示的器件。控制器15从ui系统器件17获取各种信息,并控制ui系统器件17。77.成像元件38与控制器15连接,通过在控制器15的控制下拍摄被摄体,生成表示被摄体的图像的图像数据。78.成像元件38与信号处理电路34连接。信号处理电路34是lsi,具体而言,是包含asic及fpga的器件。控制器15从信号处理电路34获取各种信息,并控制成像元件38。成像元件38在控制器15的控制下,将由光电转换元件42生成的图像数据输出到信号处理电路34。79.信号处理电路34对从成像元件38输入的图像数据进行各种信号处理。由信号处理电路34进行的各种信号处理例如包括白平衡调整、清晰度调整、伽马校正、颜色空间转换处理及色差校正等公知的信号处理。80.另外,由信号处理电路34进行的各种信号处理也可以由信号处理电路34和成像元件38分散进行。即,也可以设为使成像元件38的处理电路110承担由信号处理电路34进行的各种信号处理中的至少一部分。81.另外,在本实施方式中,作为信号处理电路34例示了包含asic及fpga的器件,但本发明的技术并不限定于此,信号处理电路34也可以是包含asic、fpga和/或pld的器件。82.并且,信号处理电路34也可以是包含cpu、储存器(storage)及存储器(memory)的计算机。这里所说的“储存器”是指ssd或hdd等非易失性存储装置,这里所说的“存储器)”是指dram或sram等易失性存储装置。计算机中包含的cpu可以是单个,也可以是多个。并且,可以使用gpu来代替cpu。并且,信号处理电路34可以通过硬件结构及软件结构的组合来实现。83.作为一例,如图4所示,控制器15具备cpu15a、储存器15b、存储器15c、输出i/f15d及接收i/f15e。cpu15a、储存器15b、存储器15c、输出i/f15d及接收i/f15e经由总线100连接。在图4所示的例子中,为了便于图示,作为总线100图示了1条总线,但总线100包括数据总线、地址总线及控制总线等。84.储存器15b存储各种参数及各种程序。储存器15b是非易失性存储装置。在此,作为储存器15b的一例,采用了eeprom,但并不限于此,也可以是掩模rom、hdd或ssd等。存储器15c是易失性存储装置。存储器15c中临时存储各种信息。存储器15c被cpu15a用作工作存储器。在此,作为存储器15c的一例,采用了dram,但并不限于此,也可以是sram等其他种类的易失性存储装置。另外,cpu15a是本发明的技术所涉及的“控制装置”的一例,储存器15b是本发明的技术所涉及的“存储装置”的一例。85.储存器15b中存储有各种程序。cpu15a从储存器15b读出各种程序,将所读出的各种程序扩展到存储器15c。cpu15a根据扩展到存储器15c的各种程序来控制整个摄像装置10。86.输出i/f15d与成像元件38连接。cpu15a经由输出i/f15d控制成像元件38。例如,cpu15a经由输出i/f15d对成像元件38提供规定进行摄像的定时的摄像定时信号,由此控制由成像元件38进行的摄像定时。87.接收i/f15e与信号处理电路34连接。cpu15a经由接收i/f15e在与信号处理电路34之间进行各种信息的授受。88.从成像元件38向信号处理电路34输入图像数据。信号处理电路34对从成像元件38输入的图像数据进行各种信号处理(详细内容将后述)。信号处理电路34将进行各种信号处理的图像数据输出到接收i/f15e。接收i/f15e接收来自信号处理电路34的图像数据,并将所接收到的图像数据传送到cpu15a。89.外部i/f104与总线100连接。外部i/f104是由电路构成的通信器件。另外,在此,作为外部i/f104采用了由电路构成的器件,但这仅为一例。外部i/f104也可以是包括asic、fpga和/或pld的器件。并且,外部i/f104可以通过硬件结构及软件结构的组合来实现。90.作为外部i/f104的一例有usb接口,能够与其连接存储卡控制器、智能器件、个人计算机、服务器、usb存储器和/或存储卡等外部装置(省略图示)。外部i/f104控制cpu15a与外部装置之间的各种信息的授受。另外,与外部i/f104直接或间接连接的外部装置,即智能器件、个人计算机、服务器、usb存储器和/或存储卡等外部装置是本发明的技术所涉及的“存储装置”的一例。91.ui系统器件17具备触摸面板显示器24及接收器件84。显示器26及触摸面板28连接于总线100。因此,cpu15a使显示器26显示各种信息,并按照由触摸面板28接收到的各种指示进行动作。92.接收器件84具备硬键部25。硬键部25是多个硬键,具有释放按钮20(参考图1)、转盘23(参考图1及图2)及指示键22(参考图2)。硬键部25连接于总线100,cpu15a获取由硬键部25接收到的指示,按照所获取的指示进行动作。93.作为一例,如图5所示,从控制器15向成像元件38输入摄像定时信号。摄像定时信号包括垂直同步信号及水平同步信号。垂直同步信号是规定从光电转换元件42的每1帧的图像数据的读出开始定时的同步信号。水平同步信号是规定从光电转换元件42的每个水平线的图像数据的读出开始定时的同步信号。成像元件38按照根据从控制器15输入的垂直同步信号确定的帧速率,从光电转换元件42读出图像数据。另外,垂直同步信号是本发明的技术所涉及的“与属性信息有关的指示”及“来自外部的帧同步信号”的一例,控制器15是本发明的技术所涉及的“外部”的一例。94.在图5所示的例子中,作为成像元件38的帧速率,示出了在期间t内从光电转换元件42进行8帧量的读出的帧速率。作为具体的帧速率的一例,可举出120fps,但并不限于此,可以是超过120fps的帧速率(例如,240fps),也可以是小于120fps的帧速率(例如,60fps)。95.作为一例,如图6所示,在成像元件38中内置有光电转换元件42、处理电路110及存储器112。成像元件38是将光电转换元件42、处理电路110及存储器112单芯片化而成的成像元件。即,光电转换元件42、处理电路110及存储器112被封装在一起。在成像元件38中,处理电路110及存储器112层叠于光电转换元件42上。具体而言,光电转换元件42及处理电路110通过铜等具有导电性的凸块(省略图示)彼此电连接,处理电路110及存储器112也通过铜等具有导电性的凸块(省略图示)彼此电连接。96.处理电路110例如是lsi。存储器112是写入定时与读出定时不同的存储器。在此,作为存储器112的一例,采用了dram。97.处理电路110是包括asic及fpga的器件,按照上述控制器15的指示控制整个成像元件38。另外,在此,举出了处理电路110通过包含asic及fpga的器件来实现的例子,但本发明的技术并不限定于此,例如也可以是包含asic、fpga和/或pld的器件。并且,作为处理电路110,也可以采用包含cpu、作为非易失性存储装置的eeprom等储存器、及作为易失性存储装置的ram等存储器的计算机。计算机中包含的cpu可以是单个,也可以是多个。使用gpu来代替cpu。并且,处理电路110可以通过硬件结构及软件结构的组合来实现。98.光电转换元件42具有配置成矩阵状的多个光电二极管。作为多个光电二极管的一例,可举出“4896×3265”像素量的光电二极管。99.在光电转换元件42中包含的各光电二极管中配置有滤色器。滤色器包含最有助于用于得到亮度信号的与g(绿色)对应的g滤色器、与r(红色)对应的r滤色器及与b(蓝色)对应的b滤色器。100.光电转换元件42具有r像素、g像素及b像素。r像素是与配置有r滤色器的光电二极管对应的像素,g像素是与配置有g滤色器的光电二极管对应的像素,b像素是与配置有b滤色器的光电二极管对应的像素。r像素、g像素及b像素在行方向(水平方向)及列方向(垂直方向)上分别以规定的周期性配置。在本实施方式中,r像素、g像素及b像素以与x-trans(注册商标)排列对应的周期性排列。另外,在此,例示了x-trans排列,但本发明的技术并不限定于此,r像素、g像素及b像素的排列也可以是拜耳排列或蜂窝排列等。101.成像元件38具有所谓的电子快门功能,在控制器15的控制下,通过启动电子快门功能而控制光电转换元件42内的各光电二极管的电荷积蓄时间。电荷积蓄时间是指所谓的快门速度。102.在成像元件38中,以滚动快门方式选择性地进行静止图像用拍摄和即时预览图像用拍摄。静止图像用拍摄通过启动电子快门功能且使机械快门(省略图示)工作来实现,即时预览图像用拍摄通过不使机械快门工作而启动电子快门功能来实现。另外,在此,例示出滚动快门方式,但本发明的技术并不限于此,可以适用全局快门方式来代替滚动快门方式。103.另外,存储器112是本发明的技术所涉及的“存储部(存储器)”的一例。在本实施方式中,作为存储器112采用了dram,但即使存储器112是其他种类的存储器,本发明的技术也成立。并且,成像元件38是本发明的技术所涉及的“层叠型成像元件”的一例。104.作为一例,如图7所示,存储器112具有第1存储区域112a、第2存储区域112b、第3存储区域112c、第4存储区域112d、第5存储区域112e及第6存储区域112f。另外,在此,为了便于说明,例示了6个存储区域,但这仅为一例,存储器112只要具有能够存储多个帧量的图像数据的多个存储区域即可。105.在图7所示的例子中,对第1存储区域112a、第2存储区域112b、第3存储区域112c、第4存储区域112d、第5存储区域112e及第6存储区域112f分别赋予存储器112内的地址。对第1存储区域112a赋予地址“0x00000000”。对第2存储区域112b赋予地址“0x00100000”。对第3存储区域112c赋予地址“0x00200000”。对第4存储区域112d赋予地址“0x00300000”。对第5存储区域112e赋予地址“0x00400000”。对第6存储区域112f赋予地址“0x00500000”。106.作为一例,如图8所示,处理电路110具备接收i/f110d1及输出i/f110d2。在此,接收i/f110d1是本发明的技术所涉及的“接收部”及“接收部”的一例,输出i/f110d2是本发明的技术所涉及的“输出部(输出接口)”的一例。另外,接收部例如表示接受器(acceptor),接收部例如表示接收器(receiver)。107.控制器15的输出i/f15d与处理电路110的接收i/f110d1连接,并将摄像定时信号输出到接收i/f110d1。接收i/f110d1接收从输出i/f15d输出的摄像定时信号。108.信号处理电路34具备接收i/f34a及输出i/f34b。接收i/f34a与成像元件38的输出i/f110d2连接。处理电路110的输出i/f110d2将图像数据等各种信息(以下,也简称为“各种信息”)输出到信号处理电路34的接收i/f34a,接收i/f34a接收从输出i/f110d2输出的各种信息。信号处理电路34根据需要对由接收i/f34a接收到的各种信息实施信号处理。输出i/f34b与控制器15的接收i/f15e连接,并将各种信息输出到控制器15的接收i/f15e。接收i/f15e接收从输出i/f34b输出的各种信息。109.在成像元件38中,处理电路110除了接收i/f110d1及输出i/f110d2以外,还具备读出电路110a、数字处理电路110b、控制电路110c、图像处理电路110e。另外,控制电路110c是本发明的技术所涉及的“控制部(控制电路)”的一例。110.读出电路110a分别与光电转换元件42、数字处理电路110b及控制电路110c连接。数字处理电路110b连接于控制电路110c。控制电路110c分别与存储器112、接收i/f110d1、输出i/f110d2及图像处理电路110e连接。111.作为一例,如图8所示,上述图像数据大致分为模拟图像数据70a和数字图像数据70b。另外,以下,为了便于说明,在不需要区分说明模拟图像数据70a和数字图像数据70b的情况下,不标注符号而称为“图像数据”。112.处理电路110的接收i/f110d1及输出i/f110d2分别是具有fpga的通信器件。并且,控制器15的输出i/f15d及接收i/f15e分别也是具有fpga的通信器件。此外,信号处理电路34的接收i/f34a及输出i/f34b分别也是具有fpga的通信器件。113.处理电路110的接收i/f110d1与控制器15的输出i/f15d之间按照pci-e的连接标准连接。并且,处理电路110的输出i/f110d2与信号处理电路34的接收i/f34a之间也按照pci-e的连接标准连接。此外,信号处理电路34的输出i/f34b与控制器15的接收i/f15e之间也按照pci-e的连接标准连接。另外,以下,在不需要区分说明接收i/f110d1、输出i/f110d2、接收i/f34a、输出i/f34b、接收i/f15e及输出i/f15d的情况下,不标注符号而称为“通信i/f”。114.在此,作为通信i/f采用了由电路(asic、fpga和/或pld等)构成的通信器件,但这仅为一例。通信i/f也可以是包含cpu、eeprom等储存器、及ram等存储器的计算机。在该情况下,计算机中包含的cpu可以是单个,也可以是多个。使用gpu来代替cpu。并且,通信i/f可以通过硬件结构及软件结构的组合来实现。115.接收i/f110d1接收从控制器15的输出i/f15d1输出的摄像定时信号,并将所接收到的摄像定时信号传送到控制电路110c。116.读出电路110a在控制电路110c的控制下控制光电转换元件42,从光电转换元件42读出模拟图像数据70a。从光电转换元件42的模拟图像数据70a的读出按照从控制器15输入到处理电路110的摄像定时信号进行。117.具体而言,首先,接收i/f110d1从控制器15接收摄像定时信号,并将所接收到的摄像定时信号传送到控制电路110c。接着,控制电路110c将从接收i/f110d1传送的摄像定时信号传送到读出电路110a。即,垂直同步信号及水平同步信号被传送到读出电路110a。并且,读出电路110a按照从控制电路110c传送的垂直同步信号开始从光电转换元件42以帧单位读出模拟图像数据70a。并且,读出电路110a按照从控制电路110c传送的水平同步信号开始以水平线单位的模拟图像数据70a的读出。118.读出电路110a对从光电转换元件42读出的模拟图像数据70a进行模拟信号处理。模拟信号处理包括噪声消除处理及模拟增益处理等公知的处理。噪声消除处理是消除由光电转换元件42中包含的像素之间的特性的偏差引起的噪声的处理。模拟增益处理是对模拟图像数据70a施加增益的处理。并且,读出电路110a对模拟图像数据70a进行相关双采样。在由读出电路110a对模拟图像数据70a进行相关双采样后,模拟图像数据70a输出到数字处理电路110b。119.数字处理电路110b具备a/d转换器110b1。a/d转换器110b1对模拟图像数据70a进行a/d转换。120.数字处理电路110b对从读出电路110a输入的模拟图像数据70a进行数字信号处理。数字信号处理例如包括相关双采样、基于a/d转换器110b1的a/d转换及数字增益处理。121.对于从读出电路110a输入的模拟图像数据70a,由a/d转换器110b1进行a/d转换,由此模拟图像数据70a被数字化,作为raw数据得到数字图像数据70b。并且,通过数字处理电路110b对数字图像数据70b进行数字增益处理。数字增益处理是指对数字图像数据70b施加增益的处理。如此通过进行数字信号处理而得到的数字图像数据70b由数字处理电路110b输出到控制电路110c。122.控制电路110c将从数字处理电路110b输入的数字图像数据70b输出到图像处理电路110e。图像处理电路110e对从控制电路110c输入的数字图像数据70b进行图像处理,将图像处理后的数字图像数据70b输出到控制电路110c。这里所说的“图像处理”例如可举出去马赛克处理和/或数字间隔剔除处理等。123.去马赛克处理是根据与滤色器的排列对应的马赛克图像对每个像素计算所有颜色信息的处理。例如,若成像元件38是适用rgb3色滤色器的成像元件,则根据rgb马赛克图像对每个像素进行所有rgb的颜色信息。数字间隔剔除处理是以行单位间隔剔除图像数据中包含的像素的处理。线单位例如是指水平线单位和/或垂直线单位。124.存储器112是能够存储多个帧的数字图像数据的存储器。存储器112具有像素单位的存储区域(参考图7),数字图像数据70b通过控制电路110c以像素单位存储于存储器112中的对应的存储区域中。控制电路110c将从图像处理电路110e输入的数字图像数据70b存储于存储器112。125.控制电路110c能够随机访问存储器112。控制电路110c根据来自控制器15的指示,获取存储于存储器112中的数字图像数据70b的属性信息。属性信息是表示存储于存储器112中的数字图像数据70b的属性的信息。在此,属性信息例如是指包含地址、图像尺寸、摄像时刻、曝光时间、成像元件灵敏度及擦除标志的信息。126.地址是指存储器112中以帧单位确定数字图像数据70b的存储位置的信息(记录地址)。图像尺寸是指1帧量的数字图像数据70b的水平线方向的尺寸(水平尺寸)及1帧量的数字图像数据70b的垂直线方向的尺寸(垂直尺寸)。摄像时刻是指由成像元件38进行摄像的时刻(例如,年月日时分秒)。这里所说的“进行摄像的时刻”例如是指1帧量的数字图像数据70b存储于存储器112中的时刻。但是,这仅为一例,进行摄像的时刻也可以是完成1帧量的曝光的时刻或完成1帧量的a/d转换的时刻等。127.曝光时间是指得到1帧量的数字图像数据70b所需的曝光时间。成像元件灵敏度例如是指光电转换元件42的灵敏度(传感器增益)。擦除标志是指表示伴随下一次摄像而是否从存储器112中擦除数字图像数据70b的标志。在擦除标志为关闭的情况下,不伴随下一次摄像而从存储器112中擦除数字图像数据70b,在擦除标志为开启的情况下,伴随下一次摄像而从存储器112中擦除数字图像数据70b。作为从存储器112擦除的数字图像数据70b的一例,可举出从存储器112擦除的1帧量的数字图像数据70b。128.另外,曝光时间及成像元件灵敏度是本发明的技术的“摄像条件”的一例,开启状态的擦除标志是本发明的技术所涉及的“擦除信息”的一例。129.在此,作为本发明的技术所涉及的“摄像条件”的一例,举出了曝光时间及成像元件灵敏度,但本发明的技术并不限定于此,代替曝光时间和/或成像元件,或除了曝光时间和/或成像元件以外,也可以采用成像透镜40的种类、被摄体距离、焦距、视角和/或抖动校正的有无等。130.控制电路110c根据来自控制器15的与属性信息有关的指示生成属性信息,将所生成的属性信息输出到输出i/f110d2。与属性信息有关的指示例如是指控制器15请求处理电路110输出属性信息的指示。在本实施方式中,作为与属性信息有关的指示的一例,采用了垂直同步信号。输出i/f110d2将从控制电路110c输入的属性信息输出到信号处理电路34。131.具体而言,首先,接收i/f110d1从控制器15接收垂直同步信号作为与属性信息有关的指示。接着,控制电路110c生成与存储于存储器112中的数字图像数据70b中最早存储的数字图像数据70b有关的属性信息,作为与由接收i/f110d1接收到的垂直同步信号对应的属性信息。并且,输出i/f110d2将由控制电路110c生成的属性信息输出到信号处理电路34。132.作为一例,如图9所示,由成像元件38进行的工序包括摄像工序和输出工序。133.在摄像工序中,依次进行曝光、模拟图像数据70a的读出、对光电转换元件42的复位、模拟信号处理、数字信号处理、第1次存储、数字图像数据70b的获取、图像处理及第2次存储。134.由光电转换元件42进行曝光。由读出电路110a进行模拟图像数据70a的读出、对光电转换元件42的复位及模拟信号处理。模拟图像数据70a的读出以垂直同步信号由接收i/f110d1接收为条件而开始。由光电转换元件42进行曝光的期间是未进行模拟图像数据70a的读出及对光电转换元件42的复位的期间。对光电转换元件42的复位是指消除光电转换元件42内的各像素的残余电荷的动作。在从进行对光电转换元件42的基于读出电路110a的上一次复位到进行读出为止的期间进行基于光电转换元件42的曝光。135.由数字处理电路110b进行数字信号处理。第1次存储是指通过进行数字信号处理而得到的数字图像数据70b向存储器112的存储。数字图像数据70b的获取是指从存储器112获取数字图像数据70b。由控制电路110c进行第1次存储及数字图像数据70b的获取。由图像处理电路110e对由控制电路110c获取的数字图像数据70b进行图像处理。第2次存储是指进行了图像处理的数字图像数据70b向存储器112的存储。由控制电路110c进行第2次存储。136.在输出工序中,进行属性信息的生成和属性信息的输出。属性信息的生成是指与存储于存储器112中的数字图像数据70b有关的每1帧的属性信息的生成。由控制电路110c进行属性信息的生成。属性信息的输出是指利用输出i/f110d2输出由控制电路110c生成的属性信息。137.图10示出第1帧(1f)~第6帧(6f)的图像数据的读出到向存储器112的存储为止的流程和每1帧的属性信息的输出定时的一例。图10所示的1f~6f的“f”是指“frame:帧”的简称。在图10所示的例子中,为了便于说明,示出了分别在存储器112的第1存储区域112a、第2存储区域112b、第3存储区域112c、第4存储区域112d、第5存储区域112e及第6存储区域112f中存储1帧量的数字图像数据70b的方式。138.作为一例,如图10所示,每当由接收i/f110d1接收垂直同步信号时,开始从光电转换元件42读出1帧量的模拟图像数据70a。在图10所示的例子中,由接收i/f110d1依次接收第1次~第6次垂直同步信号,开始第1帧~第6帧模拟图像数据70a的读出。139.对从光电转换元件42的第1行的水平线到最终行的水平线按照水平同步信号按每一行进行模拟图像数据70a的读出,当对每一行的读出结束时,结束读出的水平线的各像素被复位。模拟图像数据70a被转换为数字图像数据70b,按照所读出的模拟图像数据70a的帧的顺序(摄像顺序),数字图像数据70b以1帧单位可区分地且以fifo方式存储于存储器112。具体而言,对第1存储区域112a、第2存储区域112b、第3存储区域112c、第4存储区域112d、第5存储区域112e及第6存储区域112f依次以1帧单位覆盖保存最新的数字图像数据70b。覆盖保存按照第1存储区域112a、第2存储区域112b、第3存储区域112c、第4存储区域112d、第5存储区域112e及第6存储区域112f的顺序反复进行。140.输出i/f110d2将与存储于存储器112中的数字图像数据70b中的最新的数字图像数据70b有关的属性信息输出到信号处理电路34。在该情况下,首先,控制电路110c每当在由接收i/f110d1接收到垂直同步信号的定时完成1帧量的最新的数字图像数据70b向存储器112的存储时,生成与存储于存储器112中的数字图像数据70b中的最新的数字图像数据70b有关的属性信息。并且,输出i/f110d2将由控制电路110c生成的属性信息输出到信号处理电路34。141.作为一例,如图11a及图11b所示,各帧(在图11a及图11b所示的例子中,第1帧~第6帧)的属性信息由输出i/f110d2输出到信号处理电路34。并且,信号处理电路34将所输入的属性信息输出到控制器15。142.作为一例,如图11a所示,在第1帧输出的属性信息是与存储于第1存储区域112a中的数字图像数据70b有关的属性信息。在图11a所示的例子中,作为与存储于第1存储区域112a中的数字图像数据70b有关的属性信息的一例,可举出包含第1存储区域112a的地址、第1存储区域112a内的数字图像数据70b的水平尺寸、第1存储区域112a内的数字图像数据70b的垂直尺寸、与第1存储区域112a内的数字图像数据70b有关的摄像时刻、与第1存储区域112a内的数字图像数据70b有关的曝光时间、与第1存储区域112a内的数字图像数据70b有关的成像元件灵敏度及擦除标志_关闭的信息。在此,“擦除标志_关闭”是指表示擦除标志为关闭的状态的信息。143.在第2帧输出的属性信息是与存储于第1存储区域112a中的数字图像数据70b有关的属性信息及与存储于第2存储区域112b中的数字图像数据70b有关的属性信息。在图11a所示的例子中,作为与存储于第2存储区域112b中的数字图像数据70b有关的属性信息的一例,可举出包含第2存储区域112b的地址、第2存储区域112b内的数字图像数据70b的水平尺寸、第2存储区域112b内的数字图像数据70b的垂直尺寸、与第2存储区域112b内的数字图像数据70b有关的摄像时刻、与第2存储区域112b内的数字图像数据70b有关的曝光时间、与第2存储区域112b内的数字图像数据70b有关的成像元件灵敏度及擦除标志_关闭的信息。144.在第3帧输出的属性信息是与存储于第1存储区域112a中的数字图像数据70b有关的属性信息、与存储于第2存储区域112b中的数字图像数据70b有关的属性信息及与存储于第3存储区域112c中的数字图像数据70b有关的属性信息。在图11a所示的例子中,作为与存储于第3存储区域112c中的数字图像数据70b有关的属性信息的一例,可举出包含第3存储区域112c的地址、第3存储区域112c内的数字图像数据70b的水平尺寸、第3存储区域112c内的数字图像数据70b的垂直尺寸、与第3存储区域112c内的数字图像数据70b有关的摄像时刻、与第3存储区域112c内的数字图像数据70b有关的曝光时间、与第3存储区域112c内的数字图像数据70b有关的成像元件灵敏度及擦除标志_关闭的信息。145.在第4帧输出的属性信息是与存储于第1存储区域112a中的数字图像数据70b有关的属性信息、与存储于第2存储区域112b中的数字图像数据70b有关的属性信息、与存储于第3存储区域112c中的数字图像数据70b有关的属性信息及与存储于第4存储区域112d中的数字图像数据70b有关的属性信息。在图11a所示的例子中,作为与存储于第4存储区域112d中的数字图像数据70b有关的属性信息的一例,可举出包含第4存储区域112d的地址、第4存储区域112d内的数字图像数据70b的水平尺寸、第4存储区域112d内的数字图像数据70b的垂直尺寸、与第4存储区域112d内的数字图像数据70b有关的摄像时刻、与第4存储区域112d内的数字图像数据70b有关的曝光时间、与第4存储区域112d内的数字图像数据70b有关的成像元件灵敏度及擦除标志_关闭的信息。在此,在第4帧输出的属性信息中包含的与存储于第1存储区域112a中的数字图像数据70b有关的属性信息内的“擦除标志_关闭”由控制电路110c变更为“擦除标志_开启”。“擦除标志_开启”是指表示擦除标志为开启的状态的信息。146.如此,与存储于第1存储区域112a中的数字图像数据70b有关的属性信息内的“擦除标志_关闭”由控制电路110c变更为“擦除标志_开启”。这表示从输出i/f110d2在第4帧输出的属性信息是包含表示伴随下一次摄像而从存储器112中擦除第1存储区域112a内的数字图像数据70b的信息的信息。147.当在第4帧输出的属性信息中包含“擦除标志_开启”时,伴随下一次摄像(例如,第5帧摄像开始的时刻或当前时刻到第5帧摄像开始为止的期间),由控制电路110c擦除与作为存储器112内的成为擦除对象的数字图像数据70b的擦除对象图像数据有关的属性信息,即与第1存储区域112a有关的属性信息。并且,数字图像数据70b也由控制电路110c从第1存储区域112a擦除。在该情况下,例如,伴随下一次摄像,首先,由控制电路110c擦除与第1存储区域112a有关的属性信息,接着,由控制电路110c从第1存储区域112a擦除数字图像数据70b。另外,在此,举出了擦除数字图像数据70b及属性信息的方式例,但本发明的技术并不限定于此,“擦除”实际上除了擦除数字图像数据70b及属性信息以外,还包括释放区域,并能够将其覆盖的处理。148.作为一例,如图11b所示,在第5帧输出的属性信息是与存储于第2存储区域112b中的数字图像数据70b有关的属性信息、与存储于第3存储区域112c中的数字图像数据70b有关的属性信息、与存储于第4存储区域112d中的数字图像数据70b有关的属性信息及与存储于第5存储区域112e中的数字图像数据70b有关的属性信息。在图11b所示的例子中,作为与存储于第5存储区域112e中的数字图像数据70b有关的属性信息的一例,可举出包含第5存储区域112e的地址、第5存储区域112e内的数字图像数据70b的水平尺寸、第5存储区域112e内的数字图像数据70b的垂直尺寸、与第5存储区域112e内的数字图像数据70b有关的摄像时刻、与第5存储区域112e内的数字图像数据70b有关的曝光时间、与第5存储区域112e内的数字图像数据70b有关的成像元件灵敏度及擦除标志_关闭的信息。在此,在第5帧输出的属性信息中包含的与存储于第2存储区域112b中的数字图像数据70b有关的属性信息内的“擦除标志_关闭”由控制电路110c变更为“擦除标志_开启”。149.如此,当与存储于第2存储区域112b中的数字图像数据70b有关的属性信息内的“擦除标志_关闭”由控制电路110c变更为“擦除标志_开启”时,伴随下一次摄像(例如,第6帧摄像开始的时刻或当前时刻到第6帧摄像开始为止的期间),由控制电路110c擦除与作为存储器112内的成为擦除对象的数字图像数据70b的擦除对象图像数据有关的属性信息,即与第2存储区域112b有关的属性信息。并且,数字图像数据70b也由控制电路110c从第2存储区域112b擦除。在该情况下,例如,伴随下一次摄像,首先,由控制电路110c擦除与第2存储区域112b有关的属性信息,接着,由控制电路110c从第2存储区域112b擦除数字图像数据70b。150.在第6帧输出的属性信息是与存储于第3存储区域112c中的数字图像数据70b有关的属性信息、与存储于第4存储区域112d中的数字图像数据70b有关的属性信息、与存储于第5存储区域112e中的数字图像数据70b有关的属性信息及与存储于第6存储区域112f中的数字图像数据70b有关的属性信息。在图11b所示的例子中,作为与存储于第6存储区域112f中的数字图像数据70b有关的属性信息的一例,可举出包含第6存储区域112f的地址、第6存储区域112f内的数字图像数据70b的水平尺寸、第6存储区域112f内的数字图像数据70b的垂直尺寸、与第6存储区域112f内的数字图像数据70b有关的摄像时刻、与第6存储区域112f内的数字图像数据70b有关的曝光时间、与第6存储区域112f内的数字图像数据70b有关的成像元件灵敏度及擦除标志_关闭的信息。在此,在第6帧输出的属性信息中包含的与存储于第3存储区域112c中的数字图像数据70b有关的属性信息内的“擦除标志_关闭”由控制电路110c变更为“擦除标志_开启”。151.如此,当与存储于第3存储区域112c中的数字图像数据70b有关的属性信息内的“擦除标志_关闭”由控制电路110c变更为“擦除标志_开启”时,伴随下一次摄像(例如,第7帧摄像开始的时刻或当前时刻到第7帧摄像开始为止的期间),由控制电路110c擦除与作为存储器112内的成为擦除对象的数字图像数据70b的擦除对象图像数据有关的属性信息,即与第3存储区域112c有关的属性信息。并且,数字图像数据70b也由控制电路110c从第3存储区域112c擦除。在该情况下,例如,伴随下一次摄像,首先,由控制电路110c擦除与第3存储区域112c有关的属性信息,接着,由控制电路110c从第3存储区域112c擦除数字图像数据70b。152.如此,当属性信息按每一帧由输出i/f110d2发送到信号处理电路34时,信号处理电路34将属性信息传送到控制器15。从信号处理电路34传送到控制器15的属性信息由控制器15的接收i/f15e接收。控制器15根据需要从由接收i/f15e接收到的属性信息中获取地址。153.作为一例,如图12所示,控制器15经由输出i/f15d将从属性信息获取的地址输出到成像元件38的接收i/f110d1。成像元件38的接收i/f110d1接收来自控制器15的地址。控制电路110c按照由接收i/f110d1接收到的地址从存储器112获取数字图像数据70b,并使输出i/f110d2向信号处理电路34输出所获取的数字图像数据70b。154.另外,在此,举出从控制器15的输出i/f15d向成像元件38输出地址的方式例进行了说明,但本发明的技术并不限定于此。例如,控制器15还可以具备发送i/f,可以从发送i/f向成像元件38发送地址。155.并且,在此,举出由接收i/f110d1接收地址的方式例进行了说明,但本发明的技术并不限定于此。例如,成像元件38还可以具备接收i/f,可以由成像元件38的接收i/f接收从控制器15发送的地址。156.接着,对摄像装置10的作用进行说明。157.首先,参考图13对由成像元件38的处理电路110执行的属性信息输出处理的流程进行说明。158.在图13所示的属性信息输出处理中,首先,在步骤st10中,控制电路110c判定是否由接收i/f110d1接收到垂直同步信号。在步骤st10中,在接收i/f110d1未接收到垂直同步信号的情况下判定为“否”,属性信息输出处理转移到步骤st22。在步骤st10中,在由接收i/f110d1接收到垂直同步信号的情况下判定为“是”,属性信息输出处理转移到步骤st12。159.在步骤st12中,控制电路110c将通过拍摄而得到的数字图像数据70b存储于存储器112,然后,属性信息输出处理转移到步骤st14。160.在步骤st14中,控制电路110c生成关于在步骤st12中存储于存储器112中的数字图像数据70b的属性信息,保持所生成的属性信息,然后,属性信息输出处理转移到步骤st16。161.在步骤st16中,控制电路110c判定通过进行下一次摄像,数字图像数据70b能够存储于存储器112内的帧数是否到达上限数。在本实施方式中,存储器112具有第1存储区域112a、第2存储区域112b、第3存储区域112c、第4存储区域112d、第5存储区域112e及第6存储区域112f这6个存储区域,因此这里所说的“上限数”是“6”。另外,上限数并不限定于此,只要是能够存储于存储器112中的帧数即可。162.在步骤st16中,在通过进行下一次摄像,数字图像数据70b能够存储于存储器112内的帧数未到达上限数的情况下判定为“否”,属性信息输出处理转移到步骤st20。在步骤st16中,在通过进行下一次摄像,数字图像数据70b能够存储于存储器112内的帧数到达上限数的情况下判定为“是”,属性信息输出处理转移到步骤st18。163.在步骤st18中,控制电路110c将存储于存储器112中的全部帧量的数字图像数据70b中的关于最早存储于存储器112中的1帧量的数字图像数据70b的属性信息中包含的擦除标志开启,然后,属性信息输出处理转移到步骤st20。164.在步骤st20中,控制电路110c使输出i/f110d2向信号处理电路34输出在当前时刻保持的属性信息,然后,属性信息输出处理转移到步骤st22。165.在步骤st22中,控制电路110c判定是否满足结束属性信息输出处理的条件(以下,称为“属性信息输出处理结束条件”)。作为属性信息输出处理结束条件的一例,可举出由接收器件84(参考图4)接收到结束属性信息输出处理的指示的条件。在步骤st22中,在不满足属性信息输出处理结束条件的情况下判定为“否”,属性信息输出处理转移到步骤st10。在步骤st22中,在满足属性信息输出处理结束条件的情况下判定为“是”,属性信息输出处理结束。166.接着,参考图14对由成像元件38的处理电路110执行的数据擦除处理的流程进行说明。167.在图14所示的数据擦除处理中,首先,在步骤st50中,控制电路110c判定是否由输出i/f110d2输出属性信息。在步骤st50中,在输出i/f110d2未输出属性信息的情况下判定为“否”,数据擦除处理转移到步骤st60。在步骤st50中,在由输出i/f110d2输出属性信息的情况下判定为“是”,数据擦除处理转移到步骤st52。168.在步骤st52中,控制电路110c判定是否由接收i/f110d1接收到垂直同步信号。在步骤st52中,在接收i/f110d1未接收到垂直同步信号的情况下判定为“否”,再次进行步骤st52的判定。在步骤st52中,在由接收i/f110d1接收到垂直同步信号的情况下判定为“是”,属性信息输出处理转移到步骤st54。169.在步骤st54中,控制电路110c判定是否保持擦除标志被开启的属性信息。在步骤st54中,在未保持擦除标志被开启的属性信息的情况下判定为“否”,数据擦除处理转移到步骤st60。在步骤st54中,在保持擦除标志被开启的属性信息的情况下判定为“是”,数据擦除处理转移到步骤st56。170.在步骤st56中,控制电路110c首先根据在当前时刻保持的所有的属性信息中擦除标志被开启的属性信息中包含的地址来确定数字图像数据70b。接着,控制电路110c擦除在当前时刻保持的所有的属性信息中擦除标志被开启的属性信息。并且,控制电路110c从存储器112中擦除根据地址确定的数字图像数据70b,然后,数据擦除处理转移到步骤st60。171.在步骤st60中,控制电路110c判定是否满足结束数据擦除处理的条件(以下,称为“数据擦除处理结束条件”)。作为数据擦除处理结束条件的一例,可举出由接收器件84(参考图4)接收到结束数据擦除处理的指示的条件。在步骤st60中,在不满足数据擦除处理结束条件的情况下判定为“否”,数据擦除处理转移到步骤st50。在步骤st60中,在满足数据擦除处理结束条件的情况下判定为“是”,数据擦除处理结束。172.如以上说明,在摄像装置10中,由接收i/f110d1接收与属性信息有关的指示,由输出i/f110d2将与所接收到的指示对应的属性信息输出到后级电路13。由此,后级电路13能够通过使用属性信息请求成像元件38提供数字图像数据70b。因此,后级电路13能够从成像元件38选择性地获取需要的数字图像数据70b。并且,与同时输出数字图像数据70b和属性信息中包含的至少一部分这两者的情况相比,能够减少利用成像元件38的输出所需的耗电量。173.并且,在摄像装置10中,由控制电路110c生成与来自控制器15的垂直同步信号对应的属性信息,由输出i/f110d2将所生成的属性信息输出到信号处理电路34。因此,后级电路13能够从成像元件38获取属性信息,而无需新生成与垂直同步信号不同的信号来使用。174.并且,在摄像装置10中,由输出i/f110d2输出与存储于存储器112中的所有的数字图像数据70b中的最新的数字图像数据70b有关的属性信息。因此,后级电路13能够获取与最新的数字图像数据70b有关的属性信息。175.并且,在摄像装置10中,由输出i/f110d2输出与在由接收i/f110d1接收到垂直同步信号的定时的最新的数字图像数据70b有关的属性信息。因此,后级电路13能够获取与在由接收i/f110d1接收到垂直同步信号的定时的最新的数字图像数据70b有关的属性信息。176.并且,在摄像装置10中,输出i/f110d2能够输出多个帧的数字图像数据70b各自的属性信息,属性信息由输出i/f110d2按照摄像顺序输出。因此,后级电路13能够从成像元件38按拍摄顺序获取数字图像数据70b。177.并且,在摄像装置10中,作为属性信息,采用了包含地址、图像尺寸、摄像时刻及摄像条件的信息。因此,与属性信息中不包含地址、图像尺寸、摄像时刻及摄像条件中的任一个的情况相比,能够扩大后级电路13从成像元件38获取的数字图像数据70的用途的范围。178.并且,在摄像装置10中,在伴随下一次摄像而从存储器112中擦除数字图像数据70b的情况下,从输出i/f110d2输出的属性信息中包含标志被开启的擦除标志。因此,能够防止由后级电路13指示输出未存储于存储器112中的数字图像数据70b。179.并且,在摄像装置10中,在伴随下一次摄像而从存储器112中擦除数字图像数据70b的情况下,由控制电路110c从存储器112中擦除擦除标志被开启的属性信息,由控制电路110c从存储器112中擦除根据擦除标志被开启的属性信息中包含的地址来确定的数字图像数据70b。因此,能够在不同的定时擦除属性信息和与属性信息有关的数字图像数据70b这两者。180.并且,在摄像装置10中,由接收i/f110d1接收从控制器15发送的属性信息。在控制电路110c中,根据由接收i/f110d1接收到的属性信息从存储器112获取数字图像数据70b,由输出i/f110d2将所获取的数字图像数据70b输出到信号处理电路34。因此,成像元件38能够将后级电路13请求的数字图像数据70b输出到后级电路13。181.并且,在摄像装置10中,作为成像元件38,采用了将光电转换元件42、处理电路110及存储器112单芯片化而成的成像元件。由此,与未将光电转换元件42、处理电路110及存储器112单芯片化而成的成像元件相比,成像元件38的便携性提高。并且,与未将光电转换元件42、处理电路110及存储器112单芯片化而成的成像元件相比,能够提高设计的自由度。此外,与未将光电转换元件42、处理电路110及存储器112单芯片化而成的成像元件相比,也能够有助于摄像装置10的小型化。182.并且,如图6所示,作为成像元件38,采用了在光电转换元件42上层叠有存储器112的层叠型成像元件。由此,与未层叠光电转换元件42和存储器112的情况相比,能够提高从光电转换元件42向存储器112的图像数据的传送速度。传送速度的提高也有助于整个处理电路110中的处理的高速化。并且,与未层叠光电转换元件42和存储器112的情况相比,也能够提高设计的自由度。此外,与未层叠光电转换元件42和存储器112的情况相比,也能够有助于摄像装置10的小型化。183.并且,在摄像装置10中,基于由输出i/f110d2输出的数字图像数据70b的即时预览图像等由cpu15a显示在显示器26上。由此,能够使用户视觉辨认基于由输出i/f110d2输出的数字图像数据70b的即时预览图像等。184.此外,在摄像装置10中,由输出i/f110d2输出的数字图像数据70b由cpu15a存储于储存器15b、智能器件、个人计算机、服务器、usb存储器和/或存储卡等中。由此,能够管理由输出i/f110d2输出的数字图像数据70b。185.另外,在上述实施方式中,举出多个帧量的数字图像数据70b存储于存储器112中的方式例进行了说明,但本发明的技术并不限定于此。例如,存储器112中,除了多个帧量的数字图像数据70b以外,还可以存储压缩图像数据。压缩图像数据能够通过由图像处理电路110e进行压缩处理而得到。压缩处理是指压缩数字图像数据70b的处理。即,存储器112中,除了多个帧量的数字图像数据70b以外,还可以存储通过由作为本发明的技术所涉及的“压缩电路”的一例的图像处理电路110e压缩数字图像数据70b而得到的压缩图像数据。186.具体而言,控制电路110c将规定的帧数(在图15所示的例子中,4帧量)的数字图像数据70b存储于存储器112。并且,控制电路110c将通过由图像处理电路110e压缩数字图像数据而得到的压缩图像数据存储于存储器112。此外,控制电路110c将与压缩图像数据有关的属性信息和能够确定图像数据被压缩的压缩确定信息与压缩图像数据建立对应关联。187.在该情况下,作为一例,如图15所示,存储器112除了在上述实施方式中说明的地址以外,还具有地址“0x00540000”、“0x00580000”、及“0x005c0000”,按每个地址具有1帧量的存储区域。在图15所示的例子中,在第4帧数字图像数据70b存储于第4存储区域112d(“0x00300000”的地址的存储区域)中的情况下,由图像处理电路110e对第4帧数字图像数据70b进行压缩处理。由控制电路110c将通过压缩第4帧数字图像数据70b而得到的压缩图像数据(图15所示的例子的“压缩数据”)存储于第5存储区域112e(“0x00400000”的地址的存储区域)。188.并且,在图15所示的例子中,伴随第4帧摄像的完成,由控制电路110c从第1存储区域112a(“0x00000000”的地址的存储区域)中擦除第1帧数字图像数据70b,由控制电路110c将第5帧数字图像数据70b存储于第1存储区域112a。并且,在第5帧数字图像数据70b存储于第1存储区域112a中的情况下,由图像处理电路110e对第5帧数字图像数据70b进行压缩处理。由控制电路110c将通过压缩第5帧数字图像数据70b而得到的压缩图像数据存储于第6存储区域112f(“0x00500000”的地址的存储区域)。189.此外,在图15所示的例子中,伴随第5帧摄像的完成,由控制电路110c从第2存储区域112b(“0x00100000”的地址的存储区域)中擦除第2帧数字图像数据70b,由控制电路110c将第6帧数字图像数据70b存储于第2存储区域112b。并且,在第6帧数字图像数据70b存储于第2存储区域112b中的情况下,由图像处理电路110e对第6帧数字图像数据70b进行压缩处理。由控制电路110c将通过压缩第6帧数字图像数据70b而得到的压缩图像数据存储于第7存储区域112g(“0x00540000”的地址的存储区域)。190.如此,第4帧以后的数字图像数据70b被图像处理电路110e压缩,由控制电路110c将通过压缩而得到的压缩图像数据存储于存储器112的空闲存储区域。191.并且,在第4帧以后的数字图像数据70b被压缩,并作为压缩图像数据存储于存储器112的情况下,作为一例,如图16a及图16b所示,由控制电路110c生成属性信息。192.作为一例,如图16a所示,在第1帧~第3帧输出的属性信息是与图11a相同的属性信息。在第4帧输出的属性信息中包含与第4帧数字图像数据70b有关的属性信息。在图16a所示的例子中,作为与第4帧数字图像数据70b有关的属性信息,示出了能够确定第4存储区域112d的“0x00300000”的地址、图像尺寸、摄像时刻、摄像条件及擦除标志_关闭。并且,在第4帧输出的属性信息中包含的第1帧属性信息的擦除标志被开启。由此,伴随第5帧摄像而从第1存储区域112a中擦除第1帧数字图像数据70b。并且,在第4帧输出的属性信息还包含与第5帧数字图像数据70b的压缩图像数据有关的属性信息。在图16a所示的例子中,作为与第5帧数字图像数据70b的压缩图像数据有关的属性信息,示出了能够确定第5存储区域112e的“0x00400000”的地址、图像尺寸、摄像时刻、摄像条件及压缩确定信息。193.作为一例,如图16b所示,在第5帧输出的属性信息中包含与第5帧数字图像数据70b有关的属性信息。在图16b所示的例子中,作为与第5帧数字图像数据70b有关的属性信息,示出了能够确定第1存储区域112a的“0x00000000”的地址、图像尺寸、摄像时刻、摄像条件及擦除标志_关闭。并且,在第5帧输出的属性信息中包含的第2帧属性信息的擦除标志被开启。由此,伴随第6帧摄像而从第2存储区域112b中擦除第2帧数字图像数据70b。并且,在第5帧输出的属性信息中还包含与第5帧数字图像数据70b的压缩图像数据有关的属性信息及与第6帧数字图像数据70b的压缩图像数据有关的属性信息。在图16b所示的例子中,作为与第6帧数字图像数据70b的压缩图像数据有关的属性信息,示出了能够确定第6存储区域112f的“0x00500000”的地址、图像尺寸、摄像时刻、摄像条件及压缩确定信息。194.作为一例,如图16b所示,在第6帧输出的属性信息中包含与第6帧数字图像数据70b有关的属性信息。在图16b所示的例子中,作为与第6帧数字图像数据70b有关的属性信息,示出了能够确定第2存储区域112b的“0x01000000”的地址、图像尺寸、摄像时刻、摄像条件及擦除标志_关闭。并且,在第6帧输出的属性信息中包含的第3帧属性信息的擦除标志被开启。由此,伴随第7帧摄像而从第3存储区域112c中擦除第3帧数字图像数据70b。并且,在第5帧输出的属性信息中还包含与第5帧数字图像数据70b的压缩图像数据有关的属性信息、与第6帧数字图像数据70b的压缩图像数据有关的属性信息及与第6帧数字图像数据70b的压缩图像数据有关的属性信息。在图16b所示的例子中,作为与第7帧数字图像数据70b的压缩图像数据有关的属性信息,示出了“0x00540000”的地址、图像尺寸、摄像时刻、摄像条件及压缩确定信息。195.如此,由控制电路110c将规定的帧数的数字图像数据70b存储于存储器112,由控制电路110c还将压缩图像数据存储于存储器112,且由控制电路110c将与压缩图像数据有关的属性信息和压缩确定信息建立对应关联(在图16a及图16b所示的例子中,属性信息中包含压缩确定信息)。因此,即使在存储器112中存储有数字图像数据70b和压缩图像数据的情况下,也能够可区分地确定数字图像数据70b和压缩图像数据。196.在图16a及图16b所示的例子中,示出了与数字图像数据70b有关的属性信息中包含地址、图像尺寸、摄像时刻、摄像条件及擦除标志的方式例,但本发明的技术并不限定于此。例如,在压缩图像数据存储于存储器112的情况下,作为一例,如图17a及图17b所示,与数字图像数据70b有关的属性信息中除了地址、图像尺寸、摄像时刻、摄像条件及擦除标志以外,还可以包含表示是否预定在存储器112中存储压缩图像数据的压缩预定标志。被开启的压缩预定标志是本发明的技术所涉及的“压缩预定信息”的一例,表示预定伴随下一次摄像而在存储器112中存储压缩图像数据。被关闭的压缩预定标志表示没有预定伴随下一次摄像而在存储器112中存储压缩图像数据。197.当压缩预定标志被开启时,与压缩预定标志被开启的属性信息有关的数字图像数据70b伴随下一次摄像而被图像处理电路110e压缩。例如,如图17a所示,与在第3帧输出的属性信息中包含的第1帧数字图像数据70b有关的属性信息中包含表示压缩预定标志被开启的状态的“压缩预定标志_开启”。在该情况下,伴随下一次摄像(第4帧摄像)而第1帧数字图像数据70b被图像处理电路110e压缩,通过压缩而得到的压缩图像数据存储于第5存储区域112e。与此相伴,在第4帧输出的属性信息中包含与存储于第5存储区域112e(“0x00400000”的地址的存储区域)中的压缩图像数据有关的属性信息。与存储于第5存储区域112e中的压缩图像数据有关的属性信息中包含压缩确定信息,由此,后级电路13能够确定第5存储区域112e中存储有压缩图像数据。198.另外,擦除标志及压缩预定标志被开启的定时同步,作为一例,如图17a及图17b所示,当由控制电路110c开启擦除标志时,与此相伴,由控制电路110c也开启压缩预定标志。由此,即使从存储器112中擦除数字图像数据70b,通过压缩擦除前的数字图像数据70b而得到的压缩图像数据也由存储器112保持。199.如此,在存储器112中存储压缩图像数据的情况下,在从输出i/f110d2输出的属性信息中包含开启的压缩预定标志,因此能够对压缩图像数据的输出目的地(例如,后级电路13)赋予压缩图像数据的接受的准备宽限。200.另外,作为数字图像数据70b被压缩为压缩图像数据时的压缩形式,例如可举出mpeg、jpeg、tiff、png、gif及bmp等。在压缩图像数据存储于存储器112中的情况下,作为一例,如图18a及图18b所示,也可以在从输出i/f110d2输出的属性信息中包含能够确定压缩图像数据的压缩形式的压缩形式确定信息。在图18a及图18b所示的例子中,压缩形式确定信息与压缩确定信息一起包含在属性信息中。由此,能够使压缩图像数据的输出目的地(例如,后级电路13)根据压缩形式进行处理。201.并且,在上述实施方式中,举出在存储器112中存储1帧量的数字图像数据70b之后由输出i/f110d2输出属性信息的方式例进行了说明,但本发明的技术并不限定于此。例如,如图19所示,可以在由接收i/f110d1接收到与属性信息有关的指示(例如,垂直同步信号)的定时由输出i/f110d2输出属性信息。由此,能够根据与属性信息有关的指示即时地将属性信息提供给后级电路13。202.在上述实施方式中,举出在按每一帧输出的属性信息中包含多个帧量的属性信息的方式例进行了说明,但本发明的技术并不限定于此,例如,如图20所示,按每一帧输出的属性信息可以仅为与所对应的帧的数字图像数据70b有关的属性信息。在该情况下,与在按每一帧输出的属性信息中包含多个帧量的属性信息的情况相比,能够减少按每一帧输出到信号处理电路34的属性信息的信息量。203.另外,在图20所示的例子中,在按每一帧输出的属性信息中包含擦除标志及压缩预告标志,但本发明的技术并不限定于此,例如,如图21所示,在按每一帧输出的属性信息中可以不包含擦除标志及压缩预告标志。并且,也可以在按每一帧输出的属性信息中不包含擦除标志而包含压缩预告标志。204.并且,在上述实施方式中,举出由输出i/f110d2输出与全部帧的每一个有关的属性信息的方式例进行了说明,但本发明的技术并不限定于此,也可以从后级电路13侧向成像元件38指示使输出i/f110d2输出多少帧量的属性信息。205.在该情况下,例如,代替图13所示的属性信息输出处理,作为一例,由成像元件38的处理电路110执行图22所示的属性信息输出处理。206.图22所示的属性信息输出处理与图13所示的属性信息输出处理相比,不同点在于,具有步骤st10a来代替步骤st10,具有步骤st18a来代替步骤st18,及具有步骤st20a来代替步骤st20。控制器15经由输出i/f15d向成像元件38输出属性信息请求指示。属性信息请求指示包含垂直同步信号和输出量信息。输出量信息是指表示利用成像元件38的输出i/f110d2的属性信息的输出量的信息。这里所说的“输出量”例如由帧数规定。207.在图22所示的属性信息输出处理中,在步骤st10a中,控制电路110c判定是否由接收i/f110d1接收到从控制器15输出的属性信息请求指示。在步骤st10a中,在接收i/f110d1未接收到属性信息请求指示的情况下判定为“否”,属性信息输出处理转移到步骤st22。在步骤st10a中,在由接收i/f110d1接收到属性信息请求指示的情况下判定为“是”,属性信息输出处理转移到步骤st12。208.在步骤st18a中,控制电路110c按照由属性信息请求指示中包含的输出量信息表示的输出量选定在当前时刻保持的属性信息中使输出i/f110d2向信号处理电路34输出的属性信息。例如,若由输出量信息表示的输出量为1帧,则控制电路110c选择1帧量的与最新的数字图像数据70b有关的属性信息,若由输出量信息表示的输出量为2帧,则选择2帧量的与最新的数字图像数据70b有关的属性信息。209.在步骤st20a中,控制电路110c使输出i/f110d2向信号处理电路34输出在步骤st18a中选定的属性信息。由此,能够避免从输出i/f110d2输出必要以上的较多的属性信息。并且,由于输出量由帧数规定,因此后级电路13能够以帧单位处理属性信息。210.并且,在上述实施方式中,举出由输出i/f110d2向信号处理电路34输出属性信息及数字图像数据70b的方式例进行了说明,但本发明的技术并不限定于此。例如,如图23所示,可以由输出i/f110d2及输出i/f110d3向信号处理电路34输出属性信息及数字图像数据70b。在图23所示的例子中,处理电路110具有输出i/f110d2及输出i/f110d3。输出i/f110d3是本发明的技术所涉及的“第1输出部”的一例,输出i/f110d2是本发明的技术所涉及的“第2输出部”的一例。211.输出i/f110d3与控制电路110c连接。并且,信号处理电路34具备接收i/f34c。输出i/f110d2将属性信息输出到信号处理电路34。由信号处理电路34的接收i/f34a接收由输出i/f110d2输出的属性信息。并且,输出i/f110d3在控制电路110c的控制下将数字图像数据70b输出到信号处理电路34。由信号处理电路34的接收i/f34c接收由输出i/f110d3输出的数字图像数据70b。212.根据图23所示的结构,由输出i/f110d2输出属性信息,由输出i/f110d3输出数字图像数据70b,因此能够并行输出属性信息和数字图像数据70b。213.在上述实施方式中,例示了镜头可换式摄像装置10,但本发明的技术并不限定于此。例如,如图24所示,也可以在智能器件200上搭载有摄像装置主体214,该摄像装置主体214具有与在上述实施方式中说明的摄像装置主体12相当的结构及功能。214.作为示例,如图24所示,智能设备200具备框体212,并且摄像装置主体214容纳于框体212中。作为智能器件200的一例,可举出智能手机。在此,作为智能器件200,例如可举出作为带有摄像功能的电子设备的智能手机或平板终端等。215.成像透镜216安装于框体212上。在图24所示的例子中,成像透镜216在使智能器件200处于垂直放置的状态时的框体212的背面212a的左上部从背面212a露出。成像透镜216的中心位于光轴l1上。在摄像装置主体214上内置有成像元件38。摄像装置主体214从成像透镜216取入被摄体光。取入到摄像装置主体214内的被摄体光在成像元件38上成像,如在上述实施方式中说明的那样进行摄像。216.作为一例,如图25所示,在框体212的前表面212b设置有指示键222及触摸面板显示器224。在将智能器件200垂直放置的状态时的前表面212b的下部配置有指示键222,在指示键222的上方配置有触摸面板显示器224。触摸面板显示器224具备显示器226及触摸面板228,在显示器226上重叠有触摸面板228。触摸面板显示器224及指示键222具有与在上述实施方式中说明的ui系统器件17相同的功能。即,触摸面板显示器224及指示键222对用户提示信息,或接收来自用户的指示。来自用户的指示例如通过对显示于触摸面板显示器224上的软键(例如,与释放按钮20等相当的软键)进行触摸操作来实现。217.另外,显示器226是本发明的技术所涉及的“显示部(显示器)”的一例。并且,智能器件200是本发明的技术所涉及的“摄像装置”的一例。并且,在图24所示的例子中,示出了仅摄像装置主体214内置于智能器件200中的方式例,但本发明的技术并不限定于此,可以在智能器件200内置有多台数码相机,在该情况下,只要在至少1台数码相机中搭载有摄像装置主体214即可。218.并且,在上述实施方式中,作为成像元件38,例示了将光电转换元件42、处理电路110及存储器112单芯片化而成的成像元件,但本发明的技术并不限定于此。例如,只要将光电转换元件42、处理电路110及存储器112中的至少光电转换元件42及存储器112单芯片化即可。219.并且,在上述实施方式中,例示了属性信息是包含地址、图像尺寸、摄像时刻及摄像条件的信息,但本发明的技术并不限定于此。例如,属性信息可以是包含地址、图像尺寸、摄像时刻及摄像条件中的地址的信息,也可以是包含地址、图像尺寸、摄像时刻和/或摄像条件的信息。220.并且,在上述实施方式中,通信i/f之间按照pci-e的连接标准连接,但本发明的技术并不限定于此。也可以采用lvds、sata、slvs-ec或mipi等其他连接标准来代替pci-e连接标准。221.并且,在上述实施方式中,成像元件38与信号处理电路34之间的通信、控制器15与成像元件38的通信、及信号处理电路34与控制器15的通信均为有线形式的通信。然而,本发明的技术并不限定于此。成像元件38与信号处理电路34之间的通信、控制器15与成像元件38的通信和/或信号处理电路34与控制器15的通信也可以是无线形式的通信。222.并且,在上述实施方式中,举出ui系统器件17组装在摄像装置主体12中的方式例进行了说明,但ui系统器件17中包含的多个构成要件中的至少一部分可以外置在摄像装置主体12上。并且,ui系统器件17中包含的多个构成要件中的至少一部分也可以作为分体与外部i/f104连接来使用。223.并且,在上述实施方式中,作为帧速率例示了120fps,但本发明的技术并不限定于此,也可以将摄像用帧速率(例如,在图9所示的摄像工序中适用的帧速率)和输出用帧速率(例如,在图9所示的输出工序中适用的帧速率和/或数字图像数据70b的输出用帧速率)设为不同的帧速率。摄像用帧速率和/或输出用帧速率可以是固定的帧速率,也可以是可变的帧速率。在可变的帧速率的情况下,例如可以在满足规定条件(例如,由接收器件84接收到变更帧速率的指示的条件和/或作为变更帧速率的定时而事先确定的定时到来的条件)的情况下变更帧速率。在可变的帧速率的情况下,帧速率的具体的数值例如可以根据由接收器件84接收到的指示来变更,也可以根据后级电路13和/或成像元件38的运转率来变更。224.并且,在上述实施方式中,例示了信号处理电路34,但本发明的技术并不限定于此,除了信号处理电路34以外,还可以使用一个以上的信号处理电路。在该情况下,只要将成像元件38与多个信号处理电路分别直接连接即可。225.并且,在上述实施方式中,举出处理电路110由包含asic及fpga的器件来实现的方式例进行了说明,但本发明的技术并不限定于此。例如,也可以通过基于计算机的软件结构来实现处理电路110中包含的多个器件中的至少控制电路110c。226.在该情况下,例如,如图26所示,在成像元件38中内置有计算机852,将用于使计算机852执行上述实施方式所涉及的属性信息输出处理的属性信息输出程序902和用于使计算机852执行上述实施方式所涉及的数据擦除处理的数据擦除程序904存储于存储介质900中。作为存储介质900的一例,可举出作为非临时存储介质的ssd或usb存储器等任意的便携式存储介质。以下,为了便于说明,在不需要区分说明属性信息输出处理及数据擦除处理的情况下,称为“成像元件侧处理”,在不需要区分说明属性信息输出程序902及数据擦除程序904的情况下,称为“成像元件侧程序”。227.计算机852具备cpu852a、储存器852b及存储器852c。储存器852b是eeprom等非易失性存储装置,存储器852c是ram等易失性存储装置。存储于存储介质900中的成像元件侧程序安装于计算机852。cpu852a根据成像元件侧程序执行成像元件侧处理。228.成像元件侧程序可以不存储于存储介质900中而存储于储存器852b中。在该情况下,cpu852a从储存器852b中读出成像元件侧程序,将所读出的成像元件侧程序扩展到存储器852c。并且,cpu852a根据扩展到存储器852c的成像元件侧程序来执行成像元件侧处理。229.并且,在此,举出了属性信息输出程序902及数据擦除程序904存储于储存器852b中的方式例,但并不限于此,也可以将属性信息输出程序902及数据擦除程序904中的一者存储于储存器852b中,将另一者存储于存储介质900中。230.并且,也可以在经由通信网络(省略图示)与计算机852连接的其他计算机或服务器装置等存储部中存储成像元件侧程序,根据上述摄像装置10或智能器件200的请求下载成像元件侧程序并安装于计算机852。231.另外,不需要在与计算机852连接的其他计算机或服务器装置等存储部中存储全部成像元件侧程序,可以存储成像元件侧程序的一部分(例如,属性信息输出程序902或数据擦除程序904)。232.在图26所示的例子中,例示了成像元件38中内置有计算机852的方式例,但本发明的技术并不限定于此,例如计算机852可以设置在成像元件38的外部。233.在图26所示的例子中,cpu852a是单个cpu,但也可以是多个cpu。并且,也可以适用gpu来代替cpu852a。234.在图26所示的例子中,例示了计算机852,但本发明的技术并不限定于此,也可以适用包含asic、fpga和/或pld的器件来代替计算机852。并且,也可以使用硬件结构及软件结构的组合来代替计算机852。235.作为执行在上述实施方式中说明的成像元件侧处理的硬件资源,能够使用以下所示的各种处理器。作为处理器,例如可举出通用的处理器即cpu,如上所述,通过执行软件即程序,作为执行成像元件侧处理的硬件资源而发挥功能。并且,作为处理器,例如可举出作为处理器的专用电路,所述处理器具有fpga、pld、或asic等为了执行特定的处理而专门设计的电路结构。任何处理器中都内置或连接有存储器,通过任何处理器都使用存储器来执行信息处理装置侧处理。236.执行成像元件侧处理的硬件资源可以由这些各种处理器中的一个构成,也可以由相同种类或不同种类的两个以上的处理器的组合(例如,多个fpga的组合、或cpu与fpga的组合)构成。并且,执行成像元件侧处理的硬件资源可以是一个处理器。237.作为由一个处理器构成的例子,第一,存在如下方式:如以客户端及服务器等计算机为代表,由一个以上的cpu和软件的组合来构成一个处理器,该处理器作为执行成像元件侧处理的硬件资源而发挥功能。第二,存在如下方式:如以soc等为代表,使用由一个ic芯片来实现包括执行成像元件侧处理的多个硬件资源的整个系统的功能的处理器。如此,成像元件侧处理通过使用一个以上上述各种处理器作为硬件资源来实现。238.此外,作为这些各种处理器的硬件结构,更具体而言,能够使用将半导体元件等电路元件进行了组合的电路。239.并且,在图1所示的例子中例示摄像装置10,在图24所示的例子中例示了智能器件200,但本发明的技术并不限定于此。即,本发明的技术也能够适用于内置有具有与在上述实施方式中说明的摄像装置主体12相当的结构及功能的摄像装置的各种电子设备(例如,镜头固定式相机、个人计算机或可穿戴终端装置等),并且即使在这些电子设备中,也能够得到与摄像装置10及智能器件200相同的作用及效果。240.并且,在上述各实施方式中,例示了显示器26及226,但本发明的技术并不限定于此。例如,可以将附接到摄像装置的单独的显示器用作本发明的技术所涉及的“显示部”。241.并且,上述各种处理仅为一例。因此,在不脱离主旨的范围内,当然可以删除不必要的步骤,或者追加新的步骤,或者切换处理顺序。242.以上所示的记载内容及图示内容是关于本发明的技术所涉及部分的详细说明,只是本发明的技术的一例。例如,与上述结构、功能、作用及效果有关的说明是与本发明的技术所涉及部分的结构、功能、作用及效果的一例有关的说明。因此,在不脱离本发明的技术的主旨的范围内,当然可以对以上所示的记载内容及图示内容删除不必要的部分,或者追加新的要素,或者进行替换。并且,为了避免复杂化,并且为了容易理解本发明的技术所涉及的部分,在以上所示的记载内容及图示内容中,省略了在能够实施本发明的技术的方面不需要特别说明的与技术常识等有关的说明。243.在本说明书中,“a和/或b”与“a及b中的至少一个”的含义相同。即,“a和/或b”是指可以只是a,可以只是b,也可以是a及b的组合。并且,在本说明书中,附加“和/或”来表现3个以上的事项的情况下,也可以适用与“a和/或b”相同的概念。244.本说明书中所记载的所有文献、专利申请及技术标准,以与具体且分别记载通过参考而援用各文献、专利申请及技术标准的情况相同程度,通过参考而援用于本说明书中。245.关于以上实施方式,进一步公开以下附记。246.(附记1)247.一种成像元件,其内置有:248.处理器;及249.存储器,存储通过拍摄而得到的图像数据,且内置于上述成像元件中,250.上述处理器进行如下:251.控制上述图像数据向上述存储器的存储,252.将上述图像数据的属性信息存储于上述存储器,253.输出存储于上述存储器中的上述图像数据,254.接收与上述属性信息有关的指示,255.输出与所接收到的上述指示对应的上述属性信息。当前第1页12当前第1页12

再多了解一些

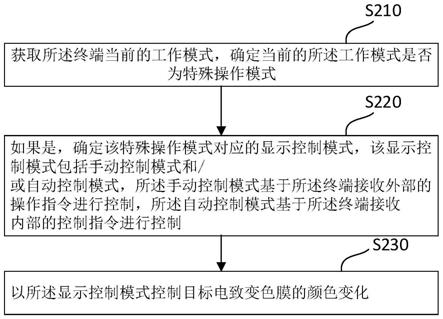

本文用于企业家、创业者技术爱好者查询,结果仅供参考。