1.本发明构思涉及一种量子比特设备以及一种用于操作量子比特设备的方法。

背景技术:

2.近年来,半导体量子点量子比特的发展取得了长足进步。半导体量子点使得能够通过限制在量子点处的电子的自旋状态来限定高保真量子比特(即,“自旋量子比特”)。可以使用静电栅从2deg在例如硅基平台中形成半导体量子点。采用来自cmos技术的常规制造技术,这使得能够紧凑地实现自旋量子比特。尤其由于这些原因,半导体量子点量子比特技术代表了可扩展量子比特系统的有前途的候选。

3.可以使用电子自旋谐振(esr)来控制量子点自旋量子比特,其中自旋状态由射频ac磁场操纵。在电偶极自旋谐振(edsr)中,自旋状态替代地由射频ac电场操纵。与esr相比,edsr使得能够实现用于量子比特控制的较有效且较简单的脉冲方案。然而,edsr依赖于电场与量子比特的自旋之间的耦合,并且电子在例如硅中的自旋轨道耦合典型地太弱而不能支持edsr。这已在现有技术中通过并有片上微磁体以在量子点处产生空间可变的面内自旋电场耦合场的构思验证设备来解决(例如,mohiyaddin f.a等人的“multiphysics simulation&design of silicon quantum dot qubit devices[硅量子点量子比特设备的多物理模拟和设计]”,iedm)。

[0004]

虽然最近取得了进展,但是仍然需要进一步促进可扩展性的量子比特设备设计。

技术实现要素:

[0005]

本发明构思的目的是提供一种改进的量子比特设备,该改进的量子比特设备促进扩展到较多数量的量子比特。可以从下文中进行理解另外的和替代性的目的。

[0006]

根据本发明构思的一方面,提供了一种量子比特设备,包括:

[0007]

半导体衬底层;

[0008]

一组控制栅,该组控制栅被配置成沿着该衬底层限定一行静电限制量子点,每个量子点适于保持量子比特;以及

[0009]

一组纳米磁体,该组纳米磁体在该衬底层上方布置成行,以使得纳米磁体布置在该行量子点中的每隔一个量子点上方,

[0010]

其中每个纳米磁体具有相对于该衬底层的面外磁化,并且其中每隔一个量子点经受由相应纳米磁体产生的面外磁场,以使得每隔一个量子点的量子比特自旋谐振频率相对于该行量子点中的邻近量子点偏移。

[0011]

本发明的量子比特设备提供了一种实现多量子比特系统的可扩展设计。

[0012]

该设备支持限定适合保持电子量子比特(比如,单电子量子比特)的面积有效且高度限制的量子点。使用控制栅以限定静电限制量子点进一步能够通过改变量子点处的电势而在邻近量子点之间依序穿梭量子比特/电子来耦合量子点之间的相邻量子点量子比特转移。

[0013]

纳米磁体提供的小尺寸以及它们在衬底上方的布置有助于设备设计的面积效率。

[0014]

此外,提供相对于衬底层具有面外磁化的纳米磁体允许在每个纳米磁体下方的相应量子点中诱发出磁场(具有面外取向)。在纳米磁体中的相应者下(并因此与其对准)限定(仅限定)该行量子点中的每隔一个量子点引起每隔一个量子点处的量子比特自旋谐振频率相对于邻近量子点偏移。这转而允许位于纳米磁体下方的量子点中的量子比特被选择性地寻址到不位于纳米磁体下方的量子点中的量子比特。

[0015]

磁场的面外取向进一步减轻了不期望的自旋轨道耦合以及由衬底-界面非均匀性产生的朗德g因子的变化。量子点处的面内磁场可能引起残余自旋轨道耦合,这可能对量子比特谐振频率引入一定程度的不可预测性。

[0016]

该行量子点可以相应地限定量子点的第一子组和量子点的第二子组,第一子组的量子点与第二子组的量子点交替,其中第一子组的每个量子点被限定在纳米磁体中的相应者下,并且具有相对于量子比特的第二子组的邻近量子比特偏移的量子比特自旋谐振频率。为了简明起见,在纳米磁体中的相应者下限定的任何量子点在下文中可以相应地被称为第一量子点。对应地,邻近于第一量子点限定的任何量子点可以被称为第二量子点。

[0017]

如从下文将变得显而易见的是,每个第一量子点可以用于控制量子比特,而每个第二任何量子点可以用于保持空闲量子比特。因此,第一量子点和第二量子点可以被称为“活动”量子点和“空闲”量子点。

[0018]

如本文所使用,术语“面外”(例如,关于磁化或磁场)是指至少具有横向于衬底层(例如,横向于衬底层的主延伸平面)的主要分量的取向或方向。

[0019]

如本文所使用,术语“纳米磁体”是指具有亚微米尺寸的永磁体,例如,具有至少亚微米长度尺寸(即,沿着行的纵向方向)、优选也具有亚微米宽度尺寸(即,沿着行的横向方向,相对于衬底层在面内)的永磁体。纳米磁体的高度或厚度尺寸(即,相对于衬底层沿着面外方向)也可以是亚微米尺寸。根据实施例,纳米磁体的长度尺寸和宽度尺寸可以是200nm或更小,有利地是150nm或更小。在任何情况下,纳米磁体的长度尺寸都可以使得每个纳米磁体仅在单一相应量子点上方延伸(即,“覆盖”)。纳米磁体的高度尺寸可以大于长度和/或宽度尺寸,比如,200nm或更大。

[0020]

衬底层可以是硅衬底层。硅支持限定高保真静电限制量子点量子比特。此外,鉴于硅在集成电路技术中几乎无处不在的使用,它代表了量子比特设备的有利平台。

[0021]

除了纳米磁体之外,量子比特设备还可以包括被配置成向每个量子点贡献均匀的面外磁场的磁布置。应理解,这种磁场贡献是纳米磁体产生的面外磁场的补充。

[0022]

根据实施例,所述每隔一个量子点中的每个量子点可以具有相同的第一量子比特自旋谐振频率,并且所述邻近量子点中的每个量子点可以具有相同的第二自旋谐振频率。

[0023]

纳米磁体下方的每隔一个量子点(即,第一量子点)因此可以呈现共同的“第一”自旋谐振频率。对应地,邻近于每隔一个量子点中的一个的每个量子点(即,第二量子点)可以呈现共同的“第二”自旋谐振频率。在此上下文中,“共同的”第一自旋谐振频率/第二自旋谐振频率确实意味着第一子组/第二子组的相应量子点中的每个量子比特可以用相同频谱内容的振荡场(磁场或电场)激发。也就是说,共同的第一自旋谐振频率/第二自旋谐振频率意味着所有第一量子点的自旋谐振频率重叠,并且所有第二量子点的自旋谐振频率重叠。因此,第一量子点可以被并行寻址,选择性地寻址到第二子组的量子点中的任何一个中的量

子比特。第一量子比特自旋谐振频率与第二量子比特自旋谐振频率之间的间隔可以比第一量子比特自旋谐振频率和第二量子比特自旋谐振频率的(相应)线宽大,有利地大两个量级或更多。第一量子点和邻近第二量子点处的面外磁场强度的差异可以有利地为5mt或更大。

[0024]

根据实施例,该组控制栅可以包括沿着该行量子点的纵向方向交替布置的势垒栅和柱塞栅(plunger gates)。

[0025]

这种配置能够使用有限数量的控制栅来限定高度限制的量子点。

[0026]

如本文所使用,术语“势垒栅”指的是被配置成在该行量子点的纵向方向上限制量子点的栅。每个势垒栅可以在每对相邻量子点之间限定隧道势垒。

[0027]

如本文所使用,术语“柱塞栅”指的是被配置成控制相应量子点的(电化学)电势的栅。因此,每个柱塞栅与相应量子点相关联。每个柱塞栅可以控制在相关联的量子点处积累的电荷。

[0028]

该组控制栅可以进一步包括一对纵向限制栅,该对纵向限制栅布置在该行量子点的相互相对侧处。

[0029]

如本文所使用,术语“纵向限制栅”(为了简洁起见,“限制栅”)指的是被配置成相对于该行量子点在横向方向上(相对于衬底层在面内)限制量子点的栅。该对限制栅可以为该行的所有量子点所共有,从而限制了所需的控制栅的数量。

[0030]

势垒栅可以全部具有相同栅长度,并且以规则间距(即,中心到中心的距离)布置。柱塞栅可以全部具有相同栅长度,并且每个柱塞栅可以在相应的一对势垒栅之间居中。

[0031]

势垒栅和柱塞栅的规则布置能够限定量子比特的静电势,该静电势沿着该行量子点的纵向方向(即,“量子比特行方向”)周期性变化。除了有助于量子点的均匀电特性之外,已认识到量子比特的周期性且规则的电势使得量子比特设备的操作对纳米磁体的可能对准误差不太敏感。如可以了解的是,纳米磁体的间距可以两倍于势垒栅的间距。

[0032]

势垒栅的间距可以在50nm至150nm的范围内。势垒栅和邻近柱塞栅之间的中心到中心的距离可以是势垒栅间距的一半。势垒栅和/或柱塞栅的栅长度可以是20nm至70nm。

[0033]

量子比特设备可以被配置成向每个势垒栅施加相同的势垒栅电势。如果与势垒栅和柱塞栅的规则布置组合,这可以进一步有助于沿着该行量子点的电势的周期性。

[0034]

该组纳米磁体可以布置在该组控制栅上方的共同层级处。

[0035]

也就是说,该组纳米磁体中的每个纳米磁体可以布置在该组控制栅上方、相对于衬底层的(相同)层级处。将纳米磁体布置在栅上方的层级处可以促进制造。进一步地,纳米磁体的高度(即,竖直尺寸)可以自由选择,而不影响栅在半导体衬底层上方的层级。这种布置也可以防止纳米磁体干扰栅。

[0036]

如果该组控制栅包括如上文所论述的势垒栅和柱塞栅,那么势垒栅和柱塞栅可以布置在衬底层上方的(相同)第一层级处,并且该组纳米磁体可以布置在第一层级上方的(相同)第二层级处。

[0037]

如果该组控制栅进一步包括如上文所论述的一对限制栅,那么限制栅可以布置在衬底上方的第三层级,第三层级位于第二层级下方。纳米磁体、势垒栅和柱塞栅以及限制栅因此可以设置在衬底层上方的不同的相应层级处,从而实现了堆叠的并因此面积有效的设计。限制栅的第三层级可以低于势垒栅和柱塞栅的第一层级。然而,替代配置也是可能的。

[0038]

根据实施例,量子比特设备可以进一步包括布置在衬底层上并嵌入该组控制栅的

电介质层结构,其中量子点可以被限定在衬底层与电介质层结构之间的界面处。这实现了单片量子比特设备,该单片量子比特设备可以依赖于来自常规cmos设备制造的处理技术(例如,电介质层沉积、栅层沉积和图案化等)以合理方式制造。

[0039]

根据实施例,量子比特设备可以被配置成:将量子比特从邻近量子点转移到所述每隔一个量子点中的所选择的量子点,这是通过改变与所选择的量子点相关联的柱塞栅的电势以及与所述邻近量子点相关联的柱塞栅的电势而进行的;并且在所选择的量子点处向所选择的量子比特供应射频电或磁控制场,以控制所选择的量子比特的自旋状态。

[0040]

因此,通过将量子比特(例如,电子)从第二/空闲量子点转移/穿梭到第一/活动量子点而实现了选择性量子比特控制。

[0041]

根据基于esr的量子比特控制,可以施加与所选择的量子比特谐振的ac磁控制场以使量子比特的自旋旋转。

[0042]

纳米磁体还实现了基于edsr的量子比特控制:由每个纳米磁体产生的磁场可以在下方的量子点处诱发出具有非零面内分量的空间磁梯度场。

[0043]

因此,每隔一个量子点(即,每个第一量子点)可以被限定在空间变化的磁场内,从而允许通过edsr来进行量子比特控制。该分量可以有利地是横向于行方向的面内分量(相对于衬底层),因为这可以促进量子比特的自旋旋转和振荡控制的较快响应。

[0044]

也就是说,量子比特设备可以被配置成通过以下方式来控制保持在量子点处的量子比特的自旋状态:使用布置在该行量子点的相对侧处的一对控制栅,使量子比特沿着横向于该行量子比特的纵向方向的方向在磁梯度场内空间振荡。

[0045]

该对控制栅可以产生变化的电场,以使得量子比特由于其振荡而经受与量子比特自旋谐振频率谐振的变化的面外磁场。

[0046]

该对控制栅可以有利地是上文所论述的该对纵向限制栅。因此,限制栅可以产生变化的电场,以使得该行量子点中的每个量子比特以一定频率振荡,而使得自旋谐振(即,自旋旋转)仅在第一量子点中的量子比特中(即,纳米磁体下)被诱发。

[0047]

每个量子点处的梯度振幅可以例如沿着横向方向至少为0.1mt/nm,有利地至少为0.4mt/nm。

[0048]

根据实施例,量子比特设备可以进一步包括连接到该组控制栅的柱塞栅的一个或多个射频谐振器。这通过检测自旋相关的谐振频率而实现了量子比特读出。

[0049]

量子比特设备可以包括一组射频谐振器,每个谐振器可以连接到该组控制栅的相应柱塞栅。这实现了由与连接到谐振器的柱塞栅相关联的量子点所保持的量子比特的读出。

[0050]

每个谐振器可以例如连接到布置在纳米磁体下所限定的量子点(即,相应的第一量子点)处的相应柱塞栅。

[0051]

量子比特设备可以被配置成:将要读取的量子比特从邻近量子点转移到与连接到谐振器的柱塞栅相关联的所选择的量子点,这是通过改变与所选择的量子点相关联的柱塞栅的电势以及与所述邻近量子点相关联的柱塞栅的电势而进行的;并且随后检测连接到与所选择的量子点相关联的柱塞栅的谐振器的谐振频率。

[0052]

因此,通过将量子比特(例如,电子)转移/穿梭到与柱塞栅相关联的量子点并感测与量子点相关联的谐振器的所得谐振频率而实现了选择性量子比特读出。

[0053]

根据实施例,量子比特设备可以进一步包括沿着该行量子点延伸的esr传输线。esr传输线可以布置在纳米磁体上方的层级上,以在纳米磁体与量子点之间实现较小间隔。

[0054]

根据实施例,量子比特设备可以进一步包括连接到纳米磁体的非磁性金属层。因此,纳米磁体可以维持在相同电势。非磁性金属层可以有利地布置在纳米磁体的顶部。非磁性金属层可以进一步连接到地。因此,可以减轻操作期间的放电的风险。

[0055]

该量子比特设备可以进一步包括一对贮存栅,该对贮存栅布置在该行量子比特的相对端处,并且被配置成向该行量子比特供应量子比特。

[0056]

根据本发明构思的第二方面,提供了一种用于操作量子比特设备的方法,该方法用于操作量子比特设备,该方法包括:

[0057]

使用一组控制栅沿着衬底层限定一行静电限制量子点,每个量子点适于保持量子比特,

[0058]

其中每隔一个量子点被限定在该衬底层上方布置成行的一组纳米磁体中的相应纳米磁体下,其中每个纳米磁体具有相对于该衬底层的面外磁化,并且其中每隔一个量子点中的每一个经受由相应纳米磁体产生的面外磁场,以使得每隔一个量子点的量子比特自旋谐振频率相对于该行量子点中的邻近量子点偏移。

[0059]

此方面总体上可以呈现与前一方面相同或对应的优点。因此,参考上述论述。特别地,对上文所述的量子比特设备或其某一元件的功能或操作的任何引用可以形成该方法的步骤或动作。

附图说明

[0060]

通过参照附图进行的以下说明性且非限制性的详细描述,将更好地理解本发明构思的以上及附加的目的、特征和优点。在附图中,除非另有说明,否则相同的附图标记将用于相同的元件。

[0061]

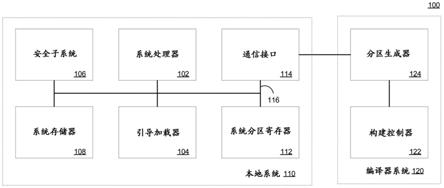

图1是量子比特设备的示意性俯视图。

[0062]

图2a至图2f是量子比特设备的示意性透视图和对应的截面图。

[0063]

图3a至图3b示意性地展示了量子比特在邻近量子点与单量子比特栅和双量子比特栅之间的穿梭。

[0064]

图4a至图4c示意性地示出了量子比特穿梭期间的量子点电势的控制。

[0065]

图5a至图5d示出了使用纳米磁体的示例配置获得的磁场的各种特性。

具体实施方式

[0066]

图1是量子比特设备100的示意性俯视图。量子比特设备100可以例如用在量子计算设备中。可以实施的算法的示例包含量子化学算法和格罗弗搜索算法。图1所描绘的量子比特设备100的元件中的一些以透明方式示出,以允许同时观察下方的元件。量子比特设备100包括半导体衬底层110。衬底层110可以是例如各向同性纯化的硅的硅层。衬底层110的其他示例材料包含gaas和sige。x和y分别表示相对于衬底层110(即,平行于衬底层110)的第一面内方向和第二面内方向。z表示例如垂直于衬底层110的面外方向。应注意,负z方向(即,-z)也被认为是相对于衬底层110的面外方向。方向x和y也可以被称为第一水平方向和第二水平方向,而z可以称为竖直方向。

[0067]

量子比特设备100包括一组控制栅112、114、116,该组控制栅被配置成沿着衬底层110限定一行静电限制量子点122。如下文将进一步描述的,量子比特设备100可以包括沿着衬底层110限定电介质-半导体界面的电介质层,其中量子比特122可以被限定在界面处。该行(即,其纵向方向)可以被限定为平行于x方向延伸。因此,横向于行方向的方向(即,行的横向方向)可以平行于y方向。量子设备100相应地适于实现线性或1d量子比特阵列。如可以了解的是,量子计算设备可以包括多个这样的1d量子比特阵列,它们彼此独立地操作。

[0068]

每个量子点122可以保持限定量子比特的一个或多个电子。然而,为了简单起见,下文的公开内容将涉及单电子量子比特。进一步设想到,量子比特设备100的原理与基于空穴的量子比特兼容,但是空穴由于其固有的自旋轨道耦合而可能较难控制。

[0069]

量子比特设备100进一步包括在衬底层110上方布置成行的一组纳米磁体124。如所展示的,该行纳米磁体可以在该行量子点122上方并沿着该行量子点延伸(即,当限定了该行量子点122时,在设备100的操作期间)。每个纳米磁体124具有相对于衬底层110的面外磁化。每隔一个量子点122a被限定在纳米磁体124中的相应者下方,并且因此经受由上方的相应纳米磁体124产生的面外磁场。在图1和随后的图中,沿着该行量子点122没有填充的圆表示位于纳米磁体124下方的量子点122a(“第一/活动量子点”)。实心圆(filled circle)表示不位于纳米磁体124下方的量子点122b(“第二/空闲量子点”)。因此,将假设每个第一量子点122处的纳米磁体124的磁化和对应磁场平行于面外方向z。

[0070]

由相应纳米磁体124产生的磁场引起相应纳米磁体124下方的量子点122a的量子比特自旋谐振频率相对于邻近(相邻)的、其上方没有纳米磁体124的量子点122b偏移。量子比特在具有强度b的磁场中的自旋谐振频率可以被表达为e

zs

/h=geμbb/h,其中e

zs

是自旋状态之间的塞曼分割,h是普朗克常数,ge是电子g因子,并且μb是玻尔磁子。在第一量子点122a处的量子比特经历的磁场强度将不同于在第二量子点122b处的量子比特经历的磁场强度,并且因此这些量子比特的谐振频率也将不同。

[0071]

如图1所示,也可以在量子点122处提供具有面外取向(例如,平行于z或-z方向)的均匀磁场贡献b0。可以出于说明的目的而称为外部磁场b0的磁场b0可以由一个或多个永磁体和/或电磁体的磁布置产生。如可以了解的是,磁场b0也可以由在量子比特设备100外部的一个或多个磁体产生。

[0072]

因此,量子点122中的量子比特所经历的有效磁场可以由外部磁场b0和纳米磁体124在量子点122的位置处产生的局部磁场的总和给出。如可以了解的是,纳米磁体124因此可以引起沿着该行量子点122的面外磁场的局部变化,以使得每个第一量子点122a的量子比特自旋谐振频率相对于该行的每个邻近第二量子点122b偏移。

[0073]

再次转向图1,每个第一量子点122a可以具有相同的第一量子比特自旋谐振频率,并且每个第二量子点122b可以具有相同的第二自旋谐振频率。这使得能够使用相同的控制信号来控制第一量子点122a中的任一个第一量子点中的量子比特。这相应地适用于第二量子点122b中的任一个第二量子点中的量子比特。可以例如使用一组相同的纳米磁体124实现相同的谐振频率,这些纳米磁体与量子点122对准,以使得每个第一量子点122a和每个第二量子点122b沿着z方向经历相应的(至少基本上)相等的磁场强度。然而,可以设想,例如第一量子点122a的不同子组可以具有不同的相应的量子比特自旋谐振频率(并且对应地,第二量子点122b也是如此),这是例如通过使用具有不同强度和/或布置在量子点122上方

不同层级处的纳米磁体124实现的。

[0074]

所展示的量子比特设备100的该组控制栅包括沿着行方向(即,沿着x方向)交替布置的势垒栅112和柱塞栅114。在下文中,附图标记114将用于统一指代柱塞栅114,而附图标记114a和114b将分别指代与第一量子点122a和第二量子点122b相关联的柱塞栅。该组控制栅进一步包括一对(纵向)限制栅116。限制栅116被布置在该行量子点122的相互相对侧处,并且沿着该行量子点延伸。量子点122可以由势垒栅112沿着x方向静电限制,并由限制栅116沿着y方向静电限制。势垒栅112和限制栅116可以被偏置,以引起栅112、116下方的自由电子的耗尽。每个量子点122的电化学电势以及因此累积的电子数量可以由相应柱塞栅114a控制。

[0075]

如图所示,势垒栅112可以各自具有相同的栅长度,并且以规则的间距布置。类似地,柱塞栅114可以各自具有相同栅长度,并且布置在相应的一对势垒栅112之间的中心位置处。量子点122因此可以被限定为具有对应于势垒栅的间距的规则间距/间隔,如图1中的p

dot

所表示。纳米磁体124的间距/间隔可以对应于量子点间距的两倍,p

magnet

=2p

dot

。为了进一步规则地增加栅图案,势垒栅122和柱塞栅114的栅长度可以相同,但是这不是必需的。

[0076]

举例来说,量子点间距可以例如是约50nm至150nm。势垒栅的间距可以在50nm至150nm的范围内。势垒栅和邻近柱塞栅之间的中心到中心的距离可以是势垒栅间距的一半。势垒栅和/或柱塞栅的栅长度可以是20nm至70nm。。

[0077]

每个势垒栅112可以被配置成向每个势垒栅112施加相同的势垒栅电势/电压。邻近量子点122a、122b之间的隧道势垒的高度因此可以沿着该行量子比特122相同。隧道势垒高度可以例如在5mev到15mev的范围内。这在假定了量子点间距p

dot

在上述范围中的情况下可以产生约1ghz的隧道耦合tc。可以通过较低的隧道势垒高度获得较大的隧道耦合值。例如,可以通过40μev至400μev的范围中的隧道势垒高度实现10ghz至100ghz的范围中的隧道耦合tc。可以选择柱塞栅114的电压,以使得一个或零个电子被限制在相关联的量子点122中。

[0078]

限定量子比特的电子可以从相应电子贮存器装载到该行量子比特112中或者从该行量子比特卸载,这些电子贮存器被限定在相应贮存栅118下,这些贮存栅被布置在该行量子比特122的相对端处。电子贮存器可以例如是2deg。

[0079]

量子比特设备100可以通过控制量子点122的电势来实现量子比特沿着该行量子点122的穿梭。图3a中示意性地描绘了使量子比特(“量子比特3”)在一对邻近量子比特122a、122b之间穿梭/转移的示例。图4a至图4c示意性地展示了转移之前(图4a)、隧穿期间(图4b)和完成转移之后(图4c)的相应量子点122a、122b的势阱和量子比特3的位置。相应势阱中的两对实线和虚线表示能级的塞曼分割。当从电子贮存器装载电子/向电子贮存器卸载电子时,通过相对于电子贮存器的电势降低或增加邻近于电子贮存器的量子点122的电势,可以应用类似做法。

[0080]

通常可以如下实现单量子比特栅:可以将所选择的量子比特(例如,“量子比特3”)从邻近量子点122b转移到第一/活动量子点122a(例如,如结合图3a和4a至图4c所论述)。所选择的量子点122a处的量子比特接着可以经受射频电控制场(用于基于edsr的量子比特控制)或磁控制场(用于基于esr的量子比特控制)以控制所选择的量子比特的自旋状态。

[0081]

如图3b所展示,通过将所选择的第一量子比特(例如,“量子比特3”)转移到邻近于

也保持量子比特(例如,“量子比特2”)的第二/空闲量子点122b的第一/活动量子点122a,可以以对应方式实现双量子比特栅(例如,cnot/cz)。接着,可以基于所选择的量子点122a和邻近量子点122b中的量子比特(例如,“量子比特2和3”)之间的交换耦合的调谐来执行双量子比特操作(依赖于esr或edsr)。可以通过改变量子点122a、122b之间的隧道耦合或能量解谐来调谐交换耦合。

[0082]

为了支持基于esr的量子比特控制,量子比特设备100可以进一步包括沿着该行量子点122延伸的电子自旋谐振esr传输线130。量子比特设备100可以包括射频产生电路,该射频产生电路用于向esr传输线130供应esr控制信号而以常规方式实现基于esr的量子比特控制。

[0083]

作为基于esr的量子比特控制的替代或补充,量子比特设备100可以允许基于edsr的量子比特控制。每个纳米磁体124可以在相关联的量子点122a的位置处诱发出具有非零面内分量(例如,dby/dy)的空间磁梯度场。因此,可以经由edsr通过使量子比特沿着面内方向在磁梯度场内空间振荡来控制保持在第一量子点122a处的量子比特的自旋状态。通过改变布置在量子点的相对侧处的一对控制栅(比如,限制栅116)的电势,可容易实现约1nm的振荡幅度。

[0084]

作为对横向磁梯度场分量dby/dy的替代,edsr可以依赖于纵向磁梯度场分量dbx/dy,在这种情况下,可以使用一对势垒栅112来控制量子比特在磁梯度场内的纵向振荡。

[0085]

为了实现量子比特状态的读出,量子比特设备100可以进一步包括图1中由附图标记132统一表示的一个或多个射频谐振器。如图所示,谐振器132可以连接到与第一量子点122a相关联的每个柱塞栅114a。每个谐振器132可以通过相应传输线连接到相关联的柱塞栅112。谐振器132的频率将取决于相关联的量子点122a处的量子比特的状态。

[0086]

参考图3b,因此可以通过以下方式来检测量子比特的状态:将所选择的第一量子比特(例如,“量子比特3”)转移到与谐振器132相关联并且邻近于也保持量子比特(例如,“量子比特2”)的第二/空闲量子点122b的第一/活动量子点122a;以及例如通过测量谐振器132的反射率来检测所得的谐振频率。当邻近量子点122a、122b处的量子比特以适当方式偏压时,泡利自旋排斥原理引起量子比特/电子到其邻近量子点122b的自旋相关的隧穿。这种自旋相关的点间隧穿可以修改谐振器132的电容并因此修改其谐振频率,从而促进自旋读出。

[0087]

根据替代配置,谐振器132可以替代地连接到与第二量子点122b相关联的每个柱塞栅114,其中可以通过将要读取的量子比特转移到与柱塞栅114b相关联的量子点122b来以对应方式执行读出。采用连接到柱塞栅114(例如,柱塞栅114a或114b)的共用集总元件谐振器,可以应用类似的读出做法。

[0088]

图5a至图5d示出了可以使用定位在量子点122a上方100nm处、具有100nm的长度尺寸、100nm的宽度尺寸以及200nm的高度的钴(co)纳米磁体获得的磁场的各种特性。方框和圆圈分别表示纳米磁体124和第一量子点122a/第二量子点122b相对于磁场的位置。

[0089]

图5a示出了两个第一量子点122a和邻近第二量子点122b的区域中的有效磁场的面外分量bz的强度。轴线表示相对于第二量子点122b的空间坐标,单位为纳米。如所表示的,纳米磁体124的使用使得能够获得第一量子点122a和第二量子点122b处例如约10mt的磁场强度差异。这转化为约280mhz的谐振频率差异,该谐振频率差异比静电限定的量子点

的典型最大量子比特线宽(例如,约1mhz)大两个以上量级。

[0090]

图5b示出了横向磁梯度场分量dby/dy。如图所示,纳米磁体124的使用实现了约0.5mt/nm的面内磁梯度。

[0091]

图5c示出了量子点122a、122b中的约0.3mt/nm的纵向磁梯度场分量dbx/dx。

[0092]

图5d示出了由限定的纳米磁体124的示例配置的去相位梯度。当与电场噪声耦合时,面内磁场相对于z方向的导数引起去相位。因此,在理想的周期性晶格中,dg应该为零,如图5d中可见,这对于示例配置,几乎得以实现。

[0093]

图2a至图2f是更详细地示出了量子比特设备100的结构和几何形状的示意性透视图和对应截面图。

[0094]

图2a和图2b从两个不同角度示出了量子比特设备100的部分。如图所示,电介质层结构120布置在衬底层110(例如,其可以是硅层)上,并嵌入该组控制栅112、114、116。电介质层结构120被示意性地示出为单一层结构,但是可以典型地包括多层不同的电介质材料,比如,不同的氧化物,例如,氧化硅和其他常规层间电介质。如上所述,量子点122可以被限定在衬底层100与电介质层结构120之间的界面处。更具体地,量子点122可以被限定在硅衬底层110与电介质层结构120的底部氧化物层之间的界面处。对于硅衬底110,在衬底110与控制栅112、114、116之间可以存在5nm至20nm厚的氧化硅。

[0095]

图2d示出了沿着图2c所示的线截取的量子比特设备100的截面。势垒栅112和柱塞栅114可以布置在衬底层110上方的共同第一层级处。纳米磁体124可以布置在衬底层110上方的共同第二层级处,第二层级位于第一层级上方。贮存栅118也可以布置在第一层级处。限制栅116可以布置在衬底层110上方的共同第三层级处,该第三层级位于第一层级和第二层级下方。在替代配置中,限制栅116的共同第三层级可以位于第一层级上方,例如第二层级下方。

[0096]

纳米磁体124的第二层级可以使得每个量子点122a被限定在相关联的纳米磁体124的磁场的远场中。

[0097]

图2e示出了沿着图2f所示的线截取的量子比特设备100的截面。如所展示的是,柱塞栅114可以被布置成不延伸到纳米磁体124与相关联的第一量子点122a之间的空间中。

[0098]

量子比特设备100可以使用常规cmos工艺制造,例如,合适的栅电介质、栅电极材料和衬底材料(例如,si、si-28、sige)的金属氧化物半导体堆叠的图案化。纳米磁体124可以在合适的位置由合适的磁性材料制成,并且嵌入在电介质材料中。

[0099]

量子比特设备100可以进一步包括连接到纳米磁体124的非磁性金属层126,例如,呈线的形状。金属层126可以布置在纳米磁体124的顶部,例如,与纳米磁体124的上表面直接接触。金属层126可以减少纳米磁体124之间的潜在变化。金属层126可以连接到量子比特设备100的电接地。用于金属层126的合适的非磁性材料包含tin、al和au。

[0100]

在上文中,已经主要参考有限数量的示例描述了本发明构思。然而,如本领域技术人员容易理解的,在由所附权利要求限定的本发明构思的范围内,除以上披露的示例之外的其他示例同样是可能的。

[0101]

例如,虽然图中所描绘的量子比特设备100包括纵向限制栅116,但是也可以通过使用势垒栅112和柱塞栅114限制量子点来提供量子点的横向限制,这些势垒栅和这些柱塞栅沿着横向尺寸为几纳米的水平纳米线(例如,在半导体衬底层中图案化)交替布置。换句

话说,该行量子点112可以被势垒栅112和柱塞栅114沿着纳米线静电限制,并且被纳米线沿着横向方向物理限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。