1.本发明涉及电池充电控制电路,尤其是电池保护ic的0v充电控制电路。

背景技术:

2.如图1所示,现有电池保护ic与锂电池的连接方式,透过工作电压接脚vcc/接地接脚vss感测电池跨压、透过感测接脚cs感测充电路径电流,再透过控制接脚do/co控制充/放电路径上的保护开关,达到电池充放电保护的目的。

3.在电池处于通常状态下,系统导通放电控制接脚do和充电控制接脚co对应的两开关,当外接适配器耦接输入端eb 和eb-之间时,适配器给电池充电;当外接负载时,电池给负载供电;在电池处于欠压状态下,系统分别关断放电控制接脚do及开启充电控制接脚co相对应的开关,当外接适配器在eb 和eb-之间时,适配器通过放电控制接脚do对应的开关的寄生二极管给电池充电;当外接负载时,由于放电控制接脚do对应的开关关断,电池无法给负载供电;在电池跨压处于0v状态下,由于芯片内部控制电路欠压无法正常工作,此时,放电控制接脚do和充电控制接脚co相对应的开关均为关断状态,禁止电池充放电动作。

4.通常锂电池的跨压降到2.5v左右,系统会进入低电量模式,对负载而言就算没电。在低电量模式中,由于电池会自身放电、保护芯片也会消耗电池电量,故即使未对负载供电,电池在久置之后也可能会被完全放电(电池跨压=0v),有些种类的锂电池在0v时充电会导致漏液、过电流过热等,故不允许0v充电;有些电池没有这些问题,故允许0v充电。对于允许0v充电的电池,就需要增加0v充电控制电路,当外接适配器时,将充电控制端上拉至vcc,当适配器压差大于充电控制端的开启阈值时,充电控制端co开启,适配器通过放电控制端do的寄生二极管给电池充电。在先技术存在的技术问题:为了因应不同电池种类,而对应电池种类在pcb上选择性配置0v充电控制电路,造成pcb生产成本提高、pcb面积变大。

技术实现要素:

5.本发明所要接脚的技术问题是提供一种电池的保护集成电路,将外部被动组件构成的0v控制电路改为内置电路,ic内部电路的功耗比pcb组件的功耗还低;将外部0v充电控制电路改为内置电路,省略了pcb面积及被动组件成本,且由于电路简单,不致过于影响原本ic面积。

6.为解决上述技术问题,本发明的技术方案是:一种电池的保护集成电路,电池具有工作电压接脚耦接电池的正极及适配器的正输入端、控制接脚耦接充电开关、感测接脚耦接适配器的负输入端、接地接脚耦接电池的负极,适配器的正输入端、电池、充电开关及适配器的负输入端形成充电路径,保护集成电路包括比较电路以及0v充电控制电路。比较电路耦接工作电压接脚,以根据电池的跨压产生复位信号。

7.0v充电控制电路包括控制电路及第一熔丝。控制电路耦接比较电路、工作电压接脚及接地接脚,并具有输出端,用以根据复位信号及电池的跨压提供控制信号。第一熔丝耦接于控制电路的输出端与工作电压接脚之间。透过熔断第一熔丝来启用0v充电控制电路。

8.作为改进,还包括充放电保护电路,分别耦接比较电路及控制接脚,根据复位信号启用或禁用充放电保护功能。

9.作为改进,还包括反向电路,其输入端耦接第一熔丝及控制逻辑的输出端。

10.作为改进,0v充电控制电路还包括第二熔丝,耦接于控制逻辑的输出端与感测接脚之间,当第一熔丝保持导通时,第二熔丝熔断,藉以降低控制逻辑的功耗。

11.作为改进,0v充电控制电路还包括延迟电路,接收控制信号,用以提供控制信号迟滞窗口。

12.作为改进,0v充电控制电路还包括滤波电路,接收控制信号,用以对控制信号进行滤波。

13.本发明与现有技术相比所带来的有益效果是:

14.低功耗:将外部被动组件构成的0v控制电路改为内置电路,ic内部电路的功耗比pcb组件的功耗还低;

15.降低pcb成本:将外部0v充电控制电路改为内置电路,省略了pcb面积及被动组件成本,且由于电路简单,不致过于影响原本ic面积;

16.降低ic生产成本:透过熔断熔丝选择性的启用/禁用0v充电控制电路,仅需一套通用模板即可生产适用于两种需求的ic,节省ic生产成本。

附图说明

17.图1为现有技术电路图。

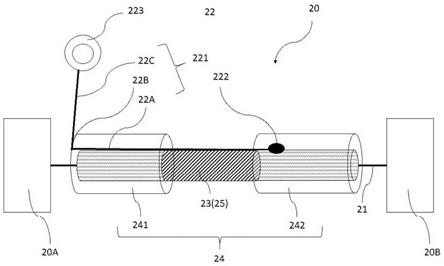

18.图2为本发明系统框架图。

19.图3为禁止0v充电的波形图。

20.图4为允许0v充电的波形图

21.图5为具体实施电路图。

具体实施方式

22.下面结合说明书附图对本发明作进一步说明。

23.如图2及图5所示,一种电池的保护集成电路,电池具有工作电压接脚vcc耦接电池的正极及适配器的正输入端eb 、控制接脚co耦接充电开关、感测接脚vm耦接适配器的负输入端eb-、接地接脚vss耦接电池的负极,适配器的正输入端eb 、电池、充电开关及适配器的负输入端eb-形成充电路径。保护集成电路包括:比较电路、0v充电控制电路、充放电保护电路和反向电路。

24.0v充电控制电路,包括控制电路、第一熔丝fuse1、第二熔丝fuse2、延迟电路和滤波电路。控制电路,耦接比较电路、工作电压接脚vcc及接地接脚vss,并具有输出端,用以根据复位信号及电池的跨压提供控制信号。第一熔丝fuse1,耦接于控制电路的输出端与工作电压接脚vcc之间;透过熔断第一熔丝fuse1来启用0v充电控制电路。第二熔丝fuse2,耦接于控制逻辑的输出端与感测接脚vm之间,当第一熔丝fuse1保持导通时,第二熔丝fuse2熔断,藉以降低控制逻辑的功耗。延迟电路,接收控制信号,用以提供控制信号迟滞窗口。滤波电路,接收控制信号,用以对控制信号进行滤波。

25.出厂时透过熔断熔丝fuse1来决定是否启用0v充电控制电路以支持0v保护,熔丝

fuse1导通:禁0v充电;熔丝fuse1断开:允许0v充电。

26.当电池及ic接上适配器时,透过vcc接脚及vm接脚提供工作电压(即eb 与eb-之间的压差)给ic内的电路,利用比较电路比较相对于接地接脚vss的工作电压vcc与vth(1.5v)产生复位信号por,当vcc》vth时,复位信号por=1,当vcc《vth时,复位信号por=0。透过复位信号por切换充放电保护电路和0v充电控制电路;复位信号por=0时,禁能充放电保护电路并提供por=0的信号给0v充电控制电路,复位信号por=1时,致能充放电保护电路并提供por=1的信号给0v充电控制电路。

27.如图3所示,在t1之前,尚未接上适配器且电池跨压vbat为0v、vcc=vss=0v,所有电路输出均为0;在t1时,接上适配器提供工作电压(例如5v)给ic,此时电池跨压vcc-vss=0v《vth使por=0启用0v充电控制电路,但由于fuce导通,故输出节点的输出信号n=1,经过反相器使节点n7=0,故控制信号co=0,使充电回路不导通,电池无法充电,尔后就固定在此状态。

28.如图4所示,在t1时,接上适配器提供工作电压(例如5v)给ic,此时电池跨压vcc-vss=0v《vth使por=0启用0v充电控制电路,由于fuce关断,故输出节点的输出信号n=0,经过反相器使节点n7=1,故控制信号co=1,使充电回路导通,电池开始充电。在t2时,电池跨压vbat爬升至vth(例如4.5v),使por=1,禁用0v充电控制电路使节点n7=0并启用充放电保护电路,以接手继续提供控制信号co=1直到电池充饱电(即vcc-vss=5v),电池充饱电之后若不触发ovp机制,充放电保护电路仍会保持控制信号co=1,这部分与本案无关,故不赘述。

29.如图5所示,控制电路包括反相器i1、晶体管pm1、晶体管pm2、熔丝fuse2和晶体管nd1;晶体管pm1栅极与vss接脚连接,晶体管pm1源极与vcc接脚连接,晶体管pm1漏极与晶体管pm2源极连接,晶体管pm2栅极与反相器i1输出端连接,晶体管pm2漏极与熔丝fuse1、熔丝fuse2及触发器i2连接,熔丝fuse2的另一端与晶体管nd1的漏极连接,晶体管nd1栅极和源极与vm接脚连接。

30.如图5所示,延迟电路包括晶体管pm3、晶体管pm4、晶体管pm5、晶体管pm6、晶体管nd2和反相器i4;晶体管pm3源极与vcc接脚连接,晶体管pm3栅极与反相器i3的输出端连接,晶体管pm3漏极与晶体管pm4源极连接,晶体管pm4栅极与vm连接,晶体管pm4漏极分别与晶体管pm5和晶体管pm6的源极连接,晶体管pm5和晶体管pm6的逻辑分别与反相器i4的输入端及晶体管nd2漏极连接,晶体管nd2栅极和源极与vm接脚连接。

31.如图5所示,反向滤波电路包括晶体管pm7、晶体管nd3、晶体管nd4、晶体管nm2、电容c1、触发器i5和晶体管pm8;晶体管pm7和晶体管nm2的栅极分别与晶体管pm6栅极及反相器i4的输出端连接,晶体管pm7源极与vcc接脚连接,晶体管pm7漏极与晶体管nd3漏极连接,晶体管nd3栅极和源极与电容c1、触发器i5的输入端及晶体管nd4漏极连接,晶体管nd4源极和栅极与晶体管nm2漏极连接,晶体管nm2源极与vm接脚及电容c1另一端连接,触发器输出端与晶体管pm8栅极连接,晶体管pm8源极与vcc接脚连接,晶体管pm8漏极与co接脚连接。

32.熔丝fuse1和熔丝fuse2为金属保险丝或聚熔断器;在熔丝fuse1导通(禁0v充电)的前提下,断开熔丝fuse2,可降低功耗;熔丝fuse1和熔丝fuse2可用激光熔断。

33.晶体管nd1、晶体管nd2、晶体管nd3和晶体管nd4均为耗尽管,其他晶体管均为普通低压管。

34.如图5所示,工作原理:在电池0v状态下的vcc=vss=0v,电池复位信号por=0,外接适配器时,eb =vcc,eb-=vm,即适配器压降落在vcc-vm之间,当系统默认为允许0v充电功能时,断开熔丝fuse1,具体工作原理如下,vcc-vss=0v,晶体管pm1关断,耗尽型晶体管nd1导通下拉节点n1,此时,节点n1=vm,输入到smit触发器i2整形,节点n2=vcc,再输入到反相器i3,得到节点n3=vm,晶体管pm3导通,由于晶体管pm4和晶体管pm5处于常通状态,故节点n4被上拉至vcc,经过反相器i4后,节点n5=vm,由晶体管pm4、晶体管pm5、晶体管pm6和反相器i4组成迟滞控制电路,提高电路抗干扰能力,节点n5信号输入到反向滤波电路中,得到节点n6=vcc,节点n6信号输入到smit触发器i5整形后,节点n7=vm,晶体管pm8导通,充电控制端co被上拉至vcc,当外接适配器电压大于充电控制开关管nmc的vth阈值时,充电控制开关管nmc被开启,适配器通过放电控制端的寄生二极管diode1形成回路给电池充电,

35.当电池被充电至上电复位阈值使por=1时,vcc-vss大于晶体管pm1的阈值,晶体管pm1开启,同时,反相器i1接收到por=1信号,开启pm2,节点n1被上拉至vcc,经过smit触发器i2和反相器i3,输出节点n3=vcc,关断晶体管pm3,该信号经过迟滞控制电路、反向滤波模块和smit触发器i5,输出节点n7=vcc关断晶体管pm8,至此,系统退出0v充电机制,并进入到电池欠压判别机制中。

36.若系统默认为禁止0v充电功能,熔丝fuse1保持连接,外接适配器时,eb =vcc,节点n1会持续被上拉至vcc,工作原理同上,使充电控制端co持续下拉为0。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。