1.本发明实施例涉及但不限于控制领域,尤其涉及一种隔离式数字信号输出电路及可编程逻辑控制器。

背景技术:

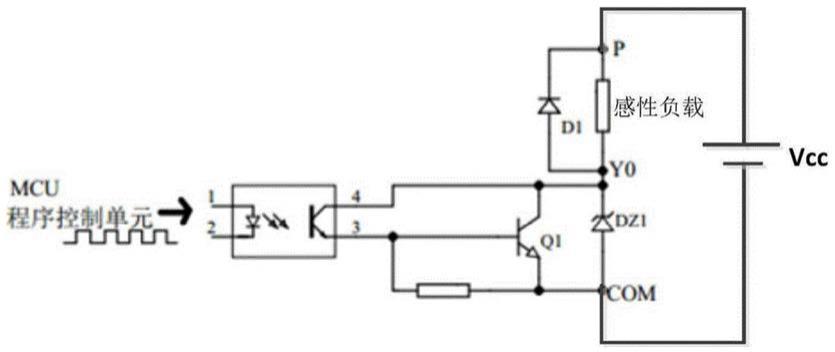

2.现有的数字信号输出电路图1所示,通过普通光耦将微处理器发出的控制信号隔离,通过光耦的通断控制驱动管q1。其中外部电源vcc用于给被隔离端供电;dz1二极管用于对q1过压钳位保护;q1的下拉电阻用于在默认情况下,关断q1;d1用于防止感性负载的瞬间关断,产生的过大放电电流,进行续流保护。该数字信号输出电路没有过流保护功能,通过的电流大小只取决于q1自身功率,其安全性差。

3.另外,该数字信号输出电路收普通光耦的速率限制,使得mcu控制单元发出的脉冲频率受限,不能支持高频率脉冲信号的应用场景,导致其应用场景受限,通用性较差。

技术实现要素:

4.本发明实施例提供的隔离式数字信号输出电路及可编程逻辑控制器,主要解决的技术问题是:解决现有数字信号输出电路安全性差,以及不支持高频率脉冲信号的应用场景,导致其应用场景受限的问题。

5.为了解决上述问题,本发明实施例提供了一种隔离式数字信号输出电路,包括高速信号隔离电路,位于所述高速信号隔离电路输入侧的信号输入电路、被隔离端信号调制电路,以及位于所述高速信号隔离电路输出侧的隔离端信号调制及控制电路、输出驱动电路和过流保护电路;

6.所述信号输入电路、被隔离端信号调制电路、高速信号隔离电路依次连接,所述信号输入电路向所述被隔离端信号调制电路输入脉冲信号,经所述被隔离端信号调制电路调制后输入所述高速信号隔离电路;

7.所述高速信号隔离电路、隔离端信号调制及控制电路以及输出驱动电路依次连接,所述高速信号隔离电路将所述脉冲信号输入至所述隔离端信号调制及控制电路进行调制后,经所述输出驱动电路输出;

8.所述过流保护电路分别与所述输出驱动电路和隔离端信号调制及控制电路连接,用于检测所述输出驱动电路的电流,并在检测到所述电流大于设定电流阈值时,向所述隔离端信号调制及控制电路输出过流保护自锁控制信号,所述隔离端信号调制及控制电路还用于在接收到所述过流保护自锁控制信号后进入过流自锁状态。

9.可选地,所述被隔离端信号调制电路包括依次连接于所述信号输入电路与所述高速信号隔离电路之间的被隔离端滤波电路和被隔离端信号还原及电压转换电路;

10.所述被隔离端滤波电路用于将所述信号输入电路输入的脉冲信号中的高频干扰信号滤除后,输入至所述被隔离端信号还原及电压转换电路;

11.所述被隔离端信号还原及电压转换电路用于将接收到的脉冲信号的波形进行还

原处理后,将还原处理后的脉冲信号的电平转换为所述高速信号隔离电路的驱动电平。

12.可选地,所述被隔离端信号还原及电压转换电路包括连接于所述被隔离端滤波电路和高速信号隔离电路之间的第一反相器。

13.可选地,所述被隔离端滤波电路为第一rc滤波电路。

14.可选地,所述隔离式数字信号输出电路还包括设置于所述高速信号隔离电路的输入端的钳位电路和/或第一限流电路。

15.可选地,所述隔离端信号调制及控制电路包括依次连接于所述高速信号隔离电路与所述输出驱动电路之间的隔离端滤波电路和驱动与自锁保护电路,所述驱动与自锁保护电路具有信号调制输入端和自锁控制输入端;

16.所述隔离端滤波电路用于将来自所述高速信号隔离电路的脉冲信号中的高频干扰信号滤除后,输入至所述驱动与自锁保护电路的信号调制输入端;

17.所述驱动与自锁保护电路的自锁控制输入端与所述过流保护电路的输出端连接,用于在未收到所述过流保护自锁控制信号时,将自所述信号调制输入端输入的脉冲信号进行还原处理后,输出至所述输出驱动电路,以及用于在通过所述自锁控制输入端接收到所述过流保护自锁控制信号时进入过流自锁状态。

18.可选地,所述隔离端滤波电路为第二rc滤波电路。

19.可选地,所述驱动与自锁保护电路为具有所述信号调制输入端和自锁控制输入端的第二反向器。

20.可选地,所述第二反向器包括与门逻辑开关,所述与门逻辑开关的两个输入端分别为所述信号调制输入端和自锁控制输入端;

21.或,所述第二反向器包括与非门逻辑开关,所述与非门逻辑开关的两个输入端分别为所述信号调制输入端和自锁控制输入端。

22.可选地,所述隔离式数字信号输出电路还包括:设置于所述高速信号隔离电路输出侧的电源端的第一退耦电路;

23.和/或,

24.设置于所述驱动与自锁保护电路的电源端的第二退耦电路。

25.可选地,所述输出驱动电路包括与所述驱动与自锁保护电路的输出端连接的驱动元件,以及与所述驱动元件连接的下拉电路。

26.可选地,所述驱动元件为mos管、三极管或集成驱动芯片。

27.可选地,所述隔离式数字信号输出电路还包括:连接于所述驱动与自锁保护电路的输出端与所述驱动元件之间的第二限流电路。

28.可选地,所述过流保护电路包括与所述下拉电路连接的电流采样电路,以及与所述电流采样电路连接的过流保护开关电路;

29.所述电流采样电路用于采集电流;

30.所述过流保护开关电路用于在所述电流采样电路采集的电流大于设定电流阈值时,向所述驱动与自锁保护电路的自锁控制输入端输出过流保护自锁控制信号。

31.可选地,所述高速信号隔离电路包括连接于所述被隔离端信号调制电路和隔离端信号调制及控制电路之间的光耦隔离电路、电磁隔离电路或电容隔离电路。

32.为了解决上述问题,本发明实施例还提供了一种可编程逻辑控制器,包括如上所

述的隔离式数字信号输出电路。

33.有益效果

34.本发明实施例提供的隔离式数字信号输出电路及可编程逻辑控制器中,该隔离式数字信号输出电路包括高速信号隔离电路,位于高速信号隔离电路输入侧的信号输入电路、被隔离端信号调制电路,以及位于高速信号隔离电路输出侧的隔离端信号调制及控制电路、输出驱动电路和过流保护电路,其中:

35.信号输入电路、被隔离端信号调制电路、高速信号隔离电路依次连接,信号输入电路向被隔离端信号调制电路输入脉冲信号,经被隔离端信号调制电路调制后输入高速信号隔离电路;高速信号隔离电路、隔离端信号调制及控制电路以及输出驱动电路依次连接,高速信号隔离电路将脉冲信号输入至隔离端信号调制及控制电路进行调制后,经输出驱动电路输出;过流保护电路分别与输出驱动电路和隔离端信号调制及控制电路连接,用于检测输出驱动电路的电流,并在检测到电流大于设定电流阈值时,向隔离端信号调制及控制电路输出过流保护自锁控制信号,隔离端信号调制及控制电路还用于在接收到过流保护自锁控制信号后进入过流自锁状态;

36.由于本发明实施例提供的隔离式数字信号输出电路的过流保护电路分别在检测到输出驱动电路的电流大于设定电流阈值时,可向隔离端信号调制及控制电路输出过流保护自锁控制信号使其进入过流自锁状态,实现过流的检测和保护,可在很大程度上提升安全性;另外本发明实施例提供的隔离式数字信号输出电路采用高速信号隔离电路,可支持高频率脉冲信号,使得高速信号隔离电路能适用于各种应用场景,通用性更好。

37.本发明其他特征和相应的有益效果在说明书的后面部分进行阐述说明,且应当理解,至少部分有益效果从本发明说明书中的记载变的显而易见。

附图说明

38.图1为现有数字信号输出电路结构示意图;

39.图2为本发明实施例提供的隔离式数字信号输出电路逻辑示意图一;

40.图3为本发明实施例提供的隔离式数字信号输出电路逻辑示意图二;

41.图4为本发明实施例提供的隔离式数字信号输出电路结构示意图一;

42.图5为本发明实施例提供的隔离式数字信号输出电路结构示意图二;

43.图6为本发明实施例提供的隔离式数字信号输出电路结构示意图三;

44.图7为本发明实施例提供的隔离式数字信号输出电路结构示意图四。

具体实施方式

45.为了使本发明的目的、技术方案及优点更加清楚明白,下面通过具体实施方式结合附图对本发明实施例作进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

46.本发明实施例所提供的隔离式数字信号输出电路具有安全性更高,可支持高频率脉冲信号的传输,通用性更好的优点。一种示例结构请参见图1所示,该隔离式数字信号输出电路包括:高速信号隔离电路3,位于高速信号隔离电路3输入侧的信号输入电路1、被隔离端信号调制电路2,以及位于高速信号隔离电路3输出侧的隔离端信号调制及控制电路4、

输出驱动电路5和过流保护电路6,其中:

47.信号输入电路1、被隔离端信号调制电路2、高速信号隔离电路3依次连接,信号输入电路1向被隔离端信号调制电路2输入脉冲信号,经被隔离端信号调制电路2调制后输入高速信号隔离电路3;其中,本实施例中信号输入电路1可与cpu、mcu或fpga等控制单元连接,用于接收脉冲信号,并将接收到的脉冲信号传输给被隔离端信号调制电路2;本实施例中被隔离端信号调制电路2对接收到的脉冲信号的处理包括但不限于信号滤波、信号还原以及电压转换等处理,具体可根据应用需求灵活设定。

48.例如,一种示例请参见图3所示,被隔离端信号调制电路2包括依次连接于信号输入电路1与高速信号隔离电路3之间的被隔离端滤波电路21和被隔离端信号还原及电压转换电路22;被隔离端滤波电路21用于将信号输入电路1输入的脉冲信号中的高频干扰信号滤除后,输入至被隔离端信号还原及电压转换电路22;被隔离端信号还原及电压转换电路22用于将接收到的脉冲信号的波形进行还原处理后,将还原处理后的脉冲信号的电平转换为高速信号隔离电路3的驱动电平。且应当理解的是,本实施例中被隔离端滤波电路21的具体电路结构以及被隔离端信号还原及电压转换电路22的具体电路结构都可根据灵活设定,只要能实现上述功能即可。例如,被隔离端滤波电路21可以通过但不限于第一rc滤波电路实现。被隔离端信号还原及电压转换电路22可包括但不限于连接于被隔离端滤波电路21和高速信号隔离电路3之间的第一反相器。

49.请参见图2所示,本实施例中的高速信号隔离电路3、隔离端信号调制及控制电路4以及输出驱动电路5依次连接,高速信号隔离电路3将脉冲信号输入至隔离端信号调制及控制电路4进行调制后,经输出驱动电路5输出;本实施例中隔离端信号调制及控制电路4对接收到的脉冲信号的处理包括但不限于信号滤波和信号还原处理。例如,一种示例请参见图3所示,隔离端信号调制及控制电路4包括依次连接于高速信号隔离电路3与输出驱动电路5之间的隔离端滤波电路41和驱动与自锁保护电路42,驱动与自锁保护电路42具有信号调制输入端和自锁控制输入端,其中:

50.隔离端滤波电路41用于将来自高速信号隔离电路3的脉冲信号中的高频干扰信号滤除后,输入至驱动与自锁保护电路42的信号调制输入端;驱动与自锁保护电路42的自锁控制输入端与过流保护电路6的输出端连接,用于在未收到过流保护自锁控制信号时,将自信号调制输入端输入的脉冲信号进行还原处理后,输出至输出驱动电路5,以及用于在通过自锁控制输入端接收到过流保护自锁控制信号时进入过流自锁状态。

51.应当理解的是,本实施例中隔离端滤波电路41和驱动与自锁保护电路42的具体电路结构也可根据具体应用场景灵活设置,只要能实现上述功能即可。例如,一种应用示例中,隔离端滤波电路41可为但不限于第二rc滤波电路;驱动与自锁保护电路42可为但不限于具有信号调制输入端和自锁控制输入端的第二反向器。在一些示例中,第二反向器包括与门逻辑开关,与门逻辑开关的两个输入端分别为信号调制输入端和自锁控制输入端;或,第二反向器包括与非门逻辑开关,与非门逻辑开关的两个输入端分别为信号调制输入端和自锁控制输入端。

52.请参见图2所示,本实施例中,过流保护电路6分别与输出驱动电路5和隔离端信号调制及控制电路4连接,用于检测输出驱动电路5的电流,并在检测到电流大于设定电流阈值时,向隔离端信号调制及控制电路4输出过流保护自锁控制信号,隔离端信号调制及控制

电路4还用于在接收到过流保护自锁控制信号后进入过流自锁状态。

53.在本实施例的一种示例中,输出驱动电路5可包括但不限于与驱动与自锁保护电路42的输出端连接的驱动元件,以及与驱动元件连接的下拉电路。本实施例中的驱动元件可以灵活选择,例如可以选择但不限于mos管、三极管、集成驱动芯片中的至少一种,也可选择其他能实现上述驱动功能的元件或电路。

54.在本实施例的一种示例中,请参见图3所示,过流保护电路6包括与上述下拉电路连接的电流采样电路61,以及与电流采样电路61连接的过流保护开关电路62;

55.电流采样61电路用于采集输出驱动电路5的电流,应当理解的是,电流采样电路61可以采用各种能实现电流采样的电路结构实现。

56.过流保护开关电路62用于在电流采样电路61采集的电流大于设定电流阈值时,向驱动与自锁保护电路42的自锁控制输入端输出过流保护自锁控制信号。

57.可选地,在本实施例的一些示例中,为了进一步提升隔离式数字信号输出电路的可靠性和安全性,参见图3所示,本示例中的隔离式数字信号输出电路还包括但不限于设置于高速信号隔离电路3的输入端的钳位电路7和/或第一限流电路8。

58.可选地,在本实施例的一些示例中,为了进一步提升隔离式数字信号输出电路的可靠性和安全性,参见图3所示,隔离式数字信号输出电路还可包括但不限于:设置于高速信号隔离电路3输出侧的电源端的第一退耦电路;和/或,设置于驱动与自锁保护电路42的电源端的第二退耦电路。其中第一退耦电路和第二退耦电路的具体电路结构也可灵活选择,只要能实现退耦目的即可。

59.可选地,在本实施例的一些示例中,为了进一步提升隔离式数字信号输出电路的可靠性和安全性,参见图3所示,隔离式数字信号输出电路还可包括但不限于:连接于所述驱动与自锁保护电路42的输出端与所述驱动元件之间的第二限流电路9。

60.本实施例中,高速信号隔离电路3可以采用各种支持10mhz以上高频率脉冲信号的电路,例如,一种示例中,该高速信号隔离电路3可以包括但不限于连接于被隔离端信号调制电路3和隔离端信号调制及控制电路4之间的光耦隔离电路、电磁隔离电路或电容隔离电路的至少一种。例如,一些应用示例中,高速信号隔离电路3可以采用光耦隔离电路、电磁隔离电路或电容隔离电路中的任意一种,也可采用光耦隔离电路、电磁隔离电路或电容隔离电路中的两种或两种以上的组合;且应当理解的是,也可采用其他支持高速信号隔离传输的电路或器件,在此不再赘述。

61.为了便于理解,本实施例下面以几种隔离式数字信号输出电路的几种示例的电路实现结构为示例进行说明。

62.一种示例请参见图4所示的隔离式数字信号输出电路结构,其包括依次连接的信号输入端1,被隔离滤波电路21、被隔离端信号还原及电压转换电路22,钳位电路7,高速信号隔离电路3,隔离端滤波电路41,驱动与自锁保护电路42,第二限流电路9以及输出电路5,还包括与输出电路5连接的过流保护电路6,其中:

63.被隔离滤波电路21包括由电阻r1和电容c1组成的第一rc滤波电路,该第一rc滤波电路构成高速信号隔离电路3被隔离端脉冲信号低通滤波,滤除高频干扰;

64.被隔离端信号还原及电压转换电路22包括第一反向器u1a,反向器u1a将第一rc滤波电路滤波后的脉冲信号的波形还原,并将脉冲高电平变换为5v(根据需求也可转换为其

他电压值),从而驱动高速信号隔离电路32,高速信号隔离电路3输入正常开关;

65.钳位电路7由并联于高速信号隔离电路3输入端的电阻r3和电容c2,用于将脉冲信号的某一部分固定在指定电压值上,并保持原波形形状不变;

66.高速信号隔离电路3采用高速光耦u2,而图1所示的数字信号输出电路采用的是普通光耦。其具体采用的是普通的4个引脚的普通光耦,在电气属性中不支持高速信号传输,例如东芝光耦4个引脚普通光耦tlp185,在最理想状态下,一个pwm周期脉冲需要响应时间:

67.tr tf ton toff ton ts toff=5us 9us 9us 9us 2us 30us 70u s=134us,则f=1/t=7461hz≈7khz。

68.本实施例中采用的是高速光耦,其电气特性与实际制造工艺支持高速信号传输。高速光耦都是五个引脚,需要外部给电源,例如可以采用但不限于东芝高速光耦tlp2361,在最理想状态下,一个pwm周期脉冲需要响应时间:

69.tphl tplh tf tr=49ns 39ns 3ns 3ns=93ns,则f=1/t=10752688hz≈10.5mhz。

70.显然,普通光耦不能支持高速基本的脉冲序列群输出,本实施例采用的高速光耦则可支持高速信号传输。

71.可选地,参见图4所示,还包括设置于高速光耦被隔离端的输入端的第一限流电路r2。

72.可选地,参见图4所示,还包括设置于高速光耦隔离端的输入端的第一退耦电路c4。

73.隔离端滤波电路41包括连接于高速光耦输出端的电阻r4和电容c3组成的第二rc滤波电路,该第二rc滤波电路可对高速光耦输出的脉冲信号低通滤波,滤除高频干扰;

74.驱动与自锁保护电路42包括连接于第二rc滤波电路与第二限流电路9之间的第二反相器u3,第二反相器u3用于将第二rc滤波电路滤波后的波形还原以及实现过流保护的自锁和驱动输出电路5;可选地,参见图4所示,包括设置于第二反相器u3电源端的第二退耦电路c5。

75.本实施例中的第二限流电路包括连接于驱动与自锁保护电路42与驱动输出电路5之间的电阻r5,实现限流;

76.驱动输出电路5包括作为驱动元件的三极管q1,以及与三极管q1连接的由电阻r6组成的下拉电路,默认让q1截止。

77.过流保护电路6包括采样电路61和过流保护开关电路62,采用电路由于下拉电路r6连接的电阻r8构成,过流保护开关电路62包括与采样电路连接的电阻r7、三极管q2以及三极管q3、电阻r10和电阻r11。正常情况下,过流保护开关电路62的输出oc1上拉输出高电平,第二反相器u3与门输出取决于脉冲输出。当电流过流时,r8两端电压u8大于q2的ube,三极管q2、q3导通,则oc1为低电平,则第二反相器u3的与门一直输出低电平,作为驱动元件的三极管q1保护截止不输出,从而进入过流自锁状态。

78.另一种示例参见图5所示,该图所示的隔离式数字信号输出电路结构包括依次连接的信号输入端1,被隔离滤波电路21、被隔离端信号还原及电压转换电路22,钳位电路7,高速信号隔离电路3,隔离端滤波电路41,驱动与自锁保护电路42,第二限流电路9以及输出电路5,还包括与输出电路5连接的过流保护电路6,其中:图5所示的隔离式数字信号输出电

路与图4所示的隔离式数字信号输出电路结构,主要区别在于,高速信号隔离电路3由高速光耦电路替换为电磁隔离电路u2。

79.又一种示例参见图6所示,该图所示的隔离式数字信号输出电路结构也包括依次连接的信号输入端1,被隔离滤波电路21、被隔离端信号还原及电压转换电路22,钳位电路7,高速信号隔离电路3,隔离端滤波电路41,驱动与自锁保护电路42,第二限流电路9以及输出电路5,还包括与输出电路5连接的过流保护电路6,其中:图6所示的隔离式数字信号输出电路与图4和图5所示的隔离式数字信号输出电路结构,主要区别在于,高速信号隔离电路3由高速光耦电路、电磁隔离电路u2替换为电容隔离电路u2。

80.又一种示例参见图7所示,该图所示的隔离式数字信号输出电路结构也包括依次连接的信号输入端1,被隔离滤波电路21、被隔离端信号还原及电压转换电路22,钳位电路7,高速信号隔离电路3,隔离端滤波电路41,驱动与自锁保护电路42,第二限流电路9以及输出电路5,还包括与输出电路5连接的过流保护电路6,其中:图7所示的隔离式数字信号输出电路与图4所示的隔离式数字信号输出电路结构,主要区别在于,第二反相器u2的与门替换为与非门结合反相器u4a实现图4中的第二反相器的功能。

81.可见,本实施例提供的隔离式数字信号输出电路的过流保护电路分别在检测到输出驱动电路的电流大于设定电流阈值时,可向隔离端信号调制及控制电路输出过流保护自锁控制信号使其进入过流自锁状态,实现过流的检测和保护,可在很大程度上提升安全性;另外本发明实施例提供的隔离式数字信号输出电路采用高速信号隔离电路,可支持高频率脉冲信号,使得高速信号隔离电路能适用于各种应用场景,通用性更好。

82.本实施例提供了一种可编程逻辑控制器,其包括如上所示的隔离式数字信号输出电路。该可编程逻辑控制器可以为步进可编程逻辑控制器,伺服可编程逻辑控制器或混合型可编程逻辑控制器。

83.需要说明的是,在本文中,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者装置不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者装置所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括该要素的过程、方法、物品或者装置中还存在另外的相同要素。

84.上述本发明实施例序号仅仅为了描述,不代表实施例的优劣。

85.通过以上的实施方式的描述,本领域的技术人员可以清楚地了解到上述实施例方法可借助软件加必需的通用硬件平台的方式来实现,当然也可以通过硬件,但很多情况下前者是更佳的实施方式。基于这样的理解,本发明的技术方案本质上或者说对现有技术做出贡献的部分可以以软件产品的形式体现出来,该计算机软件产品存储在一个存储介质(如rom/ram、磁碟、光盘)中,包括若干指令用以使得一台终端(可以是手机,计算机,服务器,空调器,或者网络设备等)执行本发明各个实施例所述的方法。

86.上面结合附图对本发明的实施例进行了描述,但是本发明并不局限于上述的具体实施方式,上述的具体实施方式仅仅是示意性的,而不是限制性的,本领域的普通技术人员在本发明的启示下,在不脱离本发明宗旨和权利要求所保护的范围情况下,还可做出很多形式,这些均属于本发明的保护之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。