1.本发明属于存储技术领域,特别涉及一种数据存储设备及其控制方法与电子设备。

背景技术:

2.随着存储行业技术快速发展,电子设备的种类逐渐增加。嵌入式多媒体存储卡(embedded multi media card,emmc)是设置在电子设备中的一种嵌入式数据存储设备,因容量更高、体积更小被广泛应用在智能手机和平板等电子产品上。但是这些电子产品中的emmc固件在进行数据的错误处理的时,对错误数据和正确数据的处理分析不够详细,且会在闪存转换层(flash translationlayer,ftl)及后端处理错误数据,这会降低闪存转换层的工作效率,进而降低电子设备的工作效率。

技术实现要素:

3.本发明的目的在于提供一种数据存储设备的数据处理方法及系统与电子设备,通过本发明提供的数据存储设备的数据处理方法及系统与电子设备,可提高电子设备对错误数据的处理效率,以及电子设备的工作效率。

4.为解决上述技术问题,本发明是通过以下技术方案实现的:

5.本发明提供一种数据存储设备的数据处理方法,其至少包括以下步骤:

6.接收主机传送的数据;

7.在前端层将数据进行校验,并将通过校验的数据存储在缓存单元中;

8.当缓存单元的缓存容量达到预设阈值时,执行缓存单元中的指令数据;以及

9.在执行写入指令数据时,接收到停止指令数据,检测所述缓存单元内是否有数据;以及

10.当所述缓存单元内有数据时,执行所述缓存单元内的数据后,再执行所述停止指令数据。

11.在本发明一实施例中,所述校验包括循环冗余校验、写保护校验以及地址超范围校验。

12.在本发明一实施例中,所述预设阈值为缓存单元总容量的85%-90%。

13.在本发明一实施例中,所述缓存单元总容量以下公式获取:

14.cs=fes c

p

×

sc c

p

×sx

c

p

×ss

;

15.c

p

=cen×

psn/2

×

pln;

16.其中,cs为缓存容量,fes为暂存单元的大小,cen为开启的通道数量,pln为每个通道中面的数量,psn为每个闪存页中有多少个扇区,sc为一次性稳定写入的闪存页数量,ss为slc存储模式的存储器单元的系数,s

x

为xlc存储模式的存储器单元的系数。

17.在本发明一实施例中,当数据未通过校验时,所述数据存储设备的控制方法包括:

18.所述前端层停止指令数据的传送,处于等待状态;以及

19.将所述缓存单元中的数据删除,并将错误信息反馈给主机。

20.在本发明一实施例中,当数据存储设备在执行读取命令时,接收到停止指令数据,所述数据存储设备立即响应所述停止指令数据。

21.在本发明一实施例中,在执行写入指令数据时,接收到停止指令数据,所述数据存储设备的控制方法包括以下步骤:

22.当检测所述缓存单元内是否有数据;

23.当所述缓存单元内有数据时,暂缓停止指令数据,并触发直接存储器访问控制器;以及

24.所述直接存储器访问控制器执行所述缓存单元中的数据。

25.在本发明一实施例中,在执行写入指令数据时,接收到停止指令数据,所述数据存储设备的控制方法包括以下步骤:

26.当检测所述缓存单元内是否有数据;以及

27.当所述缓存单元中没有数据时,立即响应所述停止指令数据。

28.本发明还提供一种数据存储设备,包括:

29.接收单元,设置在前端层中,用于接收主机传送的数据;

30.校验单元,设置在前端层中,用于将数据进行校验;

31.缓存单元,设置在前端层中,用于存储通过校验的数据;

32.控制单元,设置在前端层中,用于执行缓存单元中的指令数据,且在执行写入指令数据时,接收到停止指令数据,检测所述缓存单元内是否有数据;以及

33.直接存储器访问控制器,设置在前端层中,用于在所述缓存单元内有数据时,执行所述缓存单元内的数据后。

34.本发明还提供一种电子设备,包括:

35.主机;

36.数据存储设备,通过接口电性连接于所述主机,且所述数据存储设备包括:

37.接收单元,设置在前端层中,用于接收主机传送的数据;

38.校验单元,设置在前端层中,用于将数据进行校验;

39.缓存单元,设置在前端层中,用于存储通过校验的数据;

40.控制单元,设置在前端层中,用于执行缓存单元中的指令数据,且在执行写入指令数据时,接收到停止指令数据,检测所述缓存单元内是否有数据;以及

41.直接存储器访问控制器,设置在前端层中,用于在所述缓存单元内有数据时,执行所述缓存单元内的数据后。

42.如上所述本发明提供的一种数据存储设备及其控制方法与电子设备,在前端层进行验证,并在前端层中即将错误信息反馈至主机,避免将错误信息传递至中间层和后端层中,提高数据存储设备的工作效率。在接收到主机传动的数据时,将数据存储在缓存单元中,到达预设阈值后,再执行存储单元中的指令数据,可提高数据存储设备的执行效率。且在本技术中,在接收到主机发送停止指令数据时,依据缓存单元中的数据信息类型,灵活处理,在保证数据不会出现丢失的同时,最大限度提高数据存储设备的工作效率。通过本发明提供的一种数据存储设备及其控制方法与电子设备,可提高数据存储设备和电子设备的工作效率。

43.当然,实施本发明的任一产品并不一定需要同时达到以上所述的所有优点。

附图说明

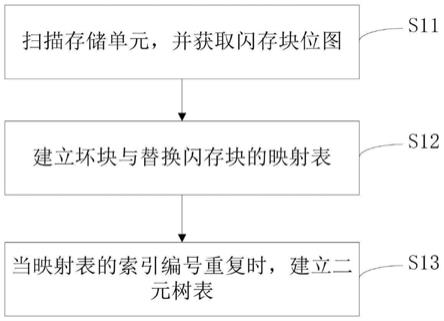

44.为了更清楚地说明本发明实施例的技术方案,下面将对实施例描述所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

45.图1为一种电子设备结构示意图。

46.图2为一种主机与数据存储设备数据传送结构示意图。

47.图3为一种存储单元结构示意图。

48.图4为一种数据存储设备的控制流程图。

49.图5为一种数据存储设备的控制流程图。

50.图6为一种读取指令数据的控制流程图。

51.图7为一种写入指令数据的控制流程图。

52.图8为一种有错误时,数数据存储设备的控制流程图。

53.图9为一种数据存储设备的结构框图。

54.图10为一种计算机可读存储介质的框图。

具体实施方式

55.以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。

56.需要说明的是,本实施例中所提供的图示仅以示意方式说明本发明的基本构想,遂图式中仅显示与本发明中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的型态、数量及比例可为一种随意的改变,且其组件布局型态也可能更为复杂。

57.请参阅图1所示,这里所描述的数据存储设备20包括用于控制包括闪存芯片的大容量存储模块的新颖结构。在图1中以高度概述的形式示出了整个数据存储设备20。与这里的其它框图一样,图1所示的元件本质上是概念性的,它们示出了这些功能块之间的互相关系的性质,而不意在表示实际的物理电路级实施。

58.请参阅图1所示,本技术提出一种电子设备,电子设备包括主机10和数据存储设备20。其中,主机10和数据存储设备20可以被实现为单独的芯片,模块,或者设备,或者可以被包括在单一设备中。例如,数据存储设备20可以为集成的单一存储设备,然后被连接至主机10。然而,本公开不限于该示例。也就是说,在另一示例中,主机10和数据存储设备20可以被集成到单一设备中。

59.请参阅图1所示,在本发明一实施例中,主机10例如由个人计算机、cpu 核或者与网络连接的服务器等构成。用户在主机10的操作系统的应用层面对电子设备20发出请求,文件系统101将读写请求经底层驱动102转化为相应的符合协议的读写和其他指令数据,数

据存储设备20通过接口收到指令数据后,经过内部计算和处理逻辑,执行用的指令数据,并向主机10反馈相应的答复。

60.请参阅图1所示,在本发明一实施例中,数据存储设备20是一种以半导体闪存作为介质的存储设备,例如为嵌入式多媒体存储卡(embedded multi mediacard,emmc)。且在本实施例中,数据存储设备20包括前端层201、中间层204 和后端层205。其中,前端层201包括控制单元202和缓存单元203,且其中的缓存单元203例如为随机存取数据存储设备(random access memory,ram),中间层204例如为闪存转换层(flash translation layer,ftl),后端层205包括多个闪存块206。当数据存储设备20接收到主机10发送的指令数据后,经过数据的验证,将相关的数据先存在缓存单元203中,中间层204会为每个逻辑数据块分配一个闪存地址,当数据凑到一定数量后,中间层204便会发送写闪存请求给后端层205,后端层205根据指令数据请求,把缓存单元203中的数据写到对应的闪存块206中,或读取对应闪存块206中的数据。

61.请参阅图1所示,在本发明一实施例中,中间层204中包括地址转换单元210,可以完成逻辑数据到闪存块206物理地址的转换或者映射。后端层205包括具有字符串单元(cell)结构的多个存储器单元。多个存储器单元被称为存储器单元阵列。数据存储设备20的存储器单元阵列包括多个存储器块。存储器块中的每一个包括多个页,每一个页包括一起共享单一字线的多个存储器单元。在本实施例中,每个存储器单元例如为一个浮栅晶体管。在数据实际存在的、存储器的地址被称为物理地址,控制单元202使用逻辑地址,其与物理地址对应。可利用闪存转换层(flash translation layer,ftl)来管理物理地址和逻辑地址。且可以以映射表的形式存储物理地址和逻辑地址。

62.请参阅图1和图3所示,在本发明一实施例中,在后端层205中,数据存储设备20的底层设置有多个通道(channel,ch),且每个通道内部有多个并行的逻辑单元(logical unit,lu)。每个逻辑单元中包括多个面(plane)、页面寄存器(page register)和缓存寄存器(cache register),其中,页面寄存器和缓存寄存器中存放将要写入到物理存储单元中去的或者刚从存储单元中读取出来的数据。在每个面中,设置有多个闪存块(block)206,每个闪存块206内设置有多个闪存页(page),每个闪存页中还包括多个存储器单元。其中,闪存块206内的存储器单元数据块可以按照实际需求配置为不同的存储模式,存储器单元例如包括slc(single-level cell,1bit/cell)存储模式和xlc存储模式。其中,slc存储模式指的是闪存块206中的每个字符串单元(cell)只存放一个比特数据,且scl存储模式的存储器单元具有较高的擦除次数,例如为 50000~100000次。xlc存储模式指的是闪存块206中的每个字符串单元(cell) 存放多个比特数据,且xlc存储模式包括mlc(multi-level cell,2bit/cell)存储模式、tlc(trinary-level cell,3bit/cell)存储模式和qlc(quad-level cell,4bit/cell) 存储模式,且xlc存储模式的存储器单元具有较低的擦除次数,例如为500~10000次。相对于xlc存储模式的存储器单元,scl存储模式的存储器单元的性能更加稳定。在存储数据时,将数据写入xlc存储模式的存储器单元中,将比较重要的数据存储在slc存储模式的存储器单元中,例如可以将读取或闪存的计数页存储在slc存储模式的存储器单元中。

63.请参阅图4所示,在本发明一实施例中,对于本发明提供的一种数据存储设备20,提供一种数据存储设备的控制方法,包括,

64.s101、接收主机传送的指令数据。

65.s102、对指令数据进行校验,当指令数据通过校验时,执行步骤s103,当指令数据未通过校验时,执行步骤s106。

66.s103、将指令数据存储在缓存单元中。

67.s104、判断缓存容量是否达到预设阈值,当缓存容量未达到预设阈值时,继续执行步骤s101,当缓存容量达到预设阈值时,执行步骤s105。

68.s105、执行指令数据。

69.s106、停止指令数据的传送,等待主机再次发送指令数据。

70.请参阅图4所示,在本发明一实施例中,在步骤s102中,在对数据进行校验时,校验未通过的错误例如包括但不仅限于循环冗余校验(cyclic redundancycheck,crc)错误、写保护(write protect,wp)和地址超范围(out ofrange, oor)错误等。其中,循环冗余校验例如通过硬件(hardware,hw)处理,以增加数据验证的效率,进而增加固件(firmware,fw)的处理效率。

71.请参阅图5所示,在本发明一实施例中,当检验未通过时,数据存储设备的控制方法具体包括,

72.s1061、前端层停止指令数据的传送,处于等待状态。

73.s1062、将缓存单元中的数据删除,并将错误信息反馈给主机。

74.s1063、主机接收到错误信息后,发送停止指令数据给数据存储设备。

75.s1064、当数据存储设备完成数据删除后,主机重新发送数据给数据存储设备。

76.在本实施例中,例如可以使用状态寄存器,记录当前错误信息的类型,以及获取当前指令数据执行结果的各种状态信息。在进行错误信息反馈时,以反馈错误的类型,可避免重新发送数据给数据存储设备时,不会有重复的数据信息也不会有缺失的数据信息。

77.请参阅图1和图4所示,在本发明一实施例中,在步骤s103中,缓存单元 203例如为随机存取数据存储设备(random access memory,ram)。在执行主机10的指令数据时,当主机10连续读取或者写入较小的数据时,将指令数据直接传递至中间层204并逐条执行,浪费时间与精力。在本实施例中,将数据先存储在缓存单元203中,当缓存单元203中的缓存容量达到预设阈值时再执行,可提高指令数据的执行效率。在本实施例中,当缓存的功能未开启时,且数据传送至数据存储设备时,前端层201中集成有一个暂存单元209,将当前执行的指令数据保存在暂存单元209中,执行完成后,暂存单元209中的数据马上删除,继续执行下一条指令数据。其中,暂存单元209可依据程序设计,暂存单元209的大小例如为2kb、4kb或8kb,本实施例以2kb为例。

78.请参阅图1和图4所示,在本发明一实施例中,在步骤s104中,缓存单元的总容量的通过以下公式获取:

79.cs=fes c

p

×

sc c

p

×sx

c

p

×ss

。

80.c

p

=cen×

psn/2

×

pln。

81.其中,cs为缓存单元的总容量,fes为暂存单元的大小,在本实施例中例如为2kb。cen为开启的通道数量,在本实施例中例如为1。pln为每个通道中面的数量,在本实施例中例如为2。psn为每个闪存页中有多少个扇区,前端层在存储数据时,依照扇区为单位传输数据,在本实施例中闪存页的大小例如为 16kb,扇区的大小例如为512b,则每个闪存页中有

32个扇区。则 c

p

=1

×

32/2

×

2=32。sc为一次性稳定写入的闪存页数量,例如可以为4、6、8、 12等,本实施例以4为例。ss为slc存储模式的存储器单元的系数,即一个 slc存储模式的闪存块中闪存页的数量,本实施例中ss例如为1。s

x

为xlc存储模式的存储器单元的系数,即一个xlc存储模式的闪存块中闪存页的数量,本实施例中s

x

例如为2。则缓存单元的总容量cs=2kb (32

×

4 32

×

2 32

×

1)

ꢀ×

512b=114kb。

82.请参阅图1和图4所示,在本实施例中,步骤s104中的预设阈值为缓存单元203总容量的例如85%-90%,具体例如为90%。当缓存单元203中的缓存容量大于预设阈值时,则执行指令数据,即将数据通过中间层204传输至后端层 205。

83.请参阅图1所示,在本发明一实施例中,在步骤s105当执行指令数据时,控制单元202通过中间层204,获取指令数据中逻辑地址对应的物理地址,并对具有该物理地址中对应的闪存块206执行相关指令数据。且本发明中的指令数据可以是主机10发送给数据存储装置的任意指令数据,例如可以为读指令数据、写指令数据、编辑指令数据或停止指令数据等。

84.请参阅图1所示,在本发明一实施例中,在指令数据传送的过程中,当指令数据接收到主机10发送的停止指令数据时,前端层201停止指令数据的接收。

85.请参阅图1和图6所示,在本发明一具体实施例中,当主机10发送的指令数据为读取指令数据时,数据存储设备的控制方法包括,

86.s111、接收主机传送的读取指令数据。

87.s112、对读取指令数据继续进行校验。当读取指令数据通过校验时,执行步骤s113,当读取数据未通过校验时,执行步骤s116。

88.s113、将读取指令数据存储在缓存单元中。

89.s114、判断缓存容量是否达到预设阈值,当缓存容量未达到预设阈值时,继续执行步骤s111,当缓存容量达到预设阈值时,执行步骤s115。

90.s115、执行读取指令数据。

91.s116、停止读取指令数据的传送,等到主机再次发送读取指令数据。

92.请参阅图2和图6所示,在本发明一实施例中,在执行读取指令数据的过程中,当数据存储设备20接收到主机10发送的停止指令数据时,数据存储设备20立即响应停止指令数据,主机10端停止输送数据。在此过程中,且在前端层201中,控制单元202不会检查缓存单元203中是否存在数据,直接响应停止指令数据,立即停止数据的传输。可提高执行停止指令数据的效率。且主机10在传送完停止指令数据时,也不再接收数据存储设备20传输的数据,进而双向保证主机10和数据存储设备20之间在发送/接收到停止指令数据后,不再进行数据传输。

93.请参阅图2和图7所示,在本发明一实施例中,当主机10发送的指令数据为写入指令数据时,数据存储设备的控制方法包括,

94.s121、接收主机传送的写入指令数据。

95.s122、对写入指令数据继续进行校验。当写入指令数据通过校验时,执行步骤s123,当写入数据未通过校验时,执行步骤s126。

96.s123、将写入指令数据存储在缓存单元中。

97.s124、判断缓存容量是否达到预设阈值,当缓存容量未达到预设阈值时,继续执行

步骤s121,当缓存容量达到预设阈值时,执行步骤s125。

98.s125、执行写入指令数据。

99.s126、停止写入指令数据的传送,等到主机再次发送写入指令数据。

100.请参阅图2和图8所示,在本发明一实施例中,在执行写入指令数据的过程中,当数据存储设备20接收到主机10发送的停止指令数据时,数据存储设备20的控制方法包括,

101.s131、检测缓存单元中是否有数据,当缓存单元中有数据时,执行步骤s132,当缓存单元中没有存储数据时,执行步骤s134。

102.s132、暂缓停止指令数据,并触发直接存储器访问(direct memoryaccess,dma)控制器。

103.s133、直接存储器访问控制器执行缓存单元中的写入指令数据,当缓存单元中的写入指令数据执行完成时,执行步骤s134。

104.s134、响应停止指令数据。

105.请参阅图2和图8所示,在执行写入指令数据的过程中,当数据存储设备 20接收到主机10发送的停止指令数据时,需要检测缓存单元203中是否存在未执行的指令数据。当缓存单元203中有未执行的指令数据时,需要执行完成后,再响应停止指令数据。因为此时若直接响应停止指令数据,缓存单元203中的指令数据有丢失的风险。在本实施例中,使用直接存储器访问(direct memory access,dma)控制器207执行缓存单元203中的指令数据,由直接存储器访问控制器207掌管总线,执行缓存单元203中的指令数据。此时,控制单元202 处于挂起状态或只执行内部操作,无法进行数据存储设备20和外部设备之间的数据传送。使用直接存储器访问控制器207执行缓存单元203中的指令数据,即可暂停响应停止指令数据,又可执行缓存单元203中的指令数据。且在完成缓存单元203中的指令数据后,触发控制单元202响应停止指令数据。

106.请参阅图1所示,在本发明一实施例中,本发明提供的电子设备具体可以包括主机10和通过接口与主机10传送指令数据和/或数据的数据存储设备20。其中,电子设备可以被实现为个人计算机(pc)、工作站、数据中心、互联网数据中心、存储区域网络、网络附属数据存储设备(nas)或移动计算设备,但是本发明构思不限于这些示例。移动计算设备可以被实现为膝上型计算机、蜂窝电话、智能电话、平板pc、个人数字助理(pda)、企业数字助理(eda)、数字静止相机、数字视频相机、便携式多媒体播放器(pmp)、个人导航设备或便携式导航设备 (pnd)、手持式游戏控制台、移动互联网设备(mid)、可穿戴计算机、物联网(iot) 设备、物联网(ioe)设备、无人机或电子书,但是本发明构思不限于这些示例。

107.请参阅图1所示,在主机10和数据存储设备20之间设置有接口,以连接主机10和存储设备20。接口可以是串行高级技术附件(sata)接口,sata快速 (satae)接口、sas(串行附件小型计算机系统接口(scsi))、外围组件互连高速 (pcie)接口、非易失性数据存储设备快速(nvme)接口、高级主机控制单元接口 (ahci)或多媒体卡(mmc)接口,但不限于此。接口可以传输电信号或光信号。主机10可以经由接口控制数据存储设备20的数据处理操作(例如,写操作或读操作)。且接口可以为单独设置在主机10和数据存储设备20之间,也可以集成在数据存储设备29上。

108.请参阅图1所示,在本发明一实施例中,数据存储设备20可以是基于闪存的存储设备,但不限于此。数据存储设备20可以被实现为ssd、嵌入式 ssd(essd)、通用闪速数据存储

设备(ufs)、mmc、嵌入式mmc(emmc)或受管理的nand,但是本发明构思不限于这些示例。基于闪存的数据存储设备设备可以包括数据存储设备单元阵列。数据存储设备单元阵列可以包括多个数据存储设备单元。数据存储设备单元阵列可以包括二维数据存储设备单元阵列或三维数据存储设备单元阵列。三维数据存储设备单元阵列可以单片地形成在具有设置在硅衬底上或上方的有源区的数据存储设备单元阵列中的一个或多个物理层级处,并且可以包括数据存储设备单元的操作所涉及的电路。所述电路可以形成在硅衬底中、硅衬底上或上方。术语“单片”意指阵列中的每一层级的层直接沉积在阵列中的下层级的层上。三维数据存储设备单元阵列可以包括竖直取向的竖直nand串,使得至少一个数据存储设备单元置于另一数据存储设备单元上或上方。所述至少一个数据存储设备单元可以包括电荷俘获层。

109.请参阅图1和图9所示,在本发明一实施例中,在数据存储设备20的器前端层201,可以包括接收单元207、验证单元208、缓存单元203和控制单元202。其中,接收单元207用于接收接收主机10传送的指令数据,且当数据存储设备为嵌入式多媒体存储卡(emmc)时,接收单元207例如为集成的多媒体卡 (mmc)接口。验证单元208电性连接于接收单元207,当接收到主机10传送的数据时,首先通过验证单元208进行检验。且在本实施例中,验证单元208 包括用于循环冗余校验的硬件,以及用于写保护验证和地址超范围错误验证固件。缓存单元203电性连接于验证单元208,用于存储待处理的数据。控制单元 202电性连接于接收单元207、验证单元208和缓存单元203,用于判断缓存容量是否达到预设阈值,当缓存容量达到预设阈值时,将数据传递至中间层204。在验证出现问题时,暂停数据的传递,并将错误循序反馈至主机10,进而执行主机10再次发出的指令数据。且在前端层201还可以设置有暂存单元,暂存单元电性连接于控制单元202,当缓存单元203关闭时,可暂存正在执行的指令数据。在前端层201中还可以设置有暂存单元209,以存储缓存功能关闭时,当前执行的指令数据。

110.请参阅图9所示,在本实施例中,在数据存储设备20的中间层204,设置有地址转换单元210可以完成逻辑数据到闪存块物理地址的转换或者映射。在后端层205中,设置有存储单元211,在本实施例中,存储单元为多个闪存块。

111.请参阅图10所示,本实施例还提出一种计算机可读存储介质3,所述计算机可读存储介质3存储有计算机指令数据30,所述计算机指令数据30用于使用所述数据存储设备的控制方法。计算机可读存储介质3可以是,电子介质、磁介质、光介质、电磁介质、红外介质或半导体系统或传播介质。计算机可读存储介质3还可以包括半导体或固态数据存储设备20、磁带、可移动计算机磁盘、随机存取数据存储设备20(ram)、只读数据存储设备20(rom)、硬磁盘和光盘。光盘可以包括光盘-只读数据存储设备20(cd-rom)、光盘-读/写(cd-rw)和dvd。

112.综上所述,本发明提供的一种数据存储设备及其控制方法与电子设备,在数据存储设备接收到主机发送的数据时,首先将数据存储在缓存单元中,当缓存容量到达预设的阈值时,才会将缓存单元中的数据下方到中间层和后端层,执行相应的指令数据,可提高数据存储设备的执行效率。在设置预设阈值时,根据闪存块的类型精确获取缓存容量的大小,可依据数据的重要程度,设定执行指令数据的速率。当数据存储设备接收到主机传送的停止指令数据时,可以依据此时存储的指令数据的类型,确认是否执行缓存单元中的指令数据,在保证指令数据效率最高的同时,不会丢失数据。本发明提供的一种数据存储设备及其

控制方法,可提高数据存储设备的执行效率。

113.以上描述仅为本技术的较佳实施例以及对所运用技术原理的说明,本领域技术人员应当理解,本技术中所涉及的发明范围,并不限于上述技术特征的特定组合而成的技术方案,同时也应涵盖在不脱离所述发明构思的情况下,由上述技术特征或其等同特征进行任意组合而形成的其它技术方案,例如上述特征与本技术中公开的(但不限于)具有类似功能的技术特征进行互相替换而形成的技术方案。

114.除说明书所述的技术特征外,其余技术特征为本领域技术人员的已知技术,为突出本发明的创新特点,其余技术特征在此不再赘述。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。