一种ldo线性稳压器的浪涌电流控制电路

技术领域

1.本发明涉及ldo线性稳压器技术领域,具体为一种ldo线性稳压器的浪涌电流控制电路。

背景技术:

2.ldo线性稳压器由于具备结构简单、成本低廉、低噪声、低功耗及较小封装尺寸能突出优点,在便携式电子设备中得到了广泛的运用。

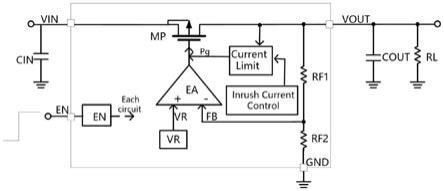

3.传统ldo如图1所示,外围元器件由输入电容cin,输出电容cout,负载电阻rl组成,芯片内部包括使能控制电路en、基准电压vr产生电路、误差放大器ea、限流电路current limit和反馈电阻rf1、rf2。ldo工作原理是:输入使能en信号控制整体电路是否工作,输出电压经反馈电阻rf1、rf2分压采样输入误差放大器ea的反向端,与误差放大器ea的同相端基准电压vr比较误差放大后输出与限流电路current limit输出同时控制调节功率pmos管mp的栅极电位,调节控制使fb电位与基准vr相等,同时控制输出电流不超出限定值,防止pmos功率管损坏同时,控制输出电压vout。

4.传统型ldo启动瞬间,功率管mp导通,给输出电容cout充电,cout一般采用陶瓷电容,esr较小,使输入到地之间低阻抗,会有很大的浪涌电流产生,此电流具有很大危害性,如果不加以解决,这可能会使电源轨失控,从而导致系统进入不希望的状态。

技术实现要素:

5.为解决传统ldo启动浪涌问题,本发明提供一种ldo线性稳压器的浪涌电流控制电路,提高ldo应用可靠性,防止在ldo电源对供电系统造成的损坏。

6.为实现上述目的,本发明提供如下技术方案:一种ldo线性稳压器的浪涌电流控制电路,包括ldo线性稳压器,还包括浪涌电流控制电路,所述浪涌电流控制电路与ldo线性稳压器连接,用于控制启动瞬间浪涌电流,防止启动电流过高对电源规及输出系统造成的损坏。

7.作为本发明的一种优选实施方式,所述ldo线性稳压器包括外围元器件输入电容cin,输出电容cout及负载电阻rl,芯片内部包括使能控制电路en、基准电压vr、误差放大器ea、限流电路、功率pmos管mp以及反馈电阻rf1和rf2,ldo线性稳压器的输出vout经反馈电阻rf1、rf2分压后得到采样电压fb连接至误差放大器ea的反向输入端,误差放大器ea的同相输入端连接基准电压vr,误差放大器ea的输出pg连接功率pmos管mp的栅极,所述浪涌电流控制电路的输出端与限流电路的负向端连接。

8.作为本发明的一种优选实施方式,所述浪涌电流控制电路包括vout电压检测比较电路,时间延时电路,电阻r2、r3、r4,开关s1、s2;vout电压检测比较电路为一比较器,正向端输入vout电压,负向端输入基准电压,输出dout信号控制s1开关和时间延时电路。

9.作为本发明的一种优选实施方式,所述基准电压为0.7v。

10.作为本发明的一种优选实施方式,pmos管mp1,mp1采样镜像mp功率管,比例镜像

iout输出电流,输出i_sense输入inrush current control电路,inrush current control电路输出v_sense电压输入至current ilimit的负向端,与正向端的基准电压vr比较输出,当v_sense升高至于vr时,通过控制pg电位使输出电流恒定不再增加

11.与现有技术相比,本发明提供了一种ldo线性稳压器的浪涌电流控制电路,具备以下有益效果:

12.该一种ldo线性稳压器的浪涌电流控制电路,通过增加浪涌电流控制浪涌电流控制电路,控制启动瞬间输出端电流,防止启动电流过高对电源规及输出系统造成的损坏,且不影响正常工作时限流电路的限流值,有效提高了ldo应用的可靠性,并防止了ldo电源对供电系统造成的损坏。

附图说明

13.通过阅读参照以下附图对非限制性实施例所作的详细描述,本发明的其它特征、目的和优点将会变得更明显:

14.图1是现有技术ldo线性稳压器;

15.图2是本发明带有浪涌电流控制电路的ldo线性稳压器;

16.图3为图2浪涌电流控制电路的等效图;

17.图4为图3中浪涌电流控制电路的一种具体实施电路。

18.图5为图2工作波形图。

具体实施方式

19.为使本发明实现的技术手段、创作特征、达成目的与功效易于明白了解,下面结合具体实施方式,进一步阐述本发明。

20.如图1-5所示,本发明提供一种技术方案:一种ldo线性稳压器的浪涌电流控制电路,包括ldo线性稳压器,还包括浪涌电流控制电路,所述浪涌电流控制电路与ldo线性稳压器连接,用于控制启动瞬间浪涌电流,防止启动电流过高对电源规及输出系统造成的损坏。

21.本实施例中(请参阅图2),所述ldo线性稳压器包括外围元器件输入电容cin,输出电容cout及负载电阻rl,芯片内部包括使能控制电路en、基准电压vr、误差放大器ea、限流电路、功率pmos管mp以及反馈电阻rf1和rf2,ldo线性稳压器的输出vout经反馈电阻rf1、rf2分压后得到采样电压fb连接至误差放大器ea的反向输入端,误差放大器ea的同相输入端连接基准电压vr,误差放大器ea的输出pg连接功率pmos管mp的栅极,所述浪涌电流控制电路的输出端与限流电路的负向端连接,本发明在现有技术基础上(请参阅图1),增加了浪涌控制电路inrush current control;由于ldo启动在未达到设定的vout值时,内部ea及current ilimit控制mp开启以限流值给输出电容及负载充电;通过增加浪涌控制电路inrush current control和current ilimit控制结合控制启动时的充电电流达到浪涌控制电路inrush current control。

22.本实施例中(请参阅图3),所述浪涌电流控制电路inrush current control包括vout电压检测比较电路detect vout,时间延时电路time delay,电阻r2、r3、r4,开关s1、s2;vout电压检测比较电路detect vout为一比较器,正向端输入vout电压,负向端输入0.7v的基准电压,输出dout信号控制s1开关和延时电路time delay,当vout低于0.7v时,

dout输出低信号,控制开关s1为“off”,控制time delay关断,此时time delay输出低信号,控制s2为“off”;当vout高于0.7v时,dout输出高信号,控制s1为“on”,同时控制time delay启动,延时计时开启,延时200us后,time delay输出dtout2控制s2由“off”变为“on”态,v_sense与gnd之间等效电阻r(v_sense-gnd)=r2//r3//r4;开关s1、s2的on/off状态控制电阻r3、r4是否与r2并联连接在v_sense和gnd之间,等效控制v_sense与gnd之间的电阻阻值大小,实现启动和正常工作状态下的具有不同限流值,达到启动瞬间浪涌电流的控制;

23.而推算出启动过程浪涌电流及正常工作的限流值如下:

24.i_inrsh1=kxvr/(r2)

ꢀꢀꢀ

(vout《0.7v)

25.i_inrush2=kxvr/(r2//r3)

ꢀꢀꢀ

(0.7≤vout,time delay《200us)

26.i_limit=kxvr/(r2//r3//r4)

ꢀꢀꢀ

(启动完成后)

27.本实施例中,还包括pmos管mp1,mp1采样镜像mp功率管,比例镜像iout输出电流,输出i_sense输入inrush current control电路,inrush current control电路输出v_sense电压输入至current ilimit的负向端,与正向端的基准电压vr比较输出,当v_sense升高至于vr时,通过控制pg电位使输出电流恒定不再增加。

28.图4是图3的一种电路实施方案,即浪涌电流控制电路的实施例,具体如下:浪涌电流控制电路包括i1,i1为一比较器,nmos管n1、n2、n3、n4;pmos管mp1、mp2;电容c1、cd、c2;电流偏置源ib1,ibd;所述i1比较器正向输入端连接vout,负向输入端连接0.7v基准电压,输出dout连接nmos管n1栅极和nmos管n3的栅极,nmos管n1的栅极连接比较器i1的输出,nmos管n1源极和衬底连接gnd,nmos管漏极连接电流偏置源ib1的负端和电容c1的正端及nmos管n2的栅极和pmos管mp2的栅极,nmos管n2的栅极连接c1的正端、pmos管mp2的栅极、nmos管n1的漏极及电流源偏置源的负端,nmos管n2的源极和衬底连接gnd,nmos管n2的漏极连接电容cd的正端、nmos管n4的栅极、及电流偏置源ibd的负端,nmos管n3的栅极连接比较器i1的输出、nmos管n1的栅极,nmos管n3的源级连接电阻r3的正端,nmos管n3的衬底连接gnd,nmos管n3的漏极连接电阻r4的正端、pmos管mp1的漏极、nmos管n4的漏极和电容c2的正端,nmos管n4的栅极连接nmos管n2的漏极、电流偏置源ibd的负端和电容cd的正向端,nmos管n4的源极连接电阻r4的正端,nmos管n4的衬底连接gnd,nmos管n4的漏极连接电阻r2的正端、pmos管mp1的漏极、nmos管n3的漏极和电容c2的正端,pmos管mp2的栅极连接电流偏置源ib1的负端和电容c1的正端及nmos管n2的栅极和nmos管n1的漏极,pmos管mp2的源极和衬底连接vin,pmos管mp2的漏极连接电流偏置源ibd的正端,pmos管mp1的栅极连接pg(功率pmos管栅极),pmos管mp1的源和衬底连接vin,pmos管mp1的漏极连接nmos管n4的漏极、电阻r2的正端、nmos管n3的漏极和电容c2的正端;电流偏置源ib1的正端连接vin,负端连接nmos管n1的漏极、电容c1的正端、nmos管n2的栅极和pmos管mp2的栅极;电流偏置源ibd的正端连接pmos管mp2的漏极,电流偏置源ibd的负端连接nmos管的n2漏极、电容cd的正端、nmos管n4的栅极;电容c1负端连接gnd,电容c1正端连接电流偏置源ib1的负端、nmos管n1的漏极、nmos管n2栅极和pmos管mp2的栅极;电容cd负端连接gnd,电容cd正端连接电流偏置源ibd的负端、nmos管n2的漏极及nmos管n4的栅极;电容c2的负端连接gnd,电容c2的正端连接pmos管mp1的漏极、nmos管n4的漏极、电阻r2的正端、nmos管n3的漏极;电阻r2的负端连接gnd,电阻r2的正端连接电容c2的正端、pmos管mp1的漏极、nmos管n4的漏极、nmos管n3的漏极;电阻r3的负端连接gnd,电阻r3的正端连接nmos管n3的源极;电阻r4的负端连接gnd,电阻r4的正端连接

nmos管n4的源极;

29.dout为比较器detect vout的输出,当vout低于0.7v时,dout输出为低,控制nmos管n1和n3关闭,同时n1管漏极输出为高,经反向输出dtout2为低,控制n4栅极也为低,此时v_sense电压值为i_sense与r2阻值乘积;当vout电压升高至0.7v时,dout由低翻高,控制nmos管n3打开,同时控制nmos管n1栅极为高,则nmos管n1漏极及nmos管n2栅极电位翻低,电流偏置源ibd开始给电容充电cd,当充电延时时间达cd*vthn/ibd时,可通过ibd及cd值调节设定此延时时间为200us,nmos管n4开启;在nmos管n4开启前v_sense电压值为i_sense与r2//r3阻值乘积,在nmos管n4开启后v_sense电压值为i_sense与r2//r3//r4阻值乘积

30.以上显示和描述了本发明的基本原理和主要特征和本发明的优点,对于本领域技术人员而言,显然本发明不限于上述示范性实施例的细节,而且在不背离本发明的精神或基本特征的情况下,能够以其他的具体形式实现本发明。因此,无论从哪一点来看,均应将实施例看作是示范性的,而且是非限制性的,本发明的范围由所附权利要求而不是上述说明限定,因此旨在将落在权利要求的等同要件的含义和范围内的所有变化囊括在本发明内。不应将权利要求中的任何附图标记视为限制所涉及的权利要求。

31.此外,应当理解,虽然本说明书按照实施方式加以描述,但并非每个实施方式仅包含一个独立的技术方案,说明书的这种叙述方式仅仅是为清楚起见,本领域技术人员应当将说明书作为一个整体,各实施例中的技术方案也可以经适当组合,形成本领域技术人员可以理解的其他实施方式。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。