1.本发明涉及空间阵列的快速、精确仿真领域领域,尤其涉及基于事件驱动的可重构空间阵列的仿真建模平台及方法。

背景技术:

2.可重构计算体系结构结合了软件灵活性和硬件高性能性,是一种可以通过自定义计算方式、存储结构和互连关系,以面向各领域内应用加速其核心计算的通用处理器,具有相当高的编程自由度,cgras除了支持动态可编程性外,还支持大量并行性,这些并行可以提高性能和能效比。cgras也可以通过可扩展的互连拓扑和可靠、高速的通信机制设计,实现算力的大规模扩展,进一步加速应用的计算过程,实现高密度计算。可重构阵列一般由三种部件组成,处理单元(processingelement,pe)阵列,互连网络,以及配置存储器。基本工作原理是将对应用算法的描述存放在配置存储器中,该配置决定了每个处理单元的功能和互连网络的数据交换方式,类似定制计算中算法到硬件电路的映射。通过改变配置存储器的内容,就可以重新构造处理单元和互连网络。然而,迄今为止,cgra上的所有工作都已限制在各自的框架上,如三星可重构处理器和renesas电子的stp可重新配置处理器不同架构框架下的pe单元、访存单元的实现千差万别。

3.现有的可重构结构并没有统一的运算模型和整体结构模型,所以不利于不同方案的横向对比。同时硬件上实现一个复杂的交换单元的设计方案,所需要的开发成本十分高昂,实现周期长。而且硬件实现的结果如果不符合交换单元的需求,那么又需要修改硬件实现方案,又需要经过漫长的时间,这样大大增加了交换单元的开发时间。如果能够在硬件实现之前,能够确保设计方案的性能满足需求,则能减少硬件修改的次数,从而缩短开发周期。而软件仿真能够衡量设计方案的性能好坏,在发现设计方案问题的时候可以及时对设计方案进行修改,然后继续进行仿真测试性能,这样为硬件实现提供了良好的方案,避免重复繁琐的硬件修改过程。

4.针对仿真平台的应用需求,常用于仿真的交互方式有:时间驱动、事件驱动等。其中时间驱动是指按照时钟线定时执行,将每个节点的仿真函数放到时间队列中按序执行,这种仿真架构可以完全模拟硬件的执行方式,可以做到周期精确,因为仿真粒度过细,时间驱动的仿真架构会使得仿真速度慢,同时仿真任务量大,不利于快速的仿真性能验证。基于事件驱动的仿真架构在系统仿真中更为常见,事件驱动架构模式是一种非常流行的分布式异步架构模式,经常被用与构建高可伸缩性的应用程序。这种架构模式由一系列高度解耦的、异步接收和处理事件的单一职责的组件所组成。离散事件模型的核心思想是用事件队列表示各种事件的先后顺序,以及在不同的事件后会触发新的事件发生,通过入队和出队操作来模拟事件的发生和结束。同样,描述芯片内部行为,还需要维护一个时间轴,所有的事件都有专属的执行时间的概念。在事件驱动的模拟引擎下,一个数据帧的到达可以用数个事件来描述(帧长、耗费的时间等)。

5.现有的cgra的软件仿真建模以时间驱动为主,可以完全模拟硬件的执行,但是对

于阵列利用率不高的应用时,时间驱动式模拟器存在无效的仿真,大大减慢了仿真的速度。

6.2017年,多伦多大学的电气和计算机工程系为了整合cgra的开发,使得 cgra的开发不受限制与具体的框架,能进行快速的设计与验证,开发了 cgra-me(coarse-grained reconfigurable architectures modelling and exploration, cgra-me)的开源框架。cgra-me允许架构师在基于xml的语言中指定cgra 架构,并提供了一个灵活的调度、映射、放置和路由工具,构建在流行的llvm 编译器框架中,它将一个优化的c语言基准映射到指定的cgra上。为cgra设备自动生成的verilog rtl允许使用modelsim进行功能验证的模拟,也允许使用 asic流将cgra合成为标准单元,以评估面积、性能和功率。cgra-me旨在将以前的cgra工作的各个方面合并到一个更大、更完整的cgra体系结构评估框架中,该框架包括体系结构描述、体系结构建模、应用程序映射、系统仿真和物理实现。但是该框架依旧采用硬件语言仿真,在探索大型应用在所设计的特定架构下的性能表现时,仍存在仿真时间长、单元建模复杂的问题。

7.异构可重构阵列处理器既可以保持相对于asic的较高性能,又可以实现类似 fpga一样的高自由度,是一种灵活性与专用性的折中方案,这让它在通用计算领域很有应用前景。然而,传统的架构设计中,设计出的可重构阵列模拟器与具体方案存在强烈的耦合,不利于进行快速的架构探索;同时基于时钟驱动的仿真器存在仿真速度慢,无法省略无效周期的问题。

8.因此,本领域的技术人员致力于开发一种基于事件驱动的可重构空间阵列的仿真建模平台及方法,能够支持快速的建模,通过周期精确的仿真平台对比不同架构参数、通信机制下的架构性能表现。

技术实现要素:

9.有鉴于现有技术的上述缺陷,本发明所要解决的技术问题是可重构阵列模拟器与具体方案存在强烈的耦合,不利于进行快速的架构探索;同时基于时钟驱动的仿真器存在仿真速度慢,无法省略无效周期的问题。

10.为实现上述目的,本发明提供了一种基于事件驱动的可重构空间阵列的仿真建模平台,所述平台包括:

11.以事件驱动为引擎;

12.通过模块设计与通信接口实现的解耦,将所述仿真建模平台搭建成为模块的组合方式实现,通过参数化、桩替代实现不同的模块不同硬件参数的快速迭代,同时测试不同硬件通信机制的性能表现。

13.以事件驱动为引擎,解决了传统可重构架构模拟器中时钟驱动的无效周期、无效仿真带来的仿真任务量大、仿真速度慢的问题,提升仿真速度。

14.进一步的,以时间驱动为引擎,将硬件中的动作执行化作带有时间帧概念的事件。

15.将硬件中的动作执行化作带有时间帧概念的事件,不再按照时钟式实现每个周期的硬件行为,简化了建模难度及跳过了因为堵塞、流水线不平问题带来的无效的节点模拟,极大的提高了仿真速度及建模速度。

16.进一步的,每个模块仿真模型的实现被划分为功能模型与硬件通信接口,实现了接口与功能的解耦,通过组合不同的功能与硬件通信机制进行架构的设计,而不需要更改

仿真平台的底层实现。

17.通过模块设计与通信接口实现的解耦,将整个仿真平台搭建成为模块的组合方式实现,实现了版本的快速迭代与验证。

18.进一步的,所述的解耦的硬件通信机制接口,包括基于ack反馈机制和基于 credit反馈机制的硬件通信接口,在硬件模块仿真时,声明模块间的通信机制,而无需修改模型代码,实现了丰富的库单元,包括功能模型库与通信接口模型库。

19.进一步的,所述仿真建模模型包括仿真环境,对仿真环境进行配置,包括:

20.配置缓存容量,以测试不同的缓存尺寸对性能的影响;

21.配置通信机制分析不用的机制对不用应用的适配程度;

22.通过配置文件和参数文件形成完整的阵列连接结构及节点功能配置,控制模块读取该配置并生成对应仿真单元;

23.所有的仿真单元均通过事件管理的时间轴进行时间帧的安排,实现周期精确的仿真。

24.进一步的,所述ack反馈机制设置主端口和从端口两个基础接口类,所述主端口的参数包括:

25.unlocksig:每次通信发送数据需要所有的从端口都接收到主端口输出,表示一次通信完成,从而释放临时端口锁;

26.sig:触发主端口发送数据到从端口,同时每当某个从端口成功接收数据,便由从端口自主临时断开端口直至主端口重新unlocksig;

27.output:主端口的输出发送数据的函数指针,需要动态绑定对应的输出函数,给从端口使用,从端口向主端口主动发起请求是便是通过该函数指针;

28.所述从端口的参数包括:

29.block:每次通信当该从端口接收到数据会,会更改该变量,临时锁住与主端口的连接,直到所有从端口均接收到数据,一次完整的通讯完成,从端口释放该变量;

30.needretry:事件驱动模型下,若发生不能成功接收数据的情况,会导致事件的注册与执行的偏差,用整型变量记录端口堵塞的数量,防止事件的丢失;

31.sendreqretry:从端口在不能成功接收数据时,会在满足接收条件后自主通过该指针,向主端口发送接收请求,该指针动态绑定主端口的output;

32.getbp:从端口向主端口通过该指针反馈是否正确接收数据,在实现实例化模型时,需要对该函数指针进行动态绑定;

33.setinput:从端口将输入取入,为模块导入主端口发送的数据;

34.unlock:释放类中的block变量,释放时机由主端口控制,对应主端口中的 unlocksig;

35.getinput:与主端口的sig绑定,是接收主端口输入的接口函数,该函数会根据getbp信息更改needretry_或者调用setinput;

36.retry:从端口空闲时,会通过该函数查询needretry_判断是否有被堵塞的数据,进而向主端口发送请求数据。

37.在实现具体的硬件模块仿真模型时,编程人员可以声明模块间的通信机制,而无需修改模型代码,实现了丰富的库单元,包括功能模型库与通信接口模型库。

38.进一步的,所述参数给sig包括数据包pkt,所述数据包pkt是模块与模块间的通信数据,每次主端口与从端口的通信数据定义在define文件中。

39.一种基于事件驱动的可重构空间阵列的仿真建模方法,应用于所述的一种基于事件驱动的可重构空间阵列的仿真建模平台上,包括以下步骤:

40.(1)对阵列的硬件结构参数进行建模设置,应用的映射受到硬件参数其硬件参数限制;

41.(2)对计算节点pe内部的alu的计算周期进行参数设定;

42.(3)对阵列进行互联及功能配置的输入,对算法进行手工映射,将对应的单元配置成独立的功能节点,同时声明互连关系,仿真平台读取配置文件,生成节点,然后根据互连关系通过attach函数进行端口的连接。

43.进一步的,根据起始节点添加首事件,节点间根据连接关系不断注册新的事件,保证每个事件均是有效事件,使用链式结构串联起整个系统的仿真。

44.进一步的,pe内部的输入buffer发生输入事件,当外部传进数据时,如果该 buffer为空,则直接在对应的延迟后的周期注册输出事件,否则在发生堵塞时,则保存输出的周期数,当该数据成为头部数据时再注册输出事件;pe输出buffer发生输出事件时,当发送数据成功时则检测是否剩有数据,再进行事件的注册;时间轴跳过空事件的周期,当时间轴上的事件列表为空时,说明完成系统的仿真。

45.本发明是基于事件驱动的面向空间阵列式处理器的快速仿真建模技术,相比于现阶段已提出的模拟器设计,本发明的特点在于:1、根据重构空间阵列中不同计算节点硬件实施细节,实现各个节点的事件驱动下的周期精确模型,构建了可重构阵列的通用库单元,解决仿真建模时周期驱动下的无效仿真及同一节点的多次建模;2、构建不同的硬件通信模型,将硬件节点的仿真与节点间通信机制解耦合;使其面向不同空间阵列架构时,能快速评估各种硬件通信机制下的性能表现3、基于硬件的物理实现,针对不同计算节点和节点间通信模型模块化精准建模,并建立事件驱动机制机制有效实现模块化模型的有机统一,实现空间阵列计算架构和互连架构设计的快速仿真与迭代。

46.本发明通过构建可扩展的事件驱动仿真框架,来解决架构探索中模拟平台与设计耦合度高,修改复杂的问题;进而根据异构单元的特性,提出实现了通用单元如pe、访存单元的软件模型库及不同的通信机制模型如基于ack的反馈机制、基于credit的反馈机制等。与传统异构阵列模拟器相比,在相同应用架构下,应用事件驱动下模块化的仿真平台进行模拟仿真在debug模式下可以获得平均89%的仿真速度提升,在release模式下可以获得平均529%的仿真速度提升。

47.以下将结合附图对本发明的构思、具体结构及产生的技术效果作进一步说明,以充分地了解本发明的目的、特征和效果。

附图说明

48.图1是典型异构可重构阵列;

49.图2是片上可配置便笺式缓存结构图;

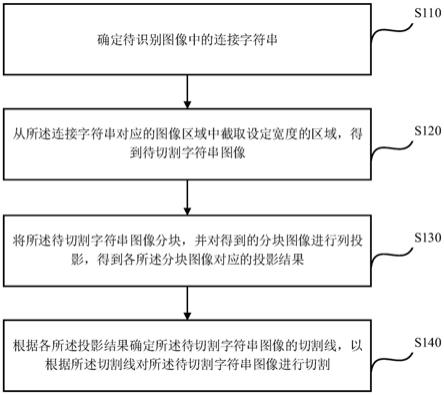

50.图3是输入事件流程图;

51.图4输出事件流程图。

具体实施方式

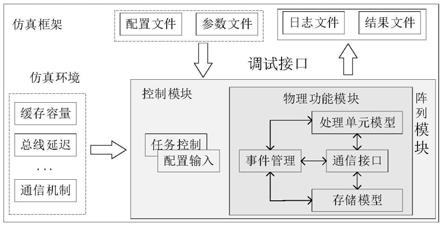

52.以下参考说明书附图介绍本发明的多个优选实施例,使其技术内容更加清楚和便于理解。本发明可以通过许多不同形式的实施例来得以体现,本发明的保护范围并非仅限于文中提到的实施例。

53.在附图中,结构相同的部件以相同数字标号表示,各处结构或功能相似的组件以相似数字标号表示。附图所示的每一组件的尺寸和厚度是任意示出的,本发明并没有限定每个组件的尺寸和厚度。为了使图示更清晰,附图中有些地方适当夸大了部件的厚度。

54.如图1所示,典型的可重构阵列由多个可重构阵列切片组成,每个切片由计算阵列、片上缓存、配置控制器及任务控制器构成。图1为典型异构可重构阵列的示意图。从功能上可以将整个cgra系统划分为三个主要部分:可重构阵列、存储系统和控制模块。基本工作原理是将对应用算法的描述存放在配置存储器中,该配置决定了每个处理单元的功能和互连网络的数据交换方式,类似定制计算中算法到硬件电路的映射。通过改变配置存储器的内容,就可以重新构造处理单元和互连网络。处理单元通常称为pe,承担主要的计算功能,阵列中会有大量pe 呈规则排布,根据不同的需要,不同的可重构处理器pe可以执行的功能与结构可能千差万别。

55.本发明以图1所示的静态异构阵列为基础,搭建不同的单元库,以事件为驱动引擎,构建整个模拟框架,在此阵列上映射不同的应用,与传统的时间驱动式仿真平台及对应硬件平台进行运行速度及仿真精确度的对比。

56.针对不同架构的性能参数,本发明通过参数化执行时间及缓存单元的深度,快速验证不同参数下的性能表现,为架构设计提供指导,便于架构的快速开发和迭代;同时本发明中将单元模型的实现与模块间的交互通信进行解耦,提供了不同的硬件反馈机制的通信机制,同样可以探索不同的通信机制对架构性能的影响。整个平台均以事件驱动,极大的减少了仿真量,同时连接不同的单元库可以直接实现不同的架构仿真,提高了平台的扩展性及适应性。

57.如图2所示,本发明中提出基于事件驱动的可重构阵列快速仿真模型生成平台,其结构示意图如图2所示,其中虚线部分是编程人员需要对模拟单元进行配置的部分。从仿真环境上,需要配置缓存容量,以测试不同的缓存尺寸对性能的影响;配置通信机制探索不用的机制对不用应用的适配程度等。通过配置文件和参数文件形成完整的阵列连接结构及节点功能配置,控制模块读取该配置并生成对应仿真单元。所有的仿真单元均通过事件管理的时间轴进行时间帧的安排,实现周期精确的仿真。

58.为实现接口化与模块化,使架构设计人员只需要关注节点的具体行为及时序。本发明中研究了可重构阵列中两种典型硬件通信机制——基于credit的反馈机制与基于ack的反馈机制,并将其与节点行为分离,编程人员在配置阵列时可以选择不同的通信机制进行性能测试。以基于ack的反馈为例,本发明中实现了两个基础接口类,为主端口(simmaster)和从端口(simslave)。这两个接口类分别对应硬件语言中的output及input类型,simmaster接口类的实现如下表1所示。

59.表1simmaster类实现接口

[0060][0061][0062]

表中所述pkt是数据包,是模块与模块间的通信数据,每次simmaster与 simslave的通信数据定义在define文件中,需要仿真人员进行定义申明,原则上不允许通信包为空类型。simslave的接口实现如下表2所示。

[0063]

表2simslave类实现接口

[0064]

[0065][0066]

针对数据驱动式异构可重构阵列的典型结构及其特点,本发明中实现阵列中的典型模块—处理运算单元及访存单元的编程模型,并将其影响架构的配置部分进行参数化,以便编程人员快速修改建模,迭代参数版本。同时支持加入自定义编程模型。接口之间的连接采用attach(simmaster*outport,simslave*inport)的方式,此函数会将上文中提出的simmaster与simslave端口连接,不允许同类端口相连接。在模块实现中,只需要将模块的端口根据输入输出类型将其声明为simmaster 或simslave,然后在对应的配置文件中声明连接关系,控制模块将二者通过上诉函数连接,便完成整个系统的搭建,实现了模块与驱动框架的分离。

[0067]

综上,本发明新提出的基于事件驱动的可重构阵列快速仿真模型生成平台的技术特点主要体现在以下两点:

[0068]

1.按事件驱动的方式实现典型可重构阵列的快速建模,将各个硬件单元按时间帧实现,并保留配置参数接口,实现了丰富的单元库,通过不同参数、结构单元的组合可以快速修改架构、验证性能,提高了版本迭代的速度。

[0069]

2.通过实现不同的硬件通信反馈机制,实现模块间的通信与功能的解耦,可以直

接通过配置文件更改通信机制而不需更改模块代码,将系统的仿真平台生成按照接口化连接,提高了代码的复用性。

[0070]

本发明中提出基于事件驱动的可重构阵列快速仿真模型生成平台核心技术主要包括:事件驱动式仿真引擎减少仿真的无效周期及无效节点的仿真,大大提高仿真速度,根据电路特点简化节点实现方式,降低了节点的实现难度;模块化的编程组合方式将各个节点的实现解耦,组装不同的硬件模块可以快速验证不同硬件参数、不同通信机制下的性能表现,而不用影响相邻组件的实现,具体实施案例如下。

[0071]

将yolov3-tiny中的卷积核为3*3的卷积神经网络映射在阵列中上,得出该应用在阵列上的计算性能及利用率等情况。首先,对模拟器中的硬件环境进行配置,上文中提到为了专注于阵列的计算性能,阵列会对计算数据包括卷积图像、卷积核等输入数据进行预取,所有的数据将存放于阵列中,因此在此工作模式下,数据不会在阵列中发生缺失。

[0072]

首先对阵列的硬件结构参数进行建模设置,应用的映射受到硬件参数其硬件参数限制,具体硬件参数如下表3所示:

[0073]

表3阵列硬件参数配置

[0074][0075]

为做到周期精确,对计算节点pe内部的alu的计算周期进行参数设定,具体参数情况如下表4所示:

[0076]

表4时钟周期配置

[0077][0078][0079]

上述实例中,在设定完成硬件信息的配置文件后,需要对阵列进行互联及功能配置的输入,对选取的上述的卷积运算的算法进行手工映射,将对应的单元配置成独立的功能节点,同时声明互连关系。仿真平台读取配置文件,生成节点,然后根据互连关系通过attach函数进行端口的连接。

[0080]

在具体执行时,根据起始节点添加首事件,称为平台激励。节点间根据连接关系便会不断注册新的事件,保证每个事件均是有效事件,使用链式结构串联起整个系统的仿真。pe内部的输入buffer发生输入事件如图3所示,当外部传进数据时,如果该buffer为空,则可以直接在对应的延迟后的周期注册输出事件,否则在发生堵塞时,则保存输出的周期数,当该数据成为头部数据时再注册输出事件。

[0081]

pe输出buffer发生输出事件时,其流程图如图4所示,当发送数据成功时则检测是否剩有数据,再进行事件的注册。

[0082]

时间轴根据会跳过空事件的周期,当时间轴上的事件列表为空时,说明完成系统的仿真。

[0083]

基于上述配置,系统可以完成神经网络卷积层的计算。当探索不同的硬件参数对性能影响时,可以直接修改配置文件。同时不同模块间的解耦实现,模块化的组合实现使得在探索某个具体模型的详细信息时,可以使用桩替换机制,更改其模型实现细节进行更详细准确的仿真,而不用修改其他模型。同时省去跳过了无效周期、无效节点的仿真使得整体仿真速度得到提升。综上,使用本发明提出的基于事件驱动的可重构阵列快速仿真模型生成平台可以进行快速的架构探索,也大幅提升了仿真速度。

[0084]

本发明中提出基于事件驱动的可重构阵列快速仿真模型生成平台,通过将不同的应用映射在使用本发明提出的仿真平台上和原有周期精确模拟器上,对比性能准确度及仿真速度;同时在对应的rtl平台上测试真实硬件对应的性能表现,体现本发明的建模准确度和仿真速度提升。其中使用的应用包括yolov3-tiny中两个典型卷积层,卷积核大小分别为3*3及1*1,因此此次测试中分别测试3*3及1*1卷积运算;快速傅里叶变换(fastfouriertransform,fft);消息摘要算法(messagedigest,md);奇偶排序算法等不同类型算法。测试应用情况如下表所示:

[0085]

表5应用测试简介

[0086][0087][0088]

执行时间:采用8*8的pe阵列映射上述算法,因此阵列共有64个计算单元及32个访存单元。针对上述5个不同类型应用,采用针对该架构的最佳映射优化方案,同时对数据进行预取,将数据提前存入片上缓存,因此忽略ddr对性能的影响。在测试中,本发明提出的事件驱动式模拟器、时钟驱动式模拟器及rtl仿真平台输入相同的配置文件,其计算周期如下

表所示。

[0089]

表6不同平台不同应用的性能表现

[0090][0091]

仿真速度提升:本发明的测试环境为visual stdio 2019,在此平台上有两种基础的运行模式—debug及release模式。本发明针对两种模式均进行了测试,以验证本发明提出的基于事件驱动的可重构阵列快速仿真模型生成平台的仿真速度提升,其仿真速度及仿真提升如下表所示。

[0092]

表7不同应用的两种仿真平台的速度对比表

[0093][0094][0095]

与传统异构阵列模拟器相比,在相同应用架构下,应用事件驱动下模块化的仿真平台进行模拟仿真在debug模式下可以获得平均89%的仿真速度提升,在release 模式下可以获得平均529%的仿真速度提升。

[0096]

以上详细描述了本发明的较佳具体实施例。应当理解,本领域的普通技术无需创造性劳动就可以根据本发明的构思作出诸多修改和变化。因此,凡本技术领域中技术人员依本发明的构思在现有技术的基础上通过逻辑分析、推理或者有限的实验可以得到的技术方案,皆应在由权利要求书所确定的保护范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。