1.本发明涉及半导体技术领域,特别涉及一种掩膜及有效减小极紫外掩膜黑边界效应的方法。

背景技术:

2.随着半导体器件尺寸不断缩小,使用传统的平版印刷技术(lithography)已经很难获得更精细的节距图案。由于有明显较窄的照明波长(λ=13.5纳米),所以极紫外光(euv)光刻有可能补足且最终取代习知深紫外光(duv)光刻,除了其它效益以外,它还可提供增强的图案化分辨率及较低的工艺复杂度。目前euv被开发成未来可能结合32纳米节距分辨率的浸润式光刻(immersion lithography),有时被称为7纳米节点。

3.euv光刻中存在掩膜黑边界效应(mask black border effect),会影响光刻效果,从而进一步地影响半导体器件的性能。

技术实现要素:

4.本发明的目的在于解决现有技术中,黑边界效应影响光刻效果的问题。本发明提供了一种掩膜及有效减小极紫外掩膜黑边界效应的方法,可有效地减小掩膜黑边界效应,即:减小掩膜黑边界效应对光刻效果的影响,进一步提高半导体器件的性能。

5.为解决上述技术问题,本发明的实施方式公开了一种光刻掩膜,所述光刻掩膜的图案区域包括第一图案区域和第二图案区域,所述第二图案区域位于所述第一图案区域的外周侧;且所述第二图案区域的掩膜图案的关键尺寸基于所述光刻掩膜图案区域的外边界到所述图案区域中轴的距离,以及所述距离和尺寸补偿值的对应关系调整得到。

6.本发明的实施方式还提供一种有效减小极紫外掩膜黑边界效应的方法,包括:

7.提供光刻掩膜;

8.得到所述光刻掩膜图案区域的外边界到所述图案区域中轴的距离,得到所述距离和尺寸补偿值的对应关系;其中,所述图案区域包括第一图案区域和第二图案区域,第二图案区域位于所述第一图案区域的外周侧;

9.根据距离确定尺寸补偿值,并根据尺寸补偿值至少对第二图案区域内的掩膜图案进行补偿,得到修正光刻掩膜,并使所述修正光刻掩膜的关键尺寸被调整至预设值内;

10.基于所述修正光刻掩膜进行光刻。根据本发明的另一具体实施方式,本发明的实施方式公开的一种有效减小极紫外掩膜黑边界效应的方法,根据下式计算进行补偿后的所述修正光刻掩膜的关键尺寸:cd2=cd1

△

cd,其中,cd1为掩膜图案的初始关键尺寸,cd2为进行补偿后的掩膜图案的关键尺寸,

△

cd为尺寸补偿值。

11.根据本发明的另一具体实施方式,本发明的实施方式公开的一种有效减小极紫外掩膜黑边界效应的方法,当距离大于零小于第一阈值时,

△

cd=a,a为任意常数。

12.根据本发明的另一具体实施方式,本发明的实施方式公开的一种有效减小极紫外

掩膜黑边界效应的方法,当距离大于第一阈值且小于第二阈值时,其中x为距离,c、x0和μ为任意常数。

13.根据本发明的另一具体实施方式,本发明的实施方式公开的一种有效减小极紫外掩膜黑边界效应的方法,当距离大于第二阈值时,

△

cd=b,b为任意常数。

14.根据本发明的另一具体实施方式,本发明的实施方式公开的一种有效减小极紫外掩膜黑边界效应的方法,a、b、c、x0、μ、第一阈值和第二阈值的均为根据初始关键尺寸和/或距离确定的常数。

15.根据本发明的另一具体实施方式,本发明的实施方式公开的一种有效减小极紫外掩膜黑边界效应的方法,所述光刻掩膜图案区域包括多个间隔设置的子图案,所述根据所述尺寸补偿值至少对所述第二图案区域内的掩膜图案进行补偿,包括:

16.减小至少一个所述子图案的关键尺寸;和/或增大至少两个相邻的所述子图案之间的子图案间隙的关键尺寸;和/或增大所述子图案与所述第一图案区域内的子图案之间的子图案间隙的关键尺寸。

17.根据本发明的另一具体实施方式,本发明的实施方式公开的一种有效减小极紫外掩膜黑边界效应的方法,图案区域的形状包括圆形、椭圆形或多边形。

18.根据本发明的另一具体实施方式,本发明的实施方式公开的一种有效减小极紫外掩膜黑边界效应的方法,当图案区域定义为矩形时,根据尺寸补偿值调整掩膜图案的关键尺寸,包括:

19.将第二图案区域周侧划分为四条边和四个角,在四条边和四个角处分别根据尺寸补偿值调整掩膜图案的关键尺寸。

20.本发明的实施方式还公开了一种掩膜关键尺寸的调整方法,包括:得到掩膜的图案区域的外边界到图案区域中轴的距离;其中,图案区域包括第一图案区域和第二图案区域,第二图案区域位于第一图案区域的外周侧;

21.根据距离与距离和尺寸补偿值的对应关系确定尺寸补偿值,并根据尺寸补偿值对第二图案区域内的掩膜图案进行补偿以调整掩膜图案的关键尺寸。

22.本发明的实施方式还公开了一种掩膜,掩膜的图案区域包括第一图案区域和第二图案区域,第二图案区域位于第一图案区域的外周侧;且第二图案区域的掩膜图案的关键尺寸通过如上的掩膜关键尺寸的调整方法调整得到。

23.本发明的有益效果是:根据距离与距离和尺寸补偿值的对应关系确定尺寸补偿值,并根据尺寸补偿值对掩膜的第二图案区域内的掩膜图案进行补偿以调整该掩膜图案的关键尺寸,使得第二图案区域内的掩膜图案的关键尺寸被补偿,在后续进行光刻的时候,可以有效地减小甚至消除掩膜黑边界效应对光刻带来的影响,使得半导体器件的关键尺寸保持在预设的范围内,有效地提升了半导体器件的性能。

附图说明

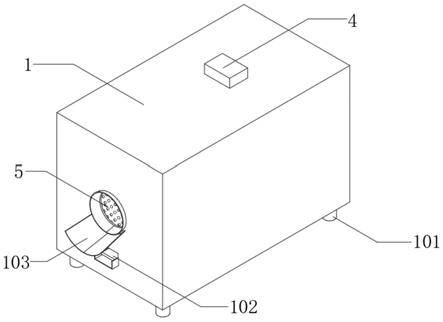

24.图1是一种euv光刻系统的结构示意图;

25.图2是一种euv光刻系统的另一结构示意图;

26.图3是一种掩膜结构示意图;

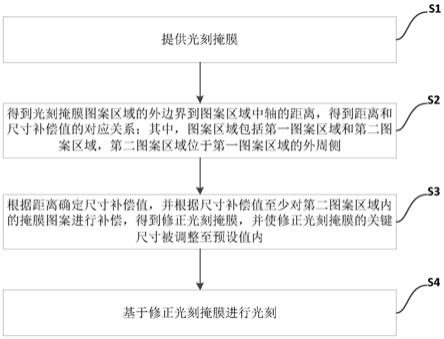

27.图4是本发明实施例提供的有效减小极紫外掩膜黑边界效应的方法流程图;

28.图5是本发明实施例提供的掩膜的另一结构示意图;

29.图6是本发明实施例提供的掩膜的图案区域的外边界到图案区域中轴的距离与初始关键尺寸的线性关系图;

30.图7是本发明实施例提供的有效减小极紫外掩膜黑边界效应对应的掩膜的又一结构示意图。

31.附图标记:

32.1.图案区域;11.第一图案区域;12.第二图案区域;21.子图案;22.子图案间隙;3.曝光系统;31.光源;32.掩膜工作台;33.投影光学单元;34.晶圆工作台;4.光刻掩膜;41.背面涂层(backside-coating)42.基底(substrate);43.金属复合层(ml);44.覆盖层(cap);45.缓冲层(buffer);46.吸收层(absorber);a.过反射部分。

具体实施方式

33.以下由特定的具体实施例说明本发明的实施方式,本领域技术人员可由本说明书所揭示的内容轻易地了解本发明的其它优点及功效。虽然本发明的描述将结合较佳实施例一起介绍,但这并不代表此发明的特征仅限于该实施方式。恰恰相反,结合实施方式作发明介绍的目的是为了覆盖基于本发明的权利要求而有可能延伸出的其它选择或改造。为了提供对本发明的深度了解,以下描述中将包含许多具体的细节。本发明也可以不使用这些细节实施。此外,为了避免混乱或模糊本发明的重点,有些具体细节将在描述中被省略。需要说明的是,在不冲突的情况下,本发明中的实施例及实施例中的特征可以相互组合。

34.应注意的是,在本说明书中,相似的标号和字母在下面的附图中表示类似项,因此,一旦某一项在一个附图中被定义,则在随后的附图中不需要对其进行进一步定义和解释。

35.在本实施例的描述中,需要说明的是,术语“上”、“下”、“内”、“底”等指示的方位或位置关系为基于附图所示的方位或位置关系,或者是该发明产品使用时惯常摆放的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

36.术语“第一”、“第二”等仅用于区分描述,而不能理解为指示或暗示相对重要性。

37.在本实施例的描述中,还需要说明的是,除非另有明确的规定和限定,术语“设置”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本实施例中的具体含义。

38.正如背景技术所述,现有的euv光刻中存在掩膜黑边界效应对光刻的影响,从而影响半导体器件的性能。

39.具体的,参见图1和图2所示的euv光刻系统的示意图,其中曝光系统3包括光源31、掩膜工作台32、投影光学单元33和晶圆工作台34。光源31是用来产生极紫外光光线,因此光源31也可以被称为极紫外光光源;而光源31发出的光线并不限定为极紫外光光线,还可以是其它高强度的光子。光源31产生的光线通过掩膜工作台32、投影光学单元33传递至晶圆

工作台34对晶圆表面的光阻进行曝光。

40.如图2所示,euv曝光系统会对光刻掩膜4进行过度扫描,反射光线会存在过反射部分a,当图案被打印至晶圆表面的光阻上时,这会导致在接下来的光刻或其它过程中,晶圆部分出现较小的恒定剂量(即过度光刻),这会影响半导体器件的性能(即会存在掩膜黑边界效应对光刻造成影响的问题)。

41.具体地,如图3所示,光刻掩膜4包括背面涂层41、基底42、金属复合层43、覆盖层44、缓冲层45和吸收层46。光刻掩膜4的图案区域1包括第一图案区域11和第二图案区域12,其中第二图案区域12会造成前述所说的掩膜黑边界效应。

42.现有技术中,提供了一种减小极紫外掩膜黑边界效应的方法,具体的,请参见图3,在第二图案区域12内刻蚀金属复合层43形成沟槽,可以有效地减小极紫外掩膜黑边界效应,但是这种处理方式会使得光刻掩膜4的有效掩膜面积减小,从而降低了有效器件区面积,提高了生产成本;而且对掩膜进行掩膜沉积及前述光刻操作的过程工艺较为复杂,既延长了生产周期,又进一步提高了生产成本。

43.为解决掩膜黑边界效应对光刻存在影响,从而影响半导体器件性能的问题,本发明提供一种光刻掩膜,该光刻掩膜的图案区域包括第一图案区域和第二图案区域,且第二图案区域位于第一图案区域外侧,第二图案区域的掩膜图案的关键尺寸基于光刻掩膜图案区域的外边界到图案区域的中轴距离,以及距离和尺寸补偿值的对应关系调整得到。

44.进一步地,为解决掩膜黑边界效应对光刻存在影响,从而影响半导体器件性能的问题,本发明提供一种区别于现有技术的有效减小极紫外掩膜黑边界效应的方法,具体地,如图4所示,包括:

45.步骤s1:提供光刻掩膜;

46.步骤s2:得到光刻掩膜图案区域的外边界到图案区域中轴的距离,得到距离和尺寸补偿值的对应关系;其中,图案区域包括第一图案区域和第二图案区域,第二图案区域位于第一图案区域的外周侧;

47.步骤s3:根据距离确定尺寸补偿值,并根据尺寸补偿值至少对第二图案区域内的掩膜图案进行补偿,得到修正光刻掩膜,并使修正光刻掩膜的关键尺寸被调整至预设值内;

48.步骤s4:基于修正光刻掩膜进行光刻。

49.上述方法可以对第二图案区域内的掩膜图案的关键尺寸进行补偿,从而不会使得第二图案区域造成掩膜黑边界效应。

50.为使本发明的目的、技术方案和优点更加清楚,下面将结合附图对本发明的实施方式作进一步地详细描述。

51.在本实施例中,光刻掩膜4包括第一图案区域11和第二图案区域12,第二图案区域12位于第一图案区域11的外周侧,第二图案区域12会造成背景技术中所说的掩膜黑边界效应。

52.如图5所示为根据仿真得到的一种掩膜的距离x与关键尺寸cd的函数关系图,其中,横坐标为x为光刻掩膜4的图案区域1的外边界到图案区域1中轴的距离,单位为纳米nm。纵坐标为关键尺寸cd,单位为纳米nm。当距离在0-200nm之间时,关键尺寸为39nm;当距离在200nm-400nm之间时,关键尺寸在39nm到38nm之间,且随着距离的增大,关键尺寸减小,在距离约为370nm,关键尺寸为38.5;当距离在400nm以上时,关键尺寸约为38nm,由此可知距离

会影响关键尺寸,因此可以通过拟合关键尺寸与外边界到图案区域1中轴距离的趋势关系,得到距离和尺寸补偿值的对应关系。

53.本实施例提供的有效减小极紫外掩膜黑边界效应的方法,首先通过测试光罩需要得到光刻掩膜4的图案区域1的外边界到图案区域1中轴的距离,并大量收集的第二图案区域12中待补偿的初始关键尺寸,通过拟合收集到的初始关键尺寸与外边界到图案区域1中轴距离的趋势关系,得到距离和尺寸补偿值的对应关系。

54.然后,根据上述距离与距离和尺寸补偿值的对应关系确定尺寸补偿值,并根据尺寸补偿值对第二图案区域12内的掩膜图案进行补偿,以调整掩膜图案的关键尺寸。

55.具体需要根据如下公式进行补偿后的掩膜图案的关键尺寸:cd2=cd1

△

cd。其中,cd1为掩膜图案的初始关键尺寸,cd2为进行补偿后的掩膜图案的关键尺寸,

△

cd为尺寸补偿值。即补偿后的掩膜图案的尺寸为初始关键尺寸加上尺寸补偿值。

56.掩膜图案的初始关键尺寸根据半导体器件的关键尺寸决定,本实施例不做限定。而掩膜图案的尺寸补偿值

△

cd与距离的对应关系具体见下式:

[0057][0058]

其中,x为光刻掩膜4的图案区域1的外边界到图案区域1中轴的距离。l1和l2为关于x的两个阈值,l1为第一阈值,l2为第二阈值。

[0059]

需要说明的是,本技术中,光刻掩膜4的图案区域1的外边界到图案区域1中轴的距离x如图7所示,若边界为b1或b2,则其对应的中轴为x轴,若边界为b3或b4,则其对应的中轴为y轴。

[0060]

当距离大于零且小于第一阈值时,

△

cd=a,a为任意常数;

[0061]

当距离大于第一阈值且小于第二阈值时,其中c、x0、μ均为任意常数。

[0062]

当距离大于第二阈值时,

△

cd=b,b为任意常数。

[0063]

上述a、b、c、x0、μ、第一阈值l1、第二阈值l2均为根据初始关键尺寸和/或距离确定的常数。也就是说,上述数值均可以根据初始关键尺寸确定,还可以根据距离确定,当然也可以根据距离和初始关键尺寸共同确定。

[0064]

如图7所示,在本实施例中,掩膜图案包括多个间隔设置的子图案21,调整掩膜图案的关键尺寸包括以下几种方法:

[0065]

第一种,减少至少一个子图案21的关键尺寸,且减少的尺寸为|

△

cd|;

[0066]

第二种,增大至少两个相邻的子图案21之间的子图案间隙22的关键尺寸;

[0067]

第三种,减小至少一个子图案21的关键尺寸,同时增大至少两个相邻的子图案21之间的子图案间隙22的关键尺寸;

[0068]

第四种,增大子图案21与第一图案区域11内的子图案21之间的子图案间隙22的关键尺寸;

[0069]

第五种,减小至少一个子图案21的关键尺寸,同时增大子图案21与第一图案区域11内的子图案21之间的子图案间隙22的关键尺寸;

[0070]

第六种,减小至少一个子图案21的关键尺寸,同时增大至少两个相邻的子图案21之间的子图案间隙22的关键尺寸,并增大子图案21与第一图案区域11内的子图案21之间的子图案间隙22的关键尺寸。

[0071]

需要理解的是,通过减小子图案11的关键尺寸和增大图案间隙22的关键尺寸对掩膜进行调整后,皆可以使得光刻光线在晶圆工作台34上形成的光刻区域的尺寸为目标光刻尺寸,以有效减小极紫外掩膜黑边界效应带来的影响。

[0072]

本实施例中,图案区域1的形状包括圆形、椭圆形或多边形。

[0073]

优选地,图案区域1的形状为矩形。

[0074]

如图5所示,当图案区域1的形状为矩形时,根据尺寸补偿值调整掩膜图案的关键尺寸包括:将第二图案区域12周侧划分为四条边和四个角,在四条边和四个角处分别根据尺寸补偿值

△

cd对掩膜图案进行补偿,以调整掩膜图案的关键尺寸。

[0075]

具体的,可以分为上、下、左、右四条边和左上角、左下角、右上角和右下角四个角。每次可以仅调整相对应的两条边,或者对四条边均进行调整。相对的两条边是指左右相对和上下相对。而调整角时,则是仅对相邻的两个角进行调整,或者对四个角皆进行调整。

[0076]

且图5中用多边形框出来的部分即为上、下、左、右四条边和左上角、左下角、右上角和右下角四个角。

[0077]

如图7所示,内框所示出的即为光刻掩膜4的图案区域1的第一图案区域11的外边界,外框所示的即为第二图案区域12的外边界。图7右侧部分为对第二图案区域12的放大结构示意图,其中,第二图案区域12内形成有间隔设置的子图案21,相邻子图案21之间形成有子图案间隙22。

[0078]

对第二图案区域12内的掩膜图案进行补偿,根据补偿后的光刻掩膜4进行光刻就可以有效减小极紫外掩膜黑边界效应。

[0079]

采用上述方案,根据距离与距离和尺寸补偿值的对应关系确定尺寸补偿值,并根据尺寸补偿值对掩膜的第二图案区域内的掩膜图案进行补偿以调整该掩膜图案的关键尺寸,使得第二图案区域内的掩膜图案的关键尺寸被补偿,在后续进行光刻的时候,可以有效地减小掩膜黑边界效应对光刻带来的影响,使得半导体器件的关键尺寸保持在预设的范围内,有效地提升了半导体器件的性能。

[0080]

本实施例还提供一种掩膜的关键尺寸的调整方法。具体的,如图5至图7所示。

[0081]

首先,得到光刻掩膜4的图案区域1的外边界到图案区域1中轴的距离;其中,图案区域1包括第一图案区域11和第二图案区域12,第二图案区域12位于第一图案区域11的外周侧;

[0082]

然后,根据距离与距离和尺寸补偿值的对应关系确定尺寸补偿值,并根据尺寸补偿值对第二图案区域12内的掩膜图案进行补偿以调整掩膜图案的关键尺寸。

[0083]

其中,尺寸补偿值的确定与上述有效减小极紫外掩膜黑边界效应的方法中,尺寸补偿值的确定方法相同,在此不再赘述。

[0084]

本实施例还提供一种掩膜,掩膜的图案区域1包括第一图案区域11和第二图案区域12,第二图案区域12位于第一图案区域11的外周侧;该掩膜的第二图案区域12的关键尺

寸由如上的掩膜的关键尺寸的调整方法调整得到。

[0085]

本实施例提供的掩膜及掩膜的关键尺寸的调整方法,可以使得得到的掩膜在光刻处理过程中,有效地有效减小极紫外掩膜黑边界效应带来的影响,从而提高半导体器件的性能。

[0086]

虽然通过参照本发明的某些优选实施方式,已经对本发明进行了图示和描述,但本领域的普通技术人员应该明白,以上内容是结合具体的实施方式对本发明所作的进一步详细说明,不能认定本发明的具体实施只局限于这些说明。本领域技术人员可以在形式上和细节上对其作各种改变,包括做出若干简单推演或替换,而不偏离本发明的精神和范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。