一种实现glonass三频新体制信号接收的基带电路结构及其方法

技术领域

1.本发明涉及测量测试技术领域,具体涉及一种实现glonass三频新体制信号接收的基带电路结构及其方法。

背景技术:

2.glonass(global navigation satellite system)是最初由苏联开发的卫星导航系统,于1982年10月开始飞行试验,苏联解体后由俄罗斯联邦继承。1996年,glonass星座首次达到额定工作的24颗。由于经济危机和卫星寿命过短,到2002年,下降到7颗卫星,正常工作6颗。随后的2003年glonass开始发射glonass-m卫星,系统状态随之改善。从2011年开始,glonass新发射的glonass-k1卫星开始增加l3oc民用新体制卫星导航信号,后来由于国际形势问题,俄罗斯受到美国的禁运的影响,后续发射卫星类型恢复为glonass-m,但都搭载了l3oc测试载核。glonass计划在未来的glonass-k2卫星上增加l1oc和l2oc两个新体制民用信号,其中l2oc仅导频信号公开。glonass于2016年公开了上述三个民用新体制信号的接口控制文件。

3.l1oc信号载波频率(标称值)为1600.995mhz,由相同功率的两个分量构成:l1ocd(数据分量)和l1ocp(导频分量)构成。这些分量通过逐码片时分复用两个伪随机噪声序列(prn)实现。l1ocd信号的调制序列是将码流时钟为0.5115mhz的伪码,时钟为500sps的二级码(oc1)符号流,和时钟为250sps的卷积编码符号流进行异或求和。l1ocp信号的符号调制序列是将码流时钟为0.5115mhz伪码和时钟为2.046mhz的曲流序列(ms)副载波进行异或求和。

4.ms是一个0101周期性序列,与伪码码片同步,ms意图为l1ocp分量构成boc(1,1)的谱。也就是说l1oc信号的功率谱相当于是一个中心频点在1600.995mhz附近的一个boc(1,1)信号。

5.l2oc信号载波频率(标称值)为1248.06mhz,信号体制与l1oc相同,区别在于仅允许访问l2ocp,码长为n=10230且周期t=20ms的gold序列。

6.l3oc信号载波频率(标称值)为1202.025mhz由相同功率的两个bpsk(10)分量构成:l3ocd(数据分量)和l3ocp(导频分量)。这些信号分量彼此相位正交,也就是l3ocd延迟90

°

。

7.上述的信号体制不能和glonass传统的fdma信号l1of和l2of相兼容,同常见的北斗、gps和galileo信号体制也存在不同,这样就为glonass三频新体制信号应用技术的大规模普及应用带来了一定的障碍。

技术实现要素:

8.本发明是为了解决glonass三频新体制信号应用的问题,提供一种实现glonass三频新体制信号接收的基带电路结构及其方法,包括l1oc、l2oc和l3oc三个频点,采用对于导

频信号分量的跟踪处理来实现整个频点信号的跟踪,仅使用一个相关器解调数据通道的导航电文,以较低的资源消耗实现了该频点信号的接收处理,电路结构简单,显著节约了电路面积;采用bump-jump技术防止l1ocp和l2ocp信号错锁在副峰上,工作性能稳定可靠;采用电路和cpu组合的软件无线电实现方案,具有配置重构方便的优点,适用范围广泛。

9.本发明提供一种实现glonass三频新体制信号接收的基带电路结构,包括依次连接的天线、低噪声放大器、功分器、射频信道组、模数转换装置组、数字前端电路、信号跟踪处理电路组、cpu和与功分器的输出端电连接的l1of/l2of处理电路,l1of/l2of处理电路与cpu电连接;

10.天线用于接收空间中传播的卫星导航信号电磁波转换为射频电信号并输出至低噪声放大器,低噪声放大器用于接收射频电信号并放大后输出至功分器,功分器用于将射频电信号分路后输出至射频信道组和l1of/l2of处理电路,射频信道组用于接收射频电信号并下变频为模拟基带信号并输出至模数转换装置组,模数转换装置组用于接收模拟基带信号并进行模数转换生成数字基带信号并输出至数字前端电路,数字前端电路用于接收数字基带信号并进行预处理、自动增益控制和压缩后输出至信号跟踪处理电路组,信号跟踪处理电路组用于接收数字基带信号并通过运算获得信号积分值和信号原始观测量输出至cpu,cpu用于接收信号积分值和信号原始观测量并获取码和载波的nco控制字写入信号跟踪处理电路组,l1of/l2of处理电路用于接收功分器输出的射频电信号利用glonass的传统信号解调电文获取卫星prn号、载波多普勒和大致的发射时间整秒点输出至信号跟踪处理电路组和cpu。

11.本发明提供一种实现glonass三频新体制信号接收的基带电路结构,作为优选方式,射频信道组包括并联设置的l1oc射频信道、l2oc射频信道和l3oc射频信道,模数转换装置组包括与l1oc射频信道的输出端电连接的第一模数转换装置、与l2oc射频信道的输出端电连接的第二模数转换装置和与l3oc射频信道的输出端电连接的第三模数转换装置,信号跟踪处理电路组包括并列设置的l1oc信号跟踪处理电路、l2ocp信号跟踪处理电路和l3oc信号跟踪处理电路,l1oc信号跟踪处理电路的输入端、l2ocp信号跟踪处理电路的输入端和l3oc信号跟踪处理电路的输入端均与数字前端电路的输出端电连接,l1oc信号跟踪处理电路的输出端、l2ocp信号跟踪处理电路的输出端和l3oc信号跟踪处理电路的输出端均与cpu电连接,l1of/l2of处理电路的输出端与l1oc信号跟踪处理电路的输入端、l2ocp信号跟踪处理电路的输入端和l3oc信号跟踪处理电路的输入端均电连接;

12.数字前端电路用于接收数字基带信号进行抗干扰滤波、信号预处理、agc并将数据位压缩到1~4bit生成l1oc i数字基带信号、l1oc q数字基带信号、l2oc i数字基带信号、l2oc q数字基带信号、l3oc i数字基带信号和l3oc q数字基带信号,数字前端电路用于将l1oc i数字基带信号和l1oc q数字基带信号输出至l1oc信号跟踪处理电路,数字前端电路用于将l2oc i数字基带信号和l2oc q数字基带信号输出至l2ocp信号跟踪处理电路,数字前端电路用于将l3oc i数字基带信号和l3oc q数字基带信号输出至l3oc信号跟踪处理电路。

13.本发明提供一种实现glonass三频新体制信号接收的基带电路结构,作为优选方式,l1oc信号跟踪处理电路包括依次电连接的l1oc载波nco、l1oc混频器,l1ocp码产生器,与l1oc混频器的输出端、l1ocp码产生器的输出端均电连接的l1ocp码相关器组,依次电连

接的l1oc码nco、l1ocd码产生器、l1ocd码相关器和设置在l1oc码nco与l1ocd码相关器之间的l1oc时分按复用信号产生器,l1oc载波nco的输入端和l1oc码nco的输入端与均cpu的输出端电连接,l1oc混频器的输入端与数字前端电路的输出端电连接,l1ocp码产生器输入端和l1ocd码产生器的输入端均与l1of/l2of处理电路的输出端电连接,l1ocp码相关器组的输出端和l1ocd码相关器的输出端均与cpu电连接,l1oc混频器的输出端与l1ocd码相关器的输入端电连接,l1oc混频器与l1ocp码相关器组之间设置乘法器,l1oc时分复用信号产生器与l1ocd码相关器之间设置反相器;

14.l2ocp信号跟踪处理电路包括依次电连接的l2oc载波nco、l2oc混频器、l2ocp码相关器组,l2oc码nco和与l2oc码nco的输出端分别电连接的l2ocp码产生器、l2oc时分复用信号产生器,l2oc载波nco的输入端和l2oc码nco的输入端均与cpu的输出端电连接,l2oc混频器的输入端与数字前端电路的输出端电连接,l2oc时分复用信号产生器的输出端与l2ocp码相关器组的输入端电连接,l2ocp码相关器组的输出端与cpu的输入端电连接,l2ocp码产生器的输入端与l1of/l2of处理电路的输出端电连接;

15.l3oc信号跟踪处理电路包括依次电连接的l3oc载波nco、l3oc混频器,l3ocp码产生器,与l3oc混频器的输出端、l3ocp码产生器的输出端均电连接的l3ocp码相关器组和依次电连接的l3oc码nco、l3ocd码产生器、l3ocd码相关器,l3oc码nco的输出端与l3ocp码产生器的输入端电连接,l3ocp码相关器组的输出端和l3ocd码相关器的输出端均与cpu电连接,l3oc混频器的输入端与l1of/l2of处理电路的输出端电连接;

16.cpu用于读取l1ocp码相关器组、l1ocd码相关器、l2ocp码相关器组、l3ocp码相关器组和l3ocd码相关器输出的相关值和对应的相位输出值;

17.l1of/l2of处理电路包括用于实现rtl的fpga或asic。

18.本发明提供一种实现glonass三频新体制信号接收的基带电路结构,作为优选方式,l1oc载波nco包括加法器和寄存器,l1oc载波nco用于在cpu的控制下复现本地载波时钟,cpu用于通过查找表获得iq两路正交的本地载波复现信号并输出至l1oc载波nco;

19.l1oc混频器为差频正交下变频;

20.l1ocp码产生器分别生成ve延迟伪随机码、e延迟伪随机码、p延迟伪随机码、l延迟伪随机码、vl延迟伪随机码、ve副载波码片、e副载波码片、p副载波码片、l副载波码片和vl副载波码片,延迟的间距为0.1chip到1chip之间;

21.l1ocp码相关器组包括各带有一个使能端的ve-i相关器、e-i相关器、p-i相关器、l-i相关器、vl-i相关器、ve-q相关器、e-q相关器、p-q相关器、l-q相关器和vl-q相关器;

22.l1ocd码相关器包括将i支路采样信号和l1ocd码进行运算且带有一个使能端的相关器;

23.l1oc时分复用信号产生器由l1oc码nco驱动并产生l1oc tddm时分复用使能信号,l1oc tddm时分复用使能信号包括ve延迟副本、e延迟副本、p延迟副本、l延迟副本和vl延迟副本,延迟的间距在0.1chip到1chip之间;

24.本发明提供一种实现glonass三频新体制信号接收的基带电路结构,作为优选方式,l2oc载波nco包括加法器和寄存器,l2oc载波nco用于在cpu的控制下复现本地载波时钟,cpu用于通过查找表获得iq两路正交的本地载波复现信号并输出至l1oc载波nco;

25.l2ocp码相关器组包括各带有一个使能端的ve-i相关器、e-i相关器、p-i相关器、

l-i相关器、vl-i相关器、ve-q相关器、e-q相关器、p-q相关器、l-q相关器和vl-q相关器;

26.l2oc时分复用信号产生器由l2oc码nco驱动并产生l2oc tddm时分复用使能信号,l2octddm时分复用使能信号包括ve延迟副本、e延迟副本、p延迟副本、l延迟副本和vl延迟副本,延迟的间距在0.1chip到1chip之间。

27.本发明提供一种实现glonass三频新体制信号接收的基带电路结构,作为优选方式,l3oc载波nco包括加法器和寄存器,l3oc载波nco用于在cpu的控制下复现本地载波时钟,cpu用于通过查找表获得iq两路正交的本地载波复现信号并输出至l1oc载波nco;

28.l3ocp码产生器用于生成e延迟码、p延迟码和l延迟码,延迟的间距在0.1chip到1chip之间;

29.l3ocd码相关器包括将q支路采样信号和l3ocd码进行运算的相关器。

30.本发明提供一种实现glonass三频新体制信号接收的方法,包括如下步骤:

31.s1、l1of/l2of处理电路利用glonass的传统信号解调电文,获取卫星prn号、载波多普勒和大致的发射时间整秒点,引导捕获l1ocp信号;

32.s2、l1ocp信号达到同步之后,利用l1ocp码相关器组中ve-i相关器、p-i相关器、vl-i相关器、ve-q相关器、p-q相关器和vl-q相关器获得l1ocp相关值并进行bump-jump峰跳检测消除副峰假锁;

33.s3、l1ocp信号达到同步并消除副峰之后,l1ocd码相关器生成l1ocd相关值输出至cpu,cpu读取l1ocd相关值与i支路采样信号并运算获取l1oc导航电文;

34.s4、cpu对l1oc导航电文进行位同步和帧同步处理,实现帧同步之后将整帧电文进行维特比译码,将译码结果进行解析获取l1oc导航参数并由达到帧同步后的观测量获得l1oc伪距实现定位导航;

35.s5、l1of/l2of处理电路利用glonass的传统信号解调电文获取卫星prn号、载波多普勒和大致的发射时间整秒点,引导捕获l2ocp信号;

36.s6、l2ocp达到同步之后,利用l2ocp码相关器组中ve-i相关器、p-i相关器、vl-i相关器、ve-q相关器、p-q相关器和vl-q相关器的相关值进行bump-jump峰跳检测消除副峰假锁;

37.s7、l2ocp信号达到同步并消除副峰之后l2ocp码相关器组生成l2ocp相关值数组输出至cpu,cpu读取l2ocp码与i支路的相关值,获取二级码,通过二级码同步获取整秒级的发射时间生成独立的伪距观测量;

38.s8、l1of/l2of处理电路利用glonass的传统信号解调电文获取卫星prn号、载波多普勒和大致的发射时间整秒点,引导捕获l3ocp信号;

39.s9、l3ocp信号达到同步之后,cpu对l3ocd导航电文进行位同步和帧同步处理,实现帧同步之后将整帧电文进行维特比译码,将译码结果进行解析获取l3oc导航参数并由达到帧同步后的观测量获得l3oc伪距,glonass三频新体制信号接收完毕。

40.本发明所述的一种实现glonass三频新体制信号接收的方法,作为优选方式,步骤s2包括:

41.s21、l1ocp信号同步:l1oc载波nco在cpu的控制下产生与l1oc基带信号同步的本地载波,本地载波包括i路本地载波和q路本地载波,i路本地载波和q路本地载波为正交、同频且相位相差90

°

;

42.l1oc混频器将数字前端电路输出的l1oc i数字基带信号、l1oc q数字基带信号与i路本地载波、q路本地载波进行正交下变频、剥离载波信号生成l1oc ii信号和l1oc qq信号,l1oc ii信号和l1oc qq信号经乘法器后输出至l1ocp码相关器组;

43.l1oc码nco在cpu的控制下产生基频为2.046mhz的l1oc副载波时钟分别输出至l1ocp码产生器和l1ocd码产生器,l1oc码nco对l1oc副载波时钟进行二分频后得到基频为1.023mhz的l1oc tddm时钟输出至l1oc时分复用信号产生器,l1oc tddm时钟驱动l1oc时分复用信号产生器产生l1oc tddm信号通过反相器后输出至l1ocd码相关器;

44.l1ocp码产生器和l1ocd码产生器分别接收l1oc副载波时钟生成基频为1.023mhz的方波副载波、再进行二分频得到基频为0.5115mhz的l1oc码时钟,l1oc码时钟驱动l1ocp码产生器中长度为n=4092的截短kasami序列电路生成l1ocp码,l1ocp码与方波副载波相乘获得l1ocp本地复现码输出至l1ocp码相关器组,l1ocp信号达到同步;

45.s22、消除副峰假锁:l1oc ii信号、l1oc qq信号、l1oc tddm信号输入l1ocp码相关器组,利用l1ocp码相关器组中ve-i相关器、p-i相关器、vl-i相关器、ve-q相关器、p-q相关器和vl-q相关器并进行bump-jump峰跳检测消除副峰假锁,获得l1ocp相关值数组输出至cpu;

46.步骤s3包括以下步骤:

47.s31、l1ocd相关值输出:l1ocd码相关器生成l1ocd相关值输出至cpu的具体方法为:l1oc码时钟驱动l1ocd码产生器中n=1023的gold序列电路生成l1ocd码,l1ocd码与方波副载波相乘获得l1ocd本地复现码输出至l1ocd码相关器,l1oc ii信号和经过反相器的l1oc tddm信号输入至l1ocd码相关器进行积分操作,获得l1ocd相关值输出至cpu;

48.s32、获取l1oc导航电文:cpu读取l1ocd相关值与i支路采样信号并运算获取l1oc导航电文。

49.本发明所述的一种实现glonass三频新体制信号接收的方法,作为优选方式,步骤s6包括:

50.s61、l2ocp同步:l2oc码nco产生基频为2.046mhz的l2oc副载波时钟,l2oc副载波时钟驱动l2ocp码产生器进行二分频后得到基频为1.023mhz的l2oc tddm时钟,l2oc tddm时钟驱动l2oc时分复用信号产生器产生l2oc tddm信号输出至l2ocp码相关器组;

51.l2ocp码产生器接收l2oc副载波时钟生成基频为1.023mhz的方波副载波,再将方波副载波进行二分频得到基频为0.5115mhz的l2oc码时钟,l2oc码时钟驱动长度为n=10230的gold序列电路生成l2ocp码,l2ocp码与方波副载波相乘获得l2ocp本地复现码输出至l2ocp码相关器组;

52.s62、消除副峰假锁:l2ocp码相关器组中ve-i相关器、p-i相关器、vl-i相关器、ve-q相关器、p-q相关器和vl-q相关器利用相关值对l2oc ii信号、l2oc qq信号、l2ocp本地复现码、l2oc tddm信号进行bump-jump峰跳检测消除副峰假锁,获得l2ocp相关值数组输出至cpu。

53.本发明所述的一种实现glonass三频新体制信号接收的方法,作为优选方式,步骤s9包括:

54.s91、l3ocp信号同步:l3oc码nco产生基频为10.23mhz的l3oc码时钟,l3oc码时钟驱动l3ocp码产生器和l3ocd码产生器获得l3ocp本地复现码和l3ocd本地复现码;

55.经过载波和码剥离的正交中频信号l3oc ii信号、l3oc qq信号输入l3ocp码相关器组,进行积分操作获得l3ocp相关值数组输出至cpu,l3ocp信号达到同步;

56.s92、获得l3ocd相关值:l3ocd码相关器将经过载波剥离的中频信号l3oc qq信号和l3ocd码进行积分操作,获得l3ocd相关值输出至cpu;

57.s93、获取l3oc导航参数:cpu对l3ocd导航电文进行位同步和帧同步处理,实现帧同步之后将整帧电文进行维特比译码,将译码结果进行解析获取l3oc导航参数并由达到帧同步后的观测量获得l3oc伪距,glonass三频新体制信号接收完毕。

58.一种实现glonass三频新体制信号接收的基带电路结构,包括数字前端电路和多个卫星跟踪处理通道,的卫星跟踪通道数量与所跟踪的卫星数量一致,每个卫星跟踪处理通道均包含l1oc信号跟踪处理电路、l2ocp信号跟踪处理电路和l3oc信号跟踪处理电路,的数字前端电路实现对输入采样信号的预处理、自动增益控制和1~4bit压缩,且的数字前端电路分别通过的l1oc信号跟踪处理电路、l2ocp信号跟踪处理电路和l3oc信号跟踪处理电路与该接收机的cpu内核相联接,其特征在于,的l1oc信号跟踪处理电路包括l1oc载波nco、l1oc混频器、l1ocp码产生器、l1ocp码相关器组、l1ocd码产生器、l1ocd码相关器、l1oc码nco、l1oc时分复用信号产生器,的l2oc信号跟踪处理电路包括l2oc载波nco、l2oc混频器、l2ocp码产生器、l2ocp码相关器组、l2oc码nco、l2oc时分复用信号产生器,的l3oc信号跟踪处理电路包括l3oc载波nco、l3oc混频器、l3ocp码产生器、l3ocp码相关器组、l3ocd码产生器、l3ocd码相关器、l3oc码nco、l3oc时分复用信号产生器。

59.电路rtl可在fpga或asic中实现。

60.l1oc载波nco、l2oc载波nco和l3oc载波nco,由一个40bit加法器和寄存器构成,复现本地载波时钟,通过查找表获得iq两路正交的本地载波复现信号,并将载波相位输出到cpu内核。

61.l1oc混频器、l2oc混频器和l3oc混频器是差频正交下变频。

62.l3ocp码产生器生成e、p、l三路延迟码,延迟的间距在0.1chip到1chip之间可设置。

63.l1ocp码产生器和l2ocp码产生器生成ve、e、p、l和vl五路延迟伪随机码和五路副载波码片,共十路本地复现信号,延迟的间距在0.1chip到1chip之间可设置。

64.l1oc时分复用信号产生器和l2oc时分复用信号产生器由各自的码nco驱动,产生对应的tddm时分复用使能信号,该信号由ve、e、p、l和vl五路延迟副本构成,延迟的间距在0.1chip到1chip之间可设置。

65.l1ocp码相关器组和l2ocp码相关器组由ve-i、e-i、p-i、l-i、vl-i、ve-q、e-q、p-q、l-q和vl-q,共十个相关器构成,每个相关器带有一个使能端。

66.l1ocd码相关器由i支路采样信号和l1ocd码进行运算的相关器构成,相关器带有一个使能端。

67.l3ocd码相关器由q支路采样信号和l3ocd码进行运算的相关器构成。

68.cpu内核可以直接读取l1ocp码相关器、l1ocd码相关器、l2ocp码相关器、l3ocd码相关器和l3ocp码相关器的相关值,以及对应的相位输出值。

69.本发明卫星导航信号由天线、低噪声放大器、功分器、l1oc射频信道、l2oc射频信道、l3oc射频信道、频标电路、adc、数字前端电路、l1oc信号跟踪处理电路、l2ocp信号跟踪

处理电路、l3oc信号跟踪处理电路和cpu内核组成。

70.天线将空间中传播的卫星导航信号电磁波转换为射频电信号,经过低噪声放大器将射频电信号的幅度放大,经过放大后的射频电信号通过功分器分成三路,分别送入l1oc射频信道、l2oc射频信道和l3oc射频信道。三路射频信道采用同一个频标电路输出的频标参考信号。三路射频信道将各自频段的射频信号下变频为模拟基带信号。三路模拟基带信号分别通过adc转换为数字基带信号,数字基带信号经过数字前端电路进行预处理、自动增益控制和1~4bit压缩,然后分别输入l1oc信号跟踪处理电路、l2ocp信号跟踪处理电路和l3oc信号跟踪处理电路,三路信号跟踪处理电路通过运算获得信号积分值和信号的原始观测量,这些数值由cpu内核读取进行处理,获取三路码和载波的nco控制字,写入信号跟踪处理电路。原始观测量可用于进行下一步导航信息处理。

71.glonass三频新体制信号接收通道电路包括载波nco、混频器、l1ocp码相关器组、l1ocd码相关器、l1oc码nco、l1ocp码产生器、l1ocd码产生器、l1oc时分复用信号产生器、l2oc码nco、l2ocp码产生器、l2ocp码相关器组、l2oc时分复用信号产生器、l3oc码nco、l3ocd码产生器、l3ocp码产生器、l3ocd码相关器、l3ocp码相关器组,各模块的具体功能如下:

72.载波nco用于产生与l1oc、l2oc和l3oc基带信号同步的本地载波,本地载波包括正交的i和q两部分,iq二者同频,相位相差90

°

。

73.混频器用于将经过压缩的iq两路数字基带信号和正交的iq两部分载波进行正交下变频,用于载波信号剥离。

74.l1oc码nco用于产生基频为2.046mhz的l1oc副载波时钟,驱动l1ocp码产生器和l1ocd码产生器,对l1oc副载波时钟进行二分频后得到基频为1.023mhz的l1oc tddm时钟驱动l1oc时分复用信号产生器产生l1oc tddm信号。

75.l1ocp码产生器和l1ocd码产生器分别接收基频为2.046mhz的l1oc副载波时钟,生成基频为1.023mhz的方波副载波,再进行二分频,得到基频为0.5115mhz的l1oc码时钟,l1oc码时钟用于驱动是长度为n=4092的截短kasami序列电路生成l1ocp码,驱动n=1023的gold序列电路生成l1ocd码,l1ocp码和l1ocd码分别与基频为1.023mhz的方波副载波相乘,获得l1ocp本地复现码和l1ocd本地复现码。

76.经过载波剥离的正交中频信号l1oc ii、l1oc qq和l1oc tddm信号输入l1ocp码相关器组,进行积分操作,获得l1ocp相关值数组。

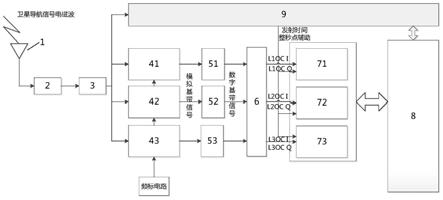

77.经过载波剥离的中频信号l1oc ii和经过反相器的l1oc tddm信号输入l1ocd码相关器,进行积分操作,获得l1ocd相关值。

78.l2oc码nco用于产生基频为2.046mhz的l2oc副载波时钟,驱动l2ocp码产生器,对l2oc副载波时钟进行二分频后得到基频为1.023mhz的l2oc tddm时钟驱动l2oc时分复用信号产生器产生l2oc tddm信号。

79.l2ocp码产生器接收基频为2.046mhz的l2oc副载波时钟,生成基频为1.023mhz的方波副载波,再进行二分频,得到基频为0.5115mhz的l2oc码时钟,l2oc码时钟用于驱动是长度为n=10230的gold序列电路生成l2ocp码,l2ocp码与基频为1.023mhz的方波副载波相乘,获得l2ocp本地复现码。

80.经过载波剥离的正交中频信号l2oc ii、l2oc qq和l2oc tddm信号输入l2ocp码相

关器组,进行积分操作,获得l2ocp相关值数组。

81.l3oc码nco用于产生基频为10.23mhz的l3oc码时钟,驱动l3ocp码产生器和l3ocd码产生器,获得l3ocp本地复现码和l3ocd本地复现码。

82.经过载波和码剥离的正交中频信号l3oc ii、l3oc qq输入l3ocp码相关器组,进行积分操作,获得l3ocp相关值数组。

83.经过载波剥离的中频信号l3oc qq和l3ocd码进行积分操作,获得l3ocd相关值。

84.如图三所示为本发明l1ocp相关器组和l2ocp相关器组电路的结构示意图,由ve-i、e-i、p-i、l-i、vl-i、ve-q、e-q、p-q、l-q和vl-q,共十个相关器构成,每个相关器带有一个使能端。

85.本发明具有以下优点:

86.(1)、本发明创新设计了一种能够实现glonass三频新体制信号接收处理系统,包括l1oc、l2oc和l3oc三个频点,其中l1oc和l2oc采用的tddm boc(1,1)信号体制不能由其它系统或传统的信号系统接收处理,本发明能够完全匹配信号体制,充分发挥信号体制的优势;

87.(2)、本发明提供的glonass三频新体制信号接收处理系统,采用对于导频信号分量的跟踪处理来实现整个频点信号的跟踪,仅使用一个相关器解调数据通道的导航电文,以较低的资源消耗实现了该频点信号的接收处理,电路结构简单,显著节约了电路面积;

88.(3)、本发明提供的glonass三频新体制信号接收处理系统,采用bump-jump技术防止l1ocp和l2ocp信号错锁在副峰上,工作性能稳定可靠;

89.(4)、本发明提供的glonass三频新体制信号接收处理系统采用电路和cpu组合的软件无线电实现方案,具有配置重构方便的优点,适用范围广泛。

附图说明

90.图1为一种实现glonass三频新体制信号接收的基带电路结构接收处理系统结构示意图;

91.图2为一种实现glonass三频新体制信号接收的基带电路结构接收通道电路的结构示意图;

92.图3为一种实现glonass三频新体制信号接收的基带电路结构l1ocp相关器组和l2ocp相关器组电路的结构示意图;

93.图4为一种实现glonass三频新体制信号接收的方法l1oc信号接收处理方法流程图;

94.图5为一种实现glonass三频新体制信号接收的方法l2oc信号接收处理方法流程图;

95.图6为一种实现glonass三频新体制信号接收的方法l1oc信号接收处理方法流程图。

96.附图标记:

97.1、天线;2、低噪声放大器;3、功分器;4、射频信道组;41、l1oc射频信道;42、l2oc射频信道;43、l3oc射频信道;5、模数转换装置组;51、第一模数转换装置;52、第二模数转换装置;53、第三模数转换装置;6、数字前端电路;7、信号跟踪处理电路组;71、l1oc信号跟踪处

理电路;711、l1oc载波nco;712、l1oc混频器;713、l1ocp码产生器;714、l1ocp码相关器组;715、l1oc码nco;716、l1ocd码产生器;717、l1ocd码相关器;718、l1oc时分复用信号产生器;72、l2ocp信号跟踪处理电路;721、l2oc载波nco;722、l2oc混频器;723、l2ocp码相关器组;724、l2oc码nco;725、l2ocp码产生器;726、l2oc时分复用信号产生器;73、l3oc信号跟踪处理电路;731、l3oc载波nco;732、l3oc混频器;733、l3ocp码产生器;734、l3ocp码相关器组;735、l3oc码nco;736、l3ocd码产生器;737、l3ocd码相关器;8、cpu;9、l1of/l2of处理电路。

具体实施方式

98.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。

99.实施例1

100.如图1所示,一种实现glonass三频新体制信号接收的基带电路结构,包括依次连接的天线1、低噪声放大器2、功分器3、射频信道组4、模数转换装置组5、数字前端电路6、信号跟踪处理电路组7、cpu8和与功分器3的输出端电连接的l1of/l2of处理电路9,l1of/l2of处理电路9与cpu8电连接;

101.天线1用于接收空间中传播的卫星导航信号电磁波转换为射频电信号并输出至低噪声放大器2,低噪声放大器2用于接收射频电信号并放大后输出至功分器3,功分器3用于将射频电信号分路后输出至射频信道组4和l1of/l2of处理电路9,射频信道组4用于接收射频电信号并下变频为模拟基带信号并输出至模数转换装置组5,模数转换装置组5用于接收模拟基带信号并进行模数转换生成数字基带信号并输出至数字前端电路6,数字前端电路6用于接收数字基带信号并进行预处理、自动增益控制和压缩后输出至信号跟踪处理电路组7,信号跟踪处理电路组7用于接收数字基带信号并通过运算获得信号积分值和信号原始观测量输出至cpu8,cpu8用于接收信号积分值和信号原始观测量并获取码和载波的nco控制字写入信号跟踪处理电路组7,l1of/l2of处理电路9用于接收功分器3输出的射频电信号利用glonass的传统信号解调电文获取卫星prn号、载波多普勒和大致的发射时间整秒点输出至信号跟踪处理电路组7和cpu8;

102.射频信道组4包括并联设置的l1oc射频信道41、l2oc射频信道42和l3oc射频信道43,模数转换装置组5包括与l1oc射频信道41的输出端电连接的第一模数转换装置51、与l2oc射频信道42的输出端电连接的第二模数转换装置52和与l3oc射频信道43的输出端电连接的第三模数转换装置53,信号跟踪处理电路组7包括并列设置的l1oc信号跟踪处理电路71、l2ocp信号跟踪处理电路72和l3oc信号跟踪处理电路73,l1oc信号跟踪处理电路71的输入端、l2ocp信号跟踪处理电路72的输入端和l3oc信号跟踪处理电路73的输入端均与数字前端电路6的输出端电连接,l1oc信号跟踪处理电路71的输出端、l2ocp信号跟踪处理电路72的输出端和l3oc信号跟踪处理电路73的输出端均与cpu8电连接,l1of/l2of处理电路9的输出端与l1oc信号跟踪处理电路71的输入端、l2ocp信号跟踪处理电路72的输入端和l3oc信号跟踪处理电路73的输入端均电连接;

103.数字前端电路6用于接收数字基带信号进行抗干扰滤波、信号预处理、agc并将数据位压缩到1~4bit生成l1oc i数字基带信号、l1oc q数字基带信号、l2oc i数字基带信号、l2oc q数字基带信号、l3oc i数字基带信号和l3oc q数字基带信号,数字前端电路6用

于将l1oc i数字基带信号和l1oc q数字基带信号输出至l1oc信号跟踪处理电路71,数字前端电路6用于将l2oc i数字基带信号和l2oc q数字基带信号输出至l2ocp信号跟踪处理电路72,数字前端电路6用于将l3oc i数字基带信号和l3oc q数字基带信号输出至l3oc信号跟踪处理电路73;

104.l1oc信号跟踪处理电路71包括依次电连接的l1oc载波nco711、l1oc混频器712,l1ocp码产生器713,与l1oc混频器712的输出端、l1ocp码产生器713的输出端均电连接的l1ocp码相关器组714,依次电连接的l1oc码nco715、l1ocd码产生器716、l1ocd码相关器717和设置在l1oc码nco715与l1ocd码相关器717之间的l1oc时分按复用信号产生器718,l1oc载波nco711的输入端和l1oc码nco715的输入端与均cpu8的输出端电连接,l1oc混频器712的输入端与数字前端电路6的输出端电连接,l1ocp码产生器713输入端和l1ocd码产生器716的输入端均与l1of/l2of处理电路9的输出端电连接,l1ocp码相关器组714的输出端和l1ocd码相关器717的输出端均与cpu8电连接,l1oc混频器712的输出端与l1ocd码相关器717的输入端电连接,l1oc混频器712与l1ocp码相关器组714之间设置乘法器,l1oc时分复用信号产生器718与l1ocd码相关器717之间设置反相器;

105.l2ocp信号跟踪处理电路72包括依次电连接的l2oc载波nco721、l2oc混频器722、l2ocp码相关器组723,l2oc码nco724和与l2oc码nco724的输出端分别电连接的l2ocp码产生器725、l2oc时分复用信号产生器726,l2oc载波nco721的输入端和l2oc码nco724的输入端均与cpu8的输出端电连接,l2oc混频器722的输入端与数字前端电路6的输出端电连接,l2oc时分复用信号产生器726的输出端与l2ocp码相关器组723的输入端电连接,l2ocp码相关器组723的输出端与cpu8的输入端电连接,l2ocp码产生器725的输入端与l1of/l2of处理电路9的输出端电连接;

106.l3oc信号跟踪处理电路73包括依次电连接的l3oc载波nco731、l3oc混频器732,l3ocp码产生器733,与l3oc混频器732的输出端、l3ocp码产生器733的输出端均电连接的l3ocp码相关器组734和依次电连接的l3oc码nco735、l3ocd码产生器736、l3ocd码相关器737,l3oc码nco735的输出端与l3ocp码产生器733的输入端电连接,l3ocp码相关器组734的输出端和l3ocd码相关器737的输出端均与cpu8电连接,l3oc混频器732的输入端与l1of/l2of处理电路9的输出端电连接;

107.cpu8用于读取l1ocp码相关器组714、l1ocd码相关器717、l2ocp码相关器组723、l3ocp码相关器组734和l3ocd码相关器737输出的相关值和对应的相位输出值;

108.l1of/l2of处理电路9包括用于实现rtl的fpga或asic;

109.l1oc载波nco711包括加法器和寄存器,l1oc载波nco711用于在cpu8的控制下复现本地载波时钟,cpu8用于通过查找表获得iq两路正交的本地载波复现信号并输出至l1oc载波nco711;

110.l1oc混频器712为差频正交下变频;

111.l1ocp码产生器713分别生成ve延迟伪随机码、e延迟伪随机码、p延迟伪随机码、l延迟伪随机码、vl延迟伪随机码、ve副载波码片、e副载波码片、p副载波码片、l副载波码片和vl副载波码片,延迟的间距为0.1chip到1chip之间;

112.l1ocp码相关器组714包括各带有一个使能端的ve-i相关器、e-i相关器、p-i相关器、l-i相关器、vl-i相关器、ve-q相关器、e-q相关器、p-q相关器、l-q相关器和vl-q相关器;

113.l1ocd码相关器717包括将i支路采样信号和l1ocd码进行运算且带有一个使能端的相关器;

114.l1oc时分复用信号产生器718由l1oc码nco715驱动并产生l1oc tddm时分复用使能信号,l1oc tddm时分复用使能信号包括ve延迟副本、e延迟副本、p延迟副本、l延迟副本和vl延迟副本,延迟的间距在0.1chip到1chip之间;

115.l2oc载波nco721包括加法器和寄存器,l2oc载波nco721用于在cpu8的控制下复现本地载波时钟,cpu8用于通过查找表获得iq两路正交的本地载波复现信号并输出至l1oc载波nco721;

116.l2ocp码相关器组723包括各带有一个使能端的ve-i相关器、e-i相关器、p-i相关器、l-i相关器、vl-i相关器、ve-q相关器、e-q相关器、p-q相关器、l-q相关器和vl-q相关器;

117.l2oc时分复用信号产生器726由l2oc码nco724驱动并产生l2oc tddm时分复用使能信号,l2octddm时分复用使能信号包括ve延迟副本、e延迟副本、p延迟副本、l延迟副本和vl延迟副本,延迟的间距在0.1chip到1chip之间;

118.l3oc载波nco731包括加法器和寄存器,l3oc载波nco731用于在cpu8的控制下复现本地载波时钟,cpu8用于通过查找表获得iq两路正交的本地载波复现信号并输出至l1oc载波nco731;

119.l3ocp码产生器733用于生成e延迟码、p延迟码和l延迟码,延迟的间距在0.1chip到1chip之间;

120.l3ocd码相关器737包括将q支路采样信号和l3ocd码进行运算的相关器。

121.如图4所示,一种实现glonass三频新体制信号接收的方法,其特征在于:包括如下步骤:

122.s1、l1of/l2of处理电路9利用glonass的传统信号解调电文,获取卫星prn号、载波多普勒和大致的发射时间整秒点,引导捕获l1ocp信号;

123.s2、l1ocp信号达到同步之后,利用l1ocp码相关器组714中ve-i相关器、p-i相关器、vl-i相关器、ve-q相关器、p-q相关器和vl-q相关器获得l1ocp相关值并进行bump-jump峰跳检测消除副峰假锁;

124.s21、l1ocp信号同步:l1oc载波nco711在cpu8的控制下产生与l1oc基带信号同步的本地载波,本地载波包括i路本地载波和q路本地载波,i路本地载波和q路本地载波为正交、同频且相位相差90

°

;

125.l1oc混频器712将数字前端电路6输出的l1oc i数字基带信号、l1oc q数字基带信号与i路本地载波、q路本地载波进行正交下变频、剥离载波信号生成l1oc ii信号和l1oc qq信号,l1oc ii信号和l1oc qq信号经乘法器后输出至l1ocp码相关器组714;

126.l1oc码nco715在cpu8的控制下产生基频为2.046mhz的l1oc副载波时钟分别输出至l1ocp码产生器713和l1ocd码产生器716,l1oc码nco715对l1oc副载波时钟进行二分频后得到基频为1.023mhz的l1oc tddm时钟输出至l1oc时分复用信号产生器718,l1oc tddm时钟驱动l1oc时分复用信号产生器718产生l1oc tddm信号通过反相器后输出至l1ocd码相关器717;

127.l1ocp码产生器713和l1ocd码产生器716分别接收l1oc副载波时钟生成基频为1.023mhz的方波副载波、再进行二分频得到基频为0.5115mhz的l1oc码时钟,l1oc码时钟驱

动l1ocp码产生器713中长度为n=4092的截短kasami序列电路生成l1ocp码,l1ocp码与方波副载波相乘获得l1ocp本地复现码输出至l1ocp码相关器组714,l1ocp信号达到同步;

128.s22、消除副峰假锁:l1oc ii信号、l1oc qq信号、l1oc tddm信号输入l1ocp码相关器组714,利用l1ocp码相关器组714中ve-i相关器、p-i相关器、vl-i相关器、ve-q相关器、p-q相关器和vl-q相关器并进行bump-jump峰跳检测消除副峰假锁,获得l1ocp相关值数组输出至cpu8;

129.s3、l1ocp信号达到同步并消除副峰之后,l1ocd码相关器717生成l1ocd相关值输出至cpu8,cpu8读取l1ocd相关值与i支路采样信号并运算获取l1oc导航电文;

130.s31、l1ocd相关值输出:l1ocd码相关器717生成l1ocd相关值输出至cpu8的具体方法为:l1oc码时钟驱动l1ocd码产生器716中n=1023的gold序列电路生成l1ocd码,l1ocd码与方波副载波相乘获得l1ocd本地复现码输出至l1ocd码相关器717,l1oc ii信号和经过反相器的l1oc tddm信号输入至l1ocd码相关器717进行积分操作,获得l1ocd相关值输出至cpu8;

131.s32、获取l1oc导航电文:cpu8读取l1ocd相关值与i支路采样信号并运算获取l1oc导航电文;

132.s4、cpu8对l1oc导航电文进行位同步和帧同步处理,实现帧同步之后将整帧电文进行维特比译码,将译码结果进行解析获取l1oc导航参数并由达到帧同步后的观测量获得l1oc伪距实现定位导航;

133.如图5所示,s5、l1of/l2of处理电路9利用glonass的传统信号解调电文获取卫星prn号、载波多普勒和大致的发射时间整秒点,引导捕获l2ocp信号;

134.s6、l2ocp达到同步之后,利用l2ocp码相关器组723中ve-i相关器、p-i相关器、vl-i相关器、ve-q相关器、p-q相关器和vl-q相关器的相关值进行bump-jump峰跳检测消除副峰假锁;

135.s61、l2ocp同步:l2oc码nco724产生基频为2.046mhz的l2oc副载波时钟,l2oc副载波时钟驱动l2ocp码产生器725进行二分频后得到基频为1.023mhz的l2oc tddm时钟,l2oc tddm时钟驱动l2oc时分复用信号产生器726产生l2oc tddm信号输出至l2ocp码相关器组723;

136.l2ocp码产生器725接收l2oc副载波时钟生成基频为1.023mhz的方波副载波,再将方波副载波进行二分频得到基频为0.5115mhz的l2oc码时钟,l2oc码时钟驱动长度为n=10230的gold序列电路生成l2ocp码,l2ocp码与方波副载波相乘获得l2ocp本地复现码输出至l2ocp码相关器组723;

137.s62、消除副峰假锁:l2ocp码相关器组723中ve-i相关器、p-i相关器、vl-i相关器、ve-q相关器、p-q相关器和vl-q相关器利用相关值对l2oc ii信号、l2oc qq信号、l2ocp本地复现码、l2oc tddm信号进行bump-jump峰跳检测消除副峰假锁,获得l2ocp相关值数组输出至cpu8;

138.s7、l2ocp信号达到同步并消除副峰之后l2ocp码相关器组723生成l2ocp相关值数组输出至cpu8,cpu8读取l2ocp码与i支路的相关值,获取二级码,通过二级码同步获取整秒级的发射时间生成独立的伪距观测量;

139.如图6所示,s8、l1of/l2of处理电路9利用glonass的传统信号解调电文获取卫星

prn号、载波多普勒和大致的发射时间整秒点,引导捕获l3ocp信号;

140.s9、l3ocp信号达到同步之后,cpu8对l3ocd导航电文进行位同步和帧同步处理,实现帧同步之后将整帧电文进行维特比译码,将译码结果进行解析获取l3oc导航参数并由达到帧同步后的观测量获得l3oc伪距,glonass三频新体制信号接收完毕;

141.s91、l3ocp信号同步:l3oc码nco735产生基频为10.23mhz的l3oc码时钟,l3oc码时钟驱动l3ocp码产生器733和l3ocd码产生器736获得l3ocp本地复现码和l3ocd本地复现码;

142.经过载波和码剥离的正交中频信号l3oc ii信号、l3oc qq信号输入l3ocp码相关器组734,进行积分操作获得l3ocp相关值数组输出至cpu8,l3ocp信号达到同步;

143.s92、获得l3ocd相关值:l3ocd码相关器737将经过载波剥离的中频信号l3oc qq信号和l3ocd码进行积分操作,获得l3ocd相关值输出至cpu8;

144.s93、获取l3oc导航参数:cpu8对l3ocd导航电文进行位同步和帧同步处理,实现帧同步之后将整帧电文进行维特比译码,将译码结果进行解析获取l3oc导航参数并由达到帧同步后的观测量获得l3oc伪距,glonass三频新体制信号接收完毕。

145.实施例2

146.如图1所示,空间中的卫星导航信号电磁波经天线转化为射频电信号后,经低噪声放大器和功分器后送入常规l1of/l2of处理电路9,对卫星进行捕获跟踪和解调电文,由此获取卫星的卫星号、多普勒和发射时间整秒点辅助,其中卫星号和多普勒由cpu8内核写入,发射时间整秒点辅助直接输入l1oc信号跟踪处理电路71、l2ocp信号跟踪处理电路72和l3oc信号跟踪处理电路73,glonass三频新体制信号接收的跟踪处理电路在cpu8内核的控制下可实现相应信号的捕获和跟踪。glonass三频新体制信号的射频信道,接收功分器分配的射频电信号进行下变频、滤波等处理生成模拟基带信号,模拟基带信号经过adc转换为数字基带信号,此时数字基带信号位数较高,可能在8-14bit之间,而且经常包含有空间中的干扰信号,经由数字前端电路6进行抗干扰滤波、信号预处理、agc等操作,进行数据位压缩到1~4bit,生成三路数字基带信号:l1oc i、l1oc q、l2oc i、l2oc q、l3oc i、l3oc q、输入glonass三频新体制信号接收的跟踪处理电路。

147.如图2所示,l1oc i、l1oc q和l1oc载波nco生成的本地载波信号输入l1oc混频器712,进行差频下变频处理,剥离残余载波,l1oc载波nco711的控制字由cpu8内核置入,l1oc混频器712输出同向分量l1oc ii和正交分量l1oc qq。

148.l1oc码nco715的控制字由cpu8内核置入,生成2.046mhz的副载波时钟和1.023mhz的l1oc tddm时钟。

149.2.046mhz的副载波时钟驱动l1ocp码产生器713生成l1ocp本地复现码,驱动l1ocd码产生器716生成l1ocd本地复现码。

150.同向分量l1oc ii和正交分量l1oc qq与l1ocp本地复现码、l1oc tddm共同进入l1ocp码相关器组714,可以得到l1ocp相关值数组,包括ve-i、e-i、p-i、l-i、vl-i、ve-q、e-q、p-q、l-q和vl-q,共十个相关值数组,由cpu内核读取,进行计算生成l1oc载波和码nco控制字。

151.同向分量l1oc ii与l1ocd本地复现码、l1oc tddm的反相值共同进入l1ocd码相关器717,可以得到l1ocd相关值,由cpu8内核读取获得导航电文。

152.l2oc和l1oc类似,区别仅在于本地复现码不同,而且没有l2ocd码相关器。

153.l3oc码nco735的控制字由cpu8内核置入,生成10.23mhz的码时钟,驱动l3ocp码产生器733生成l3ocp本地复现码,驱动l3ocd码产生器736生成l3ocd本地复现码。

154.同向分量l3oc ii和正交分量l3oc qq与l3ocp本地复现码共同进入l3ocp码相关器组734,可以得到l3ocp相关值数组,包括e-i、p-i、l-i、e-q、p-q和l-q,共六个相关值数组,由cpu内核读取,进行计算生成l3oc载波和码nco控制字。

155.正交分量l3oc qq与l3ocd本地复现码共同进入l3ocd码相关器737,可以得到l3ocd相关值,由cpu8内核读取获得导航电文。

156.本实施例中glonass三频新体制信号接收方法,包括如下步骤:

157.(1)、利用glonass的传统信号l1of或l2of,解调电文,获取卫星prn号、载波多普勒和大致的发射时间整秒点,引导捕获l1ocp信号;

158.(2)、当l1ocp达到同步之后,利用所述的ve-i、p-i、vl-i、ve-q、p-q和vl-q六组相关器的相关值进行bump-jump峰跳检测消除副峰假锁;

159.(3)、当l1ocp达到同步并消除副峰之后,读取l1ocd码与i支路的相关值,获取导航电文;

160.(4)、对l1oc导航电文进行位同步和帧同步处理,实现帧同步之后将整帧电文进行维特比译码,将译码结果进行解析获取l1oc导航参数,由达到帧同步后的观测量获得l1oc伪距实现定位导航;

161.(5)、利用glonass的传统信号l1of或l2of,解调电文,获取卫星prn号、载波多普勒和大致的发射时间整秒点,引导捕获l2ocp信号;

162.(6)、当l2ocp达到同步之后,利用所述的ve-i、p-i、vl-i、ve-q、p-q和vl-q六组相关器的相关值进行bump-jump峰跳检测消除副峰假锁;

163.(7)、当l2ocp达到同步并消除副峰之后,读取l2ocp码与i支路的相关值,获取二级码,通过二级码同步获取整秒级的发射时间,用于生成独立的伪距观测量;

164.(8)、利用glonass的传统信号l1of或l2of,解调电文,获取卫星prn号、载波多普勒和大致的发射时间整秒点,引导捕获l3ocp信号;

165.(9)、当l3ocp达到同步之后,对l3ocd导航电文进行位同步和帧同步处理,实现帧同步之后将整帧电文进行维特比译码,将译码结果进行解析获取l3oc导航参数,由达到帧同步后的观测量获得l3oc伪距。

166.以上所述,仅为本发明较佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,根据本发明的技术方案及其发明构思加以等同替换或改变,都应涵盖在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。