1.本发明涉及一种用于对电子器件进行编程的装置以及相关的编程方法。

2.特别地,根据本发明的装置可以用于电子器件的icp(电路内编程)、isp(系统内编程)或pp(预编程)类型的编程,例如微控制器、微处理器、非易失性存储器、闪存、串行存储器或其他存储器,其可以已经:被组装(icp、isp)在电子器件上,电子器件例如但不限于手机、电子控制单元、数码相机;或未组装(pp),下面的描述将明确地对其进行参考而不失一般性。

背景技术:

3.已知编程装置,其用于例如但不仅限于原型设计阶段或最终生产阶段中用于icp、isp或pp编程(通过在已经组装在印刷电路或电子器件上或尚未组装的微控制器、微处理器和/或非易失性电子存储器上下载应用程序或预定数据集)。

4.这种已知的编程装置包括至少一个处理单元或cpu(中央处理单元),通常是微处理器或微控制器,其被设计用于基于其特定类型或系列来处理和管理电子器件编程算法。事实上,第一处理单元转而用专门设计用于对预定类型的器件(例如,特定系列的微处理器或非易失性存储器)进行编程的特定代码进行编程。因此,该编程算法是基于待编程电子器件的特定硬件架构来实现的,例如存储器地址空间的特定内部结构(在待编程器件为微控制器、微处理器或存储器的情况下),或者其器件的地址,例如串行端口、i2c端口、adc端口、计数器或硬件或其他“定时器”(在待编程器件是微控制器或微处理器的情况下)。

5.编程装置还包括至少一个现场可编程器件或fpd(现场可编程器件),例如fpga(现场可编程门阵列)器件,其一侧连接到处理单元,并且另一侧连接到至少一个编程端口,以用于isp、icp或pp编程,其可以选择性地连接到电子板或电子装置,从而连接到待编程的电子器件。

6.作为示例但不限于此,有可能在单个电子组件中使用由微处理器单元或硬处理器系统(hard processor system,hps)单元和可编程单元或fpd单元(fpga)组成的处理单元。这允许限制编程系统的印刷电路上的必要空间,并在两个组件单元之间提供非常快速和高效的通信通道。

7.处理单元的fpga部分被布置为从处理单元的hps部分接收电子器件的编程数据,例如按块顺序地接收,并基于预定的icp、isp或pp通信协议通过编程端口将它们发送到待编程的电子器件。因此,处理单元的fpga部分被专门编程来管理所述通信协议以及相关的数据流和控制信号。

8.这种编程装置还提供与电子处理器的连接,该电子处理器设置有合适的用户接口,以用于选择与程序或要编程的电子器件的编程数据有关的一个或多个文件并将其传送到该装置本身。这种连接通常是通过数据通信线实现的,例如rs232型串行线、并行线、usb线、以太网线或其他连接到处理单元的线。

9.已知的用于编程的装置的缺点在于,在需要高编程速度的情况下,必须在编程系

统和待编程器件之间提供长度有限且具有良好尺寸的电气特征的通信线。这也可能需要基于待编程器件和安装该器件的板来修改通信线的特征。这需要编程系统的高成本和长集成时间。

10.已知的用于编程的装置的另一个缺点是,在需要在待编程器件内部下载大量配置数据的情况下,必须提供编程系统的符合这样的数据量的非易失性存储容量。事实上,非易失性存储容量的缺乏可能需要在电子处理器和编程系统之间交换大量数据,从而导致编程时间的增加。

技术实现要素:

11.因此,本发明的目的是克服上面强调的已知技术的装置的显著限制。

12.特别地,本发明的目的是具有能够支持处理单元和接口块之间的不同通信可能性的整个编程系统的架构。这允许编程系统轻松集成并适应生产环境和不断变化的操作条件。

13.本发明的另一目的在于提高从处理单元向接口块发送的数据和从接口块向处理单元发送的数据的传输速度。这导致器件编程时间的减少。

14.本发明的另一个目的是保护从处理单元发送到接口块的数据和从接口块发送到处理单元的数据的完整性。这转化为编程系统的更大鲁棒性。

15.本发明的另一个目的是允许在编程系统内存储大量数据,以允许更快和更有效地访问要下载到待编程器件的数据。

附图说明

16.本发明的结构和功能特征及其相对于已知技术的优势将通过考察以下描述变得更加明显,这些描述是参考示出了用于电子器件编程的装置的一些优选但非限制性实施例的附图进行的,在附图中:

[0017]-图1是示意性地表示待编程器件通过双向单端线连接到编程系统的实施方式的框图;

[0018]-图2是示意性地表示待编程器件通过双向差分并行线连接到编程系统的实施方式的框图;

[0019]-图3是示意性地表示待编程器件通过双向差分高速串行线连接到编程系统的实施方式的框图;

[0020]-图4是示意性地表示待编程器件通过双向差分高速串行线连接到编程系统的实施方式的框图;在后一种实施方式中,高速串行化/解串行化程序被集成到编程系统的处理单元中。

具体实施方式

[0021]

根据上述目的,一种用于对电子器件进行编程,特别是用于isp、icp或pp编程的装置,包括hps处理单元,其准备用于处理和管理对应的待编程电子器件的一个或多个编程算法。

[0022]

根据本发明的用于编程的装置还包括可编程现场单元或fpd,例如fpga单元,其连

接到hps处理单元或形成处理单元本身的一部分并且可操作地与至少一个待编程的电子器件相关联。所述fpga单元被布置为从hps处理单元接收被处理的编程数据,以基于预定的通信协议将它们发送到待编程的电子器件。

[0023]

该装置还包括至少一个接口块,其与所述处理单元的相关编程接口相关联,以用于连接待编程的电子器件。

[0024]

根据本发明的一方面,现场可编程单元或fpd(特别是可编程fpga单元)设置有多个逻辑端口,这些逻辑端口被选择性地编程和/或以动态方式可编程以管理所述一个或多个算法通过输出接口进行icp、isp或pp编程(取决于待编程的特定电子器件)。

[0025]

因此,使用根据需要被编程为充当用于管理至少一个特定编程算法的预定处理单元的fpd单元(特别是fpga单元)允许维持相同的电路作为编程板来在不同的时间执行对电子器件(甚至彼此完全不同的电子器件)的编程。

[0026]

根据本发明的变体,编程装置还包括与可编程类型单元或fpd单元相关联的辅助处理单元,其被布置为在其上加载预定的配置数据。该配置数据至少涉及fpd单元的逻辑端口的期望编程以及一种或多种编程算法。

[0027]

根据本发明的另一方面,每个输出接口连接到所述辅助处理单元以根据取决于电子器件的特定操作参数由其选择性地编程。

[0028]

提供以下内容落入本发明的精神内:编程装置包括读取单元,该读取单元连接到处理单元,非易失性电子存储单元可以选择性地关联到该处理单元,所述配置数据被存储在该非易失性电子存储单元中。因此,通过关联,即通过选择性地将诸如sd闪存卡或微型sd之类的存储单元插入到读取单元中,有可能为编程装置配置(也可能在每次通电时)期望配置的数据,以允许对特定电子器件进行编程。

[0029]

根据另一变型,编程装置包括易失性电子存储单元,其连接到处理单元以用于临时存储所述配置数据。

[0030]

根据另一变型,编程装置包括非易失性电子存储单元,其具有大存储容量以及访问它以高速读写的可能性,非易失性电子存储单元连接到处理单元,特别是连接到fpga部分,以用于存储所述配置数据。

[0031]

根据另一变型,编程装置包括与处理单元相关联的至少一个输入接口,以用于与电子处理器连接以从其至少接收与一个或多个编程算法有关的数据和用于待编程电子器件的编程数据。

[0032]

这样,有可能例如通过电子处理器的用户接口动态选择与待编程电子器件的程序相关的预定文件、特定的编程算法和相关的编程接口。

[0033]

根据本发明的变型,当相关接口块在可编程单元附近运行时,处理单元上的每个编程接口(特别是fpga部分)可以通过双向单端线直接连接到相关接口块。作为非限制性示例,当接口块与可编程单元或fpd单元位于同一印刷电路上时。

[0034]

根据本发明的变型,在将双向单端线适当地转换为双向差分线之后,可编程类型单元或fpd单元上的每个编程接口可以用连接电缆连接到次级外部单元。该次级单元由将双向差分线转换为双向单端线的块和连接到待编程器件的相关接口块组成。作为非限制性示例,连接电缆由来自承载一个或多个电源电压的线和地线的双向差分数据线组成。根据本发明的变体,可编程类型单元或fpd单元上的每个编程接口可以采用连接到次级外部单

元的至少一条高速双向差分串行线的形式。作为非限制性示例,这由如下特定类型的可编程单元或fpd单元所允许:其集成与高速双向差分线接合的高速串行化和解串行化系统。作为非限制性示例,与次级外部单元的连接电缆由至少一条双向差分高速串行数据线、承载一个或多个电源电压的线和地线组成。次级单元由用于将高速双向差分串行线转换为双向单端线的块和连接到待编程器件的相关接口块组成。

[0035]

根据本发明的一个变型,可编程类型单元或fpd单元上的每个编程接口可以通过由单端双向线组成的并行总线连接到高速串行化和解串行化单元。作为非限制性示例,高速串行化和解串行化单元可以由集成高速串行化和解串行化系统的另一个可编程单元或fpd单元组成,这些系统允许通过高速双向差分串行线连接到次级外部单元。作为非限制性示例,与次级外部单元的连接电缆由至少一条双向差分高速串行数据线、承载一个或多个电源电压的线和地线组成。次级单元由用于将高速双向差分串行线转换为双向单端线的块和连接到待编程器件的相关接口块组成。本发明还涵盖了一种用于电子器件的编程方法,特别是用于对微处理器、微控制器、串行存储器、闪存等进行icp、isp或pp类型的编程。

[0036]

根据本发明的过程包括编程步骤,其中通过处理单元处理和管理与待编程的特定电子器件的编程数据相关的至少一个预定编程算法。在这个阶段,由所述算法处理的编程数据被发送到处理单元的fpga可编程部分,该fpga可编程部分可操作地与待编程的电子器件相关联。编程数据由所述fpga单元通过与其相关联的输出接口注意、基于预定的和特定的通信协议(取决于待编程器件的类型)传输到相关的电子器件。

[0037]

根据本发明的一方面,该编程方法包括初始化步骤,其中处理单元(特别是fpga部分)在现场被选择性地编程,使得其逻辑端口的至少一部分被配置为模拟被布置用于管理和处理所述编程算法的期望的和特定的微控制器或微处理器的操作。

[0038]

根据本发明的变型,至少所述配置数据在所述初始化步骤中通过非易失性电子存储单元被卸载,所述非易失性电子存储单元可操作地连接到处理单元。

[0039]

根据进一步的变型,所述配置数据由读取单元读取,所述读取单元连接到处理单元,并且非易失性电子存储单元选择性地关联到所述读取单元,所述配置数据被存储在所述非易失性电子存储单元中。

[0040]

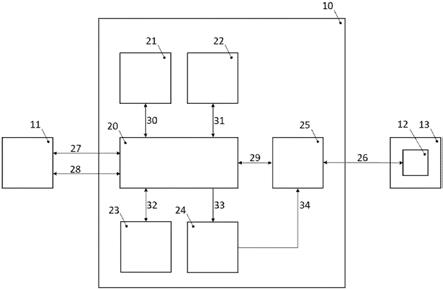

现在进入具体细节,参考所附的图1、图2、图3和图4,根据本发明的装置10可以用于对至少一个电子器件12中的电子器件进行编程,特别是用于进行系统内编程(isp)、电路内编程(icp)或预编程(pp)类型的编程,所述电子器件例如微控制器、微处理器、串行闪存等,其在isp和icp的情况下可以在诸如蜂窝电话、电子控制单元、相机或数码相机等电子装置的电路或电子板13上直接组装地编程,或者在pp情况下未组装地编程。

[0041]

所讨论的装置有利地但非排他地可在新装置的原型设计阶段期间使用,以允许对待编程器件中的应用代码进行任何重新编程。

[0042]

下面将描述图1所示的实施方式。在图2、图3和图4中所示的其他实施方式中,将描述与先前实施方式的不同之处。

[0043]

装置10包括处理单元20、可编程类型单元25、或辅助单元、第一易失性电子存储器21、第二非易失性电子存储器22、第三非易失性电子存储器23和至少一个接口块25。

[0044]

处理单元20集成了处理器部分(hps)和fpd部分(fpga)。单元20的fpd部分(fpga)是可编程现场单元,其逻辑端口可以以动态方式选择性地可编程,如下文将更好地描述的,

以便模拟特定cpu(中央处理单元),通过该特定cpu可以管理与每次要编程的特定电子器件12有关的编程数据的特定算法。

[0045]

处理单元20连接到装置10的不同组件,如下所述:

[0046]-通过双向数据总线30连接到第一电子存储器21,其例如可以是sram(静态随机存取存储器)或sdram(同步动态随机存取存储器),其具有快速访问能力,用于对编程数据或编程期间使用的特定数据用户参数进行临时存储;

[0047]-通过双向数据总线31连接到第二电子存储器22,其例如可以是用于对编程数据或编程期间使用的特定用户参数进行非易失性存储的快速访问emmc(嵌入式多媒体卡);

[0048]-通过双向数据总线32连接到第三电子存储器23,其可以是例如用于对可编程单元fpd的配置数据、编程数据、或编程期间使用的特定用户参数的非易失性存储的sd或微型sd;

[0049]-通过双向数据总线29连接到接口块25,用于基于预定的通信协议发送或接收数据,该预定的通信协议是基于被编程的特定器件12动态地确定的;

[0050]-通过数据总线33连接到辅助可编程单元25,用于将基于被编程的特定器件12而动态选择的配置参数发送到接口块25。

[0051]

处理单元20还可以通过串行线uart(通用异步接收器-发送器)27或专有通信线28选择性地可连接到电子处理器11,例如个人计算机、膝上型计算机等,电子处理器11设置有足够的用户接口。

[0052]

第二电子存储器22是具有高存储容量和高读写访问速度的非易失性存储器。在该存储器中预防性加载编程数据允许在器件12的编程阶段期间不必使用通向电子处理器的通信线27和28来访问编程数据。这导致器件12的编程时间减少。

[0053]

第三电子存储器23为可选择性移除的非易失性类型的电子存储器,例如插入对应插槽的sd(storage device)或微sd存储器(未标示)并且被布置用于存储装置10的特定的配置参数,特别是单元20的fpd可编程部分的特定的配置参数。因此,存储器23的移除和它的重新编程,或者用具有其他存储内容的不同存储器15替换,使得可以实质上在每次通电时基于待编程的特定器件12修改装置的配置参数。

[0054]

接口块25被布置为定义电信号的正确电平和要用于对特定器件12进行编程的特定信号线。实际上,接口块25在一侧连接到处理单元20并且在另一侧通过通信线26连接到要待编程器件12。

[0055]

通信线26包括一组预定的电导体,其取决于每次编程的器件12的类型可以具有不同的数量。有利地,通信线26连接到电气和机械适配器(未标示),转而物理连接到待编程的电气器件12,这允许定义与器件12兼容的期望的和特定的电气编程信号。

[0056]

接口块25尤其包括未指示的一组预定的元件,这些元件通过接口29由处理单元20可选择性地和动态地进行配置,以便在特定编程信号的方向的操作中与器件12建立预定的电连接。

[0057]

接口块25还包括动态可配置系统,以用于通过接口29由处理单元20选择特定编程信号(未标示)的输入和输出电压电平,以便取决于特定编程信号的电压电平与器件12建立预定的电连接。

[0058]

接口块25还包括用于定义特定编程信号(未标示)的输入和输出行为的系统,该系

统通过接口34由可编程单元24可选择性地和动态地进行配置,以便取决于特定编程信号的上拉或下拉条件的配置与器件12建立预定的电连接。

[0059]

如下所述,处理单元20被编程(如下所述)以便定义不同的功能块,如下所述:

[0060]-第一块101管理通过uart串行线27的数据通信;

[0061]-第二块102管理通过专有通信线28的数据通信;

[0062]-第三块103管理处理单元的hps处理器部分和处理单元的fpd可编程部分之间的通信;

[0063]-第四块104模拟预定微处理器的操作,其基于被编程的电子器件12而被动态选择;第四块104处理和管理特定的编程算法,并向接口块25发送编程数据,因此,转而向器件12发送;第四块104根据编程系统10所支持的编程通道的数量(即,可以并行编程的器件的数量)来复制;

[0064]-第五块105管理通过线32与电子存储器23的数据交换;

[0065]-第六块106管理通过数据总线30与电子存储器21的数据交换;

[0066]-第七块107管理通过数据总线31与电子存储器22的数据交换;

[0067]-第八块108管理通过线33与可编程单元24的通信,因此转而管理通过线34向接口块25的通信;

[0068]-第九块109通过处理单元20的hps处理器部分管理处理单元20的fpd可编程部分的配置的动态加载。

[0069]

上述功能块可以通过对处理单元20的可编程部分的重新编程来动态修改,这取决于待编程的特定器件12。特别地,根据硬件架构的可能修改,块104可以通过块109频繁地重新编程。

[0070]

因此,即使在对待编程的特定器件进行任何修改和/或改变的情况下,也不需要更换或重新设计装置10本身,因此也不需要更换或重新设计整个相关的功能应用代码。

[0071]

下面描述到此为止描述的装置10的操作。当它通电时,装置10在它可以用于对电子器件12进行编程之前,通过允许配置装置的不同组件的一系列操作来被初始化;下面描述优选的初始化序列。应当理解,该序列不应被理解为限制性的,因为取决于其他和不同组件的存在,其他序列也是可能的。

[0072]

在初始化阶段,处理单元20的hps处理器部分通过访问线32访问非易失性存储器23以读取与操作系统相关的文件并激活引导(boot)序列。基于处理单元20的hps处理器部分的操作系统管理与编号101、102、103、105、106、107和109相对应的上述功能块。

[0073]

在初始化阶段,电子处理器通过接口27或28将与器件12相关的数据和编程参数发送到处理单元20的hps处理器部分,这些数据和编程参数转而存储在存储器23中。处理单元20的hps处理器部分通过功能块109访问非易失性存储器23并且基于经由接口27或28从存在于电子处理器11上的用户接口接收的设置对处理单元20的fpd可编程部分进行编程。该最后一个过程允许动态修改功能块104。处理单元20的功能块104转而配置接口块25,特别是基于从处理单元20的hps处理器部分接收的设置来执行信号、它们的方向(输入/输出)和它们的电压电平的指派。处理单元20的功能块104还基于从处理单元20的hps处理器部分接收的设置来在信号没有被驱动(上拉或下拉条件)时将信号的配置传送到可编程单元24。可编程单元24转而配置接口块25。

[0074]

在对器件12进行编程期间,处理单元20的hps处理器部分使用存储器21或存储器22为支撑,从存储器23中读取器件12的编程数据块。这些数据被发送到处理单元20的fpd可编程部分,处理单元20转而将它们发送到接口块25,并因此发送到待编程的器件12。该编程步骤以本身已知的方式进行,因此这里不再进一步描述。

[0075]

参考图2,表示以上定义的装置10的演变的装置14的侧边是通过通信线38连接到编程系统14的次级外部单元15。

[0076]

装置14包括处理单元20、第一易失性电子存储器21、第二非易失性电子存储器22、第三非易失性电子存储器23和至少一个通信块35。

[0077]

次级外部单元15由通信块36和接口块25组成。

[0078]

装置14的通信块35通过以下方式被连接:

[0079]-通过双向数据总线37连接到处理单元20,以用于基于预定的通信协议发送或接收数据,该预定的通信协议是基于被编程的特定器件12而动态地确定的;

[0080]-通过双向数据总线38连接到次级外部单元15的通信块36,以用于基于预定的通信协议发送或接收数据,该预定的通信协议是基于被编程的特定器件12而动态地确定的。

[0081]

通信块35通过由一组双向单端线构成的通信接口37与处理单元20交换数据。通信块35执行:将接口37的单端线转换成通信线38的双向差分线。

[0082]

通信线38由通过差分格式的双向数据线和电源线构成(但不排他)。

[0083]

次级外部单元15的通信块36通过以下方式被连接:

[0084]-通过双向数据总线38连接到编程系统14的通信块35,以用于基于预定的通信协议来发送或接收数据,该预定的通信协议是基于被编程的特定器件12动态地确定的;

[0085]-通过双向数据总线39连接到次级外部单元15的接口块25,以用于基于预定的通信协议发送或接收数据,该预定的通信协议是基于经由通信线26编程的特定器件12动态地确定的。

[0086]

次级外部单元15的通信块36通过由差分类型的一组双向数据线构成的通信接口38与编程系统14的通信块35交换数据。通信块36执行:将接口38的差分线转换成通信线39的双向单端线。通信线39由单端格式的双向数据线以及电源线构成(但不排他)。

[0087]

参考图3,代表以上定义的装置10至14的演变的装置16的两侧是经由通信线43连接到编程系统16的次级外部单元17。

[0088]

装置16包括处理单元20、第一易失性电子存储器21、第二非易失性电子存储器22、第三非易失性电子存储器23和至少一个通信块40。

[0089]

次级外部单元17由通信块41和接口块25组成。

[0090]

装置16的通信块41通过以下方式被连接:

[0091]-通过双向数据总线42连接到处理单元20,以用于基于预定的通信协议发送或接收数据,该预定的通信协议是基于被编程的特定器件12动态地确定的;

[0092]-通过双向数据总线43连接到次级外部单元17的通信块41,以用于基于预定的通信协议发送或接收数据,该预定的通信协议是基于被编程的特定器件12动态地确定的。

[0093]

通信块40通过由一组双向单端线构成的通信接口42与处理单元20交换数据。通信块40执行:在通信线43的一条或多条高速双向差分串行线中接口42的单端线的转换和串行化/解串行化。

[0094]

通信线43由一条或多条高速差分双向串行数据线和电源线构成。作为非限制性示例,它们可以用作通过利用传递高速数据的差分线和用于电力传输的以太网供电(power on ethernet,poe)技术传输以太网电缆的手段。

[0095]

次级外部单元17的通信块41被连接:

[0096]-通过双向数据总线43连接到编程系统16的通信块40,以用于基于预定的通信协议发送或接收数据,该预定的通信协议是基于被编程的特定器件12动态地确定的;

[0097]-通过双向数据总线44连接到次级外部单元17的接口块25,以用于基于预定的通信协议发送或接收数据,该预定的通信协议是基于经由通信线26编程的特定器件12动态地确定的。

[0098]

次级外部单元17的通信块41通过由一条或多条高速差分串行线构成的通信接口43与编程系统16的通信块40交换数据。通信块41执行:将接口43的高速差分串行线转换和串行化/解串行化为通信线44的单端双向线。

[0099]

通信线44由单端格式的双向数据线和电源线构成(但不排他)。

[0100]

作为非限制性示例,分别存在于编程系统16和次级外部单元17中的通信块40和41可以使用集成高速serdes收发器类型的串行化和解串行化系统的可编程fpga器件来实现。

[0101]

参考图4,代表以上定义的装置16的演变的装置18的两侧是经由通信线43连接到编程系统18的次级外部单元17。

[0102]

相对于先前的编程系统16,在编程系统18中引入的变化涉及:消除通信块40和接口42,以及用处理单元45替换处理单元20。由通信块40和接口42执行的功能集成在处理单元45中。

[0103]

作为示例但不限于此,最终有可能在单个电子组件中使用处理单元,该处理单元由微处理器单元或硬处理器系统(hard processor system,hps)单元、可编程单元或fpd单元(fpga)和一个或多个高速serdes收发器组成。这允许限制印刷电路上的必要空间并在组件单元之间具有非常快速和高效的通信通道。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。