一种基于sopc的时间继电器校准装置

技术领域

1.本发明涉及到计量技术领域,尤其涉及一种基于sopc的时间继电器校准装置。

背景技术:

2.时间继电器是一种常用的继电器,在其输入端加入特定信号后,输出端经过设定时间的延迟后发生触点动作输出,从而实现延时动作,在电路中起着自动调节、安全保护、转换电路的作用。一般是由时基电路、控制电路、计时电路、计时显示、整定电路、驱动电路和触点簧片组成。目前广泛地应用于工业制造的各种工艺设备上的时间控制系统。

3.目前,现有的时间继电器校准设备主要存在以下问题:现有校准装置通常使用单片机与其他分离器件的形式来设计电路,体积大、便携性差、完成现场校准工作困难,还有维护困难及信号易受干扰的缺点。校准时间继电器时,接线繁琐,而且不同类型的时间继电器的接线方式也有较大不同,在校准过程中频繁的拆装接线容易致使仪器损坏。

4.公开号为cn 211826375u,公开日为2020年10月30日的中国专利文献公开了一种时间继电器的校准系统,包括两个相同的时间继电器,其中第一时间继电器为待测试时间继电器,第二时间继电器为测试用时间继电器,其中还包括调压器、ac/dc转换器、校准装置、第一开关、第二开关、第三开关、第四开关和辅助电源;校准装置响应于第一开关、第二开关和第三开关均处于导通状态,使得第一时间继电器的信号输入端与第二时间继电器的输入端同时得电,记录第一时间点t1;并且,响应于第三开关断开,第四开关导通,使得第二时间继电器的输入端的第二次得电,记录第二时间点t2;由此校准装置根据所述第二时间点t2、第一时间点t1以及第一时间继电器的标定延时时间获得时间校准参数。

5.该专利文献公开的时间继电器的校准系统,校准方案简单易行,成本较低。但是,信号高速传输时的稳定性欠佳,校准操作繁琐。

技术实现要素:

6.本发明为了克服上述现有技术的缺陷,提供一种基于sopc的时间继电器校准装置,本发明能够减少通用芯片与分立元件的使用,提高了信号高速传输时的稳定性,合理规划人机交互界面,提升便携性,通过设计合理的信号处理电路,减少了校准过程中的连线及拆装过程,校准操作简便。

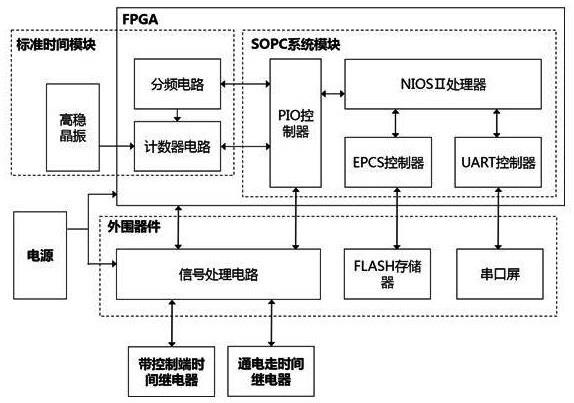

7.本发明通过下述技术方案实现:一种基于sopc的时间继电器校准装置,包括标准时间模块,其特征在于:还包括sopc系统模块、信号处理电路、flash存储器和串口型液晶触摸屏,所述标准时间模块包括分频电路和计数器电路,所述sopc系统模块通过在fpga上嵌入niosⅱ软核处理器、uart控制器、pio控制器和epcs控制器形成,sopc系统模块的信息通过avalon总线进行传输,所述sopc系统模块分别与标准时间模块、信号处理电路、flash存储器和串口型液晶触摸屏电连接。

8.所述niosⅱ软核处理器,用于处理系统控制、多任务处理和中断响应。

9.所述uart控制器,用于与串口型液晶触摸屏进行通讯并进行数据解析。

10.所述pio控制器,用于向标准时间模块和信号处理电路提供控制信号。

11.所述epcs控制器通过spi协议与flash存储器进行通信,完成fpga的配置。

12.所述标准时间模块采用高稳晶振提供校准装置的标准时钟信号,在fpga内使用时序逻辑电路对晶振输入时钟进行硬件分频。

13.所述高稳晶振的时钟信号分频后得到1μs、10μs、100μs、1ms、10ms、100ms、1s和10s 八个时标信号。

14.所述计数器电路的输入端连接sopc系统模块的pio控制器接收设置信息,输出端连接pio控制器实时输出计数器的计数值。

15.所述信号处理电路包括连接带控制端时间继电器的信号处理电路和连接无控制端时间继电器的信号处理电路。

16.本发明所述sopc系统模块是指可编程的片上系统。

17.本发明所述fpga是指场可编程门阵列。

18.本发明所述uart控制器是指通用异步收发传输器。

19.本发明所述pio控制器是指并行输入/输出控制器。

20.本发明所述epcs控制器是指串行存储器。

21.本发明所述niosⅱ软核处理器是指嵌入式处理器。

22.本发明所述spi是指串行外围设备接口。

23.本发明的有益效果主要表现在以下方面:1、本发明,标准时间模块包括分频电路和计数器电路, sopc系统模块通过在fpga上嵌入niosⅱ软核处理器、uart控制器、pio控制器和epcs控制器形成,sopc系统模块的信息通过avalon总线进行传输, sopc系统模块分别与标准时间模块、信号处理电路、flash存储器和串口型液晶触摸屏电连接,较现有技术而言,能够减少通用芯片与分立元件的使用,提高了信号高速传输时的稳定性,合理规划人机交互界面,提升便携性,通过设计合理的信号处理电路,减少了校准过程中的连线及拆装过程,校准操作简便。

24.2、本发明,采用sopc,将嵌入式处理器、接口控制器、数字逻辑电路集成到一块fpga芯片上,具备软硬件设计的功能,减少了元器件的使用,提高了信号高速传输时的稳定性,具有集成度高、可靠性好、低功耗、便于升级的优点。

25.3、本发明,人机交互通过串口型液晶触摸屏实现,通过串口型液晶触摸屏的虚拟按键实现数字键及功能键的按键功能,减少了采用实体键所占用的面板面积。

26.4、本发明,通过采用高稳晶振提供高稳定度的基准时钟信号,保证了被校时间类测量设备对时标的要求。

27.5、本发明,根据时间继电器的不同类别,设计连接带控制端时间继电器的信号处理电路和连接无控制端时间继电器的信号处理电路,增强了校准过程的安全性和便利性。

附图说明

28.下面将结合说明书附图和具体实施方式对本发明作进一步的具体说明,其中:图1为本发明的结构框图;

图2为本发明sopc系统模块的结构框图;图3 为本发明串口型液晶触摸屏的连接示意图;图4 为本发明分频电路及计数电路信号连接图;图5为本发明带控制端时间继电器信号处理电路原理图;图6为本发明采用交流固态继电器的无控制端时间继电器信号处理电路原理图;图7为本发明采用直流固态继电器的无控制端时间继电器信号处理电路原理图。

具体实施方式

29.实施例1参见图1-图4,一种基于sopc的时间继电器校准装置,包括标准时间模块,还包括sopc系统模块、信号处理电路、flash存储器和串口型液晶触摸屏,所述标准时间模块包括分频电路和计数器电路,所述sopc系统模块通过在fpga上嵌入niosⅱ软核处理器、uart控制器、pio控制器和epcs控制器形成,sopc系统模块的信息通过avalon总线进行传输,所述sopc系统模块分别与标准时间模块、信号处理电路、flash存储器和串口型液晶触摸屏电连接。

30.本实施例为最基本的实施方式,标准时间模块包括分频电路和计数器电路, sopc系统模块通过在fpga上嵌入niosⅱ软核处理器、uart控制器、pio控制器和epcs控制器形成,sopc系统模块的信息通过avalon总线进行传输, sopc系统模块分别与标准时间模块、信号处理电路、flash存储器和串口型液晶触摸屏电连接,较现有技术而言,能够减少通用芯片与分立元件的使用,提高了信号高速传输时的稳定性,合理规划人机交互界面,提升便携性,通过设计合理的信号处理电路,减少了校准过程中的连线及拆装过程,校准操作简便。

31.实施例2参见图1-图4,一种基于sopc的时间继电器校准装置,包括标准时间模块,还包括sopc系统模块、信号处理电路、flash存储器和串口型液晶触摸屏,所述标准时间模块包括分频电路和计数器电路,所述sopc系统模块通过在fpga上嵌入niosⅱ软核处理器、uart控制器、pio控制器和epcs控制器形成,sopc系统模块的信息通过avalon总线进行传输,所述sopc系统模块分别与标准时间模块、信号处理电路、flash存储器和串口型液晶触摸屏电连接。

32.所述niosⅱ软核处理器,用于处理系统控制、多任务处理和中断响应。

33.实施例3参见图1-图4,一种基于sopc的时间继电器校准装置,包括标准时间模块,还包括sopc系统模块、信号处理电路、flash存储器和串口型液晶触摸屏,所述标准时间模块包括分频电路和计数器电路,所述sopc系统模块通过在fpga上嵌入niosⅱ软核处理器、uart控制器、pio控制器和epcs控制器形成,sopc系统模块的信息通过avalon总线进行传输,所述sopc系统模块分别与标准时间模块、信号处理电路、flash存储器和串口型液晶触摸屏电连接。

34.所述niosⅱ软核处理器,用于处理系统控制、多任务处理和中断响应。

35.所述uart控制器,用于与串口型液晶触摸屏进行通讯并进行数据解析。

36.本实施例为一较佳实施方式,采用sopc,将嵌入式处理器、接口控制器、数字逻辑电路集成到一块fpga芯片上,具备软硬件设计的功能,减少了元器件的使用,提高了信号高速传输时的稳定性,具有集成度高、可靠性好、低功耗、便于升级的优点。

37.实施例4参见图1-图4,一种基于sopc的时间继电器校准装置,包括标准时间模块,还包括sopc系统模块、信号处理电路、flash存储器和串口型液晶触摸屏,所述标准时间模块包括分频电路和计数器电路,所述sopc系统模块通过在fpga上嵌入niosⅱ软核处理器、uart控制器、pio控制器和epcs控制器形成,sopc系统模块的信息通过avalon总线进行传输,所述sopc系统模块分别与标准时间模块、信号处理电路、flash存储器和串口型液晶触摸屏电连接。

38.所述niosⅱ软核处理器,用于处理系统控制、多任务处理和中断响应。

39.所述uart控制器,用于与串口型液晶触摸屏进行通讯并进行数据解析。

40.所述pio控制器,用于向标准时间模块和信号处理电路提供控制信号。

41.所述epcs控制器通过spi协议与flash存储器进行通信,完成fpga的配置。

42.本实施例为又一较佳实施方式,人机交互通过串口型液晶触摸屏实现,通过串口型液晶触摸屏的虚拟按键实现数字键及功能键的按键功能,减少了采用实体键所占用的面板面积。

43.实施例5参见图1-图4,一种基于sopc的时间继电器校准装置,包括标准时间模块,还包括sopc系统模块、信号处理电路、flash存储器和串口型液晶触摸屏,所述标准时间模块包括分频电路和计数器电路,所述sopc系统模块通过在fpga上嵌入niosⅱ软核处理器、uart控制器、pio控制器和epcs控制器形成,sopc系统模块的信息通过avalon总线进行传输,所述sopc系统模块分别与标准时间模块、信号处理电路、flash存储器和串口型液晶触摸屏电连接。

44.所述niosⅱ软核处理器,用于处理系统控制、多任务处理和中断响应。

45.所述uart控制器,用于与串口型液晶触摸屏进行通讯并进行数据解析。

46.所述pio控制器,用于向标准时间模块和信号处理电路提供控制信号。

47.所述epcs控制器通过spi协议与flash存储器进行通信,完成fpga的配置。

48.所述标准时间模块采用高稳晶振提供校准装置的标准时钟信号,在fpga内使用时序逻辑电路对晶振输入时钟进行硬件分频。

49.所述高稳晶振的时钟信号分频后得到1μs、10μs、100μs、1ms、10ms、100ms、1s和10s 八个时标信号。

50.本实施例为又一较佳实施方式,通过采用高稳晶振提供高稳定度的基准时钟信号,保证了被校时间类测量设备对时标的要求。

51.实施例6参见图1-图4,一种基于sopc的时间继电器校准装置,包括标准时间模块,还包括sopc系统模块、信号处理电路、flash存储器和串口型液晶触摸屏,所述标准时间模块包括分频电路和计数器电路,所述sopc系统模块通过在fpga上嵌入niosⅱ软核处理器、uart控制器、pio控制器和epcs控制器形成,sopc系统模块的信息通过avalon总线进行传输,所述

sopc系统模块分别与标准时间模块、信号处理电路、flash存储器和串口型液晶触摸屏电连接。

52.所述niosⅱ软核处理器,用于处理系统控制、多任务处理和中断响应。

53.所述uart控制器,用于与串口型液晶触摸屏进行通讯并进行数据解析。

54.所述pio控制器,用于向标准时间模块和信号处理电路提供控制信号。

55.所述epcs控制器通过spi协议与flash存储器进行通信,完成fpga的配置。

56.所述标准时间模块采用高稳晶振提供校准装置的标准时钟信号,在fpga内使用时序逻辑电路对晶振输入时钟进行硬件分频。

57.所述高稳晶振的时钟信号分频后得到1μs、10μs、100μs、1ms、10ms、100ms、1s和10s 八个时标信号。

58.所述计数器电路的输入端连接sopc系统模块的pio控制器接收设置信息,输出端连接pio控制器实时输出计数器的计数值。

59.所述信号处理电路包括连接带控制端时间继电器的信号处理电路和连接无控制端时间继电器的信号处理电路。

60.本实施例为最佳实施方式,根据时间继电器的不同类别,设计连接带控制端时间继电器的信号处理电路和连接无控制端时间继电器的信号处理电路,增强了校准过程的安全性和便利性。

61.本发明信号处理电路根据时间继电器的控制方式不同,设计出两种不同的控制电路:连接带控制端时间继电器的信号处理电路,参见图5。

62.每个校准通道使用了三个电子开关,接时间继电器reset端的是一个dg442电子开关,pio接口在最开始给这个电子开关in引脚提供一个10ms的正脉冲使其接通,时间继电器reset端与com端连接复位。下一步,pio接口将连接时间继电器pause端的电子开关dg442的in引脚拉低使其断开,使时间继电器pause端与com端断开取消暂停,同时恢复时间继电器计时功能,下一步,pio接口将连接时间继电器常闭端的电子开关dg442的in引脚拉高使其接通,时间继电器常闭端导通开始计时,同时时间继电器两端分别连接的校准装置的计数使能端与pio输出的高电平导通,校准装置也同时开始计时,时间继电器设置时间到后,常闭端断开,时间继电器和校准装置同时停止计时,实现带控制端时间继电器的校准。

63.连接无控制端时间继电器的信号处理电路,参见图6和图7。

64.交流时间继电器与直流时间继电器的控制原理相同,以直流时间继电器校准为例进行说明,pio接口输出高电平接入时间继电器常闭端使校准装置计数器开始计时,同时高电平信号通过uln2003驱动后将固态输入端拉高,固态继电器输出端导通,外部直流电源与时间继电器正端导通,时间继电器也同步开始计时,时间继电器设置时间到后,常闭端断开,时间继电器和校准装置同时停止计时,实现无控制端时间继电器的校准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。