1.本技术实施例涉及通信技术领域,尤其涉及一种重传方法及装置。

背景技术:

2.信道编码作为最基本的无线接入技术,在保证数据的可靠性传输方面起到至关重要的作用。在现有的无线通信系统中,一般采用turbo码、低密度奇偶校验码(low density parity check,ldpc)和极化(polar)码进行信道编码。turbo码不能够支持过低或过高码率的信息传输。而对于中短包传输,turbo码和ldpc码也由于自身编译码的特点,在有限码长下很难达到理想的性能。在实现方面,turbo码和ldpc码在编译码实现过程中具有较高的计算复杂度。polar码是理论上证明可以取得香农容量,且具有相对简单的编译码复杂度的好码,因而得到了越来越广泛的应用。在第五代(5th generation,5g)通信系统中,将polar码确定为控制信道的编码方式。因此在标准中详细的规定了polar码的编码流程,包括是否分段、确定速率匹配方式、信息比特和校验比特(包括循环冗余校验比特和/或奇偶校验比特)在极化信道上的映射、编码、速率匹配等具体的过程。

3.但也正因为在5g标准中polar码只用于控制信道,因此不涉及混合自动重传请求(hybrid automatic repeat request,harq)的机制设计。而在数据信道中,harq的引入将有效的增强传输的可靠性并进而增大系统的吞吐量。所以如何针对polar码的编码机制,设计合适的harq方案,就成为将polar码应用到数据信道传输这一课题亟需解决的问题。

技术实现要素:

4.本技术实施例提供一种应用于无线通信的重传方法及装置,具有实现简单的优点。

5.本技术实施例提供的具体技术方案如下:

6.第一方面,提供一种重传方法,其特征在于,包括:

7.发送装置获取包括k待编码比特的待编码比特序列,k为正整数;

8.对所述待编码序列进行极化编码,得到编码后的第一比特序列,所述第一比特序列的长度为n0,确定初传版本rv0;

9.确定重传版本rv1的长度e1;

10.根据初传码率r0确定重传版本rv1;

11.发送所述rv1。

12.通过这样的实施方法,一方面尽量复用了现有标准中的设计,另一方面又吸纳了现有harq机制的优点,因此实现简单,性能也能满足需求。

13.在一种可能的设计中,所述根据初传码率r0确定重传版本rv1包括:

14.当r0小于或等于预设的码率门限r_threshold时,所述rv1为从初传的第一循环缓存中读取的e1个比特;或者

15.当r0大于r_threshold时,采用增量冗余ir的方式生成编码后的第二比特序列,根

据所述第二比特序列获取rv1,所述第二比特序列长度为n1,n1=2*n0。

16.在一种可能的设计中,所述根据所述第二比特序列获取rv1为:

17.获取子信道集合q1,所述q1中包括k个元素,所述k个元素是初传中用于放置所述k个待编码比特的k个子信道的序号;

18.获取子信道集合q2,其中q2(i)=q1(i) n0,其中i=0,1,

…

,k-1,其中n0为初传时采用的极化码的母码长度;

19.获取子信道集合q3,其中q3(i)《n0或者q3(i)∈q2其中i=0,1,

…

,k-1;

20.确定扩展待编码比特集合qext,其中的元素为所述q3中小于n0的元素;

21.确定复制比特集合qchk=q2\(q3\qext);

22.根据所述q2、所述q3、所述qext、所述qchk对所述k个待编码比特进行母码长度为n1的polar码编码,得到所述第二比特序列。

23.在一种可能的设计中,所述q3是根据长度为n1的可靠度排序序列以及重传的速率匹配方式确定的。

24.在一种可能的设计中,所述根据所述q2、所述q3、所述qext、所述qchk对所述k个待编码比特进行母码长度为n1的polar码编码包括:

25.选取部分或全部qchk中的子信道上的比特值逐个复制到对应的qext的子信道上。

26.在一种可能的设计中,所述根据所述第二比特序列获取rv1为:

27.根据重传的速率匹配方式从第二比特序列的前n0个比特中得到rv1。

28.在一种可能的设计中,所述方法还包括:

29.所述发送装置将rv0和rv1级联输入第二循环缓存;

30.所述发送装置根据rv0和rv1进行重传。

31.第二方面,提供一种重传方法,其特征在于:

32.接收装置接收包含k个待编码比特的信息的接收信号,所述接收信号对应的母码长度n0,确定初传版本rv0;

33.确定重传版本rv1的长度e1;

34.根据初传码率r0确定重传版本rv1;

35.根据所述rv0和rv1进行解码。

36.在一种可能的设计中,所述根据初传码率r0确定重传版本rv1包括:

37.当r0小于或等于预设的码率门限r_threshold时,所述rv1为从初传的第一循环缓存中读取的e1个比特;或者

38.当r0大于r_threshold时,采用增量冗余ir的方式生成编码后的第二比特序列,根据所述第二比特序列获取rv1,所述第二比特序列长度为n1,n1=2*n0。

39.在一种可能的设计中,所述根据所述第二比特序列获取rv1为:

40.获取子信道集合q1,所述q1中包括k个元素,所述k个元素是初传中用于放置所述k个待编码比特的k个子信道的序号;

41.获取子信道集合q2,其中q2(i)=q1(i) n0,其中i=0,1,

…

,k-1,其中n0为初传时采用的极化码的母码长度;

42.获取子信道集合q3,其中q3(i)《n0或者q3(i)∈q2其中i=0,1,

…

,k-1;

43.确定扩展待编码比特集合qext,其中的元素为所述q3中小于n0的元素;

44.确定复制比特集合qchk=q2\(q3\qext);

45.根据所述q2、所述q3、所述qext、所述qchk对所述k个待编码比特进行母码长度为n1的polar码编码,得到所述第二比特序列。

46.在一种可能的设计中,所述q3是根据长度为n1的可靠度排序序列以及重传的速率匹配方式确定的。

47.在一种可能的设计中,所述根据所述q2、所述q3、所述qext、所述qchk对所述k个待编码比特进行母码长度为n1的polar码编码包括:

48.选取部分或全部qchk中的子信道上的比特值逐个复制到对应的qext的子信道上。

49.在一种可能的设计中,所述根据所述第二比特序列获取rv1为:

50.根据重传的速率匹配方式从第二比特序列的前n0个比特中得到rv1。

51.在一种可能的设计中,所述方法还包括:

52.所述发送装置将rv0和rv1级联输入第二循环缓存;

53.所述发送装置根据rv0和rv1进行重传。

54.第三方面,提供一种发送装置,该装置具有实现上述第一方面和第一方面的任一种可能的设计中所述的方法的功能。所述功能可以通过硬件实现,也可以通过硬件执行相应的软件实现。所述硬件或软件包括一个或多个与上述功能相对应的模块。

55.在一个可能的设计中,当所述功能的部分或全部通过硬件实现时,所述发送装置包括:输入接口电路,用于获取待传传输块;逻辑电路,用于执行上述第一方面和第一方面的任一种可能的设计中所述的行为;输出接口电路,用于输出编码后的序列或者重传的序列。

56.可选的,所述发送装置可以是芯片或者集成电路。

57.在一个可能的设计中,当所述功能的部分或全部通过软件实现时,所述发送装置包括:存储器,用于存储程序;处理器,用于执行所述存储器存储的所述程序,当所述程序被执行时,所述发送装置可以实现如上述第一方面和第一方面的任一种可能的设计中所述的方法。

58.可选的,上述存储器可以是物理上独立的单元,也可以与处理器集成在一起。

59.在一个可能的设计中,当所述功能的部分或全部通过软件实现时,所述发送装置包括处理器。用于存储程序的存储器位于所述发送装置之外,处理器通过电路/电线与存储器连接,用于读取并执行所述存储器中存储的程序。

60.在一个可能的设计中,所述装置为网络设备或终端。

61.第四方面,提供一种接收装置,该装置具有实现上述第二方面和第二方面的任一种可能的设计中所述的方法的功能。所述功能可以通过硬件实现,也可以通过硬件执行相应的软件实现。所述硬件或软件包括一个或多个与上述功能相对应的模块。

62.在一个可能的设计中,当所述功能的部分或全部通过硬件实现时,所述接收装置包括:输入接口电路,用于获取接收信号;逻辑电路,用于执行上述第二方面和第二方面的任一种可能的设计中所述的行为;输出接口电路,用于输出解码结果。

63.可选的,所述接收装置可以是芯片或者集成电路。

64.在一个可能的设计中,当所述功能的部分或全部通过软件实现时,所述接收装置包括:存储器,用于存储程序;处理器,用于执行所述存储器存储的所述程序,当所述程序被

执行时,所述发送装置可以实现如上述第一方面和第一方面的任一种可能的设计中所述的方法。

65.可选的,上述存储器可以是物理上独立的单元,也可以与处理器集成在一起。

66.在一个可能的设计中,当所述功能的部分或全部通过软件实现时,所述接收装置包括处理器。用于存储程序的存储器位于所述接收装置之外,处理器通过电路/电线与存储器连接,用于读取并执行所述存储器中存储的程序。

67.在一个可能的设计中,所述装置为网络设备或终端。

68.第五方面,提供了一种计算机存储介质,存储有计算机程序,该计算机程序包括用于执行第一方面和第一方面的任一可能设计中任一种所述的方法的指令。

69.第六方面,提供了一种计算机存储介质,存储有计算机程序,该计算机程序包括用于执行第二方面和第二方面的任一可能设计中任一种所述的方法的指令。

70.第七方面,本技术实施例提供了一种包含指令的计算机程序产品,当其在计算机上运行时,使得计算机执行上述各方面所述的方法。

71.第八方面,提供了一种无线设备,包括用于实施第一方面和第一方面的任一可能设计的发送装置和收发器,

72.所述收发器用于接收或发送信号。

73.在一个可能的设计中,所述无线设备为终端或者网络设备。

74.第九方面,提供了一种无线设备,包括用于实施第二方面和第二方面的任一可能设计的接收装置和收发器,

75.所述收发器用于接收或发送信号。

76.在一个可能的设计中,所述无线设备为终端或者网络设备。

附图说明

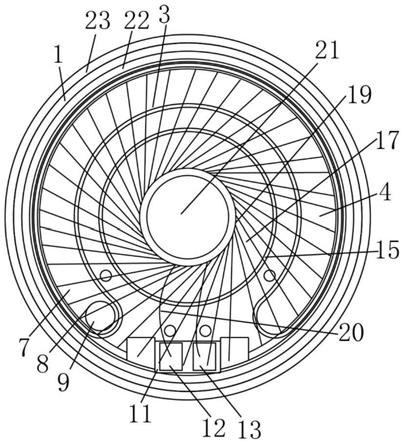

77.图1为本技术实施例中应用的通信系统架构示意图;

78.图2为本技术实施例中rv版本确认的流程示意图;

79.图3为本技术实施例中rv1版本确认的流程示意图;

80.图4为本技术实施例中比特复制示意图;

81.图5为本技术实施例中发送装置结构示意图之一;

82.图6为本技术实施例中发送装置结构示意图之二;

83.图7为本技术实施例中发送设备示意图;

84.图8为本技术实施例中接收装置结构示意图之一;

85.图9为本技术实施例中接收装置结构示意图之二;

86.图10为本技术实施例中接收设备示意图。

具体实施方式

87.下面将结合附图,对本技术实施例进行详细描述。

88.在考虑将polar码推广到数据信道时,一个合理的想法是尽量复用现有5g标准中的polar码编码方法,例如不同长度的母码序列之间的嵌套特性,速率匹配方式的选取原则等等,当然在本技术中,对此也并不限制。

radio,nr)标准中,针对打孔的情形,还额外确定了一些称为预冻结的极化子信道,也用于放置冻结比特,这里不妨将预冻结的极化子信道数量定义为p,p大于或者等于0(对于缩短的情形,p显然为0,这时候是可以不需要考虑p的),然后在剩下的e-p个极化子信道中按照可靠度挑选其中可靠度较高的k个极化子信道用于放置k个信息比特。当然,也可以先选择可靠度较低的e-p-k个子信道用于放置冻结比特,而余下的k个子信道则用于放置信息比特。放置k个信息比特的k个极化子信道中的任意一个极化子信道的可靠度都高于用于放置冻结比特的e-p-k个子信道中的任意一个子信道的可靠度。在本技术中,对p的取值不做限制,即使对于打孔的情形,p也可以为0,即使对于缩短的情形,p也可以取为大于0,并不影响本技术技术方案的实施,无论是编码端还是解码端,确认k个子信道用于放置k个信息比特的原则和方法是一致的。同时,5g nr标准中,对于n-e个极化子信道的选取,是将子块交织(例如分成32个子块)后的序列放到循环缓存(英文为circular buffer,相当于速率匹配序列)上,如果是打孔,则在循环缓存上从第n-e个位置开始读取,丢弃从0到n-e-1位置上的比特,如果是缩短,则在循环缓存上从第0个位置开始读取直至第e-1个位置,而丢弃从第e到n-1位置上的比特。这种方式并未考虑不同母码长度之间的速率匹配序列之间的关系。

95.需要说明的是,这里说的可靠度的相对关系是基于一个给定的可靠度的计算方式,不同的可靠度计算方式可能会导致极化子信道的可靠度相对关系发生变化,但选择放置信息比特的极化子信道的方法是一样的。在5g nr标准之外,信息比特也可以考虑放置于最后被打孔或者缩短的极化子信道。本技术并不限制必须按照5g nr的标准选择放置信息比特的极化子信道。

96.当数据信道的传输块大小(transport block size,tbs)过大时,需要将传输块分段,以上的介绍涉及的方案可以认为是对每一个分段进行polar编码的实施方案,本技术并不限定具体的分段准则。

97.图1为本发明实施例无线通信网络的结构示意图。图1只是一种示例,其它能用到本发明实施例的重传方法或装置的无线网络也都在本发明的保护范围内。

98.如图1所示,无线通信网络100包括网络设备110,和终端112。当无线通信网络100包括核心网102时,该网络设备110还可以与核心网102相连。网络设备110还可以与ip网络104进行通信,例如,因特网(internet),私有的ip网,或其它数据网等。网络设备为覆盖范围内的终端提供服务。例如,参见图1所示,网络设备110为网络设备110覆盖范围内的一个或多个终端112提供无线接入。除此之外,网络设备之间的覆盖范围可以存在重叠的区域,例如网络设备110和120。网络设备之间还可以可以互相通信,例如,网络设备110可以与网络设备120之间进行通信。

99.上述网络设备可以是用于与终端设备进行通信的设备。例如,可以是lte系统中的演进型基站(evolved node b,enb或enodeb),还可以是5g网络中的gnb,还可以是卫星通信中的卫星,或者未来通信系统中的网络侧设备等。或者该网络设备还可以是中继站、接入点、车载设备等。在设备对设备(device to device,d2d)通信系统、机器对机器(machine to machine,m2m)通信系统和车联网系统中,该网络设备还可以是担任基站功能的终端。

100.上述终端可以指用户设备(user equipment,ue)、接入终端、用户单元、移动站、远方站、远程终端、移动设备、用户终端、无线通信设备、用户代理或用户装置。接入终端可以是蜂窝电话、无绳电话、会话启动协议(session initiation protocol,sip)电话、无线本

地环路(wireless local loop,wll)站、个人数字处理(personal digital assistant,pda)、具有无线通信功能的手持设备、计算设备或连接到无线调制解调器的其它处理设备、车载设备、可穿戴设备、万物互联中的可通信设备,未来通信网络中的终端设备等。

101.基于图1所示的通信系统架构,本技术实施例中,执行polar码编码方法的执行主体可以为上述网络设备或终端,当网络设备或终端作为发送端发送数据或信息时,均可以采用此polar码编码方法。

102.那么,在采用polar码作为数据信道的信道编码方式时,如果在初次传输(简称初传)出错后,又如何进行重传呢?在现有的3gpp协议中并未规定polar码的harq方案,因此,一方面,数据信道的初次传输方案可以考虑复用现有3gpp技术,包括速率匹配方案的选择,信息比特的选取原则,但由于数据信道支持的传输块较大,因此nmax肯定要提高,相应的可靠度排序序列也要设计,不过这并非本发明的涉及范围,所以不作限制。另一方面,这里首先提供一种重传的方法:即初次传输出错的时候,第一次重传采用增量冗余(incremental redundancy,ir)的方式,而之后的重传则采用追逐合并(chase combining,cc)的方式。这个方式既可以利用到ir方式的优点,又可以简化设计,是个比较好的折中。

103.如图2所示,揭示了一种如何构造冗余版本(redundancy version,rv)用于harq传输的重传方法的实施例。

104.操作310:发送端对获取待编码比特序列进行polar编码,得到编码后的第一比特序列,并根据速率匹配方式获取初传版本rv0。

105.本步骤可以采用现有技术。例如,按照3gpp的标准,编码后的第一比特序列经过交织后写入第一循环缓存,当初传码率r0小于或等于7/16的时候,采用打孔的速率匹配方式,这时rv0就是第一循环缓存中的后e0个比特;而当r0大于7/16的时候,则采用缩短的速率匹配方式,这时rv0就是第一循环缓存中的前e0个比特。其中r0=k/e0,e0为初传中空口实际传输的比特数量。

106.操作320:确定重传版本rv1的长度e1。

107.e1为第一次重传的空口可以传输的比特数量,具体的取值方法和确定e0的方法一致。

108.操作330:根据初传码率r0,rv0的长度e0,rv1的长度e1,,重传的速率匹配方式等参数中的一个或多个来确定rv1。

109.当r0小于或等于预设的码率门限r_threshold(即r0≤r_threshold)时,可以直接从初传的第一循环缓存中直接读取长度为e1的rv1版本。其中r_threshold可以采用在1/4和1/2之间的任意一个值,例如1/4、3/8、7/16、15/32、1/2等等。rv1可以是第一循环缓存中的前e1个比特或者说是从第一循环缓存的起点顺时针依次读取的e1个比特,这种取法可以把初传中未传的比特优先放入rv1。也可以用与初传类似的方式根据重传的速率匹配方式确定如何从第一循环缓存中读取rv1。这里并不限定。

110.而当r0大于r_threshold(即r0》r_threshold)时,可以采用ir的方式生成编码后的第二比特序列,并根据包括但不限于码率、nmax、初传编码所采用的母码长度n0、e0、e1等参数中的一个或多个来进行速率匹配,从而获得rv1。

111.具体而言,若e1≥n0,则重传的速率匹配方式为重复,否则当r0小于或等于预设的码率门限r_threshold_initial时,重传的速率匹配方式就是打孔,而r0大于预设的码率门

限r_threshold_initial时,重传的速率匹配方式为缩短。其中r_threshold_initial为初传时判断速率匹配方式的门限,在5g nr标准中其取值为7/16,当然也可以是其他预先设定的值。为了简便起见,可以令r_threshold_initial=r_threshold。当然,r0=r_threshold的时候也可以采用和r0》r_threshold的时候一样的方式,具体看收发两端约定。

112.在一种可能的设计中,若e1≥n0,则重传的速率匹配方式为重复,否则当r0大于预设的码率门限r_threshold_initial且重传版本rv1的长度e1小于初传版本rv0的长度e0时,重传的速率匹配方式可以为缩短,打孔,或两者的组合。

113.当初传的速率匹配方式为缩短或重复时,可以有如下三种可能的实施方式。

114.实施方式a:

115.当初传的速率匹配方式为缩短时,将第二比特序列前n0个比特经过子块交织(可以根据nr标准规定的子块交织方式,也可以采用其他例如行列交织方式等,本技术不作限定,以下不再赘述)得到第三比特序列,将第二比特序列前n0/2个比特经过子块交织得到第四比特序列:

116.具体地:

117.当e1《β*e0(这里的门限值取值中,β的典型值为1/4,但也可能为1/6,1/8,1/16等值,不失一般性,在下面的叙述中以1/4为例说明。且符号“《”也可以是“≤”,这是因为在取值为门限值时,归于大于一侧还是小于一侧从总体的性能差别不大,类似的,不失一般性,在以下的叙述中对门限值的处理不再另行说明),将第一循环缓存中的第e0-e1~第e0-1个比特作为rv1;

118.而当e1≥β*e0(当上述的“《”为“≤”时,这里的“≥”则是“》”)且e1《e0,执行如下操作:

119.1.当e0-e1≤δ*n0(这里的门限值取值中,δ的典型值为1/2,,不失一般性,在下面的叙述中以1/2为例说明。且符号“≤”也可以是“《”,这是因为在取值为门限值时,归于大于一侧还是小于一侧从总体的性能差别不大,类似的,不失一般性,在以下的叙述中对门限值的处理不再另行说明),将第三比特序列的第0~第e0-e1-1个比特作为打孔比特,第e0-e1~第e0-1个比特作为rv1,第e0~n

0-1个比特作为缩短比特;

120.2.当e0-e1>δ*n0(当上述的“≤”为“《”时,这里的“》”则是“≥”),将第四比特序列的第0~第δ*n

0-e1-1个比特作为打孔比特,第δ*n

0-e1~第δ*n

0-1个比特作为rv1,并将第二比特序列的第δ*n0~n0-1个比特作为缩短比特。

121.当初传的速率匹配方式为重复时,将第二比特序列前n0个比特经过子块交织得到第三比特序列,将第二比特序列前n0/2个比特经过子块交织得到第四比特序列:

122.当e1《1/4*e0(即β=1/4),将第一循环缓存中的第n0-e1~第n0-1个比特作为rv1;

123.当e1》=1/4*e0且e1《e0,执行如下判断操作:

124.1.当n0-e1≤n0/2(即δ=1/2),将第三比特序列的第0~第n0-e1-1个比特作为打孔比特,第n0-e1~第n0-1个比特作为rv1;

125.2.当n0-e1>n0/2,将第四比特序列的第0~第n0/2-e1-1个比特作为打孔比特,第n0/2-e1~第n0/2-1个比特作为rv1,并将第二比特序列的第n0/2~n0-1个比特作为缩短比特。

126.当初传的速率匹配方式是重复或缩短时,也可以采用统一的方式进行操作而不区

分初传的速率匹配方式究竟是重复还是缩短,具体地,将第二比特序列前n0个比特经过子块交织得到第三比特序列,将第二比特序列前n0/2个比特经过子块交织得到第四比特序列:

127.当e1《1/4*e0(即β=1/4),将第一循环缓存中的第min(n0,e0)-e1~第min(n0,e0)-1个比特作为rv1;

128.当e1》=1/4*e0且e1《e0,执行如下操作:

129.1.当min(n0,e0)-e1≤n0/2(即δ=1/2),将第三比特序列的第0~第min(n0,e0)-e1-1个比特作为打孔比特,第min(n0,e0)-e1~第min(n0,e0)-1个比特作为rv1,第min(n0,e0)~n

0-1个比特作为缩短比特,其中,当n0≤e0时,缩短比特数量为0;

130.2.当min(n0,e0)-e1>n0/2,将第四比特序列的第0~第n0/2-e1-1个比特作为打孔比特,第n0/2-e1~第n0/2-1个比特作为rv1,并将第二比特序列的第n0/2~n0-1个比特作为缩短比特。

131.实施方式b:

132.当初传的速率匹配方式为重复或缩短时,将第二比特序列前n0个比特经过子块交织得到第三比特序列:

133.当e1《1/4*e0(即β=1/4)或者min(n0,e0)-e1>n0/2(即δ=1/2),将第一循环缓存中的第min(n0,e0)-e1~第min(n0,e0)-1个比特作为rv1;

134.当e1》=1/4*e0且min(n0,e0)-e1≤n0/2,将第三比特序列的第0~第min(n0,e0)-e1-1个比特作为打孔比特,第min(n0,e0)-e1~第min(n0,e0)-1个比特作为rv1,第min(n0,e0)~n0-1个比特作为缩短比特,其中,当n0≤e0时,缩短比特数量为0。

135.实施方式c:

136.当初传的速率匹配方式为缩短时,将第二比特序列前n0个比特经过子块交织得到第三比特序列,将第二比特序列前n0/2个比特经过子块交织得到第四比特序列:

137.当e1《1/4*e0(即β=1/4),将第一循环缓存中的第e0-e1~第e0-1个比特作为rv1;

138.当e1》=1/4*e0且e1《1/2*e0(即δ=1/2),将第四比特序列的第0~第n0/2-e1-1个比特作为打孔比特,第n0/2-e1~第n0/2-1个比特作为rv1,并将第二比特序列的第n0/2~n0-1个比特作为缩短比特,注意这里的第四比特序列长度为n0/2,这种方式下重传的速率匹配方式既包含打孔又包含缩短,通过这样的设计,可以有效的提升不同码长或不同码率下的性能稳定性;

139.当e1》=1/2*e0(即δ=1/2)且e1《e0,将第三比特序列的第0~第e0-e1-1个比特作为打孔比特,第e0-e1~第e0-1个比特作为rv1,第e0~n0-1个比特作为缩短比特;

140.当初传的速率匹配方式为重复时,将第二比特序列前n0个比特经过子块交织得到第三比特序列,将第二比特序列前n0/2个比特经过子块交织得到第四比特序列:

141.当e1《1/4*e0(即β=1/4),将第一循环缓存中的第n0-e1~第n0-1个比特作为rv1;

142.当e1》=1/4*e0且e1《1/2*n0(即δ=1/2),将第四比特序列的第0~第n0/2-e1-1个比特作为打孔比特,第n0/2-e1~第n0/2-1个比特作为rv1,并将第二比特序列的第n0/2~n0-1个比特作为缩短比特,注意这里的第四比特序列长度为n0/2,这种方式下重传的速率匹配方式既包含打孔又包含缩短,通过这样的设计,可以有效的提升不同码长或不同码率下的性能稳定性:

143.当e1》=1/2*n0且e1《e0,将第三比特序列的第0~第n0-e1-1个比特作为打孔比特,第n0-e1~第n0-1个比特作为rv1;

144.与实施方式a类似,也可以不区分初传的速率匹配方式为重复或缩短,具体地,将第二比特序列前n0个比特经过子块交织得到第三比特序列,将第二比特序列前n0/2个比特经过子块交织得到第四比特序列:

145.当e1《1/4*e0(即β=1/4),将第一循环缓存中的第min(e0,n0)-e1~第min(e0,n0)-1个比特作为rv1;

146.当e1》=1/4*e0且e1《1/2*min(e0,n0)(即δ=1/2),将第四比特序列的第0~第n0/2-e1-1个比特作为打孔比特,第n0/2-e1~第n0/2-1个比特作为rv1,并将第二比特序列的第n0/2~n0-1个比特作为缩短比特,注意这里的第四比特序列长度为n0/2,这种方式下重传的速率匹配方式既包含打孔又包含缩短,通过这样的设计,可以有效的提升不同码长或不同码率下的性能稳定性:

147.当e1》=1/2*min(e0,n0)且e1《e0,将第三比特序列的第0~第min(e0,n0)-e1-1个比特作为打孔比特,第min(e0,n0)-e1~第min(e0,n0)-1个比特作为rv1,第min(e0,n0)~n0-1个比特作为缩短比特,其中,当n0≤e0时,缩短比特数量为0。

148.可选的,在确定速率匹配比特中的打孔比特的位置后,还可以预冻结部分比特位置,但与现有nr协议确定预冻结比特位置的方式不同,本技术提出一种新的确定预冻结比特位置的方法,具体如下:

149.1.第i个子块中被打孔的比特数量pi等于或超过第一预设值,则将该子块对应的其它极化子信道确定为预冻结极化子信道,其中,所述第一预设值可以是常数,例如1、10、16,甚至还可以是子块长度等;或者

150.2.第i个子块中被打孔的比特数量pi超过该子块对应的极化子信道总数的预设比例,则将该子块对应的其它极化子信道确定为预冻结极化子信道,其中,所述预设比例可以是1/16,1/8,1/4,1/2等,或者

151.3.第i个子块中被打孔的比特数量pi等于或超过第二预设值,则将该子块对应的其它极化子信道确定为预冻结极化子信道,并将第i 1~第i g个子块对应的所有极化子信道确定为预冻结极化子信道,其中,所述第二预设值可以是常数,例如1、10、16,甚至还可以是子块长度,所述k可以是常数,如2,3,4等。通过这种方式,可以有效的均衡不同码率不同码长下的性能。注意,这里的i、i 1、i g均指子块交织以后的子块顺序。

152.当然,若某一子块对应的所有极化子信道均被打孔,则该子块中不存在预冻结的极化子信道。

153.具体来说,如图3所示实施例,可采用如下的操作:

154.操作330a:获取子信道集合q1,q1中包括k个元素,这些元素是初传中用于放置k个待编码比特的k个子信道的序号,这可以在操作310一并获取;

155.操作330b:将q1中的所有子信道序号增加n0,获取子信道集合q2,其中,q2(i)=q1(i) n0,其中i=0,1,

…

,k-1;不失一般性,本技术中还是以子信道序号从0开始编号为例说明。如果是从1开始编号,相应加1即可,不再赘述;

156.操作330c:根据长度为n1=2*n0的可靠度排序序列以及重传的速率匹配方式确定在母码长度为n1时k1个待编码比特的子信道集合q3。q3中的元素满足:q3(i)《n0或者q3(i)

∈q2其中i=0,1,

…

,k1-1,这里k1=k k_adjust,k_adjust为新增的待编码比特,其值为0或cbcrc1,cbcrc1可以为0也可以不为0,不为0的原因是考虑到重传的时候有可能需要重新进行一些crc校验以提高重传的可靠性,cbcrc1取值可以由如下任一方式确定:

157.·

方式一:设置为0;

158.·

方式二:基于条件判断,当n0=4096,设置为第一预设值,例如6,8,16,24等,否则设置为0;

159.·

方式三:基于条件判断,当n0=4096,且e1》=alpha*e0,设置为第一预设值,第一预设值可以设置为例如6,8,16,24等,否则设置为0,其中alpha取值可以为[1/2,1]区间内任一值,例如1/2,3/4,7/8,1等;

[0160]

cbcrc1可以和初传的crc采用相同的方式,也可以用短一些的crc多项式,例如,初传用24比特的crc,重传则采用8比特的crc(即cbcrc1=8);

[0161]

操作330d:确定扩展待编码比特集合qext,其中的元素为q3中小于n0的元素;

[0162]

当cbcrc1取值方式为上述的方式二且取值不为0时,还需要执行如下的操作330e0(图中未示出)。需要指出的是,cbcrc1为0的时候当然也可以执行操作330e0,但对结果没有影响,因此一般建议当cbcrc1为0时不执行操作330e0。

[0163]

操作330e0:

[0164]

当|qchk|=0(也即|qext|=cbcrc1),则cbcrc1的取值调整为0,否则不调整;

[0165]

可选的,当|qchk|≠0,cbcrc1的取值还可以进行进一步的判断调整,例如:

[0166]

·

0《|qchk|《=chk_threshold(chk_threshold为预设的门限值,典型取值可以为10,50等),则cbcrc1的取值调整为第二预设值,第二预设值小于第一预设值,例如由8调整为6或者调整为3等等;

[0167]

操作330e:确定复制比特集合qchk=q2\(q3\qext),其中的“\”代表的是集合的差运算,即a\b表示所有属于a且不属于b的元素;

[0168]

操作330f:选取部分或全部qchk中的子信道上的比特值逐个复制到对应的qext的子信道上。图4给出了一个示意图:在qext中先选出cbcrc1个子信道用于放置crc比特(cbcrc1=0的时候此步骤省略),从qchk中选取|qext|-cbcrc1个子信道上的比特复制到qext中余下的|qext|-cbcrc1个子信道,这cbcrc1个crc比特即用于对这|qext|-cbcrc1个复制比特进行crc校验,其中操作|a|表示取集合a的元素个数。qext中先选出cbcrc1个子信道以及从qchk中选取|qext|-cbcrc1个子信道的方法可以是按自然序从前到后或从后到前依次选取,也可以是按照这些子信道的可靠度从前到后或从后到前依次选取的,它们的取法可以一致也可以不一致,这里不做限定;当|qext|较大而|qchk|较小时,也需要在qext中选取|qchk|个位置用于放置复制比特时,选取的方法也是类似的,即既可以是按自然序从前到后或从后到前依次选取,也可以是按照这些子信道的可靠度从前到后或从后到前依次选取的。无论是哪种选取方法,只需发送端和接收端约定统一即可。

[0169]

操作330g:根据上述确定的位置和取值对k个待编码比特进行母码长度为n1的polar码重传编码,得到极化编码后的第二比特序列,然后根据重传的速率匹配方式从第二比特序列的前n0个比特中得到rv1。具体从这前n0个比特中得到rv1的方式与从第一比特序列中得到rv0的方式可以一致。

[0170]

为更好的说明上述步骤,下面举一个具体的例子。

[0171]

假设n0=64,n1=128,不妨直接采用3gpp 5g nr标准中的可靠度排序序列:

[0172]

n0=64:s0=[0,1,2,4,8,16,32,3,5,9,6,17,10,18,12,33,20,34,24,36,7,11,40,19,13,48,14,21,35,26,37,25,22,38,41,28,42,49,44,50,15,52,23,56,27,39,29,43,30,45,51,46,53,54,57,58,60,31,47,55,59,61,62,63];

[0173]

n1=128:s1=[0,1,2,4,8,16,32,3,5,64,9,6,17,10,18,12,33,65,20,34,24,36,7,66,11,40,68,19,13,48,14,72,21,35,26,80,37,25,22,38,96,67,41,28,69,42,49,74,70,44,81,50,73,15,52,23,76,82,56,27,97,39,84,29,43,98,88,30,71,45,100,51,46,75,104,53,77,54,83,57,112,78,85,58,99,86,60,89,101,31,90,102,105,92,47,106,55,113,79,108,59,114,87,116,61,91,120,62,103,93,107,94,109,115,110,117,118,121,122,63,124,95,111,119,123,125,126,127]。

[0174]

假设e0=60,k=50,因此r=5/6,r_threshold=7/16,因此需要用ir方式构造rv1,初传采用缩短的速率匹配方式。

[0175]

q1=[6 7 10 11 12 13 14 15 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59];

[0176]

相应的:

[0177]

q2=[70 71 74 75 76 77 78 79 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123];

[0178]

假设e1正好等于e0,也等于60,在子信道64~127中也同样采用缩短的速率匹配方式,因此所有缩短的子信道为q

rm

=[60 61 62 63 124 125 126 127];

[0179]

k_adjust为0时:

[0180]

q3=[31 46 47 51 53 54 55 57 58 59 75 77 78 79 83 85 86

[0181]

87 89 90 91 92 93 94 95 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123];

[0182]

qext=[31 46 47 51 53 54 55 57 58 59];

[0183]

qchk=[70 71 74 76 81 82 84 88 97 98];

[0184]

若cbcrc1=0,则将qchk中的子信道的比特复制到qext中,可以就按上述的顺序依次复制,也可以在考虑译码顺序的前提下将qchk中较大序号的子信道的比特复制到qext中序号比较小的子信道,即子信道98的比特复制到子信道31,子信道97的比特复制到子信道46,依次类推,子信道70的比特复制到子信道59。

[0185]

若cbcrc1=8,则可将qext中除31、46之外的8个子信道用于承载新增的crc比特。而qchk中选取子信道70和71的值分别复制到子信道46和31即可。这8个crc比特即用于对这2个比特进行crc校验。可以看出,在这种情况下8个crc比特显然冗余了,所以实际应用中,还有一种可能,即待编码比特的数量在第一区间时不需要新增crc比特,而在第二区间则需要新增crc比特,或者在第三区间时新增较少的crc比特,而在第四区间则新增较多的crc比特。具体区间划分、是否新增crc以及到底新增多少crc比特,只需要发送端和接收端统一即可。

[0186]

k_adjust为8时,q3可取为:

[0187]

q3=[29 30 31 43 45 46 47 51 53 54 55 57 58 59 71 75 77 78 79 83 84 85 86 87 88 89 90 91 92 93 94 95 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123];

[0188]

相应的,相应的q2、qext、qchk为:

[0189]

q2=[70 71 74 75 76 77 78 79 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123];

[0190]

qext=[29 30 31 43 45 46 47 51 53 54 55 57 58 59];

[0191]

qchk=[70 74 76 81 82 97]。

[0192]

可将qext这个47、51、53、54、55、57、58、59这8个子信道用于承载新增的crc比特,而将qchk中6个子信道上的比特复制到29、30、31、43、45、46这6个子信道上,具体地,子信道70的比特复制到子信道46,子信道74的比特复制到子信道45,依次类推,子信道97的比特复制到子信道29。

[0193]

可以看到,即使对于相同的cbcrc1,k_adjust的取值不同也会影响到最后的结果。因此必须在发送端和接收端统一。

[0194]

操作340:将rv0和rv1级联输入第二循环缓存;

[0195]

操作350:进一步重传。

[0196]

若第一次重传发送的rv1已经正确解码,则无需进行操作340、350,因此以虚线表示,若第一次重传还是未能正确解码,则还需进一步重传,如前所述,这时候采用cc重传,这时发送端可直接从第二循环缓存中读取相应的版本发送即可。例如,第x次传输的比特可以是上一次传输的最后一个比特位置之后的第一个比特位开始读取的ex个比特(空口传输的比特数),也可以是上一次传输所用rv版本(rv0或者rv1)的最后一个比特位置之后的第一个比特位开始读取的ex个比特,x大于1。

[0197]

无论是初传还是重传,为克服信道影响,还可以对经过速率匹配后的发送比特进一步进行信道交织的操作,具体的可以将待发送比特输入信道交织器然后发送交织后的比特,一般可选该交织器为行列交织器,按行写入、按列读出,或者按列写入、按行读出;为了让发送比特在交织器中分布更均匀、保证随机性能,所述行列交织器的行数可以是14,则第x次传输的列数为其中x为大于或等于0的整数,x=0的时候表示是初传,x为其他值的时候表示是第几次重传。

[0198]

虽然如图2中以分开的多个步骤确定rv1,实际应用中可以合并其中的部分步骤或者在不影响最终结果的前提下对计算的前后顺序做出改变。

[0199]

以上对图2的实施例描述是针对发送端的,但事实上,接收端的操作也极其类似,区别在于操作310中不是进行编码,而是进行解码,得到的是解码后的第一比特序列,简单来说,就是接收端接收待解码信号,然后根据前述实施例的方法和原则确定rv0和rv1,然后根据rv0和rv1在各次重传中用于ir合并或cc合并对待解码信号进行解码解调等操作,从而得到并输出解码结果。当然操作350就不再需要了。因此不再赘述。

[0200]

如图5所示,本技术实施例中还提供一种发送装置600。图2、图3所示的重传方法中的部分或全部可以通过硬件来实现也可以通过软件来实现。

[0201]

对于发送装置600,基于图2-4所示的重传方法的同一发明构思,该发送装置600用

于执行图2-4所示的重传方法。当通过硬件实现时,发送装置600包括:输入接口电路601,用于获取待传传输块;逻辑电路602,用于执行上述图2-4所示的重传方法,具体请见前面方法实施例中的描述,此处不再赘述;输出接口电路603,用于输出编码后的序列或者重传的序列。进一步地,编码后的序列或者重传的序列输出给收发器620,收发器620对编码后的序列或者重传的序列进行相应处理(包括但不限于数模变换和/或变频等处理)后通过天线630发送出去。可选的,发送装置600在具体实现时可以是芯片或者集成电路。

[0202]

可选的,当上述实施例的重传方法中的部分或全部通过软件来实现时,如图7所示,发送装置700包括:存储器701,用于存储程序;处理器702,用于执行存储器701存储的程序,当程序被执行时,使得发送装置700可以实现上述实施例提供的重传方法。

[0203]

可选的,上述存储器701可以是物理上独立的单元,也可以与处理器702集成在一起。

[0204]

可选的,当上述实施例的分段、重传方法中的部分或全部通过软件实现时,发送装置700也可以只包括处理器702。用于存储程序的存储器701位于发送装置700之外,处理器702通过电路/电线与存储器701连接,用于读取并执行存储器701中存储的程序。

[0205]

基于图2-4所示的重传方法,如图7所示,本技术实施例还提供了一种发送设备800,用于执行图2-4所示的重传方法,发送设备800包括:

[0206]

获取单元801,用于获取待传传输块;

[0207]

编码单元802,用于对每一段传输块进行编码或者重传编码;

[0208]

确定单元803,用于按照如图2-4所示实施例的重传方法确定rv0版本和rv1版本。

[0209]

与发送端相对应,接收端的装置也可以进行类似的设计。

[0210]

如图8所述,接收装置900包括:输入接口电路901用于输入接收信号,逻辑电路902用于执行前述的重传方法用于解码,以获取解码结果;输出接口电路903用于输出解码结果。接收装置900还可以包括收发器920通过天线930获取接收信号。在具体实现时可以是芯片或者集成电路。

[0211]

可选的,当上述实施例的重传方法中的部分或全部通过软件来实现时,如图9所示,接收装置1000包括:存储器1001,用于存储程序;处理器1002,用于执行存储器1001存储的程序,当程序被执行时,使得接收装置1000可以实现上述实施例提供的重传方法。

[0212]

可选的,上述存储器1001可以是物理上独立的单元,也可以处理器1002集成在一起。

[0213]

可选的,当上述实施例的重传方法中的部分或全部通过软件实现时,接收1000也可以只包括处理器1002。用于存储程序的存储器1001位于接收装置1000之外,处理器1002通过电路/电线与存储器1001连接,用于读取并执行存储器1001中存储的程序。

[0214]

处理器702和/或处理器1002可以是中央处理器(central processing unit,cpu),网络处理器(network processor,np)或者cpu和np的组合。

[0215]

处理器702和/或处理器1002还可以进一步包括硬件芯片。上述硬件芯片可以是专用集成电路(application-specific integrated circuit,asic),可编程逻辑器件(programmable logic device,pld)或其组合。上述pld可以是复杂可编程逻辑器件(complex programmable logic device,cpld),现场可编程逻辑门阵列(field-programmable gate array,fpga),通用阵列逻辑(generic array logic,gal)或其任意组

合。

[0216]

上述实施例中的存储器可以包括易失性存储器(volatile memory),例如随机存取存储器(random-access memory,ram);存储器也可以包括非易失性存储器(non-volatile memory),例如快闪存储器(flash memory),硬盘(hard disk drive,hdd)或固态硬盘(solid-state drive,ssd);存储器还可以包括上述种类的存储器的组合。

[0217]

基于上述的重传方法,如图10所示,本技术实施例还提供了一种接收设备1100,接收装置1100用于执行前述的重传方法,接收装置1100包括:

[0218]

获取单元1101,用于获取接收信号;

[0219]

确定单元1102,用于按照如图2-4所示实施例的重传方法确定rv0版本和rv1版本;

[0220]

解码单元1103,用于对接收到的每一段传输块进行解码。

[0221]

本技术实施例还提供了一种计算机存储介质,存储有计算机程序指令,该计算机程序指令由计算机执行时,使得前述的重传方法被执行。

[0222]

本技术实施例还提供了一种包含指令的计算机程序产品,当其在计算机上运行时,使得前述的重传方法被执行。

[0223]

本领域内的技术人员应明白,本技术的实施例可提供为方法、系统、或计算机程序产品。因此,本技术可采用完全硬件实施例、完全软件实施例、或结合软件和硬件方面的实施例的形式。而且,本技术可采用在一个或多个其中包含有计算机可用程序代码的计算机可用存储介质(包括但不限于磁盘存储器、cd-rom、光学存储器等)上实施的计算机程序产品的形式。

[0224]

本技术是参照根据本技术实施例的方法、设备(系统)、和计算机程序产品的流程图和/或方框图来描述的。应理解可由计算机程序指令实现流程图和/或方框图中的每一流程和/或方框、以及流程图和/或方框图中的流程和/或方框的结合。可提供这些计算机程序指令到通用计算机、专用计算机、嵌入式处理机或其他可编程数据处理设备的处理器以产生一个机器,使得通过计算机或其他可编程数据处理设备的处理器执行的指令产生用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的装置。

[0225]

这些计算机程序指令也可存储在能引导计算机或其他可编程数据处理设备以特定方式工作的计算机可读存储器中,使得存储在该计算机可读存储器中的指令产生包括指令装置的制造品,该指令装置实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能。

[0226]

这些计算机程序指令也可装载到计算机或其他可编程数据处理设备上,使得在计算机或其他可编程设备上执行一系列操作步骤以产生计算机实现的处理,从而在计算机或其他可编程设备上执行的指令提供用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的步骤。

[0227]

在本技术实施例之外,本领域内的技术人员一旦得知了基本创造性概念,则可对这些实施例作出另外的变更和修改。所以,所附权利要求意欲解释为包括优选实施例以及落入本技术范围的所有变更和修改。

[0228]

显然,本领域的技术人员可以对本技术实施例进行各种改动和变型而不脱离本技术实施例的精神和范围。这样,倘若本技术实施例的这些修改和变型属于本技术权利要求及其等同技术的范围之内,则本技术也意图包含这些改动和变型在内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。