技术特征:

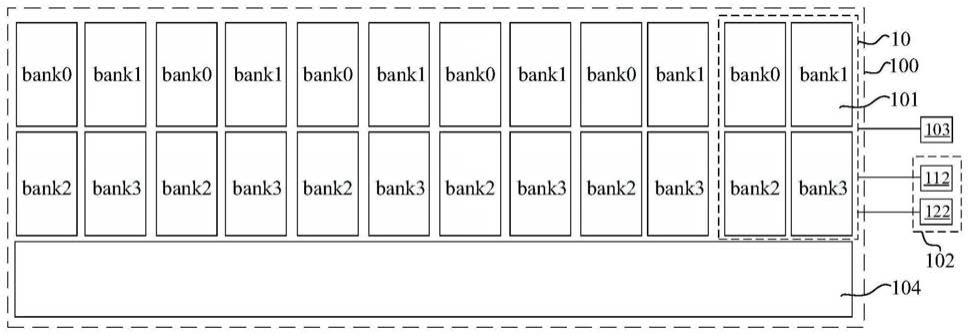

1.一种存储器,其特征在于,包括:控制芯片;多个存储芯片,多个所述存储芯片共用信道与所述控制芯片电连接,多个所述存储芯片被配置为,采用第一时钟信号的不同时钟沿与控制芯片进行信息交互,所述第一时钟信号具有第一时钟周期,且所述不同时钟沿包括连续的两个上升沿和/或连续的两个下降沿;多个所述存储芯片还被配置为,接收第二时钟信号并基于所述第二时钟信号区分所述不同时钟沿,且所述第二时钟信号具有的第二时钟周期大于所述第一时钟周期。2.如权利要求1所述的存储器,其特征在于,所述不同时钟沿包括连续的第一上升沿、第一下降沿、第二上升沿以及第二下降沿;多个所述存储芯片包括:第一存储芯片组和第二存储芯片组;所述第一存储芯片组中的存储芯片被配置为,采用所述第一上升沿和/或所述第一下降沿与所述控制芯片进行信息交互;所述第二存储芯片组中的存储芯片被配置为,采用所述第二上升沿和/或所述第二下降沿与所述控制芯片进行信息交互。3.如权利要求2所述的存储器,其特征在于,所述第一存储芯片组包括第一存储芯片和第二存储芯片,所述第一存储芯片在所述第一上升沿与所述控制芯片进行信息交互,所述第二存储芯片在所述第一下降沿与所述控制芯片进行信息交互;所述第二存储芯片组包括第三存储芯片和第四存储芯片,所述第三存储芯片在所述第二上升沿与所述控制芯片进行信息交互,所述第四存储芯片在所述第二下降沿与所述控制芯片进行信息交互。4.如权利要求2所述的存储器,其特征在于,所述第一时钟周期等于所述第二时钟周期的1/2倍。5.如权利要求1所述的存储器,其特征在于,每一所述存储芯片包括至少一个通道,所述通道包括:多个存储块,每一所述存储块包括多个存储单元,多个所述存储块被配置为交替进行读写操作;命令端口,所述命令端口被配置为在的对应时钟沿接收命令信号,所述命令信号用于控制所述存储块的读写操作;数据端口,所述数据端口被配置为,在对应时钟沿接收待写入到所述存储块的数据信号或者发送数据信号;所述命令端口包括行地址端口和列地址端口,所述行地址端口用于接收目标存储单元所在位置的行地址信号,所述列地址端口用于接收目标存储单元所在位置的列地址信号,所述目标存储单元为所述多个存储单元中选中的存储单元。6.如权利要求5所述的存储器,其特征在于,所述命令信号包括激活命令以及与每一所述激活命令对应的读命令;所述通道还被配置为,所述命令端口接收针对一所述存储块的所述激活命令后,所述命令端口接收与所述激活命令对应的所述读命令。7.如权利要求6所述的存储器,其特征在于,所述通道还被配置为,在所述命令端口接收所述读命令之后,所述数据端口发送所述数据信号。8.如权利要求5所述的存储器,其特征在于,所述命令信号包括激活命令以及与每一所述激活命令对应的多个读命令;所述通道还被配置为,所述命令端口接收针对一所述存储块的所述激活命令后,所述命令端口在多个对应时钟沿接收一与所述激活命令对应的所述读命令,以使所述命令端口在连续多个对应时钟沿接收多个与所述激活命令对应的所述读命令。9.如权利要求8所述的存储器,其特征在于,所述通道还被配置为,所述数据端口在连续多个所述对应时钟沿分别发送多个所述数据信号,所述数据信号的数量与所接收到的所

述读命令的数量相同。10.如权利要求5所述的存储器,其特征在于,所述命令信号包括激活命令和与所述激活命令对应的读命令;所述通道还被配置为,所述命令端口交替接收针对不同所述存储块的激活命令后,所述命令端口交替接收与所述激活命令对应的所述读命令。11.如权利要求10所述的存储器,其特征在于,所述通道还被配置为,在所述命令端口接收所述读命令之后,所述数据端口交替发送与不同所述存储块对应的所述数据信号。12.如权利要求5所述的存储器,其特征在于,所述命令信号包括激活命令以及与每一所述激活命令对应的多个读命令;所述通道还被配置为,所述命令端口交替接收针对不同存储块的所述激活命令,且所述命令端口交替接收与每一所述激活命令对应的多个所述读命令。13.如权利要求6、8、10或12所述的存储器,其特征在于,所述激活命令包括所述行地址信号,所述读命令包括所述列地址信号;所述通道还被配置为:所述激活命令和所述读命令通过所述命令端口中的不同端口接收。14.如权利要求5所述的存储器,其特征在于,所述存储芯片包括多个所述通道,所述存储芯片还包括多个所述通道共用的共用电路。15.如权利要求14所述的存储器,其特征在于,所述存储芯片还包括:测试端口,在测试模式下,多个所述通道共用同一所述测试端口进行测试。16.如权利要求14所述的存储器,其特征在于,所述共用电路包括测试控制电路,所述测试控制电路用于对多个所述通道的测试控制。17.如权利要求1所述的存储器,其特征在于,多个所述存储芯片依次堆叠于所述控制芯片上,所述信道包括硅通孔结构。

技术总结

本发明实施例提供一种存储器,包括:控制芯片;多个存储芯片,多个所述存储芯片共用信道与所述控制芯片电连接,多个所述存储芯片被配置为,采用第一时钟信号的不同时钟沿与控制芯片进行信息交互,所述第一时钟信号具有第一时钟周期,且所述不同时钟沿包括连续的两个上升沿和/或连续的两个下降沿;多个所述存储芯片还被配置为,接收第二时钟信号并基于所述第二时钟信号区分所述不同时钟沿,且所述第二时钟信号具有的第二时钟周期大于所述第一时钟周期。本发明实施例能够减少存储器的信道数量。量。量。

技术研发人员:寗树梁 何军 应战 刘杰

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:2020.08.26

技术公布日:2022/2/28

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。