1.本发明实施例涉及半导体技术领域,特别涉及一种存储器。

背景技术:

2.动态随机存取存储器(dynamic random access memory,dram)是计算机中常用的半导体存储器件,由许多重复的存储单元组成。每个存储单元通常包括电容器和晶体管,晶体管的栅极与字线相连、漏极与位线相连、源极与电容器相连,字线上的电压信号能够控制晶体管的打开或关闭,进而通过位线读取存储在电容器中的数据信息,或者通过位线将数据信息写入到电容器中进行存储。

3.随着dram应用的领域越来越多,如dram越来越多地应用于各种领域,用户对于dram性能指标的要求越来越高,且会由于应用领域不同而对dram有着不同的要求。

技术实现要素:

4.本发明实施例解决的技术问题为提供一种存储器,用于改善数据浪费的问题,提高存储器的存储速度。

5.为解决上述问题,本发明实施例提供一种存储器,包括:存储芯片,所述存储芯片包括至少一个通道,所述通道包括:多个存储块,每一所述存储块包括多个存储单元,多个所述存储块被配置为交替进行读写操作;命令端口,所述命令端口被配置为在命令时钟的预设沿接收命令信号,所述命令信号用于控制所述存储块的读写操作;数据端口,所述数据端口被配置为,在数据时钟的预设沿接收待写入到所述存储块的数据信号或者发送数据信号;其中,所述命令端口包括行地址端口和列地址端口,所述行地址端口用于接收目标存储单元所在位置的行地址信号,所述列地址端口用于接收目标存储单元所在位置的列地址信号,所述目标存储单元为所述多个存储单元中选中的存储单元。

6.另外,所述命令时钟和所述数据时钟为同一时钟信号。

7.另外,所述存储芯片为多个,每一所述存储芯片采用相同时钟信号,且各所述存储芯片的所述命令端口和所述数据端口均采用相同的所述预设沿接收或者发送信号。

8.另外,所述预设沿为时钟上升沿或者时钟下降沿。

9.另外,所述命令信号包括激活命令以及与每一所述激活命令对应的读命令;所述通道还被配置为,所述命令端口接收针对一所述存储块的所述激活命令后,所述命令端口接收与所述激活命令对应的所述读命令。

10.另外,所述通道还被配置为,在所述命令端口接收所述读命令之后,所述数据端口发送所述数据信号。

11.另外,所述命令信号包括激活命令以及与每一所述激活命令对应的多个读命令;所述通道还被配置为,所述命令端口接收针对一所述存储块的所述激活命令后,所述命令端口在多个所述预设沿中的每一所述预设沿接收一与所述激活命令对应的所述读命令,以使所述命令端口在连续多个所述预设沿接收多个与所述激活命令对应的所述读命令。

12.另外,所述通道还被配置为,所述数据端口在连续多个所述预设沿分别发送多个所述数据信号,所述数据信号的数量与所接受到的所述读命令的数量相同。

13.另外,所述命令信号包括激活命令和与所述激活命令对应的读命令;所述通道还被配置为,所述命令端口交替接收针对不同所述存储块的激活命令后,所述命令端口交替接收与所述激活命令对应的所述读命令。

14.另外,所述通道还被配置为,在所述命令端口接收所述读命令之后,所述数据端口交替发送与不同所述存储块对应的所述数据信号。

15.另外,所述命令信号包括激活命令以及与每一所述激活命令对应的多个读命令;所述通道还被配置为,所述命令端口交替接收针对不同存储块的所述激活命令,且所述命令端口交替接收与每一所述激活命令对应的多个所述读命令。

16.另外,所述激活命令包括所述行地址信号,所述读命令包括所述列地址信号;所述通道还被配置为:所述激活命令和所述读命令通过所述命令端口中的不同端口接收。

17.另外,还包括:控制芯片,所述控制芯片与所述存储芯片电连接,且多个所述存储芯片分别通过单独的信道与所述控制芯片电连接。

18.另外,多个所述存储芯片依次堆叠于所述控制芯片上,所述信道包括硅通孔结构。

19.另外,所述存储芯片包括多个所述通道,所述存储芯片还包括多个所述通道共用的共用电路。

20.另外,所述存储芯片还包括:测试端口,在测试模式下,多个所述通道共用同一所述测试端口进行测试。

21.另外,所述共用电路包括测试控制电路,所述测试控制电路用于对多个所述通道的测试控制。

22.与现有技术相比,本发明实施例提供的技术方案具有以下优点:

23.本发明实施例提供一种结构性能优越的存储器,由于行地址端口与列地址端口分开,因而可以实现行地址信号和列地址信号同时传输,避免了读命令传输完成后才能传输激活命令信号的问题,因此有利于避免在某些时间段上数据线未被占满的问题,保证数据线始终被数据占满,从而提高存储器的存储速度,改善存储器的存储性能。

附图说明

24.一个或多个实施例通过与之对应的附图中的图片进行示例性说明,这些示例性说明并不构成对实施例的限定,附图中具有相同参考数字标号的元件表示为类似的元件,除非有特别申明,附图中的图不构成比例限制。

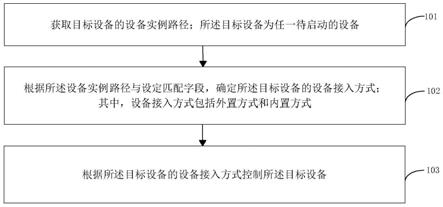

25.图1为本发明实施例提供的存储器中一个存储芯片的结构示意图;

26.图2为本发明实施例提供的包括多个存储芯片的存储器的结构示意图;

27.图3为本发明实施例提供的存储器对应的各工作信号的一种时序图;

28.图4为本发明实施例提供的存储器对应的各工作信号的另一种时序图。

具体实施方式

29.由背景技术可知,现有技术的存储器的性能有待提高。

30.分析发现,为了减少引脚数量目前的存储器采用同一端口接收行地址信号以及列

地址信号。该端口接收行地址信号期间无法接收列地址信号,在接收列地址信号期间无法接收行地址信号,为了实现数据信号的连续传输,以及为了得到更快的传输速度,通常需要搭配预取(pre-fetch)和/或突发(burst)等技术手段,这将增加每次读取数据的粒度(数据量大小)。尤其对于高带宽应用场景下的存储器来说,情况更甚,在有些应用下,粒度的大幅增加可能会导致总线上数据的浪费,灵活性较差。

31.为解决上问题,本发明实施提供一种存储器,将行地址端口和列地址端口分开,从而解决上述问题。

32.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合附图对本发明的各实施例进行详细的阐述。然而,本领域的普通技术人员可以理解,在本发明各实施例中,为了使读者更好地理解本技术而提出了许多技术细节。但是,即使没有这些技术细节和基于以下各实施例的种种变化和修改,也可以实现本技术所要求保护的技术方案。

33.图1为本发明实施例提供的存储器中一个存储芯片的结构示意图;图2为本发明实施例提供的包括多个存储芯片的存储器的结构示意图;图3为本发明实施例提供的存储器对应的各工作信号的一种时序图;图4为本发明实施例提供的存储器对应的各工作信号的另一种时序图。

34.参考图1至图3,本实施例中,存储器包括:存储芯片100,存储芯片100包括至少一个通道10,通道10包括:多个存储块101,每一存储块101包括多个存储单元,多个存储块101被配置为交替进行读写操作;命令端口102,命令端口102被配置为在命令时钟的预设沿接收命令信号,命令信号用于控制存储块101的读写操作;数据端口103,数据端口103被配置为,在数据时钟的预设沿接收待写入到存储块101的数据信号或者发送数据信号;命令端口102包括行地址端口112和列地址端口122,行地址端口112用于接收目标存储单元所在位置的行地址信号,列地址端口122用于接收目标存储单元所在位置的列地址信号,目标存储单元为多个存储单元中选中的存储单元。

35.需要注意的是,本实施例所称的命令端口包括传输命令信号和地址信号的端口,但也不限于此。

36.以下将结合附图对本实施例提供的存储器进行详细说明。

37.本实施例提供的存储器可以为动态随机存储器(dram)。

38.每一存储块101中的多个存储单元可以呈阵列式分布。本实施例中,以每一通道(channel)10包括4个存储块101作为示例,图1中以bank0、bank1、bank2以bank3示意出一通道10中的4个存储块101。可以理解的是,在其他实施例中,每一通道包括的存储块的数量也可以为其他任意数量个,例如为2个、6个等。

39.数据端口103用于接收待存入存储单元中的数据或发送从存储单元中读出的数据。

40.存储芯片100包括多个通道10,且存储芯片100还包括多个通道10共用的共用电路104。本实施例中,该共用电路104可以为测试控制电路,测试控制电路用于对多个通道10的测试控制。在其他实施例中,该共用电路也可以为温度传感器电路、模拟电路或者电荷泵电路中的至少一种。

41.存储器还可以包括:测试端口,且在测试模式下多个通道10共用同一测试端口进行测试。由于共用测试端口的设置,有利于减少存储器中端口的数量,从而降低采用探针卡

对存储器进行测试的难度,且降低探针卡的制造难度。

42.参考图2,存储器还可以包括:控制芯片114,控制芯片114与存储芯片100电连接,且多个存储芯片100分别通过单独的信道与控制芯片114电连接。

43.具体地,多个存储芯片100可以在控制芯片114上依次层叠设置,有利于提高存储密度且减小存储芯片100与控制芯片114的距离;或者,多个存储芯片100也可以在控制芯片114上并排设置,有利于减小存储器的纵向厚度。本实施例中,多个存储芯片100依次堆叠于控制芯片114上,且信道包括硅通孔结构(tsv,through silicon via)。

44.本实施例中,命令时钟和数据时钟为同一时钟信号,图3中以ck示意出该时钟信号的时序图。如此,有利于简化电路设计,避免由于命令时钟和数据时钟握手或同步产生的错误而导致的数据接收或发送错误,提高存储器的存储正确率。需要说明的是,在其他实施例中,命令时钟和数据时钟也可以为不同的时钟信号,相应的,需区分命令时钟的时钟沿以及数据时钟的时钟沿。

45.另外,本实施例中,存储芯片100为多个,每一存储芯片100采用相同的时钟信号,且各存储芯片100的命令端口和数据端口均采用相同的预设沿接收或者发送信号。该预设沿可以为时钟上升沿或者时钟下降沿中的至少一种。本实施例中,以该预设沿为时钟上升沿作为示例。

46.具体地,命令信号包括激活命令以及与每一激活命令对应的读命令。通道10还被配置为,命令端口接收针对一存储块的激活命令后,命令端口接收与激活命令对应的读命令。更具体地,激活命令包括行地址信号,其中行地址信号通过行地址端口112接收;读命令包括列地址信号,其中列地址信号通过列地址端口122接收。需要注意的是,激活命令和读命令中还可能包含除行地址信号或列地址信号以外的其他控制信号,这些其他控制信号用于帮助或辅助存储芯片100识别该命令是否是激活命令或读命令,且这些其他控制信号可通过除行地址端口112和列地址端口122之外的其他命令端口接收;如此,行地址端口112可以连续地接收行地址信号,列地址端口122可以连续地接收列地址信号。相应的,通道10还被配置为:激活命令和读命令通过命令端口102中的不同端口接收,从而可以实现激活命令和读命令的同时接收。

47.本实施例中,命令信号包括激活命令和与激活命令对应的读命令;通道还被配置为,命令端口交替接收针对不同存储块的激活命令后,命令端口交替接收激活命令对应的读命令。具体地,行地址端口交替接收针对不同存储块的激活命令后,列地址端口交替接收激活命令对应的读命令。

48.此外,通道还被配置为,在命令端口接收读命令之后,数据端口交替发送与不同存储块对应的数据信号。

49.以下将结合时序图对该存储器的工作原理进行说明。

50.图3中以ck示意出时钟信号,act示意出激活命令信号的时序图,rd示意出读命令信号的时序图,data示意出数据信号的时序图。其中,以bank0、bank1、bank2以bank3四个存储块作为示例,激活命令信号包括分别用于激活bank0、bank1、bank2以bank3的act0/act1/act2/act3,act0与bank0对应,act1与bank1对应,以此类推;读命令信号包括与bank0、bank1、bank2以bank3一一对应的rd0/rd1/rd2/rd3,数据信号包括data0/data1/data2/data3;激活命令act0与bank0、1个读命令rd0以及数据信号data0对应,激活命令act1与

bank1、1个读命令rd1以及数据信号data1对应,激活命令act2与bank2、1个读命令rd2以及数据信号data2对应,激活命令act3与bank3、与1个读命令rd3以及数据信号data3对应,即一激活命令对应一读命令。

51.如图3所示,命令端口102在时钟信号的上升沿接收到针对一存储块的激活命令act0后,命令端口102在上升沿接收与激活命令act0对应的1个读命令rd0;在命令端口102接收读命令rd0之后,数据端口103在时钟信号的上升沿发送数据信号data0。关于命令端口102接收到激活命令act1/act2/act3后的流程与前述类似。具体地,命令端口102中的行地址端口112在时钟信号的第一个上升沿接收激活bank0的激活命令act0,命令端口102中的行地址端口112在时钟信号的第二个上升沿接收激活bank1的激活命令act1,在时钟信号的第三个上升沿接收激活bank2的激活命令act2,在时钟信号的第四个上升沿接收激活bank3的激活命令act2;命令端口102中的列地址端口122在第n个上升沿接收与激活命令act0对应的读命令rd0,命令端口在第n 1个上升沿接收与激活命令act1对应的读命令rd1,在第n 2个上升沿接收与激活命令act2对应的读命令rd2,在第n 3个上升沿接收与激活命令act3对应的读命令rd3,其中,n为任意自然数。相应的,数据端口103在时钟信号的第m个上升沿发送与存储块bank0对应的数据信号data0,数据端口103在时钟信号的第m 1个上升沿发送与存储块bank1对应的数据信号data1,在第m 2个上升沿发送与bank2对应的数据信号data2,在第m 3个上升沿发送与bank3对应的数据信号data3,其中,m为任意自然数,且对于每一存储块而言,对应的m大于n。

52.需要说明的是,图3中以在连续的上升沿分别接收激活命令act0、act1、act2、act3作为示例,即在连续的上升沿分别接收不同存储块对应的激活命令,在其他实施例中,也可以在非连续的上升沿分别接收不同存储块对应的激活命令。

53.从图3中不难发现,由于行地址端口112与列地址端口122不共用,因此在列地址端口122接收读命令rd2期间,行地址端口112可以接收激活命令act2,如此,无需等待所有的读命令信号都接收完毕之后才能接收激活命令,使得数据总线能够被填满,即数据端口103可以连续传输数据,避免数据总线在一定时间段内出现的空闲问题,从而有利于提升存储器的存储速度。

54.在另一例子中,命令信号包括激活命令以及与每一激活命令对应的多个读命令;通道10还被配置为,命令端口102接收针对一存储块的激活命令后,命令端口102在多个预设沿中的每一预设沿接收一与激活命令对应的读命令,以使命令端口102在多个预设沿接收多个与激活命令对应的读命令。本实施例中,通道10还被配置为:在命令端口102接收读命令之后,数据端口103发送数据信号。其中,通道10还可以被配置为:数据端口103在连续多个预设沿分别发送多个数据信号,且数据信号的数量与所接收到的读命令的数量相同。

55.此外,每一激活命令与多个读命令对应;通道还可以被配置为,命令端口交替接收针对不同存储块的激活命令,且命令端口交替接收与每一激活命令对应的多个读命令。具体地,命令端口交替接收针对不同存储块的激活命令后,命令端口在多个预设沿中的每一预设沿接收一与激活命令对应的读命令,以使命令端口在连续多个预设沿接收多个与激活命令对应的读命令,直至命令端口接收与激活命令对应的多个读命令,之后,命令端口接收针对另一存储块的激活命令对应的多个读命令。

56.以下结合图4对该存储器的工作原理进行说明:

57.图4中以ck示意出时钟信号,act示意出激活命令信号的时序图,rd示意出读命令信号的时序图,data示意出数据信号的时序图。其中,激活命令信号包括分别与bank0、bank1、bank2以bank3一一对应的act0/act1/act2/act3,读命令信号包括rd0/rd1/rd2/rd3,数据信号包括data0/data1/data2/data3;用于激活bank0的激活命令act0与4个读命令rd0以及4个数据信号data0对应,用于激活bank1的激活命令act1与4个读命令rd1以及数据信号data1对应,以此类推,即一激活命令对应多个不同的读命令。

58.如图4所示,命令端口102在时钟信号的上升沿接收到针对一存储块的激活命令act0后,命令端口102在4个连续的上升沿接收与激活命令act0对应的4个读命令rd0,在命令端口102接收读命令rd0之后,数据端口103在时钟信号的上升沿发送四个数据信号data0。在接收到针对另一存储块的激活命令act1后,命令端口102在4个连续的上升沿接收与激活命令act1对应的4个读命令rd1,在命令端口102接收读命令rd1之后,数据端口103在时钟信号的上升沿发送四个数据信号data1,关于命令端口102接收到激活命令act2以及act3后的流程与前述类似。

59.需要说明的是,本实施例中,通道还被配置为:对于任意存储块,接收命令信号与接收对应的读命令信号的时间差大于或等于trcd,trcd为存储块在接收到命令信号之后可进行读操作所需的最短准备时间。具体地,关于trcd的定义为:从行有效到读/写命令发出之间的间隔被定义为trcd,即ras到cas的延迟,ras为行地址选通脉冲信号简称行地址信号,cas为列地址选通脉冲信号简称列地址信号,trcd可理解为行选通周期。如此,可以保证存储块在接收到读命令之前或接收到读命令时已经被完全激活,在接收到读命令时即可进行读操作,从而进一步的提高存储器的存储速度。

60.具体地,如图3及图4,对于bank0而言,act0与rd0之间的时间差为trcd;对于bank1而言,act1与rd1之间的时间差可以大于或等于trcd,关于bank2以及bank3的情形在此不再一一列举。不管一个激活命令对应一个读命令还是对应多个读命令,均可以通过合理的设置保证对于任意存储块,接收命令信号与接收对应的读命令信号的时间差大于或等于trcd。

61.本实施例提供的存储器中,不同的存储块采用相同的命令端口以及数据端口。在其他实施例中,不同的存储块也可以采用不同的命令端口以及不同的数据端口。

62.本实施例提供的存储器,由于行地址端口与列地址端口分开,因而可以实现行地址信号和列地址信号同时传输,避免由于命令时钟和数据时钟握手或同步产生的错误而导致的数据接收或发送错误,因此有利于避免在某些时间段上数据线未被占满的问题,保证数据线始终被数据占满,从而提高存储器的存储速度,改善存储器的存储性能。

63.本领域的普通技术人员可以理解,上述各实施方式是实现本发明的具体实施例,而在实际应用中,可以在形式上和细节上对其作各种改变,而不偏离本发明的精神和范围。任何本领域技术人员,在不脱离本发明的精神和范围内,均可作各自更动与修改,因此本发明的保护范围应当以权利要求限定的范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。