1.本发明涉及芯片技术领域,特别是涉及一种时钟丢失监测电路及实现方法。

背景技术:

2.现有技术中,在有功能安全需求的芯片当中,对周期性信号例如时钟,有正确性和安全性的要求,需要监测在系统运行过程中时钟是否丢失。

3.传统的监测时钟是否丢失的方式,一种方法是把时钟信号送到芯片外面观测,另一种办法是用不同的时钟进行计数,周期性的去比较计数器的值是否有发生变化,从而间接的判断时钟是否丢失。

4.在常见的芯片系统当中,存在很多不同的时钟,送给不同的模块。用传统的方式对所有的时钟进行丢失监测,成本较高,同时复杂度较高。

技术实现要素:

5.为了解决现有技术存在的不足,本发明的目的在于提供一种时钟丢失监测电路及实现方法,能够降低成本,同时响应速度快。

6.为实现上述目的,本发明提供的一种时钟丢失监测电路,包括延时元件,反相器,与门,带异步复位端的寄存器以及时钟检测寄存器,其中,所述延时元件与所述反相器连接,所述反相器与所述与门连接,所述与门与所述带异步复位端的寄存器连接,所述带异步复位端的寄存器与所述时钟检测寄存器连接;所述时钟检测寄存器,用于接收反相后的基准时钟信号和所述带异步复位端的寄存器输出的待监测信号,在基准时钟的下降沿检查寄存器的值。

7.进一步地,所述延时元件,用于当基准时钟的上升沿,经过延时元件时,产生带异步复位端寄存器的异步复位信号输出到所述带异步复位端的寄存器,将带异步复位端寄存器复位成0;所述带异步复位端的寄存器,用于接收高电平和时钟检查信号,输出待监测信号到所述时钟检测寄存器;所述反相器,用于将反相后的基准时钟延迟信号输出到所述与门,将反相后的基准时钟信号输出到时钟检测寄存器;所述与门,用于接收基准时钟信号和反向基准时钟延迟信号执行逻辑与操作,输出异步复位信号到所述带异步复位端的寄存器。

8.进一步地,所述带异步复位端的寄存器,还用于当有被监测时钟信号时,输出待监测信号为1的信号到所述时钟检测寄存器,当没有被监测时钟信号时,输出待监测信号为0的信号到所述时钟检测寄存器。

9.进一步地,所述时钟检测寄存器,还用于当进行基准时钟下降沿检查,寄存器的值为0时,输出时钟丢失信号作为中断上报。

10.进一步地,所述时钟检测寄存器,还用于当被监测时钟没有丢失的情况下,基准时

钟下降沿检查时,寄存器的值为1。

11.为实现上述目的,本发明还提供一种时钟丢失监测电路的实现方法,包括以下步骤,当基准时钟的上升沿,经过延时元件,产生寄存器的异步复位信号,将寄存器复位成0;当被监测时钟的上升沿到来时,将寄存器赋值成1;在基准时钟的下降沿检查寄存器的值,若检测到时钟丢失则输出中断。

12.进一步地,所述当基准时钟的上升沿,经过延时元件,产生寄存器的异步复位信号,将寄存器复位成0的步骤,还包括,基准时钟的上升沿经过延时元件后进行反向,将延迟后反向的基准时钟信号与基准时钟信号进行逻辑与操作,生成寄存器的异步复位信号。

13.更进一步地,所述在基准时钟的下降沿检查寄存器的值,若检测到时钟丢失则输出中断的步骤,还包括,当检查寄存器的值为0时,被监测时钟丢失;当检查寄存器的值为1时,被监测时钟未丢失。

14.为实现上述目的,本发明还提供一种计算机可读存储介质,其上存储有计算机程序,所述计算机程序运行时执行如上文所述的时钟丢失监测电路的实现方法的步骤。

15.本发明的时钟丢失监测电路及实现方法,具有以下有益效果:1)灵活性高,设计复杂度低,成本低,同时响应速度快。

16.2)逻辑单元非常少,安全性也更高。

17.本发明的其它特征和优点将在随后的说明书中阐述,并且,部分地从说明书中变得显而易见,或者通过实施本发明而了解。

附图说明

18.附图用来提供对本发明的进一步理解,并且构成说明书的一部分,并与本发明的实施例一起,用于解释本发明,并不构成对本发明的限制。在附图中:图1为根据本发明的时钟丢失监测电路图;图2为根据本发明的时钟丢失监测电路的实现方法流程图;图3为根据本发明的实施例一时钟丢失监测电路的波形图;图4为根据本发明的实施例一系统应用的电路图。

具体实施方式

19.以下结合附图对本发明的优选实施例进行说明,应当理解,此处所描述的优选实施例仅用于说明和解释本发明,并不用于限定本发明。

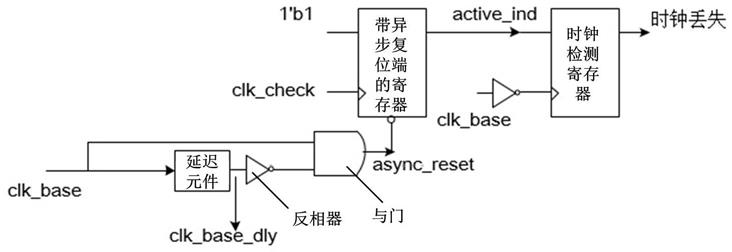

20.实施例1图1为根据本发明的时钟丢失监测电路图,如图1所示,本发明的时钟丢失监测电路,包括延时元件,反相器,与门,带异步复位端的寄存器以及时钟检测寄存器,其中,所述延时元件与所述反相器连接,所述反相器与所述与门连接,所述与门与所述带异步复位端的寄存器连接,所述带异步复位端的寄存器与所述时钟检测寄存器连接。

21.所述延时元件,用于当基准时钟的上升沿,经过延时元件时,产生带异步复位端寄存器的异步复位信号输出到所述带异步复位端的寄存器,将带异步复位端寄存器复位成0。

22.所述带异步复位端的寄存器,用于接收高电平1’b1和时钟检查信号,输出active_ind信号到所述时钟检测寄存器。

23.优选地,所述带异步复位端的寄存器,还用于当被监测时钟clk_check的上升沿到来时,将带异步复位端寄存器赋值成1,输出active_ind为1的信号到所述时钟检测寄存器。

24.优选地,所述带异步复位端的寄存器,还用于当有clk_check时,active_ind输出为1,没有clk_check时,active_ind输出为0。

25.所述时钟检测寄存器,用于接收反相后的基准时钟信号和所述带异步复位端的寄存器输出的active_ind,在基准时钟的下降沿检查寄存器的值。

26.优选地,所述时钟检测寄存器,还用于当被监测时钟丢失的情况发生时,基准时钟下降沿检查时,寄存器的值为0,时钟丢失信号作为中断上报;当被监测时钟没有丢失的情况下,基准时钟下降沿检查时,寄存器的值为1。

27.本发明实施例中,下降沿将active_ind 输出到q端,如果是1,就是没有丢失,如果是0就是丢失。

28.所述反相器,用于将反相后的基准时钟延迟信号输出到所述与门,将反相后的基准时钟信号输出到时钟检测寄存器。

29.所述与门,用于接收基准时钟信号和反向基准时钟延迟信号执行逻辑与操作,输出异步复位信号到所述带异步复位端的寄存器。

30.本发明实施例中,所述与门将clk_base和clk_base_dly取反后进行与操作。

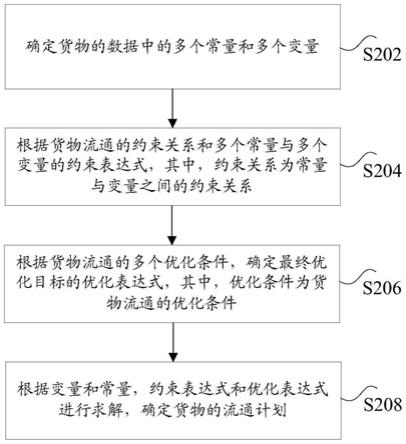

31.实施例2图2为根据本发明的时钟丢失监测电路的实现方法流程图,下面将参考图2,对本发明的时钟丢失监测电路的实现方法进行详细描述。

32.在步骤201,当基准时钟的上升沿,经过延时元件,产生寄存器的异步复位信号,将寄存器复位成0。

33.优选地,基准时钟的上升沿经过延时元件后进行反向,将延迟后反向的基准时钟信号与基准时钟信号进行逻辑与操作,生成寄存器的异步复位信号。

34.在步骤202,当被监测时钟的上升沿到来时,将寄存器赋值成1。

35.在步骤203,在基准时钟的下降沿检查寄存器的值,若检测到时钟丢失则输出中断。

36.优选地,当检查寄存器的值为0时,被监测时钟丢失;当检查寄存器的值为1时,被监测时钟未丢失。

37.实施例3如图3所示,本发明实施例中,根据奈奎斯特采样定律,clk_base的一半(高电平)比clk_check慢一倍以上就可以,在半个clock cycle后,由上升沿转成下降沿。只要delay的时间满足dff(data flip-flop,数据触发器)的重置最小脉冲宽度即可,从逻辑层面讲,对延迟时间尽可能小,可以一级buffer,也可以一个delay cell。dff的异步复位,会将active_ind复位成复位值。

38.实施例4

如图4所示,本发明实施例中,模块ip1 、模块ip2、

……

、模块ipn-1、模块ipn,根据系统应用,系统应用需要检查哪个clock是否丢失,就选择到哪路clock。不同模块的时钟经过时钟丢失监测单元的选择器(decoder)选出一个clock,作为时钟丢失检测模块中的clk_check 输入。如果发生了时钟丢失,作为异常事件输出中断。对于异常事件来讲,通知cpu发生了此异常事件,cpu根据系统应用执行重启系统,或点亮一个信号灯,或蜂鸣等操作。

39.本发明提供的时钟丢失监测电路,灵活性高,设计复杂度低,成本低,同时响应速度快。因为所用的逻辑单元非常少,安全性也更高。

40.本发明提供的一种时钟丢失监测电路及实现方法,能够成本更低,响应速度更快。

41.本发明的一个实施例中,还提供一种计算机可读存储介质,其上存储有计算机程序,所述计算机程序运行时执行如上文所述的时钟丢失监测电路实现方法的步骤。

42.本领域普通技术人员可以理解:以上所述仅为本发明的优选实施例而已,并不用于限制本发明,尽管参照前述实施例对本发明进行了详细的说明,对于本领域的技术人员来说,其依然可以对前述各实施例记载的技术方案进行修改,或者对其中部分技术特征进行等同替换。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。