储存器装置和操作储存器装置的方法

1.相关申请的交叉引用

2.本技术要求于2020年8月10日在韩国知识产权局提交的韩国专利申请no.10-2020-0099602的优先权,其公开内容以引用方式全部并入本文中。

技术领域

3.与示例实施例一致的方法、设备和系统一般地涉及储存器,并且更具体地,涉及储存器装置和操作储存器装置的方法。

背景技术:

4.储存器装置是用于根据诸如计算机、智能电话和/或智能平板的主机装置的控制来存储数据的装置。储存器装置包括用于在磁盘上存储数据的装置(诸如硬盘驱动器(hdd))和用于在半导体存储器上存储数据的装置(诸如固态驱动器(ssd)和存储卡),即,包括非易失性存储器。

5.包括非易失性存储器的储存器装置的使用正从个人计算机扩展到诸如数据服务器的商业计算机。随着储存器装置的扩展使用,在各个领域中需要储存器装置的各种功能和外形因素。储存器装置连接到各种主机并将高频信号传输到主机,并且因此需要增强从储存器装置输出的信号特性。

技术实现要素:

6.一些示例实施例提供了一种能够增强从储存器装置输出的信号的信号完整性的储存器装置。

7.一些示例实施例提供了一种操作储存器装置的方法,其能够增强从储存器装置输出的信号的信号完整性。

8.根据示例实施例,一种储存器装置包括:设置在印刷电路板(pcb)上的多个非易失性存储器装置、连接器、储存器控制器和至少一个第一无源滤波器。连接器设置在pcb中并且包括多个连接端子。储存器控制器设置在pcb上,通过连接端子与外部主机通信并控制所述多个非易失性存储器装置。所述至少一个第一无源滤波器设置在pcb中,连接在连接器和储存器控制器之间,并对提供给储存器控制器的信号和从储存器控制器提供的信号执行均衡。

9.根据示例实施例,一种操作储存器装置的方法包括:在印刷电路板(pcb)上设置储存器控制器和多个非易失性存储器装置;在pcb中设置包括多个连接端子的连接器;在pcb中设置电连接储存器控制器和所述多个非易失性存储器装置的数据传输线;在pcb中在连接器和储存器控制器之间设置至少一个无源滤波器;使用至少一个无源滤波器对提供给储存器控制器的信号或从储存器控制器提供的信号执行均衡;以及使用储存器控制器通过连接器与外部主机进行通信。

10.根据示例实施例,一种储存器装置包括:设置在印刷电路板(pcb)上的多个非易失

性存储器装置、连接器、储存器控制器和至少一个无源滤波器。连接器设置在pcb中并且包括多个连接端子。储存器控制器设置在pcb上,通过连接端子与外部主机通信,并控制多个非易失性存储器装置。所述至少一个无源滤波器设置在pcb中,连接在连接器和储存器控制器之间,并且对提供给储存器控制器的信号或从储存器控制器提供的信号执行均衡。所述至少一个无源滤波器包括在第一节点和第二节点之间并联连接的滤波器电阻器和滤波器电容器。滤波器电阻器和滤波器电容器设置在pcb中。第一节点耦接到储存器控制器,第二节点耦接到连接器。

11.因此,在pcb中在连接器与储存器控制器之间设置至少一个无源滤波器,储存器控制器通过该连接器与外部主机通信,并且储存器控制器和该至少一个无源滤波器对从储存器控制器提供的信号或提供给储存器控制器的信号执行均衡。因此,从储存器控制器输出到主机的高频信号的信号完整性得到改善,并且因此,可降低储存器装置的功耗。

附图说明

12.根据以下参照附图对示例实施例的描述,上述及其它目的和特征将变得更加明显,在附图中:

13.图1是示出根据示例实施例的储存器系统的框图。

14.图2是示出根据示例实施例的图1中的主机的框图。

15.图3是示出根据示例实施例的图1中的储存器控制器的示例的框图。

16.图4是进一步示出用于图1的储存器系统的接口的示例的框图。

17.图5a示出根据示例实施例的图1中的连接器的上表面,图5b示出根据示例实施例的图1中的连接器的下表面。

18.图6示出根据示例实施例的图5a和图5b中的连接器的连接端子。

19.图7示出根据示例实施例的图1中的无源滤波器、储存器控制器和主机的关系。

20.图8示出根据示例实施例的图7中的第一滤波器的示例。

21.图9和图10分别是示出根据示例实施例的其上安装有储存器装置的pcb的平面图和截面图。

22.图11和图12是示出根据示例实施例的储存器装置的平面图和截面图。

23.图13是示出根据示例实施例的图1中的储存器装置的示例的框图。

24.图14示出根据示例实施例的其中在pcb中设置图13中的无源滤波器的示例。

25.图15示出根据示例实施例的其中在pcb中设置图13中的无源滤波器的另一示例。

26.图16是示出根据示例实施例的图1中的储存器装置的另一示例的框图。

27.图17是示出根据示例实施例的图1中的储存器装置中的非易失性存储器装置之一的框图。

28.图18示出根据示例实施例的图17的非易失性存储器装置中的存储器单元阵列的框图。

29.图19示出根据示例实施例的图18的存储器块之一的电路图。

30.图20示出图19的存储器块中的单元串的结构的示例。

31.图21和图22是用于解释根据示例实施例的储存器装置的操作的示图。

32.图23是示出根据示例实施例的操作储存器装置的方法的流程图。

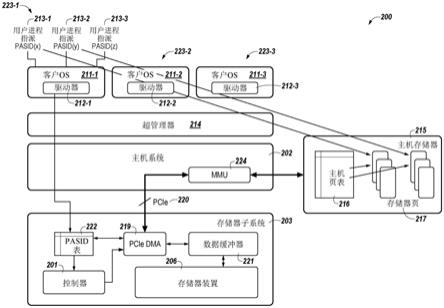

33.图24是示出根据示例实施例的储存器系统的框图。

具体实施方式

34.在下文中,将参照附图在下文中更全面地描述示例实施例,在附图中示出了一些示例实施例。

35.图1是示出根据示例实施例的储存器系统的框图。

36.参照图1,储存器系统可包括主机100和储存器装置200。主机100可包括储存器接口140。

37.在图1中,作为示例,储存器装置200被示为固态驱动器(ssd)装置。然而,示例实施例不限于此。根据一些示例实施例,储存器装置200可以是任何种类的储存器装置。

38.储存器装置200可包括储存器控制器300、多个非易失性存储器装置400a至400k(其中k是大于2的整数)、电源电路500和连接器240。连接器240可包括信号连接器241和电源连接器243。储存器装置200还可包括易失性存储器装置250。

39.多个非易失性存储器装置400a至400k可用作储存器装置200的储存介质。在一些示例实施例中,多个非易失性存储器装置400a至400k中的每一个可包括闪速存储器或竖直nand存储器装置。储存器控制器300可分别通过多个通道chg1至chgk耦接至多个非易失性存储器装置400a至400k。

40.储存器控制器300可从主机100接收接收信号rx,可向主机100发送发送信号tx,并可通过信号连接器241与主机100交换时钟信号clk。接收信号rx可包括命令信号、地址信号和数据。

41.储存器控制器300可基于命令信号和地址信号将数据写入多个非易失性存储器装置400a至400k,或基于命令信号和地址信号从多个非易失性存储器装置400a至400k读取数据。也就是说,储存器控制器300可通过连接器240与主机100通信。

42.储存器控制器300可使用易失性存储器装置250作为输入/输出缓冲器与主机100进行数据通信。在一些示例实施例中,易失性存储器装置250可包括动态随机存取存储器(dram)。

43.另外,储存器装置200可包括连接在储存器控制器300和信号连接器241之间的至少一个无源滤波器260和280。至少一个无源滤波器260和280可对提供至储存器控制器300的信号或由储存器控制器300提供的信号执行均衡。

44.至少一个无源滤波器260和280可设置在印刷电路板(pcb)中,在该印刷电路板(pcb)上设置有储存器控制器300和多个非易失性存储器装置400a至400k。可通过使用pcb的至少一部分来提供(或形成)至少一个无源滤波器260和280。

45.无源滤波器260可对从储存器控制器300提供至主机100的信号执行均衡,并且无源滤波器280可对从主机100提供至储存器控制器300的信号执行均衡。也就是说,至少一个无源滤波器260和280可增强在主机100和储存器装置200之间交换的信号的信号完整性。信号可指示数据。

46.电源电路500可被配置为通过电源连接器243从主机100接收电源电压(即,外部电源电压)ves。电源电路500可基于电源电压ves生成由多个非易失性存储器装置400a至400k使用的至少一个第一操作电压vop1、由储存器控制器300使用的至少一个第二操作电压

vop2、以及由易失性存储器装置250使用的至少一个第三操作电压vop3。

47.电源电路500可向多个非易失性存储器装置400a至400k提供第一操作电压vop1,可向储存器控制器300提供第二操作电压vop2,并且可向易失性存储器装置250提供第三操作电压vop3。

48.图2是示出根据示例实施例的图1中的主机的框图。

49.参照图2,主机100可包括中央处理单元(cpu)110、只读存储器(rom)120、主存储器130、储存器接口140、用户接口150和总线160。

50.总线160可指经由其在主机100的cpu 110、rom 120、主存储器130、储存器接口140和用户接口150之间收发数据的通道。rom 120可存储各种应用程序。例如,存储支持诸如高级技术附件(ata)、小型计算机系统接口(scsi)、嵌入式多媒体卡(emmc)和/或unix文件系统(ufs)协议的存储协议的应用程序。

51.主存储器130可临时存储数据或程序。用户接口150可以是用于在用户和主机100、计算机程序等之间交换信息的物理或虚拟介质,并且包括物理硬件和逻辑软件。例如,用户接口150可包括用于允许用户操纵主机100的输入装置,以及用于输出用户的输入的处理结果的输出装置。

52.cpu 110可控制主机100的整体操作。cpu 110可通过使用存储在rom 120中的应用来生成用于将数据存储在储存器装置200中的命令或用于从储存器装置200读取数据的请求(或命令),并经由储存器接口140将请求发送到储存器装置200。

53.图3是示出根据示例实施例的图1中的储存器控制器的示例的框图。

54.参照图3,储存器控制器300可包括处理器310、纠错码(ecc)引擎320、rom 330、随机函数发生器335、主机接口340、存储器控制器360和非易失性存储器接口350,它们经由总线305连接。

55.处理器310控制存储器控制器360的整体操作。

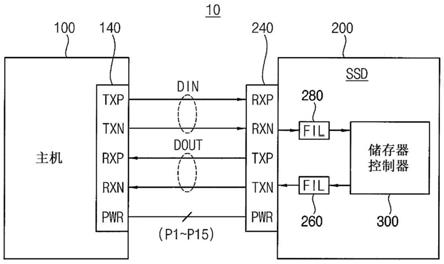

56.非易失性存储器装置400a至400k的存储器单元的阈值电压分布可能由于诸如程序运行时间、温度、程序干扰、读取干扰等的原因而变化。例如,由于上述原因,存储在非易失性存储器装置400a至400k中的数据变得错误。储存器控制器300利用各种纠错技术来纠正这样的错误。例如,储存器控制器300可包括ecc引擎320。ecc引擎320可对从非易失性存储器装置400a至400k读取的数据中的错误进行纠正。

57.rom 330可存储固件,并且固件可被加载到易失性存储器装置250并由处理器310驱动。

58.随机函数发生器335对将存储在非易失性存储器装置400a至400k中的数据进行随机化。例如,随机函数发生器335可以字线为单位对将存储在非易失性存储器装置400a至400k中的数据进行随机化。

59.数据随机化是为了处理数据,使得连接到字线的存储器单元的编程状态具有相同的比率。例如,如果连接到一条字线的存储器单元是各自存储2比特数据的多级单元(mlc),则存储器单元中的每一个具有以下状态中的一个:擦除状态以及第一编程状态至第三编程状态。

60.在这种情况下,随机函数发生器335随机化数据,使得在连接到一条字线的存储器单元中,具有擦除状态的存储器单元的数量、具有第一编程状态的存储器单元的数量、具有

第二编程状态的存储器单元的数量和具有第三编程状态的存储器单元的数量基本上彼此相同。例如,其中存储有随机化数据的存储器单元具有其数量彼此相等的编程状态。

61.随机函数发生器335对从非易失性存储器装置400a至400k读取的数据去随机化。

62.储存器控制器300可通过主机接口340与主机100通信,并且可通过非易失性存储器接口350与非易失性存储器装置400a至400k通信。储存器控制器300可通过存储器控制器360控制易失性存储器装置250。

63.图4是进一步示出用于图1的储存器系统的接口的示例的各方面的框图。

64.在图4中,示出sata接口作为示例。然而,示例实施例不限于此。

65.储存器接口140和连接器240可经由包括数据段和电力段的sata电缆连接。

66.数据段(即,信号连接器241)被示出为包括两个单向数据线对din和dout。din用于将数据从主机100提供至储存器装置200。dout用于将数据从储存器装置200提供至主机100。实现din和dout的数据线可连接在主机100和储存器装置200的相应的发送(tx)端子和接收(rx)端子(例如,txp、txn、rxp和rxn端子)之间。数据段也可称为信号段。

67.电力段(即,电源连接器243)包括15条电源线(例如,p1至p15)。电力段可连接到主机100和储存器装置200的各种电力端子(pwr),并且可分别用于将诸如3.3v、5v和12v的各种电压从主机100提供至储存器装置200。

68.无源滤波器260和280可设置在连接器240和储存器控制器300之间。

69.图5a示出根据示例实施例的图1中的连接器的上表面,图5b示出根据示例实施例的图1中的连接器的下表面。

70.如图5a所示,第1引脚至第75引脚中的奇数编号的引脚可平行地设置在连接器240的上表面上。如图5b所示,第2引脚至第74引脚中的偶数编号的引脚可平行地设置在连接器240的下表面上。

71.连接器240可提供其中不设置引脚的键。键可防止连接器240在被插入主机100时被颠倒。例如,键可偏离连接器240的中心,并可形成在第59引脚至第66引脚(引脚59至引脚66)的位置处。连接器240的引脚可被布置为支持诸如pcie的通信接口。引脚的布置可被改变以支持其它通信接口。

72.图6示出根据示例实施例的图5a和图5b中的连接器的连接端子。

73.参照图5a和图6,示出连接器240的第1引脚至第75引脚。例如,第1引脚至第75引脚中的奇数编号的引脚可设置在连接器240的上表面上,第2引脚至第74引脚中的偶数编号的引脚可设置在连接器240的下表面上。

74.第1、第3、第9、第15、第21、第27、第33、第39、第45、第51、第57、第71、第73和/或第75引脚(引脚1、引脚3、引脚9、引脚15、引脚21、引脚27、引脚33、引脚39、引脚45、引脚51、引脚57、引脚71、引脚73和/或引脚75)可被配置为连接到地电压gnd,而不考虑储存器装置200的通信类型。

75.取决于功率模式,第2、第4、第14、第16、第18、第70、第72和第74引脚(引脚2、引脚4、引脚14、引脚16、引脚18、引脚70、引脚72和引脚74)可不连接(未连接(n/c))或接收3.3v的电力。可基于储存器装置200的通信类型或者不考虑储存器装置200的通信类型来确定功率模式。n/c可表示引脚没有通过物理布线连接到储存器控制器300。在一些示例实施例中,n/c可表示引脚通过物理布线连接到储存器控制器300,但是储存器控制器300可不使用该

引脚。

76.第40引脚和第42引脚(引脚40和引脚42)可形成边带接口作为系统管理总线(smbus)的一部分。第40引脚(引脚40)可将系统管理总线的时钟smb_clk从主机100输入到连接器240,或者可将时钟smb_clk从连接器240输出到主机100。第40引脚(引脚40)可在0v和1.8v之间切换。

77.第42引脚(引脚42)可将系统管理总线的数据smb_data从主机100输入到连接器240,或者可将数据smb_data从连接器240输出到主机100。第42引脚(引脚42)可在0v和1.8v之间切换。

78.第56引脚和第58引脚(引脚56和引脚58)可在储存器装置200的制造过程期间被使用。第56引脚(引脚56)可在制造期间被保留用于制造数据传输(mfg_data)。

79.第58引脚(引脚58)可在制造期间被保留用于制造时钟传输(mfg_clk)。在储存器装置200的制造完成之后,即在储存器装置200的正常操作期间,可不使用第56和第58引脚(引脚56和引脚58)。第68引脚(引脚68)可用于在低功率模式下接收暂停时钟susclk。例如,暂停时钟susclk可具有32khz的频率。

80.第59引脚至第66引脚(引脚59至66引脚)对应于图2所示的键,并且实际上可不提供第59引脚至第66引脚(引脚59至66引脚)。然而,第59引脚至第66引脚(引脚59至引脚66)在图6中被示出以清楚地描述引脚编号。

81.第5引脚(引脚5)可用作pcie通信接口中的第三负发送端子petn3。第7引脚(引脚7)可用作pcie通信接口中的第三正发送端子petp3。第11引脚(引脚11)可用作pcie通信接口中的第三负接收端子pern3。

82.第13引脚(引脚13)可用作pcie通信接口中的第三正接收端子perp3。

83.第17引脚(引脚17)可用作pcie通信接口中的第二负发送端子petn2。第19引脚(引脚19)可用作pcie通信接口中的第二正发送端子petp2。第23引脚(引脚23)可用作pcie通信接口中的第二负接收端子pern2。

84.第25引脚(引脚25)可用作pcie通信接口中的第二正接收端子perp2。

85.第29引脚(引脚29)可用作pcie通信接口中的第一负发送端子petn1。第31引脚(引脚31)可用作pcie通信接口中的第一正发送端子petp1。第35引脚(引脚35)可用作pcie通信接口中的第一负接收端子pern1。第37引脚(引脚37)可用作pcie通信接口中的第一正接收端子perp1。

86.第41引脚(引脚41)可用作pcie通信接口中的第零负发送端子petn0。第43引脚(引脚43)可用作pcie通信接口中的第零正发送端子petp0。

87.第47引脚(引脚47)可用作pcie通信接口中的第零负接收端子pern0。第49引脚(引脚49)可用作pcie通信接口中的第零正接收端子perp0。

88.第53引脚(引脚53)可用于接收pcie通信接口中的负参考时钟refclkn。第55引脚(引脚55)可用于接收pcie通信接口中的正参考时钟refclkp。

89.第10引脚(引脚10)可由储存器装置200用于将用于对外部发光二极管(led)进行控制的信号led1#发送到外部(例如,主机100)。

90.第38连接端子38可用于在sata通信类型中发送或接收装置休眠信号devslp或电力停用信号pwdis,并且可以在pcie通信类型中是未连接n/c。第44连接端子44可以在sata

通信类型中是未连接n/c,并且可用于在pcie通信类型中接收或发送警报信号alert#。第44连接端子44可被包括在pcie通信类型中的系统管理总线smbus中。

91.第50连接端子50可以在sata通信类型中是未连接n/c,并且可用于在pcie通信类型中接收复位信号perst#0。第52连接端子52可以在sata通信类型中是未连接n/c,并且可用于在pcie通信类型中发送或接收时钟请求信号clkreq#。第54连接端子54可以在sata通信类型中是未连接n/c,并且可用于在pcie通信类型中发送或接收唤醒信号pewake#。

92.第69连接端子69可用于向外部主机通知关于储存器装置200的通信类型的信息。第69连接端子69可在sata通信类型中连接到储存器装置200的接地节点,并可向主机提供地电压作为通知信号pedet。第69连接端子69在pcie通信类型中可以是未连接n/c,或者可以是浮置的。也就是说,第69连接端子69可用于储存器装置200以支持多个通信协议,具体地,以确定是否使用多个通信协议中的任何一个。

93.第6、第8、第20、第22、第24、第26、第28、第30、第32、第34、第36、第46、第48和第67连接端子(连接端子6、连接端子8、连接端子20、连接端子22、连接端子24、连接端子26、连接端子28、连接端子30、连接端子32、连接端子34、连接端子36、连接端子46、连接端子48和连接端子67)可用于支持功率模式。

94.关于连接端子的描述仅仅是示例,并且连接端子的数量和连接端子的每一个的功能可基于通信协议而变化。

95.图7示出根据示例实施例的图1中的无源滤波器、储存器控制器和主机的关系。

96.在图7中,还示出图2中的储存器接口中的接收器141和主机接口340中的发送器341。

97.在图7中,发送器341包括驱动器342,驱动器342用于通过焊盘pd11和pd12、无源滤波器260、信号连接器241的连接端子241a和241b以及主通道hch1和hch2向接收器141发送差分信号sigp和sign。

98.参照图7,发送器341包括驱动器342、第一电阻器r11、第一电容器c11、第二电阻器r12和第二电容器c12。

99.第一电阻器r11可耦接在节点n11与驱动器342之间,第一电容器c11可耦接在节点n11与地电压vss之间,第二电阻器r12可耦接在节点n12与驱动器342之间,并且第二电容器c12可耦接在节点n12与地电压vss之间。

100.第一电阻器r11和第二电阻器r12可具有相同的电阻值。第一电容器c11和第二电容器c12可具有相同的电容值。发送器341可在节点n11处提供正信号sigp并且可在节点n12处提供负信号sign。

101.无源滤波器260可包括第一滤波器(fil1)261和第二滤波器(fil2)263。

102.第一滤波器261可连接在焊盘pd11和第一连接端子241a之间,第二滤波器263可连接在焊盘pd12和第二连接端子241b之间。第一滤波器261可对正信号sigp进行均衡(滤波)以通过第一连接端子241a向主通道hch1提供经过均衡的信号,并且第二滤波器263可对负信号sign进行均衡(滤波)以通过第二连接端子241b向主通道hch2提供经过均衡的信号。

103.第一连接端子241a可通过主通道hch1连接到接收器141,第二连接端子241b可通过主通道hch2连接到接收器141。

104.接收器141可包括电阻器r2、第一电容器c21和第二电容器c22。

105.电阻器r2可耦接在节点n31与节点n32之间,第一电容器c21可耦接在节点n31与地电压vss之间,并且第二电容器c22可耦接在节点n32与地电压vss之间。第一电容器c21和第二电容器c22可具有相同的电容。在节点n31提供响应于正信号sigp的正电压信号voutp,在节点n32提供响应于负信号sign的负电压信号voutn。

106.图8示出根据示例实施例的图7中的第一滤波器的示例。

107.参考图8,第一滤波器261可包括并联耦接在第一节点n21和第二节点n22之间的滤波器电阻器rf和滤波器电容器cf。

108.第二滤波器263的构造可与图7的第一滤波器261的构造相同。可通过使用pcb的至少一部分来提供滤波器电阻器rf和滤波器电容器cf中的至少一个。

109.图7中的接收器141中的电阻器r2和电容器c21和c22以及图8中的第一滤波器261中的滤波器电阻器rf和滤波器电容器cf可构成无源连续时间线性均衡器(ctle)。无源ctle可提供增强的线性度,并且可提高电压信号voutp和voutn的信号完整性。

110.图9和图10分别是示出根据示例实施例的其上安装有储存器装置的pcb的平面图和截面图。

111.参照图9和图10,pcb 10被示出为包括第一通道图案chp1至第四通道图案chp4。

112.pcb 10可包括主体层11、顶部保护层13和底部保护层15。pcb 10可包括布线单元,并且pcb 10上的布线单元可电连接到储存器控制器300和非易失性存储器装置400a至400k。另外,pcb 10可包括连接器240。pcb 10可通过连接器240电连接到模块衬底、系统板、主板等。

113.在主体层11中,可形成多层或单层的布线单元,并且pcb 10可通过布线单元电连接到储存器控制器300和非易失性存储器装置400a至400k。顶部保护层13和底部保护层15可执行保护功能,并且可由阻焊剂形成。

114.另外,主体层11通常可通过以下步骤来实现:将诸如热固性树脂、环氧树脂、和酚醛树脂(诸如阻燃剂4(fr-4)、双马来酰亚胺三嗪(bt)和味之素构造膜(abf))的高聚物材料压制到一定厚度,将压制结果形成为薄层,在形成的薄层的两侧上涂覆铜箔,并通过图案化形成作为电信号的传输路径的布线单元。

115.此外,pcb 10可分为在其一侧上形成布线的单层pcb和在其两侧上形成布线的双层pcb。另外,薄层的数量可以是3或更多,并且可通过使用诸如半固化片的绝缘材料来形成薄层,并且可根据所形成的薄层的数量通过形成3个或更多个布线层来实现包括多层布线的pcb。

116.pcb 10可以是其上安装有半导体封装件的衬底,并且包括绝缘层和布线单元。布线单元可包括形成在绝缘层中的第一导电迹线ct1和第二导电迹线ct2,并且可包括穿过绝缘层并连接到第一导电迹线ct1的第一导电过孔件cv1以及穿过绝缘层并连接到第二导电迹线ct2的第二导电过孔件cv2。

117.第一通道图案chp1可以是第一布线单元,并且可包括在第一方向d1上延伸的第一导电迹线ct1、在第三方向d3上延伸的第一导电过孔件cv1、以及形成在第一导电过孔件cv1的顶侧上的第一导电焊盘cp1。

118.第二通道图案chp2可以是第二布线单元,并且可包括在第一方向d1上延伸的第二导电迹线ct2、在第三方向d3上延伸的第二导电过孔件cv2、以及形成在第二导电过孔件cv2

的顶侧上的第二导电焊盘cp2。

119.在一些示例实施例中,以雏菊链方式/拓扑形成的第二通道图案chp2可在第一安装区域mr1和第二安装区域mr2中具有不同的布线长度,以补偿仅在第一安装区域mr1和第二安装区域mr2中的任何一个中的信号损耗。

120.在一些示例实施例中,第一安装区域mr1中的半导体封装件可电连接到第一通道图案chp1至第四通道图案chp4,并且第二安装区域mr2中的半导体封装件可电连接到第二通道图案chp2和第三通道图案chp3。

121.尽管为了便于描述在图10中仅示出了第一通道图案chp1和第二通道图案chp2,但是第一通道图案chp1和第三通道图案chp3可被配置为以点对点的方式/拓扑基本上彼此相同(或者可被配置为一个通道图案组),并且第二通道图案chp2和第四通道图案chp4可被配置为以雏菊链的方式/拓扑基本上彼此相同(或者可被配置为另一个通道图案组)。第二通道图案chp2和第四通道图案chp4可形成为彼此面对并且彼此相邻;并且第一通道图案chp1和第三通道图案chp3可形成为彼此面对,并且第二通道图案chp2和第四通道图案chp4位于第一通道图案chp1和第三通道图案chp3之间。因为第二通道图案chp2和第四通道图案chp4以雏菊链的方式/拓扑形成并且在其中间具有分支点,所以可以以如上所述的布置形状来配置分支点,使得分支点不与第一通道图案chp1和第三通道图案chp3重叠,换句话说,为了电路设计的容易性。

122.在图10中,第二通道图案chp2的第二导电迹线ct2被示出为形成在比第一通道图案chp1的第一导电迹线ct1更靠近底部保护层15的层上。然而,示例实施例不限于此,并且第一通道图案chp1的第一导电迹线ct1可形成在比第二通道图案chp2的第二导电迹线ct2更靠近底部保护层15的层上,并且第一通道图案chp1的第一导电迹线ct1和第二通道图案chp2的第二导电迹线ct2也可形成在同一层上。

123.储存器控制器区域cr和第一安装区域mr1可包括第一通道图案chp1至第四通道图案chp4中包括的第一导电过孔件cv1和第二导电过孔件cv2以及第一导电焊盘cp1和第二导电焊盘cp2的全部,并且第二安装区域mr2可仅包括第二通道图案chp2和第三通道图案chp3中包括的第一导电过孔件cv1和第二导电过孔件cv2以及第一导电焊盘cp1和第二导电焊盘cp2的一部分。

124.此外,pcb 10可包括储存器控制器区域cr旁边的电源区域pr。

125.图11和图12分别是示出根据示例实施例的储存器装置的平面图和截面图。

126.参考图11和图12,提供了储存器装置200a,其中,第一存储器封装件401可仅安装在pcb 10的第一安装区域mr1中,第二存储器封装件402可仅安装在pcb 10的第二安装区域mr2中,第一通道ch1和第三通道ch3连接到第一存储器封装件401,并且第二通道ch2和第四通道ch4连接到第二存储器封装件402。

127.可通过堆叠图1中的非易失性存储器装置400a至400k中的至少一些来形成第一存储器封装件401和第二存储器封装件402中的每一个。第一存储器封装件401可通过焊球sb11和sb12连接到第一通道ch1和第二通道ch2,第二存储器封装件402可通过焊球sb22连接到第二通道ch2,并且储存器控制器300可通过焊球sb31和sb32连接到第一通道ch1和第二通道ch2。

128.将连接器240和储存器控制器300连接的无源滤波器260和280设置在pcb 10中。无

源滤波器260可通过焊球sb33连接到储存器控制器300。

129.图13是示出根据示例实施例的图1中的储存器装置的示例的框图。

130.参照图13,储存器装置200b可包括储存器控制器300和封装件400,封装件400包括设置在pcb 10上的多个非易失性存储器装置400a至400k。

131.储存器控制器300和非易失性存储器装置400a至400k可通过传输线50彼此电耦接。储存器控制器300可通过传输线50向非易失性存储器装置400a至400k发送命令信号和地址信号,并且可通过传输线50与非易失性存储器装置400a至400k交换数据。

132.储存器装置200b还可包括作为pcb 10的一部分设置的连接器240和连接在连接器240和储存器控制器300之间的至少一个无源滤波器260。至少一个无源滤波器260设置在pcb 10中,并且可通过使用pcb 10的至少一部分来提供(或形成)至少一个无源滤波器260。无源滤波器260可通过第一导电图案45连接到储存器控制器300,并且可通过第二导电图案40连接到连接器240的图1中的信号连接器241。

133.如参照图7和图8所述,无源滤波器260可对通过连接器240从储存器控制器300提供至主机100的信号进行均衡,以增加信号的线性度。

134.尽管图13中示出的储存器装置200b包括储存器控制器300和具有多个非易失性存储器装置400a至400k的封装件400,但是储存器装置200b还可包括诸如电源电路和易失性存储器装置的其它组件。

135.储存器装置200b可包括基于闪速存储器的数据储存介质,诸如存储卡、智能卡、通用串行总线(usb)存储器、固态驱动器(ssd)。

136.封装件400可包括非易失性存储器装置400a至400k。如果非易失性存储器装置400a至400k以多堆叠芯片的形式容纳在封装件400中,则堆叠的非易失性存储器装置400a至400k通过相同的通道连接到储存器控制器300。当从主机接收到与读取操作或写入操作关联的命令,要从其读取数据或要向其写入数据的非易失性存储器装置400a被选择时,通道的电容可包括与读取操作或写入操作或回拷操作等没有关联的未被选择的非易失性存储器装置400b至400k的寄生电容。

137.在信号完整性方面,寄生电容影响通过通道的数据传输。非易失性存储器装置400a至400k连接到同一通道,并且写入数据通过该通道被发送到非易失性存储器。当非易失性存储器装置400a至400k和通道之间的反射系数为“0”时,将传输到非易失性存储器的数据可在没有反射的情况下被传输到非易失性存储器。反射系数由以下等式表示:

138.[等式1]

[0139]

γ=(zr-z0)/(zr z0)

[0140]

在等式1中,“zr”表示非易失性存储器装置400a至400k的阻抗,“zo”表示通道的自阻抗。

[0141]

理论上,当非易失性存储器装置400a至400k的阻抗值等于通道的自阻抗值时,不会发生反射。连接到同一通道的非易失性存储器的寄生电容与连接到同一通道的非易失性存储器的数量成比例地增加。

[0142]

随着连接到同一通道的非易失性存储器的数量增加,从储存器控制器300发送到非易失性存储器装置400a至400k的信号被反射的概率会变得更高。因为信号由于反射或阻抗失配而失真,所以期望使通道的测量出的电抗值具有预定值。

[0143]

因为从储存器控制器300发送到主机100的信号由于寄生电容而在连接器240中被反射的概率可能变得更高,所以使通道的测量出的电抗值具有预定值类似地应用于当通过储存器控制器将读取数据从非易失性存储器装置提供给主机100时的情况。

[0144]

根据示例实施例的储存器装置200提供在pcb 10中连接在连接器240和储存器控制器300之间的至少一个无源滤波器260,并且可提高在储存器控制器300和主机100之间交换的信号的信号完整性。也就是说,储存器装置200可在pcb 10中在连接器240和储存器控制器300之间提供均衡器。

[0145]

图14示出根据示例实施例的其中在pcb中设置图13中的无源滤波器的示例。

[0146]

参照图14,无源滤波器260a可包括第一焊盘265、第二焊盘267和竖直导电图案268。第一焊盘265可在pcb 10中连接到连接器240。第二焊盘267可在从pcb 10的上表面uf至pcb 10的下表面bf的竖直方向d3上与第一焊盘265间隔开。竖直导电图案268可在竖直方向d3上连接第一焊盘265与第二焊盘267。

[0147]

第一焊盘265与第二焊盘267可提供图8中的滤波器电容器cf,并且竖直导电图案268可提供图8中的滤波器电阻器rf。第二焊盘267可通过第一导电图案45连接到储存器控制器300。

[0148]

第一焊盘265是直接连接到连接器240的元件,第二焊盘267是连接到第一焊盘265的元件,并且第一焊盘265和第二焊盘267可具有高电容。竖直导电图案268可由具有高电阻的金属来实现。

[0149]

图15示出根据示例实施例的其中在pcb中设置图13中的无源滤波器的另一示例。

[0150]

参照图15,无源滤波器260b可包括第一焊盘265、第二焊盘267a和电阻元件269。第一焊盘265可在pcb 10中连接到连接器240。第二焊盘267a在从pcb 10的上表面uf至pcb 10的下表面bf的竖直方向d3上与第一焊盘265间隔开。电阻元件269可设置在pcb 10的下表面bf上。

[0151]

第一焊盘265和第二焊盘267a可分别通过竖直方向d3上的第一过孔件266a和第二过孔件266b连接到电阻元件269。第二过孔件266b可穿透第二焊盘267a的至少一部分以连接到电阻元件269。

[0152]

第一焊盘265与第二焊盘267a可提供图8中的滤波器电容器cf,并且电阻元件269,第一过孔件266a与第二过孔件266b可提供图8中的滤波器电阻器rf。第二焊盘267a可通过第一导电图案45连接到储存器控制器300。

[0153]

第一焊盘265是直接连接到连接器240的元件,并且第一焊盘265和第二焊盘267a可具有高电容。

[0154]

图16是示出根据示例实施例的图1中的储存器装置的另一示例的框图。

[0155]

参照图16,储存器装置200c可包括设置在pcb 10上的储存器控制器300、包括多个非易失性存储器装置400a至400k的封装件400、以及易失性存储器装置250。

[0156]

储存器控制器300和非易失性存储器装置400a至400k可通过第一传输线50a和第二传输线50b彼此电耦接。储存器控制器300可通过第一传输线50a和第二传输线50b向非易失性存储器装置400a至400k发送命令信号和地址信号,并且可通过第一传输线50a和第二传输线50b与非易失性存储器装置400a至400k交换数据。

[0157]

此外,储存器装置200c还可包括作为pcb 10的一部分提供的连接器240和连接在

连接器240与储存器控制器300之间的至少一个无源滤波器260。至少一个无源滤波器260设置在pcb 10中,并且可通过使用pcb 10的至少一部分来提供(或形成)至少一个无源滤波器260。无源滤波器260可通过第一导电图案45连接到储存器控制器300,并且可通过第二导电图案40连接到连接器240的图1中的信号连接器241。

[0158]

储存器装置200c还可包括设置在pcb 10中并且连接在储存器控制器300和非易失性存储器装置400a至400k之间的至少一个无源滤波器(fil)80。

[0159]

至少一个无源滤波器80可通过第一传输线50a连接到储存器控制器300,并且可通过第二传输线50b连接到非易失性存储器装置400a至400k。至少一个无源滤波器80可对在储存器控制器300和非易失性存储器装置400a至400k之间交换的信号执行均衡。至少一个无源滤波器80可提高在储存器控制器300和非易失性存储器装置400a至400k之间交换的信号的信号完整性。

[0160]

储存器装置200c还可包括设置在pcb 10中并且连接在储存器控制器300和易失性存储器装置(vm)250之间的至少一个无源滤波器(fil)90。

[0161]

至少一个无源滤波器90可通过第一传输线95a连接到储存器控制器300,并且可通过第二传输线95b连接到易失性存储器装置250。至少一个无源滤波器90可对在储存器控制器300和易失性存储器装置250之间交换的信号执行均衡。至少一个无源滤波器90可提高在储存器控制器300和易失性存储器装置250之间交换的信号的信号完整性。

[0162]

至少一个无源滤波器260可被称为至少一个第一无源滤波器,至少一个无源滤波器80可被称为至少一个第二无源滤波器,并且至少一个无源滤波器90可被称为至少一个第三无源滤波器。

[0163]

无源滤波器80和90中的每一个可包括以与无源滤波器260类似的方式并联连接的滤波器电阻器和滤波器电容器。无源滤波器80和90中的每一个可包括如参照图8所述的并联连接的滤波器电阻器和滤波器电容器。

[0164]

图17是示出根据示例实施例的图1中的储存器装置中的非易失性存储器装置之一的框图。

[0165]

参照图17,非易失性存储器装置400a包括存储器单元阵列430、地址解码器460、页缓冲器电路410、数据输入/输出电路420、控制电路450和电压发生器470。

[0166]

存储器单元阵列430通过串选择线ssl、多条字线wl和接地选择线gsl耦接到地址解码器460。此外,存储器单元阵列430通过多条位线bl耦接到页缓冲器电路410。存储器单元阵列430包括耦接到多条字线wl和多条位线bl的多个存储器单元。存储器单元阵列430可包括耦接到在垂直于衬底的竖直方向上堆叠的多条字线wl的多个存储器单元。

[0167]

图18示出图17的非易失性存储器装置中的存储器单元阵列的框图。

[0168]

参照图18,存储器单元阵列430可包括多个存储器块blk1至blkz。存储器块blk1至blkz沿第一方向d1、第二方向d2、和第三方向d3延伸。在示例实施例中,存储器块blk1至blkz由图17中的地址解码器460选择。例如,地址解码器460可从存储器块blk1至blkz中选择与块地址对应的存储器块blk。

[0169]

图19示出图18的存储器块之一的电路图。

[0170]

图19的存储器块blki可以以三维结构(或竖直结构)形成在衬底sub上。例如,包括在存储器块blki中的多个存储器单元串可形成在垂直于衬底sub的方向pd上。

[0171]

参照图19,存储器块blki可包括耦接在位线bl1、bl2和bl3与公共源极线csl之间的存储器单元串ns11、ns12、ns 13、ns21、ns22、ns23、ns31、ns32和ns33(在下文中可被称为存储器单元串ns11至ns33)。存储器单元串ns11至ns33中的每一个可包括串选择晶体管sst,多个存储器单元mc1、mc2、mc3、mc4、mc5、mc6、mc7和mc8(在下文中可被称为存储器单元mc1至mc8),以及接地选择晶体管gst。在图19中,存储器单元串ns11至ns33中的每一个包括8个存储器单元mc1至mc8。然而,示例实施例不限于此。在一些示例实施例中,存储器单元串ns11至ns33中的每一个可包括任何数量的存储器单元。

[0172]

串选择晶体管sst可连接到对应的串选择线ssl1、ssl2和ssl3。多个存储器单元mc1至mc8可分别连接到对应的字线wl1、wl2、wl3、wl4、wl5、wl6、wl7和wl8(在下文中可被称为字线wl1至wl8)。接地选择晶体管gst可连接到对应的接地选择线gsl1、gsl2和gsl3。串选择晶体管sst可连接到对应的位线bl1、bl2和bl3,并且接地选择晶体管gst可连接到公共源极线csl。

[0173]

具有相同高度的字线(例如,wl1)可共同连接,并且接地选择线gsl1至gsl3和串选择线ssl1至ssl3可分离。在图16中,存储器块blki耦接到8条字线wl1至wl8以及3条位线bl1至bl3。然而,示例实施例不限于此。在一些示例实施例中,存储器单元阵列430可耦接到任何数量的字线和位线。

[0174]

图20示出图19的存储器块中的单元串cs(例如,存储器单元串ns11)的结构的示例。

[0175]

参照图19和图20,柱pl设置在衬底sub上,使得柱pl在垂直于衬底sub的方向上延伸以与衬底sub接触。图19中所示的接地选择线gsl(例如,接地选择线gsl1)、字线wl1至wl8以及串选择线ssl(例如,串选择线ssl1)中的每一个可由与衬底sub平行的导电材料(例如,金属材料)形成。柱pl可通过形成串选择线ssl、字线wl1至wl8以及接地选择线gsl的导电材料与衬底sub接触。

[0176]

图20中还示出沿线a-a’截取的截面图。在示例实施例中,示出对应于第一字线wl1的第一存储器单元mc1的截面图。柱pl可包括圆柱形体bd。气隙ag可限定在体bd的内部中。

[0177]

体bd可包括p型硅,并且可以是将形成通道的区域。柱pl还可包括围绕体bd的圆柱形隧道绝缘层ti和围绕隧道绝缘层ti的圆柱形电荷俘获层ct。阻挡绝缘层bi可设置在第一字线wl和柱pl之间。体bd、隧道绝缘层ti、电荷俘获层ct、阻挡绝缘层bi和第一字线wl可构成形成在垂直于衬底sub或垂直于衬底sub的上表面的方向上的电荷俘获型晶体管。串选择晶体管sst、接地选择晶体管gst和其它存储器单元可具有与第一存储器单元mc1相同的结构。

[0178]

返回参照图17,控制电路450可从储存器控制器300接收命令信号cmd和地址信号addr,并且基于命令信号cmd和地址信号addr来控制非易失性存储器装置400a的擦除操作、编程操作和读取操作。

[0179]

例如,控制电路450可基于命令信号cmd产生用于控制电压发生器470的控制信号ctl,并且基于地址信号addr产生行地址r_addr和列地址c_addr。控制电路450可将行地址r_addr提供给地址解码器460,并且将列地址c_addr提供给数据输入/输出电路420。

[0180]

在示例实施例中,地址解码器460通过串选择线ssl、多条字线wl和接地选择线gsl耦接到存储器单元阵列430。

[0181]

在示例实施例中,电压发生器470基于控制信号ctl使用第一操作电压vop1产生用于非易失性存储器装置400a的操作的字线电压vwl。字线电压vwl通过地址解码器460施加到多条字线wl。

[0182]

在示例实施例中,页缓冲器电路410通过多条位线bl耦接到存储器单元阵列430。页缓冲器电路410可包括多个页缓冲器。在一些示例实施例中,一个页缓冲器可连接到一条位线。在其它示例实施例中,一个页缓冲器可连接到两条或更多条位线。页缓冲器电路410可临时地存储将编程到所选页中的数据或从所选页读出的数据。响应于从控制电路450接收的控制信号pcll来控制页缓冲器电路410。

[0183]

在示例实施例中,数据输入/输出电路420通过数据线dl耦接到页缓冲器电路410。在编程操作期间,数据输入/输出电路420可从储存器控制器300接收编程数据dta,并且基于从控制电路450接收的列地址c_addr将编程数据dta提供给页缓冲器电路410。在读取操作期间,数据输入/输出电路420可基于从控制电路450接收的列地址c_addr将存储在页缓冲器电路410中的读取数据dta提供给储存器控制器300。

[0184]

图21和图22是用于解释根据示例实施例的储存器装置的操作的示图。

[0185]

图21是当图1中的储存器装置200不包括至少一个无源滤波器260和280时从连接器240输出到主机100的数据信号的眼图。图22是当图1中的储存器装置200包括至少一个无源滤波器260和280时从连接器240输出到主机100的数据信号的眼图。

[0186]

在图21和图22中,水平轴表示时间,竖直轴表示数据信号的电压电平。

[0187]

参考图1、图21和图22,注意到,图1中的储存器装置200包括至少一个无源滤波器260和280的眼开口率eo2大于图1中的储存器装置200不包括至少一个无源滤波器260和280的眼开口率eo1。此外,注意到,数据信号在图21中如部分f所示是分散的,并且数据信号在图22中如部分f’所示不是分散的。因此,当储存器装置200包括至少一个无源滤波器260和280时,可提高从储存器装置200输出的信号完整性。

[0188]

根据示例实施例,至少一个无源滤波器在pcb中设置在连接器和储存器控制器之间,并且至少一个无源滤波器对从储存器控制器提供的或提供给储存器控制器的信号进行均衡。因此,可提高从储存器控制器输出到主机的高频信号的信号完整性,并且因此,可降低储存器装置的功耗。

[0189]

图23是示出根据示例实施例的操作储存器装置的方法的流程图。

[0190]

参照图1至图23,在操作储存器装置200的方法中,在pcb 10上设置储存器控制器300和多个非易失性存储器装置400a至400k(操作s110)。多个非易失性存储器装置400a至400k可分布在pcb10上,或者多个非易失性存储器装置400a至400k可以以多堆叠芯片封装件的形式设置在pcb上。

[0191]

在pcb 10中设置包括多个连接端子的连接器240(操作s 120)。储存器控制器300可通过连接器240与外部主机100通信。

[0192]

在pcb中设置电连接储存器控制器300和非易失性存储器装置400a至400k的多条传输线50(操作s130)。

[0193]

在pcb 10中在储存器控制器300和连接器240之间设置至少一个无源滤波器260和280(操作s140)。至少一个无源滤波器260和280可对提供给储存器控制器300的信号或从储存器控制器300提供的信号执行均衡。

[0194]

可通过在pcb 10中在耦接到储存器控制器300的第一节点n21与耦接到连接器240的第二节点n22之间并联连接滤波器电阻器rf和滤波器电容器cf来设置至少一个无源滤波器260和280。

[0195]

因此,至少一个无源滤波器260和280可提高在储存器控制器300和主机100之间交换的信号的信号完整性。

[0196]

图24是示出根据示例实施例的储存器系统的框图。

[0197]

参照图24,储存器系统1000可包括主机1100和储存器装置1200。储存器装置1200可通过包括多个连接端子的连接器1201连接到主机1100,并且可与主机1100通信。连接器1201可包括如参照图1所述的信号连接器和电源连接器。

[0198]

主机1100包括应用1110、装置驱动器1120、主机控制器1130和缓冲器ram 1140。主机控制器1130包括命令管理器1131、主机直接存储器存取(dma)1132和电力管理器1133。

[0199]

在操作中,由主机1100的应用1110和装置驱动器1120生成系统级命令(例如,写入命令),然后将系统级命令提供给主机控制器1130的命令管理器1131。命令管理器1131可用于生成使用装置驱动器1120提供给储存器装置1200的对应的储存器装置命令(即,与储存器系统1000实现的协议一致的对应的命令或命令集)。由命令管理器1131生成的命令还可被提供给主机dma 1132,主机dma 1132经由储存器接口1101将命令发送到储存器装置1200。

[0200]

储存器装置1200包括闪速存储器装置1210、装置控制器1230、以及缓冲器随机存取存储器(ram)1240。装置控制器1230可包括中央处理单元(cpu)1231、装置dma 1232、闪存dma 1233、命令管理器1234、缓冲器管理器1235、闪存转换层(ftl)1236、闪存管理器1237和电源电路1238。电源电路1238可基于由主机1100提供的电源电压ves来生成操作电压。

[0201]

闪速存储器装置1210、装置控制器1230和缓冲器ram 1240可设置在pcb上。储存器装置1200还可包括连接在装置控制器1230和连接器1201之间的至少一个无源滤波器1220。至少一个无源滤波器1220可设置在pcb中。

[0202]

至少一个无源滤波器1220可对在装置控制器1230与连接器1201之间交换的信号执行均衡,并且可提高信号的信号完整性。至少一个无源滤波器1220可包括如参照图8所述的并联连接的滤波器电阻器和滤波器电容器。

[0203]

从主机1100传输到储存器装置1200的命令可经由连接器1201被提供给装置dma 1232。

[0204]

然后,装置dma 1232可将接收到的命令传送给命令管理器1234。命令管理器1234可用于分配缓冲器ram 1240中的存储器空间,以便经由缓冲器管理器1235接收对应的写入数据。一旦储存器装置1200准备好接收写入数据,命令管理器1234就可向主机1100传送“传输就绪”信号。

[0205]

在接收到传输就绪信号时,主机1100将把写入数据传送到储存器装置1200。可使用主机dma 1132和储存器接口1101将写入数据发送到储存器装置1200。然后,储存器装置1200可使用装置dma 1232和缓冲器管理器1235将接收到的写入数据存储在缓冲器ram 1240中。然后,可经由闪存dma 1233将存储在缓冲器ram 1240中的写入数据提供给闪存管理器1237。闪存管理器1237可用于根据闪存存储器1210的地址来对写入数据进行编程,所述闪存存储器1210的地址是由闪存转换层1236从地址映射表中导出的。

[0206]

一旦写入数据的传送和编程完成,储存器装置1200就可向主机1100发送响应,通知主机1100已经成功地执行了写入命令。基于接收到的响应信号,主机1100向装置驱动器1120和应用1110指示命令完成,并且此后将终止执行与命令对应的操作。

[0207]

如上所述,主机1100和储存器装置1200可经由数据段的数据线(例如,数据线din和dout)交换数据、对应命令和/或(一个或多个)控制信号(例如,就绪信号和响应信号)。

[0208]

储存器装置1200包括在pcb中连接在装置控制器1230和连接器1201之间的无源滤波器1220,并且可提高从装置控制器1230输出到主机1100的信号的信号完整性。

[0209]

可使用各种封装类型或封装配置来封装根据示例实施例的储存器装置或储存器系统。

[0210]

本公开可应用于包括储存器装置的各种电子装置。

[0211]

以上是示例实施例的说明,而不应被解释为对其的限制。尽管已经描述了一些示例实施例,但是本领域技术人员将容易地理解,可在实质上不脱离本公开的新颖教导和优点的情况下在示例实施例中进行许多修改。因此,所有这些修改都旨在被包括在如权利要求中所限定的本公开的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。