存储器控制器、操作存储器控制器的方法和存储设备

1.相关申请的交叉引用

2.本技术要求2020年8月11日在韩国知识产权局提交的第10-2020-0100460号韩国专利申请的优先权,其全部内容通过引用结合于此。

技术领域

3.本公开涉及存储器控制器、操作存储器控制器的方法和存储设备。

背景技术:

4.pci express(pcie)接口协议在计算行业中被广泛用于高速数据传输。pcie提供可以同时发送和接收数据的双向连接。双向连接包括单工发送路径和单工接收路径,并且为了强调这种结构,pcie接口协议采用的双向连接模型也被称为双单工连接模型。

5.使用pcie接口协议发送和接收数据的pcie设备之间的发送路径和接收路径被定义为链路。链路包括一个或多个发送路径和接收路径对,其中形成一对的发送路径和接收路径被定义为通道(lane)。此外,形成一条链路的通道的数量被定义为链路宽度。

技术实现要素:

6.本公开的各方面提供了一种能够连接到各种连接器的存储器控制器。

7.本公开的各方面还提供了一种操作能够连接到各种连接器的存储器控制器的方法。

8.本公开的各方面还提供了一种包括能够连接到各种连接器的存储器控制器的存储设备。

9.根据发明构思的一些方面,一种存储器控制器包括:phy模块,包括连接到设备连接器的多个引脚的第一phy端子;mac模块,包括被启用以与第一phy端子形成第一通道的第一mac端子;以及第二mac端子,在没有连接到第一phy端子的情况下被禁用;开关控制器,被配置为从多个引脚中的至少一个接收连接到设备连接器的主机连接器的信号,并响应于主机连接器的信号输出开关信号;以及开关,被配置为响应于开关信号,禁用第二mac端子并通过将第一phy端子连接到第一mac端子来形成第一通道。

10.根据发明构思的一些方面,一种存储器控制器包括:phy模块,包括根据设备连接器的类型连接到包括在设备连接器中的多个引脚的phy端子;mac模块,包括第一mac端子和第二mac端子,第一mac端子与phy端子形成第一通道,并被配置为通过第一通道向phy模块发送数据和从phy模块接收数据,第二mac端子不向phy模块发送数据其不从phy模块接收数据;开关控制器,被配置为从多个引脚接收连接到设备连接器的主机连接器的信号,并响应于主机连接器的信号输出开关信号;以及开关,被配置为响应于开关信号,通过将phy端子连接到第一mac端子来形成第一通道。

11.根据发明构思的一些方面,一种存储器控制器包括:phy模块,包括根据设备连接器的类型连接到包括在设备连接器中的多个引脚的第一phy端子和第二phy端子;mac模块,

包括第一端口和第二端口,第一端口脑阔多个第一mac端子,第二端口包括多个第二mac端子;开关控制器,被配置为从多个引脚接收指示连接到设备连接器的主机连接器的端口的数量和设备连接器的类型的连接器信号,并响应于连接器信号输出开关信号;以及开关,被配置为通过连接多个第一mac端子中的至少一些与第二phy端子来形成第一通道,和/或被配置为通过根据开关信号连接多个第二mac端子中的至少一些与第二phy端子来形成第二通道,其中,mac模块被配置为通过第一通道和/或第二通道向phy模块发送数据和从phy模块接收数据。

12.根据发明构思的一些方面,一种存储器控制器包括:phy模块,包括根据设备连接器的类型连接到包括在设备连接器中的多个引脚的第一phy端子和第二phy端子;mac模块,包括第一端口和第二端口,第一端口包括彼此不同的第一mac端子和第二mac端子,第二端口包括第三mac端子,第二端口与第一端口不同;以及开关,被配置为禁用第三mac端子,并通过在第一时间点将第一phy端子连接到第一mac端子并将第二phy端子连接到第二mac端子来形成第一通道,开关被配置为禁用第二mac端子,通过在不同于第一时间点的第二时间点将第一phy端子连接到第一mac端子来形成第一通道,并且通过将第二phy端子连接到第三mac端子来形成第二通道。

13.根据发明构思的一些方面,一种存储设备包括:设备连接器,包括多个引脚并耦合到主机连接器;存储器控制器,根据主机连接器和设备连接器的类型,经由接口、通过主机连接器和设备连接器与主机通信;以及非易失性存储器,由存储器控制器将数据从主机写入该非易失性存储器或者从该非易失性存储器向主机读出数据,其中存储器控制器包括:phy模块,包括根据设备连接器的类型连接到多个引脚的第一phy端子和第二phy端子;mac模块,包括第一端口和第二端口,第一端口包括多个第一mac端子,第二端口包括多个第二mac端子;开关控制器,被配置为通过多个引脚接收包括主机连接器的端口的数量和设备连接器的类型的连接器信号,并响应于连接器信号输出开关信号;以及开关,被配置为通过连接多个第一mac端子中的至少一些与第一phy端子来形成第一通道,和/或被配置为通过根据开关信号连接多个第二mac端子中的至少一些与第二phy端子来形成第二通道,其中mac模块被配置为通过第一通道和/或第二通道向phy模块发送数据和从phy模块接收数据。

14.根据发明构思的一些方面,提出了一种操作存储器控制器的方法,该存储器控制器通过phy模块和包括第一端口和第二端口的mac模块发送和接收数据,该方法包括,从连接到phy模块的phy端子的设备连接器提供连接器信号,该连接器信号包括连接到设备连接器的主机连接器的信息;根据来自存储器的连接器信号读取phy模块和mac模块之间的通道信息;以及通过开关连接phy端子与包括在第一端口中的多个第一mac端子中的至少一些来形成第一通道;以及根据读取的通道信息、通过开关连接phy端子与包括在第二端口中的多个第二mac端子中的至少一些来形成第二通道。

15.然而,本公开的各方面不限于本文所阐述的那些。通过参考下面给出的本公开的详细描述,本公开的上述和其他方面对于本公开所属领域的普通技术人员将变得更加清楚。

附图说明

16.通过参考附图详细描述本公开的示例实施例,本公开的上述和其他方面和特征将

变得更加清楚,其中:

17.图1是示出根据一些示例实施例的存储系统的框图;

18.图2是示出图1的存储系统的框图;

19.图3是示出图1的主机的框图;

20.图4是示出图1的存储设备的框图;

21.图5是示出图1的存储器控制器的框图;

22.图6是示出图5的存储器的框图;

23.图7是解释图5的存储器控制器的操作的流程图;

24.图8至图16是解释图5的存储器控制器的操作的框图;和

25.图17是解释图1的存储器控制器的框图。

具体实施方式

26.图1是示出根据一些示例实施例的存储系统的框图。

27.参考图1,根据一些示例实施例的存储系统可以包括主机100和/或存储设备200。

28.主机100可以包括中央处理单元(cpu)110、主机端子120和/或主机连接器130。

29.主机100可以是例如任何电子设备,诸如个人计算机(pc)、膝上型计算机、移动电话、智能电话、平板pc、mp3播放器、个人数字助理(pda)、企业数字助理(eda)、便携式多媒体播放器(pmp)、数码相机、音乐播放器、便携式游戏控制台、导航设备、可穿戴设备、物联网(iot)设备、万物互联(ioe)设备、电子书、虚拟现实(vr)设备和增强现实(ar)设备。

30.中央处理单元110可以控制主机100的所有操作。中央处理单元110可以连接到主机端子120。主机端子120可以连接到主机连接器130,并且中央处理单元110可以通过主机连接器130和主机端子120连接到存储设备200。中央处理单元110可以通过例如主机连接器130和主机端子120、根据pcie接口协议向存储设备200发送数据和从存储设备200接收数据。

31.存储设备200可以包括设备连接器210、存储器控制器300和/或非易失性存储器设备310。

32.在一些示例实施例中,存储设备200可以是作为存储系统的固态驱动器(ssd)。然而,本公开不限于此,并且存储设备10可以被实现为各种类型的设备,诸如嵌入式多媒体卡(emmc)、通用闪存(ufs)存储器卡、紧凑型闪存(cf)卡、安全数字(sd)卡、微型安全数字(micro-sd)卡、微型安全数字(mini-sd)卡、极端数字(xd)卡或记忆棒。

33.存储器控制器300可以控制存储设备200的所有操作。存储器控制器300可以连接到设备连接器210。设备连接器210可以连接到主机连接器130。存储器控制器300可以通过例如设备连接器210、根据pcie接口协议发送和接收数据。

34.存储器控制器300可以控制非易失性存储器设备310的操作。例如,存储器控制器300可以根据从主机100提供的命令在非易失性存储器设备310中写入或读取数据。

35.非易失性存储器设备310可以包括例如闪存或电阻存储器,诸如电阻式ram(reram)、相变ram(pram)或磁ram(mram)。此外,非易失性存储器设备200可以包括集成电路,该集成电路包括处理器和ram,例如存储设备或存储器中处理(processing in memory,pim)。

36.图2是示出图1的存储系统的框图。

37.参考图2,根据一些示例实施例的存储系统可以包括主机100和/或存储设备200。主机100和存储设备200可以根据pcie接口协议彼此发送和接收数据。

38.pcie架构可以包括逻辑上分开的多个层,包括物理层pl、数据链路层dl、事务(transaction)层tl和软件层sl。

39.物理层pl对应于最低层,并且在主机100和存储设备200之间串行传输在数据链路层dl中生成的分组。物理层pl提供通过pcie设备100和200之间的tx和rx形成的链路,并且分组通过链路在主机100和存储设备200之间传输。

40.数据链路层dl对应于物理层pl的上层,保证通过链路的分组传输的可靠性,并提供管理链路的功能。例如,数据链路层dl可以向在事务层tl中生成的分组添加序列号、循环冗余校验(crc)信息等。

41.事务层tl从软件层sl接收读取或写入请求,生成请求分组,并将请求分组传送到数据链路层dl。此外,事务层tl从数据链路层dl接收响应分组,并将响应分组与从软件层sl接收到的请求进行匹配。

42.软件层sl是未被pcie规范定义的最高层,并且软件层sl可以包括例如驱动pcie设备的软件、或者从用户或主机应用接收数据读取或写入请求并向用户或主机应用提供相应的响应的软件。

43.在pcie规范中定义了对物理层pl、数据链路层dl、事务层tl和软件层sl的更详细描述。

44.图3是示出图1的主机的框图。

45.参考图3,主机100和主机连接器130可以形成主机端口150。主机端子120可以包括多个主机通道151至158。

46.例如,连接到中央处理单元110的多个主机端子121至128可以与包括在主机连接器130中的多个主机单引脚131至138形成多个主机通道151至158。主机通道151至158可以包括在主机端子121至128和主机单引脚131至138之间形成一对的发送路径和接收路径。

47.主机端子121至128可以通过主机通道151至158向主机单引脚131至138发送数据和从主机单引脚131至138接收数据。因此,中央处理单元110可以通过主机端口150向连接到主机连接器130的外部设备发送数据和从外部设备接收数据。

48.另一方面,主机连接器130可以包括主机单引脚131至138、第一主机引脚139和第二主机引脚140。

49.如上所述,主机单引脚131至138可以与主机端子120形成主机端口150。

50.第一主机引脚139可以指示主机连接器130的类型。例如,当外部设备的连接器(例如,图1的存储设备200的设备连接器210)连接到主机连接器130时,第一主机引脚139可以发送来自主机100的、指示主机连接器130的类型的第一信号sig1。主机连接器130的类型可以表示,例如,主机连接器的形状因数(form factor),诸如u.2、u.3、aic、edsff等。

51.第二主机引脚140可以指示主机连接器130的端口的数量。也就是说,第二主机引脚140可以表示主机连接器130的主机端口150的数量。例如,当外部设备的连接器(例如,图1的存储设备200的设备连接器210)连接到主机连接器130时,第二主机引脚140可以发送来自主机100的、指示主机连接器130的端口的数量的第二信号sig2。

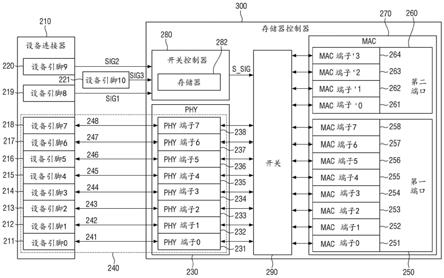

52.主机端口150的数量可以表示主机端口150(诸如,例如单端口或双端口)的数量。换句话说,由于一个中央处理单元110与主机连接器130形成一个主机端口150,所以主机连接器130的端口的数量可以表示包括在主机100中的中央处理单元110的数量。在图3中,由于主机端口150的数量是1,所以主机连接器130的端口的数量可以是1。可替代地,由于图3中的中央处理单元110的数量是1,所以主机连接器130的端口的数量可以是1。

53.图4是示出图1的存储设备的框图。

54.参考图4,存储设备200可以包括基底(substrate)201、设备连接器210、存储器控制器300和/或非易失性存储器设备310。

55.基底201可以由诸如塑料的绝缘材料制成,并且可以是例如印刷电路板(pcb)。设备连接器210、存储器控制器300和非易失性存储器设备310可以安装在基底201上。

56.设备连接器210、存储器控制器300和非易失性存储器设备310可以通过基底201上的布线彼此电连接。例如,设备连接器210的多个单引脚211至218、第一引脚219、第二引脚220和第三引脚221可以通过基底201上的布线202电连接到存储器控制器300。在附图中,为了简化描述,示出了基底201上的布线202中的一些。

57.例如,设备连接器210可以被设置在基底201的一个侧表面上。可替代地,设备连接器210可以是基底201的部分,并且设备连接器210可以由与基底201相同的材料形成。设备连接器210可以具有从基底101的一个侧表面突出的形状。设备连接器210可以包括多个引脚211至220。多个引脚211至220可以包括多个单引脚211至218、第一引脚219和第二引脚220。多个单引脚211至218、第一引脚219和第二引脚220可以由例如导电材料形成。因此,多个单引脚211至218、第一引脚219和第二引脚220可以电连接到被连接到设备连接器210的外部设备的引脚。

58.例如,基底201和设备连接器210的形状(shape)和形状因数可以符合外围组件互连快速(pcie)标准。

59.图5是示出图1的存储器控制器的框图。图6是示出图5的存储器的框图。

60.参考图5,存储器控制器300可以包括phy模块230、mac模块270、开关控制器280和/或开关290。

61.phy模块230可以与设备连接器210形成设备端口240。设备端口240可以包括多个设备通道241至248。

62.例如,包括在phy模块230中的多个phy端子231至238可以与包括在设备连接器210中的多个单引脚211至218形成多个设备通道241至248。设备通道241至248可以包括在phy端子231至238和单引脚211至218之间形成一对的发送路径和接收路径。

63.phy端子231至238可以通过设备通道241至248向单引脚211至218发送数据和从单引脚211至218接收数据。因此,存储器控制器300可以通过设备端口240向连接到设备连接器210的外部设备发送数据和从外部设备接收数据。

64.参考图4,设备连接器210的多个单引脚211至218可以通过基底201上的布线202连接到存储器控制器300。也就是说,多个单引脚211至218可以通过基底201上的布线202连接到多个phy端子231至238。因此,设备通道241至248可以由基底201上的布线202来确定。

65.mac模块270可以通过通道向phy模块230发送数据和从phy模块230接收数据。mac模块270可以包括包含多个第一mac端子251至258的第一端口250和包含多个第二mac端子

261至264的第二端口260。尽管图5中示出了包括两个端口250和260的mac模块270,但是本公开不限于此,mac模块270可以包括三个或更多个端口。

66.参考图2,phy模块230可以是物理层pl的模块。phy模块230可以与存储器控制器300接口。也就是说,存储器控制器300可以通过phy模块230发送和接收数据。此外,mac模块270可以是数据链路层dl的模块。也就是说,mac模块270可以生成要通过phy模块230作为分组被提供的数据。

67.返回参考图5,存储器控制器300可以从设备连接器210的多个引脚211至221中的至少一个引脚接收连接到设备连接器210的主机连接器的信号。开关控制器280可以从设备连接器210的多个引脚211至221中的至少一个引脚接收连接到设备连接器210的主机连接器的信号。例如,开关控制器280可以从多个引脚211至221当中的第一引脚219、第二引脚220和第三引脚221接收主机连接器的信号。在下文中,假设开关控制器280从第一引脚219、第二引脚220和第三引脚221接收开关连接器的信号,但是本公开不限于此。

68.当外部设备的连接器(例如,图1的主机100的主机连接器130)连接到设备连接器210时,主机连接器的信号可以包括外部设备的连接器的类型、外部设备的连接器的端口的数量以及设备连接器210的类型。例如,主机连接器的信号可以包括第一信号sig1、第二信号sig2和第三信号sig3。

69.例如,第一信号sig1可以通过第一引脚219提供。开关控制器280可以通过第三引脚221接收第三信号sig3。当外部设备的连接器(例如,图1的主机100的主机连接器130)连接到设备连接器210时,第一信号sig1和第三信号sig3可以指示外部设备的连接器的类型和设备连接器210的类型。例如,外部设备的连接器的类型和设备连接器210的类型可以分别表示外部设备的连接器和设备连接器210的形状因数。

70.开关控制器280可以通过第二引脚220接收第二信号sig2。当外部设备的连接器(例如,图1的主机100的主机连接器130)连接到设备连接器210时,第二信号sig2可以指示外部设备的连接器的端口的数量。

71.开关控制器280可以接收第一信号sig1、第二信号sig2和第三信号sig3。开关控制器280可以根据第一信号sig1、第二信号sig2和第三信号sig3来确定外部设备的连接器的类型、设备连接器210的类型以及外部设备的连接器的端口的数量。

72.例如,参考图6,开关控制器280中可以包括存储器282。存储器282可以根据第一信号sig1、第二信号sig2和第三信号sig3存储外部设备的连接器的类型和外部设备的连接器的端口的数量。因此,开关控制器280可以从存储器282读取外部设备的连接器的类型和外部设备的连接器的端口的数量。

73.此外,存储器282可以根据第一信号sig1、第二信号sig2和第三信号sig3存储phy模块230和mac模块270之间的通道配置。因此,开关控制器280可以根据第一信号sig1、第二信号sig2和第三信号sig3输出包括通道配置的开关信号s_sig。

74.参考图3和图5,通道配置可以被配置为使得主机100的主机端子121至128对应于并连接到mac模块270的mac端子251至258和261至264。此外,主机100的第一中央处理单元110可以被配置为连接到第一端口250。例如,可以配置通道,使得第一主机端子121连接到第一端口250的第一mac端子251,并且可以配置通道,使得第一主机端子122连接到第一端口250的第一mac端子252。

75.返回参考图5,开关290可以被设置在phy模块230和mac模块270之间。开关290可以从开关控制器280接收开关信号s_sig。开关290可以通过开关信号s_sig将phy模块230连接到mac模块270来形成通道。因此,phy模块230和mac模块270可以彼此发送和接收数据。

76.在附图中,尽管示出了多个引脚211至221当中的多个单引脚211至218与phy端子231至238形成设备通道241至248,并且存储器控制器300从多个引脚211至221当中的第一引脚219、第二引脚220和第三引脚221接收主机连接器的信号,但是本公开不限于此。多个引脚211至221中的至少一个引脚可以与phy端子231至238形成设备通道,并且存储器控制器300可以从多个引脚211至221当中除了形成设备通道的引脚之外的至少一个引脚接收主机连接器的信号。

77.图7是解释图5的存储器控制器的操作的流程图。

78.参考图5和图7,第一引脚219可以接收第一信号sig1,第二引脚220可以接收第二信号sig2,并且第三引脚221可以接收第三信号sig3(操作s1000)。

79.第一信号sig1、第二信号sig2和第三信号sig3可以从第一引脚219、第二引脚220和第三引脚221被发送到开关控制器280(操作s1001)。

80.开关控制器280可以接收第一信号sig1、第二信号sig2和第三信号sig3(操作s1001)。

81.开关控制器280可以根据第一信号sig1、第二信号sig2和第三信号sig3确定连接到设备连接器210的主机连接器130的类型和端口的数量(操作s1003)。例如,开关控制器280可以读取存储在存储器282中的数据,以确定主机连接器130的类型和端口的数量。

82.开关控制器280可以根据所确定的主机连接器130的类型和端口的数量来确定phy模块230和mac模块270之间的通道配置(操作s1005)。例如,开关控制器280可以读取存储在存储器282中的数据,以确定phy模块230和mac模块270之间的通道配置。

83.开关控制器280可以向开关290发送开关信号s_sig,该开关信号s_sig包括所确定的phy模块230和mac模块270之间的通道配置(操作s1007)。

84.开关290可以响应于开关信号s_sig,配置phy模块230和mac模块270之间的通道(操作s1009)。例如,开关290可以启用配置通道的phy模块230的phy端子231至238和mac模块270的mac端子251至258,并且可以禁用不配置通道的phy模块230的phy端子231至238和mac模块270的mac端子251至258。开关290可以通过将phy模块230的启用的phy端子231至238连接到mac模块270的启用的mac端子251至258来形成通道。在下文中,将参考图8至图17进行详细描述。

85.图8至图16是解释图5的存储器控制器的操作的框图。

86.参考图8,主机100可以包括第一中央处理单元110。第一中央处理单元110可以连接到第一主机端子121至124。

87.第一主机端子121至124可以与主机连接器130的主机单引脚133至136形成第一主机端口。第一主机端口可以包括将第一主机端子121至124连接到主机单引脚133至136的主机通道151至154。例如,主机通道#0 151可以包括主机端子#0 121和主机单引脚#3 133之间的发送路径和接收路径。

88.因此,如图8所示,主机连接器130可以包括由四个主机通道151至154构成的第一主机端口。也就是说,主机连接器130可以是包括四个通道的单端口。

89.包括在设备连接器210中的单引脚221至216可以与phy模块230的phy端子231至238形成设备端口。设备端口可以包括设备通道241至246,设备通道241至246包括主机单引脚133至136和phy端子231至233和235至237之间的发送路径和接收路径。例如,设备通道#0 241可以包括单引脚#0 211和phy端子#2 233之间的发送路径和接收路径。这可以由基底201上的布线202形成,如图4所示。

90.第一主机引脚139可以连接到设备连接器210的第一引脚219。第一主机引脚139可以具有第一逻辑电平。第一逻辑电平可以是例如1。第一引脚219可以将包括第一逻辑电平的第一信号sig1从第一主机引脚139发送到开关控制器280。

91.第二主机引脚140可以连接到设备连接器210的第二引脚220。第二主机引脚140可以具有第一逻辑电平。第二引脚220可以将包括第一逻辑电平的第二信号sig2从第二主机引脚140发送到开关控制器280。

92.第三引脚221可以具有第一逻辑电平。第三引脚221可以将包括第一逻辑电平的第三信号sig3发送到开关控制器280。

93.参考图6,开关控制器280可以读取存储器282,并根据第一信号sig1、第二信号sig2和第三信号sig3确定主机连接器130是单端口和u.2类型。

94.开关控制器280可以根据所确定的主机连接器130的类型和端口的数量,向开关290发送包括通道配置c的开关信号s_sig。开关290可以根据开关信号s_sig启用或禁用phy端子231至238和mac端子251至258及261至264。开关290可以启用连接到主机单引脚133至136的phy端子231、232、235和236。此外,开关290可以禁用不与主机单引脚133至136形成设备通道241至246的phy端子233、234、237和238。

95.例如,由于单引脚#0 211没有连接到主机单引脚131,所以可以禁用与单引脚#0 221形成设备通道#0 241的phy端子#2 233。因为单引脚#2 213连接到主机单引脚133,所以可以启用与单引脚#2 213形成设备通道#3 243的phy端子#0 231。因为phy端子#2 233没有与单引脚211至216形成设备通道241至246,所以phy端子#2 233可以被禁用。

96.本文所使用的术语“禁用”可以表示没有形成通道的状态。可替代地,术语“禁用”可以表示没有通过通道发送/接收数据、以及尽管输入了数据但是没有输出数据的状态。术语“启用”可以表示形成了通道并且通过该通道发送/接收数据的状态。也就是说,当输入数据时,术语“启用”可以表示输出数据存在的状态。

97.由于主机连接器130是单端口,所以phy模块230可以与mac模块270的第一端口250形成第一通道291至294。因此,包括在mac模块270的第二端口260中的第二mac端子261至264可以被禁用。

98.开关290可以在启用的phy端子231、232、235和236与启用的第一mac端子251、252、253和254之间配置第一通道291、292、293和294。例如,phy端子#0 231可以与第一端口250的第一mac端子的mac端子#0 251形成第一通道的通道#0 291。

99.因此,主机100的第一主机端子121可以通过第一主机通道151、设备通道243和第一通道291连接到mac模块270的第一mac端子251。也就是说,主机100的第一主机端子121至124可以分别连接到第一端口250的相应的第二mac端子251至254。

100.如先前参考图4所述的,存储器控制器300可以被配置为单芯片,并且可以被安装在基底201上。在一些示例实施例中,存储器控制器300可以通过基底201上的布线202连接

到设备连接器210。也就是说,存储器控制器300的phy模块230和设备连接器210之间的设备通道241至248可以由基底201上的布线202确定。因此,当主机连接器130或设备连接器210的类型改变时,存储器控制器300的phy模块230和设备连接器210之间的设备通道241至248的配置改变。因此,phy模块230和mac模块270之间的第一通道291至294的配置也需要改变。因此,当主机连接器130或设备连接器210的类型改变时,制造商需要设计新的存储器控制器。

101.另一方面,根据一些示例实施例的存储器控制器300中可以包括开关290,并且phy模块230和mac模块270之间的第一通道291至294的配置可以由开关290改变。因此,在根据一些示例实施例的存储器控制器300中,尽管主机连接器130或设备连接器210的类型改变,但是phy模块230和mac模块270之间的第一通道291至294的配置被开关290改变,因此不需要设计新的存储器控制器。

102.此外,由于phy模块230和mac模块270之间的第一通道291至294的配置被开关290改变,因此不需要单独的元件。

103.除了存储在存储器282中的主机连接器130或设备连接器210的类型之外,可以出现新的连接器类型或多端口,诸如双端口或更多的端口。在一些示例实施例中,制造商可以根据存储器282中的新的连接器的类型和端口的数量,存储phy模块230和mac模块270之间的通道配置,而不必从头设计新的存储器控制器。因此,可以更方便地制造存储器控制器。

104.当形成通道但实际上没有通过通道发送或接收数据时,可以影响实际发送和接收数据的通道。因此,在实际发送和接收数据的通道中可能发生故障。

105.然而,根据一些示例实施例,不形成第一通道291至294的phy端子233、234、237和238以及mac端子255至258和261至264被开关290禁用。也就是说,在禁用的phy端子233、234、237和238与禁用的mac端子255至258和261至264之间没有形成通道。因此,由于没有形成未被使用的通道,所以可以防止或减少正在使用的第一通道291至294的故障。

106.图9是解释图5的存储器控制器的操作的框图。为了描述简单,将主要描述与图8的不同之处。

107.参考图9,主机100可以包括第一中央处理单元110和第二中央处理单元410。第一中央处理单元110可以连接到第一主机端子121和122,并且第二中央处理单元410可以连接到第二主机端子421和422。第一中央处理单元110连接到的第一主机端子121和122的数量可以与第二中央处理单元410连接到的第二主机端子421和422的数量相同。

108.第一主机端子121和122可以与主机连接器130的主机单引脚133和134形成第一主机端口。第一主机端口可以包括将第一主机端子121和122连接到主机单引脚133和134的第一主机通道151和152。

109.第二主机端子421和422可以与主机连接器130的主机单引脚135和136形成第二主机端口。第二主机端口可以包括将第二主机端子421和422连接到主机单引脚135和136的第二主机通道451和452。

110.因此,如图9所示,主机连接器130可以包括由两个第一主机通道151和152构成的第一主机端口和由两个第二主机通道451和452构成的第二主机端口。也就是说,主机连接器130可以是包括两个通道的双端口。

111.包括在设备连接器210中的单引脚211至216可以与phy模块230的phy端子231至

238形成设备端口。可以形成与如图8所示的相同的设备端口。

112.第一引脚219可以将包括第一逻辑电平的第一信号sig1从第一主机引脚139发送到开关控制器280。

113.第二引脚220可以将包括第二逻辑电平的第二信号sig2从第二主机引脚140发送到开关控制器280。第二逻辑电平可以是例如0。

114.第三引脚221可以将包括第一逻辑电平的第三信号sig3发送到开关控制器280。

115.参考图6,开关控制器280可以读取存储器282,并根据第一信号sig1、第二信号sig2和第三信号sig3确定主机连接器130是双端口和u.2类型。

116.开关控制器280可以根据所确定的主机连接器130的类型和端口的数量,向开关290发送包括通道配置g的开关信号s_sig。开关290可以根据开关信号s_sig启用或禁用phy端子231至238和mac端子251至258和261至264。

117.由于主机连接器130是双端口,所以phy模块230可以与mac模块270的第一端口250形成第一通道291和292,并且与第二端口260形成第二通道491和492。第一通道291和292的数量可以与第二通道491和492的数量相同。

118.开关290可以配置连接到第一主机端子121和122的phy端子231和232与第一端口250的第一mac端子251和252之间的第一通道291和292。因此,第一中央处理单元110可以连接到第一端口250,并且可以辨识连接到主机连接器130的存储设备。

119.开关290可以配置连接到第二主机端子421和422的phy端子235和236与第二端口260的第二mac端子261和262之间的第二通道491和492。因此,第二中央处理单元410可以连接到第二端口260,并且可以辨识连接到主机连接器130的存储设备。第一中央处理单元110和第二中央处理单元410可以被辨识为分别连接到单独的存储设备。

120.此外,主机100的第一主机端子121和122可以分别连接到第一端口250的相应的第一mac端子251和252,并且主机100的第二主机端子421和422可以连接到第二端口260的第二mac端子261和262。第一中央处理单元110可以连接到第一端口250,并且第二中央处理单元410可以连接到第二端口260。

121.参考图8和图9,如图8所示的单端口u.2类型的主机连接器130可以在第一时间点连接到设备连接器210。此后,移除主机连接器130,并且如图9所示的双端口u.2类型的主机连接器130可以在第二时间点连接到设备连接器210。尽管主机连接器130的端口的数量改变,但是phy模块230和mac模块270之间的通道配置可以被开关290改变。也就是说,可以改变配置与phy端子231、232、235和236的通道291至294、491和492的mac端子251、252、261和262。因此,主机连接器130和设备连接器210可以正常连接。

122.例如,phy端子#5 235可以在第一时间点与第一端口250的第一mac端子251至258的mac端子#2 253形成第一通道293。phy端子#5 235可以在第二时间点与第二端口260的第二mac端子261至264的mac端子#0 261形成第二通道491。此外,第一时间点的第一通道291至294的数量可以不同于第二时间点的第一通道291和292的数量。第一时间点的第一通道291至294的数量可以等于第二时间点的第一通道291和292的数量与第二通道491和492的数量之和。

123.图10是解释图9的存储器控制器的操作的框图。

124.参考图10,第一中央处理单元110可以连接到mac模块270的第一端口250,并且第

二中央处理单元410可以连接到mac模块270的第二端口260。第一中央处理单元110可以通过第一端口250彼此发送数据到非易失性存储器设备和从非易失性存储器设备接收数据,第二中央处理单元410可以通过第二端口260彼此发送数据到非易失性存储器设备和从非易失性存储器设备接收数据。

125.phy模块230可以生成彼此不同的第一系统时钟clk1和第二系统时钟clk2。phy模块230可以通过第一通道291和292向第一端口250提供第一系统时钟clk1。phy模块230可以通过第二通道491和492向第二端口260提供第二系统时钟clk2。因此,第一端口250和第二端口260可以根据不同的系统时钟clk1和clk2来驱动。第一端口250和第二端口260可以彼此分开驱动。

126.因此,phy模块230通过第一通道291和292向第一端口250发送数据和从第一端口250接收数据的时间点可以不同于phy模块230通过第二通道491和492向第二端口260发送数据和从第二端口260接收数据的时间点。

127.图11是解释图5的存储器控制器的操作的框图。为了描述简单,将主要描述与图8的不同之处。

128.参考图11,第一主机端子121、122、123和124可以与主机连接器130的主机单引脚131、132、134和135形成第一主机端口。第一主机端口可以包括连接第一主机端子121、122、123和124以及主机单引脚131、132、134和135的第一主机通道151至154。

129.如图11所示,主机连接器130可以包括由四个第一主机通道151至154构成的第一主机端口。也就是说,主机连接器130可以是包括四个通道的单端口。

130.包括在设备连接器210中的单引脚211、212、214和215可以与phy模块230的phy端子232、233、235和237形成设备端口。

131.第一引脚219可以将包括第二逻辑电平的第一信号sig1从第一主机引脚139发送到开关控制器280。第二引脚220可以将包括第一逻辑电平的第二信号sig2从第二主机引脚140发送到开关控制器280。第三引脚221可以将包括第一逻辑电平的第三信号sig3发送到开关控制器280。

132.参考图6,开关控制器280可以读取存储器282,并根据第一信号sig1、第二信号sig2和第三信号sig3来确定主机连接器130是单端口和u.3类型。

133.开关控制器280可以根据所确定的主机连接器130的类型和端口的数量,向开关290发送包括通道配置d的开关信号s_sig。因此,可以禁用phy端子231、234、236和238、第一mac端子255至258以及第二mac端子261至264,并且可以启用phy端子232、233、235和237以及第一mac端子251至254。启用的phy端子232、233、235、237和启用的第一mac端子251至254可以形成第一通道291至294。

134.图12是解释图5的存储器控制器的操作的框图。为了描述简单,将主要描述与图11的不同之处。

135.参考图12,主机100还可以包括第二中央处理单元410。第一中央处理单元110可以连接到第一主机端子121和122,并且第二中央处理单元410可以连接到第二主机端子421和422。

136.第一主机端子121和122可以与主机连接器130的主机单引脚131和134形成第一主机端口。第一主机端口可以包括将第一主机端子121和122连接到主机单引脚131和134的第

一主机通道151和152。

137.第二主机端子421和422可以与主机连接器130的主机单引脚132和135形成第二主机端口。第二主机端口可以包括将第二主机端子421和422连接到主机单引脚132和135的第二主机通道451和452。

138.第一引脚219可以将包括第二逻辑电平的第一信号sig1从第一主机引脚139发送到开关控制器280。第二引脚220可以将包括第二逻辑电平的第二信号sig2从第二主机引脚140发送到开关控制器280。第三引脚221可以将包括第一逻辑电平的第三信号sig3发送到开关控制器280。

139.参考图6,开关控制器280可以读取存储器282,并根据第一信号sig1、第二信号sig2和第三信号sig3来确定主机连接器130是双端口和u.3类型。

140.开关控制器280可以根据所确定的主机连接器130的类型和端口的数量向开关290发送包括通道配置h的开关信号s_sig。因此,可以禁用phy端子231、234、236和238、第一mac端子253至258以及第二mac端子263和264,并且可以启用phy端子232、233、235和237、第一mac端子251和252以及第二mac端子261和262。启用的phy端子232和233以及启用的第一mac端子251和252可以形成第一通道291和292。启用的phy端子235和237以及启用的第二mac端子261和262可以形成第二通道491和492。

141.图13是解释图5的存储器控制器的操作的框图。为了描述简单,将主要描述与图8的不同之处。

142.参考图13,第一中央处理单元110可以连接到第一主机端子121至128。第一主机端子121至128可以与主机连接器130的主机单引脚131至138形成第一主机端口。第一主机端口可以包括将第一主机端子121至128连接到主机单引脚131至138的第一主机通道151至158。

143.第一引脚219可以将包括第一逻辑电平的第一信号sig1从第一主机引脚139发送到开关控制器280。第二引脚220可以将包括第一逻辑电平的第二信号sig2从第二主机引脚140发送到开关控制器280。第三引脚221可以将包括第二逻辑电平的第三信号sig3发送到开关控制器280。

144.参考图6,开关控制器280可以读取存储器282,并根据第一信号sig1、第二信号sig2和第三信号sig3确定主机连接器130是单端口和aic类型。

145.开关控制器280可以根据所确定的主机连接器130的类型和端口的数量,向开关290发送包括通道配置a的开关信号s_sig。因此,可以禁用第二mac端子261至264,并且可以启用phy端子231至238和第一mac端子251至258。启用的phy端子231至238和启用的第一mac端子251至258可以形成第一通道291至298。

146.图14是解释图5的存储器控制器的操作的框图。为了描述简单,将主要描述与图13的不同之处。

147.参考图14,第一主机端子121至124可以与主机连接器130的主机单引脚131至134形成第一主机端口。第一主机端口可以包括将第一主机端子121至124连接到主机单引脚131至134的第一主机通道151至154。

148.第二主机端子421至424可以与主机连接器130的主机单引脚135至138形成第二主机端口。第二主机端口可以包括连接第二主机端子421至424和主机单引脚135至138的第二

主机通道451至454。

149.第一引脚219可以将包括第一逻辑电平的第一信号sig1从第一主机引脚139发送到开关控制器280。第二引脚220可以将包括第二逻辑电平的第二信号sig2从第二主机引脚140发送到开关控制器280。第三引脚221可以将包括第二逻辑电平的第三信号sig3发送到开关控制器280。

150.参考图6,开关控制器280可以读取存储器282,并根据第一信号sig1、第二信号sig2和第三信号sig3确定主机连接器130是双端口和aic类型。

151.开关控制器280可以根据所确定的主机连接器130的类型和端口的数量,向开关290发送包括通道配置e的开关信号s_sig。因此,可以禁用第一mac端子255至258,并且可以启用phy端子231至238、第一mac端子251至254和第二mac端子261至264。启用的phy端子231至234和启用的第一mac端子251至254可以形成第一通道291至294。启用的phy端子235至238和启用的第二mac端子261至264可以形成第二通道491至494。

152.图15是解释图5的存储器控制器的操作的框图。为了描述简单,将主要描述与图8的不同之处。

153.参考图15,第一中央处理单元110可以连接到第一主机端子121至128。第一主机端子121至128可以与主机连接器130的主机单引脚131至138形成第一主机端口。第一主机端口可以包括将第一主机端子121至128连接到主机单引脚131至138的第一主机通道151至158。

154.第一引脚219可以将包括第二逻辑电平的第一信号sig1从第一主机引脚139发送到开关控制器280。第二引脚220可以将包括第一逻辑电平的第二信号sig2从第一主机引脚140发送到开关控制器280。第三引脚221可以将包括第二逻辑电平的第三信号sig3发送到开关控制器280。

155.参考图6,开关控制器280可以读取存储器282,并根据第一信号sig1、第二信号sig2和第三信号sig3确定主机连接器130是单端口和edsff类型。

156.开关控制器280可以根据所确定的主机连接器130的类型和端口的数量,向开关290发送包括通道配置b的开关信号s_sig。因此,可以禁用第二mac端子261至264,并且可以启用phy端子231至238和第一mac端子251至258。启用的phy端子231至238和启用的第一mac端子251至258可以形成第一通道291至298。

157.图16是解释图5的存储器控制器的操作的框图。为了描述简单,将主要描述与图15的不同之处。

158.参考图16,第一主机端子121至124可以与主机连接器130的主机单引脚131、132、135和136形成第一主机端口。第一主机端口可以包括将第一主机端子121至124连接到主机单引脚131、132、135和136的第一主机通道151至154。

159.第二主机端子421至424可以与主机连接器130的主机单引脚133、134、137和138形成第二主机端口。第二主机端口可以包括将第二主机端子421至424连接到主机单引脚133、134、137和138的第二主机通道451至454。

160.第一引脚219可以将包括第二逻辑电平的第一信号sig1从第一主机引脚139发送到开关控制器280。第二引脚220可以将包括第二逻辑电平的第二信号sig2从第二主机引脚140发送到开关控制器280。第三引脚221可以将包括第二逻辑电平的第三信号sig3发送到

开关控制器280。

161.参考图6,开关控制器280可以读取存储器282,并根据第一信号sig1、第二信号sig2和第三信号sig3确定主机连接器130是双端口和edsff类型。

162.开关控制器280可以根据所确定的主机连接器130的类型和端口的数量,向开关290发送包括通道配置f的开关信号s_sig。因此,可以禁用第一mac端子255至258,并且可以启用phy端子231至238、第一mac端子251至254和第二mac端子261至264。启用的phy端子231至234和启用的第一mac端子251至254可以形成第一通道291至294。启用的phy端子235至238和启用的第二mac端子261至264可以形成第二通道491至494。

163.图17是解释图1的存储器控制器的框图。为了描述简单,将主要描述与图5的不同之处。

164.参考图17,根据一些示例实施例的存储器控制器300可以包括phy模块230、mac模块270、开关控制器280、存储器282和/或开关290。

165.存储器282可以被设置在开关控制器280的外部。当从第一引脚219、第二引脚220和第三引脚221接收到第一信号sig1、第二信号sig2和第三信号sig3时,作为响应,开关控制器280可以读取存储在存储器282中的数据,并确定主机连接器130的类型和端口的数量。此外,开关控制器280可以读取存储在存储器282中的数据,以确定phy模块230和mac模块270之间的通道配置。

166.上面公开的一个或多个元件可以包括或在一个或多个处理电路(诸如包括逻辑电路的硬件、硬件/软件组合(诸如执行软件的处理器)、或者它们的组合)中、或者在一个或多个处理电路中实现。例如,更具体地,处理电路可以包括但不限于中央处理单元(cpu)、算术逻辑单元(alu)、数字信号处理器、微型计算机、现场可编程门阵列(fpga)、片上系统(soc)、可编程逻辑单元、微处理器、专用集成电路(asic)等。

167.在对详细的描述进行总结时,本领域的技术人员将理解,在基本上不脱离本公开的原理的情况下,可以对示例实施例进行多种变化和修改。因此,仅在一般和描述性的意义上使用所公开的本发明构思的示例实施例,而不是出于限制的目的使用所公开的本发明构思的示例实施例。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。