1.本发明涉及主动笔,尤其涉及进行发送和接收双方的主动笔。

背景技术:

2.已知有以下的主动笔:其构成为进行传感器控制器发送的上行链路信号的接收,另一方面,对传感器控制器进行下行链路信号的发送。在专利文献1中公开了这种主动笔的例子。

3.在专利文献1中公开了各种主动笔,其中,双模式触控笔是与双向通信即第一通信方法和从主动笔向传感器控制器的单向通信即第二通信方法双方对应的主动笔。双模式触控笔构成为,若接收到上行链路信号,则以第一通信方法动作,若在未接收到上行链路信号的状态下检测到笔触摸操作,则以第二通信方法动作。

4.在专利文献2~5的各自中公开了主动笔的通信方法的例子。

5.现有技术文献

6.专利文献

7.专利文献1:日本专利第6059410号公报

8.专利文献2:国际公开第2017/029836号公报

9.专利文献3:国际公开第2015/111159号公报

10.专利文献4:美国专利第8536471号说明书

11.专利文献5:美国专利申请公开第2012-0105362号说明书

技术实现要素:

12.发明所要解决的课题

13.专利文献1所记载的双模式触控笔构成为将上行链路信号的接收和下行链路信号的发送通过时间分割来进行。然而,若这样将发送和接收通过时间分割来进行,则在发送下行链路信号的期间(例如约4msec的期间)无法接收上行链路信号。这样一来,上行链路信号的接收产生延迟,第一通信方法下的动作开始有时会延迟,因此需要改善。

14.因此,本发明的目的之一在于提供能够防止上行链路信号的接收产生延迟的主动笔。

15.用于解决课题的手段

16.本发明的第一侧面的主动笔包括:第一及第二电极,设置于互相不同的位置;发送电路,通过使用升压电路对所述第一电极提供变化来发送下行链路信号;接收电路,使用所述第二电极来检测上行链路信号;及阻止滤波器,阻止所述第一电极的电位的变化影响由所述接收电路检测到的所述上行链路信号的电位。

17.本发明的第二侧面的主动笔包括:第一动作模式,进行在正在从第一电极发送下行链路信号时检测来到了第二电极的上行链路信号的处理;及第二动作模式,将从所述第一电极的所述下行链路信号的发送和来到了所述第二电极的所述上行链路信号的检测通

过时间分割来进行,在所述第一动作模式下的动作中检测到所述上行链路信号的情况下,所述主动笔向所述第二动作模式转换。

18.发明效果

19.根据本发明的第一侧面,主动笔能够将上行链路信号的接收和下行链路信号的发送不是通过时间分割来进行而是同时进行。因此,能够防止上行链路信号的接收产生延迟。

20.根据本发明的第二侧面,还未检测到传感器控制器而不知道传感器控制器的上行链路信号的发送定时的主动笔能够同时进行上行链路信号的接收和下行链路信号的发送,另一方面,一旦检测到上行链路信号而知道了传感器控制器的上行链路信号的发送定时的主动笔能够将上行链路信号的接收和下行链路信号的发送通过时间分割来进行。因此,能够防止上行链路信号的接收产生延迟,并在一旦检测到上行链路信号后以噪声少的状态进行上行链路信号的检测。

附图说明

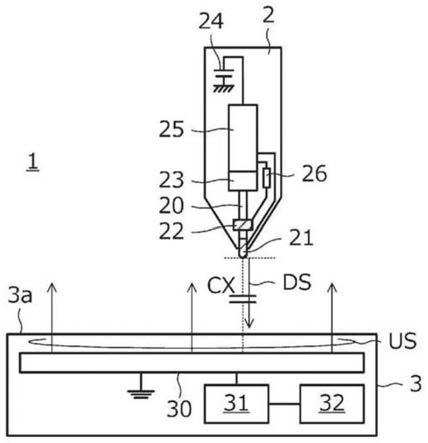

21.图1是示出本发明的实施方式的位置检测系统1的结构的图。

22.图2是图1所示的集成电路25的状态转换图。

23.图3是关于传感器控制器31是与第一通信方法对应的传感器控制器31-1的情况说明主动笔2及传感器控制器31的动作的图。

24.图4是关于传感器控制器31是与第二通信方法对应的传感器控制器31-2的情况说明主动笔2及传感器控制器31的动作的图。

25.图5是示意性地示出图1所示的主动笔2内的结构的图。

26.图6是示出图5所示的阻止滤波器26的第一例即阻止滤波器26a的结构的图。

27.图7是示出使用图6的结构进行了各信号的模拟的结果的图。

28.图8是示出为了通过仅提取上行链路信号us1的边沿而成的边沿信号来接收上行链路信号us1而设置于集成电路25内的接收电路的结构的图。

29.图9是示出由图8所示的接收电路生成的输出信号fo的例子的图。

30.图10是示出图5所示的阻止滤波器26的第二例即阻止滤波器26b的结构的图。

31.图11是示出使用图10的结构进行了各信号的模拟的结果的图。

32.图12是示出使用图10的结构进行了各信号的模拟的结果的图。

33.图13是示出图5所示的阻止滤波器26的第三例即阻止滤波器26c的结构的图。

34.图14是示出使用图13的结构进行了各信号的模拟的结果的图。

35.图15是示出图5所示的阻止滤波器26的第四例即阻止滤波器26d的结构的图。

36.图16是示出使用图15的结构进行了各信号的模拟的结果的图。

37.图17是示出图5所示的阻止滤波器26的第五例即阻止滤波器26e的结构的图。

具体实施方式

38.以下,一边参照附图,一边对本发明的优选的实施方式进行详细说明。

39.图1是示出本发明的实施方式的位置检测系统1的结构的图。如该图所示,位置检测系统1构成为具备主动笔2和检测主动笔2的位置检测装置即电子设备3。作为电子设备3的例子,可举出平板计算机、具备数字转换器的设备。

40.电子设备3具有触摸面3a、配置于触摸面3a的正下方的传感器电极群30、连接于传感器电极群30的传感器控制器31及控制包括它们的传感器控制器31的各部分的主机处理器32。传感器控制器31是具有以下功能的集成电路:通过经由传感器电极群30而与主动笔2通信,导出触摸面3a内的主动笔2的位置,并且从主动笔2取得数据,将导出的位置及取得的数据每次向主机处理器32供给。主机处理器32是电子设备3的中央处理装置,构成为能够执行包括描绘应用的各种程序。描绘应用是具有以下功能的程序:基于从传感器控制器31供给的位置及数据来生成数字墨水,并向电子设备3内的存储器存储,并且显示于显示器。

41.在主动笔2接近触摸面3a时,在主动笔2与传感器电极群30之间产生静电容cx。传感器控制器31构成为,通过该静电容cx而与主动笔2之间交换电荷(静电耦合),从而能够与主动笔2通信。

42.主动笔2是与双向通信即第一通信方法和从主动笔2向传感器控制器31的单向通信即第二通信方法双方对应的主动型的静电触控笔(双触控笔)。第一通信方法例如是专利文献2所记载的通信方法(aes2.0方式),第二通信方法例如是专利文献3所记载的通信方法(aes1.0方式)、专利文献4所记载的通信方法或专利文献5所记载的通信方法。

43.以下,将从传感器控制器31对主动笔2发送的信号称作上行链路信号us,将从主动笔2对传感器控制器31发送的信号称作下行链路信号ds。上行链路信号us由将各发送位利用规定码片长的码片串(扩频码)扩频而成的脉冲波(矩形波)构成。上行链路信号us1的码片长(=上行链路信号us1的脉冲周期)例如是1μsec或2μsec等时间,边沿期间(上升期间或下降期间)例如是10nsec。若以aes2.0来说,则曼彻斯特编码后的脉冲波的脉冲周期成为2μsec。另一方面,下行链路信号ds由脉冲波(矩形波)或以正弦波为基础的信号(包括规定频率的正弦波信号和调制该正弦波信号而成的信号)构成。关于下行链路信号ds的详情后述。

44.如图1所示,主动笔2构成为具有芯体20、笔尖电极21(第一电极)、环电极22(第二电极)、压力传感器23、电池24、集成电路25及阻止滤波器26。芯体20是构成主动笔2的笔轴的构件。芯体20的顶端构成主动笔2的笔尖,末端抵接于压力传感器23。笔尖电极21及环电极22是设置于互相不同的位置的导电体,笔尖电极21配置于主动笔2的笔尖,环电极22以包围芯体20的方式配置于比笔尖电极21靠近主动笔2的中央的位置。

45.压力传感器23是检测向芯体20的顶端施加的压力的传感器。压力传感器23检测到的压力作为笔压值而向集成电路25供给。电池24起到供给集成电路25动作所需的电力的作用。

46.集成电路25是由包括升压电路、发送电路、接收电路及处理电路的各种电路构成的集成电路。发送电路连接于笔尖电极21及环电极22,起到通过使用升压电路对笔尖电极21或环电极22提供变化而发送下行链路信号ds的作用。接收电路连接于环电极22,起到通过使用环电极22进行上行链路信号us的检测动作而接收上行链路信号us的作用。处理电路进行生成下行链路信号ds并使发送电路发送所生成的下行链路信号ds的处理。在进行第一通信方法的情况下,该下行链路信号ds的生成基于由接收电路接收到的上行链路信号us来进行。

47.阻止滤波器26是插入于环电极22与集成电路25之间的滤波器电路。关于阻止滤波器26的详细结构后述,但阻止滤波器26是为了使得能够同时进行使用了环电极22的上行链路信号us的检测和从笔尖电极21的下行链路信号ds的发送而设置的电路。

48.若详细说明,则由为了发送下行链路信号ds而使用的升压电路引起的电位的上升幅度会达到18~20v,因此伴随于下行链路信号ds的发送的笔尖电极21的电位的变化也会给接收电路造成影响。作为结果,在由接收电路检测的上行链路信号us的电位上会重叠下行链路信号ds,因此难以与下行链路信号ds的发送同时地检测上行链路信号us。在主动笔2处于悬停状态而环电极22距传感器电极群30远的情况下,上行链路信号us的接收强度变小,因此上行链路信号us的检测进一步变得困难。阻止滤波器26起到以下作用:阻止伴随于下行链路信号ds的发送的笔尖电极21的电位的变化影响由集成电路25内的接收电路检测到的上行链路信号us的电位,由此,使得能够同时进行使用了环电极22的上行链路信号us的检测和从笔尖电极21的下行链路信号ds的发送。

49.图2是集成电路25的状态转换图。如该图所示,集成电路25构成为以发现模式(第一动作模式)、第一模式(第二动作模式)及第二模式中的任一模式动作。

50.发现模式是集成电路25还未检测到电子设备3的情况下的动作模式。集成电路25构成为,若被投入电源,则首先进入发现模式。另外,第一及第二模式分别是集成电路25用于与对应于第一及第二通信方法的传感器控制器31进行通信的动作模式。

51.在此,在以下的说明中,有时将在第一通信方法中说明的上行链路信号us称作上行链路信号us1,将在第一通信方法中使用的下行链路信号ds中的从笔尖电极21发送的信号称作下行链路信号ds1a,将从环电极22发送的信号称作下行链路信号ds1b。另外,有时将在第二通信方法中使用的下行链路信号ds中的从笔尖电极21发送的信号称作下行链路信号ds2a,将从环电极22发送的信号称作下行链路信号ds2b。

52.进入到发现模式的集成电路25使用环电极22来进行上行链路信号us1的检测动作,并且从笔尖电极21进行下行链路信号ds2a的发送(步骤s1)。该检测动作和发送不是通过时间分割来进行,而是同时执行。

53.在步骤s1中检测到上行链路信号us1的集成电路25进入第一模式(步骤s2),开始基于第一通信方法的通信。具体而言,首先,基于检测到的上行链路信号us1的接收定时来取得上行链路信号us1及下行链路信号ds1a、ds1b的收发日程。然后,集成电路25按照收发日程首先进行下行链路信号ds1a、ds1b的发送(步骤s10),若上行链路信号us1的接收定时到来(步骤s11),则执行上行链路信号us1的检测动作(步骤s12)。步骤s10的发送和步骤s12的检测动作通过时间分割而执行。

54.在此,上行链路信号us1是由表示相对于主动笔2的命令的指令调制后的信号。另外,下行链路信号ds1a是包括例如是无调制的脉冲波或正弦波的位置信号和由主动笔2具有的数据调制后的数据信号的信号。

55.位置信号为了传感器控制器31导出主动笔2的笔尖的位置而使用。另一方面,数据信号为了传感器控制器31从主动笔2取得各种数据而使用。关于数据信号,集成电路25构成为,按照从传感器控制器31接收到的上行链路信号us1中包含的指令,取得通过数据信号而发送的数据。在这样取得的数据中,除了上述的笔压值之外,还能够包括保存于集成电路25的内置存储器的笔id、表示设置于主动笔2的表面的开关的接通断开状态的开关信息等。

56.下行链路信号ds1b仅由是无调制的脉冲波或正弦波的位置信号构成。不过,构成下行链路信号ds1b的脉冲波或正弦波由与构成下行链路信号ds1a的脉冲波或正弦波不同的频率(脉冲周期)构成。这是为了使得传感器控制器31能够将下行链路信号ds1a和下行链

路信号ds1b区分而接收。传感器控制器31基于下行链路信号ds1b来导出环电极22的位置,并导出与基于下行链路信号ds1a内的位置信号而导出的笔尖的位置之间的距离,从而取得主动笔2的倾斜。

57.在作为在步骤s12中执行了上行链路信号us1的检测动作的结果而检测到上行链路信号us1的情况下,集成电路25维持第一模式,返回步骤s10而进行下行链路信号ds1a、ds1b的发送(步骤s13)。另一方面,在未检测到上行链路信号us1的情况下,集成电路25脱离第一模式而返回发现模式,继续处理(步骤s14)。需要说明的是,集成电路25也可以在连续规定次数未检测到上行链路信号us1的情况下,脱离第一模式而返回发现模式。

58.集成电路25在进入到发现模式的期间,也进行笔压值的监视。在作为其结果而检测到笔压值成为了比0大的值的情况下,集成电路25判断为主动笔2的笔尖接触了触摸面3a(发生了笔触摸)而进入第二模式(步骤s3),开始基于第二通信方法的通信。

59.具体来说,集成电路25首先一边使变量count每次增加1(步骤s21)一边反复进行下行链路信号ds2a、ds2b的发送(步骤s20)。

60.在此,下行链路信号ds2a、ds2b是与下行链路信号ds1a、ds1b同样的信号。传感器控制器31基于下行链路信号ds2a、ds2b,与第一通信方法的情况同样,取得主动笔2的位置及倾斜,并且从主动笔2取得各种数据。不过,由于不存在上行链路信号us1,所以无法从传感器控制器31侧要求主动笔2发送的数据。

61.在变量count达到了规定值n的情况下,集成电路25将变量count恢复为1(步骤s22),并且进行笔触摸判定(步骤s23)。笔触摸判定概括而言是笔压值是否是0的判定,集成电路25在笔压值不是0的情况下判定为主动笔2处于笔触摸状态,另一方面,在笔压值是0的情况下判定为主动笔2不处于笔触摸状态(即,处于悬停状态)。在判定为主动笔2处于笔触摸状态的情况下,集成电路25维持第二模式,返回步骤s20而继续下行链路信号ds2a、ds2b的发送(步骤s24)。另一方面,在判定为主动笔2不处于笔触摸状态的情况下,集成电路25脱离第二模式而返回发现模式,继续处理(步骤s25)。

62.图3及图4是说明主动笔2及传感器控制器31的动作的图。图3所示的传感器控制器31-1示出了与第一通信方法对应的传感器控制器31,图3所示的传感器控制器31-2示出了与第二通信方法对应的传感器控制器31。以下,一边参照该图3及图4,一边对主动笔2及传感器控制器31的动作重新详细说明。

63.首先参照图3,还未发现传感器控制器31的集成电路25进入到发现模式,在正在从笔尖电极21发送下行链路信号ds2a时,也进行来到了环电极22的上行链路信号us1的检测。需要说明的是,该图所示的“r”表示信号的检测动作(接收动作)。另一方面,传感器控制器31-1以规定的周期upintv发送上行链路信号us1,并且在未发送上行链路信号us1时进行下行链路信号ds1a、ds1b的检测动作。

64.若在时刻t1下主动笔2进入上行链路信号us1的可接收区(落笔),则在之后的时刻t2下,集成电路25接收上行链路信号us1。这样接收到上行链路信号us1的集成电路25进入第一模式,之后,通过由上行链路信号us1的接收定时决定的收发日程,将下行链路信号ds1a、ds1b的发送和上行链路信号us1的检测动作通过时间分割而反复执行。虽然在图3中未示出,但在即使进行上行链路信号us1的检测动作也未接收到上行链路信号us1的情况下,集成电路25将自身的动作模式恢复为发现模式。

65.接着参照图4,在未接收到上行链路信号us1的状态下在时刻t3下检测到笔压值成为了0的集成电路25进入第二模式。然后,在进入到第二模式的期间,反复执行下行链路信号ds2a、ds2b的发送。若在时刻t4下发生抬笔,则集成电路25在从时刻t4经过了时间t的时刻t5下,脱离第二模式而返回发现模式。时间t的时间长由图2所示的规定值n决定。在时间t的期间返回了笔触摸状态的情况下,集成电路25不返回发现模式而继续第二模式。

66.接着,关于用于使得能够同时进行使用了环电极22的上行链路信号us的检测和从笔尖电极21的下行链路信号ds的发送的阻止滤波器26,一边参照附图一边详细说明。

67.图5是示意性地示出主动笔2内的结构的图。如该图所示,阻止滤波器26插设于连结环电极22和集成电路25的布线。因此,来到了环电极22的上行链路信号us1经由阻止滤波器26而向集成电路25供给。

68.图5所示的静电容cy表示在笔尖电极21及连结笔尖电极21和集成电路25的布线和环电极22及环电极22与集成电路25之间产生的寄生电容。由于存在该寄生电容cy,所以若在上行链路信号us1来到了环电极22时从笔尖电极21发送下行链路信号ds2a,则下行链路信号ds2a会重叠于上行链路信号us1。阻止滤波器26起到从这样重叠了下行链路信号ds2a的上行链路信号us1仅除去下行链路信号ds2a而使得仅上行链路信号us1向集成电路25供给的作用。

69.作为阻止滤波器26的具体的结构,能够采用各种结构。于是,以下,例示5个种类的阻止滤波器26a~26e,对各自进行详细说明。

70.图6是示出阻止滤波器26的第一例即阻止滤波器26a的结构的图。在该图中示出了下行链路信号ds2a由以规定频率的正弦波为基础的信号构成的情况下的例子。这样的下行链路信号ds2a例如在aes1.0中使用,该情况下的上述规定频率成为1.8mhz。

71.在此,在该图及后面的图10及图13中,将主动笔2及传感器控制器31的结构利用等效电路示出。具体来说,首先,振荡器v1对应于传感器控制器31,生成上行链路信号us1。振荡器v2对应于集成电路25内的发送电路,生成下行链路信号ds2a。静电容cx表示形成于环电极22与传感器电极群30(参照图1)之间的静电容。静电容c1表示形成于环电极22及连结环电极22和集成电路25的布线与接地端之间的静电容。电压vring对应于在环电极22出现的信号(重叠了下行链路信号ds2a的状态的上行链路信号us1),电压vfiltout对应于阻止滤波器26的输出信号。被供给电压vfiltout的集成电路25内的电路实际上是接收电路,但在图6及后面的图10及图13中,简易地仅图示了静电容c2与电阻r1的串联电路。电压vrxin对应于由接受了电压vfiltout的输入的接收电路接收的信号。

72.图6的例子的阻止滤波器26a由阻止包括上述规定频率(下行链路信号ds2a的载波频率)的特定频段的带阻滤波器(陷波滤波器)构成。具体来说,如图6所示,阻止滤波器26a构成为包括第一电路和第二电路,第一电路是分别为电阻值r的2个电阻元件串联连接且这2个电阻元件的连接点经由电容值2c的电容器接地而成的电路,第二电路是分别为电容值c的2个电容器串联连接且这2个电容器的连接点经由电阻值r/2的电阻元件接地而成的电路。第一电路及第二电路并联连接于环电极22与集成电路25之间,电容值c及电阻值r以使陷波频率1/2πcr与上述规定频率相等的方式设定。

73.图7是示出使用图6的结构进行了各信号的模拟的结果的图。在该图中示出了上行链路信号us1、电压vring、电压vfiltout、电压vrxin。在该模拟中,上述规定频率设为了

1.8mhz,上行链路信号us1的脉冲周期设为了2μsec。在电压vring中的图示的期间x的部分中,下行链路信号ds2a以不重叠于上行链路信号us1的状态出现。

74.如图7所示,在电压vring中,在上行链路信号us1上重叠有下行链路信号ds2a,另一方面,在电压vfiltout、vrxin中,上行链路信号us1单独出现。从该结果可理解到,由阻止滤波器26a选择性地阻止了下行链路信号ds2a。

75.不过,如从图7所理解的那样,出现于电压vfiltout、vrxin的上行链路信号us1不是原来的脉冲波,而是仅提取脉冲波的边沿而成的边沿信号。因此,集成电路25内的接收电路需要构成为能够通过该边沿信号来接收上行链路信号us1。以下,对这样构成的接收电路的结构进行详细说明。

76.图8是示出为了通过上述边沿信号来接收上行链路信号us1而设置于集成电路25内的接收电路的结构的图。如该图所示,该情况下的集成电路25构成为具有放大电路40、δσ调制部41、脉冲密度检测部42、增益控制部43、边沿匹配滤波器44、图案存储部45及上行链路信号复原部46。

77.放大电路40是将从图6所示的阻止滤波器26a输出后的电压vfiltout放大并作为输出信号do向δσ调制部41供给的电路。放大电路40由构成为能够通过增益控制部43来控制放大率的可变增益的放大器构成。

78.δσ调制部41是对放大电路40的输出信号do进行至少使用了与正、负分别对应的2个基准电位vtp、vtn(vtp=-vtn》0)的比较且进行比较结果的反馈处理的功能部,如图8所示,构成为具有相减电路41a、相加电路41b、比较电路41c及延迟电路41d、41e。

79.比较电路41c是比较相加电路41b的输出信号io和基准电位vtp、vtn的电路,构成为具有比较结果的输出端子、正侧输出端子( 1)、负侧输出端子(-1)这3个输出端子。其中,从比较结果的输出端子输出的信号构成δσ调制部41的输出信号co。

80.比较电路41c的动作如下。即,比较电路41c在相加电路41b的输出信号io超过了基准电位vtp的情况下,作为输出信号co而输出 1,并且将正侧输出端子的电位设为高,将负侧输出端子的电位设为低。另外,比较电路41c在相加电路41b的输出信号io低于基准电位vtn的情况下,作为输出信号co而输出-1,并且将负侧输出端子的电位设为高,将正侧输出端子的电位设为低。在其他的情况下,比较电路41c作为输出信号co而输出0,并且将正侧输出端子及负侧输出端子的电位都设为低。作为这样的比较电路41c的动作的结果,比较电路41c的输出信号co成为取 1、0、-1的任一值的3值的脉冲信号。

81.比较电路41c构成为以比构成上行链路信号us1的码片串的码片长短的周期动作。因此,输出信号co成为相对于构成上行链路信号us1的码片串的1码片包括多个码片(例如4个码片)的脉冲信号。

82.延迟电路41d是使比较电路41c的正侧输出端子的电位成为了δ倍之后例如延迟1时钟量(输出信号co的1码片量)并向相减电路41a反馈的电路。同样,延迟电路41e是使比较电路41c的负侧输出端子的电位成为了-δ倍之后延迟例如1时钟量并向相减电路41a反馈的电路。需要说明的是,δ的具体的值适合设为与基准电位vtp相等的值。

83.相减电路41a是输出从放大电路40的输出信号do减去与延迟电路41d、41e的输出信号对应的量的电位而成的信号的电路。根据该相减,在1时钟前的输出信号io超过了基准电位vtp的情况下,相加电路41b的输入信号的电位电平下降,在1时钟前的输出信号io低于

基准电位vtn的情况下,相加电路41b的输入信号的电位电平上升,因此得到使相加电路41b的输出信号io的电位电平处于一定的范围内这一效果。

84.相加电路41b是输出对相减电路41a的输出信号进行积分而成的信号的电路。相加电路41b的输出信号io成为对1时钟前的相加电路41b的输出信号加上相减电路41a的输出信号而得到的信号。

85.脉冲密度检测部42是检测δσ调制部41的输出信号co的脉冲密度并将其结果向增益控制部43通知的功能部。增益控制部43承担以下作用:基于从脉冲密度检测部42通知的脉冲密度来控制放大电路40的增益,从而防止因输出信号do的绝对值过大或过小而输出信号co被固定。

86.图案存储部45由存储电路构成,该存储电路关于传感器控制器31有可能在上行链路信号us的发送中使用的多个扩频码(2值的码片串)的各自,将由取 1、0、1的任一值的多个码片构成的3值的码片串作为已知的图案存储。

87.边沿匹配滤波器44具有以能够保存与1个扩频码对应的码片数量的码片串的方式设定的先进先出方式的移位寄存器,每当将δσ调制部41的输出信号co取得了1码片时,向该移位寄存器保存。并且,每当保存了新的1码片时,算出在该时间点下保存于移位寄存器的码片串与存储于图案存储部45的多个已知的图案的各自的相关,将其结果逐次作为输出信号fo而向上行链路信号复原部46供给。

88.上行链路信号复原部46在输出信号fo成为了规定值以上的情况下,判定为检测到与在该输出信号fo的算出中使用的图案对应的扩频码。然后,基于连续不断地检测的扩频码来复原上行链路信号us1。集成电路25通过对这样复原后的上行链路信号us进行解调来接收传感器控制器31发送出的指令。

89.图9是示出由图8所示的接收电路生成的输出信号fo的例子的图。不过,在该图中,示出了使用与接收到的上行链路信号us1的码片串对应的图案算出了相关的情况。另外,图9(c)是将电压vfiltout向接收电路输入的情况,但为了比较,在图9(a)中示出了将无噪声的理想的上行链路信号us向接收电路输入的情况,在图9(b)中示出了将电压vring向接收电路输入的情况。从图9所示的结果可理解到,通过组合图6所示的阻止滤波器26a和图8所示的接收电路,与将无噪声的理想的上行链路信号us向接收电路输入的情况同样,能够正确地接收上行链路信号us1。

90.图10是示出阻止滤波器26的第二例即阻止滤波器26b的结构的图。在该图中示出了下行链路信号ds2a由脉冲波构成的情况下的例子。不过,与同样是脉冲波的上行链路信号us1相比,下行链路信号ds2a的脉冲周期大幅变长,另外,边沿期间的时间长也变长。若举出具体的例子,则脉冲周期例如成为4μsec~40μsec,边沿期间例如成为100nsec~5μsec。

91.阻止滤波器26b由使构成上行链路信号us1的脉冲波(第一脉冲波)而阻止构成下行链路信号ds2a的脉冲波(第二脉冲波)高通滤波器50构成。高通滤波器50的具体的结构例如如图10所示,适合设为由一端连接于环电极22且另一端连接于集成电路25的电容值c的电容器和连接于该电容器的另一端与接地端之间的电阻值r的电阻元件构成的cr滤波器。电容值c及电阻值r以使阻止滤波器26b使上行链路信号us1通过而阻止下行链路信号ds2a的方式设定。

92.图11是示出使用图10的结构进行了各信号的模拟的结果的图。在该图中示出了上

行链路信号us1、下行链路信号ds2a、电压vring、电压vfiltout。在图11的例子中,将上行链路信号us1的脉冲周期设为了2μsec,将下行链路信号ds2a的脉冲周期设为了40μsec。另外,将上行链路信号us1的边沿期间e1的时间长设为了10nsec,将下行链路信号ds2a的边沿期间e2的时间长设为了2μsec。

93.如图11所示,在电压vring中,在上行链路信号us1上重叠有下行链路信号ds2a,另一方面,在电压vfiltout中,下行链路信号ds2a大致消失。从该结果可理解到,通过阻止滤波器26b,下行链路信号ds2a也被选择性地阻止。不过,在图11的例子中也是,出现于电压vfiltout的上行链路信号us1不是原来的脉冲波,而是仅提取脉冲波的边沿而成的边沿信号。因此,作为集成电路25内的接收电路,优选与第一例同样,使用具有参照图8说明的结构的接收电路。

94.在此,在使用图10所示的结构的阻止滤波器26b的情况下,若下行链路信号ds2a的边沿期间e2的时间长与上行链路信号us1的边沿期间e1的时间长之差变小,则有时难以从电压vring除去下行链路信号ds2a。以下,举出具体的例子来说明。

95.图12与图11同样,是示出使用图10的结构进行了各信号的模拟的结果的图。与图11的不同在于将下行链路信号ds2a的边沿期间e2的时间长设为了200nsec这一点。如图12所示,在该情况下,下行链路信号ds2a的边沿明确地残留于电压vfiltout。

96.图13是示出阻止滤波器26的第三例即阻止滤波器26c的结构的图。若使用该阻止滤波器26c,则能够解决上述的阻止滤波器26b的课题。以下,详细说明。

97.阻止滤波器26c具有在也示于图10的高通滤波器50的后段设置有静默电路51的结构。静默电路51构成为具有连接于构成高通滤波器50的电容器的另一端与接地端之间的开关元件sw和时钟电路clk。开关元件sw具有非反转输入端子和反转输入端子,构成为在非反转输入端子的电位与反转输入端子的电位之差为规定值以上的情况下将阻止滤波器26c的输出端接地,另一方面,在不是这样的情况下不进行该接地。另外,时钟电路clk构成为,输出在下行链路信号ds2a的边沿期间成为高且在其他期间成为低的信号,并向开关元件sw的非反转输入端子供给。通过这样的开关元件sw及时钟电路clk的动作,在下行链路信号ds2a的边沿期间阻止滤波器26c的输出(=电压vfiltout)被静默。

98.图14是示出使用图13的结构进行了各信号的模拟的结果的图。上行链路信号us1及下行链路信号ds2a的波形与图12的例子是同样的。如比较图14和图12所理解的那样,在图14的例子中,下行链路信号ds2a的边沿从电压vfiltout消失。从该结果可理解到,静默电路51起到了从电压vring除去下行链路信号ds2a的作用。

99.在此,若使用静默电路51,则上行链路信号us1的脉冲有可能局部缺少。于是,与第一及第二例同样,在第三例中,作为集成电路25内的接收电路,也优选使用具有参照图8说明的结构的接收电路。通过这样,能够通过边沿匹配滤波器44的相关运算而将上行链路信号us1复原,因此,即使因静默电路51的作用而上行链路信号us1的脉冲些许缺少,也能够正确地接收上行链路信号us1。

100.图15是示出阻止滤波器26的第四例即阻止滤波器26d的结构的图。如该图所示,阻止滤波器26d构成为包括增益电路52和差动电路53。

101.增益电路52是控制下行链路信号ds2a的振幅并予以输出的电路。增益电路52的输入端连接于集成电路25内的发送电路的输出端,输出端连接于差动电路53的反转输入端

子。增益电路52起到将下行链路信号ds2a的振幅衰减至与经由寄生电容cy而重叠于上行链路信号us1的下行链路信号ds2a相同的程度的作用。

102.差动电路53是进行从来到了环电极22的上行链路信号us1减去增益电路52的输出信号而成的输出的电路。差动电路53的非反转输入端子连接于环电极22,因此,对差动电路53的非反转输入端子输入经由寄生电容cy而重叠了下行链路信号ds2a的状态的上行链路信号us1。如上所述,增益电路52的输出信号成为了衰减至与重叠于上行链路信号us1的下行链路信号ds2a相同程度的振幅的下行链路信号ds2a,因此,差动电路53的输出信号成为未重叠下行链路信号ds2a的状态的上行链路信号us1。

103.图16是示出使用图15的结构进行了各信号的模拟的结果的图。图16(a)示出了由传感器控制器31生成的上行链路信号us1,图16(b)~(d)分别示出了出现于图15所示的节点n1~n3的信号。需要说明的是,在图16中示出了上行链路信号us1及下行链路信号ds2a均由脉冲波构成且下行链路信号ds2a的脉冲周期比上行链路信号us1的脉冲周期大幅长的例子。

104.如从图16所理解的那样,出现于节点n1的信号成为了由传感器控制器31生成的上行链路信号us1和出现于节点n2的下行链路信号ds2a重叠而成的信号。并且,出现于节点n3的信号作为从出现于节点n1的信号除去出现于节点n2的下行链路信号ds2a的结果而成为了具有与原来的上行链路信号us1同样的波形的信号。从该结果可理解到,阻止滤波器26d起到了从来到了环电极22的信号除去下行链路信号ds2a的作用。

105.在此,虽然在图15及图16的例子未考虑,但在实际的增益电路52的输入上会重叠经由寄生电容cy而绕入到笔尖电极21侧的上行链路信号us1。在该重叠的影响无法忽视的情况下,需要在阻止滤波器26内从下行链路信号ds2a除去上行链路信号us1的成分。在接着说明的第五例中,对能够实现该除去的阻止滤波器26进行说明。

106.图17是示出阻止滤波器26的第五例即阻止滤波器26e的结构的图。如该图所示,阻止滤波器26e构成为包括fir(finite impulse response:有限冲激响应)滤波器54、减法器55及反馈电路56。

107.fir滤波器54是构成为仅提取特定的信号成分的数字滤波器。在阻止滤波器26e中,fir滤波器54起到作为从自集成电路25内的发送电路输出的下行链路信号ds2a除去上行链路信号us1的成分的滤波器电路及控制下行链路信号ds2a的振幅并予以输出的增益电路的作用。减法器55与图15所示的差动电路53同样,是进行从来到了环电极22的上行链路信号us1减去fir滤波器54的输出信号而成的输出的差动电路。

108.反馈电路56是以使减法器55的输出信号的振幅变小的方式(即,以使输出能量变小的方式)控制fir滤波器54对下行链路信号ds2a的振幅的控制量的电路。具体而言,优选使用lms(least mean squares:最小均方)算法来控制fir滤波器54的传递函数中包含的各系数的值。作为反馈电路56的控制的结果,从fir滤波器54输出的信号成为与不具有上行链路信号us1的成分的纯粹的下行链路信号ds2a相近的信号。因此,根据阻止滤波器26e,可实现:即使经由寄生电容cy而在fir滤波器54的输入上重叠了上行链路信号us1,也从来到了环电极22的信号有效地除去下行链路信号ds2a。

109.如以上说明那样,根据本实施方式的主动笔2,由于在环电极22与集成电路25之间设置了阻止滤波器26,所以能够将上行链路信号us1的接收和下行链路信号ds2a的发送不

是通过时间分割来进行而是同时进行。因此,能够防止上行链路信号us1的接收产生延迟。

110.另外,根据本实施方式的主动笔2,在还未检测到传感器控制器31而不知道传感器控制器31的上行链路信号us的发送定时的阶段(发现模式)中,能够同时进行上行链路信号us的接收和下行链路信号ds的发送,另一方面,在一旦检测到上行链路信号us而弄清楚了传感器控制器31的上行链路信号us的发送定时的阶段(第一模式)中,能够将上行链路信号us的接收和下行链路信号ds的发送通过时间分割来进行。因此,能够防止上行链路信号us的接收产生延迟,并在一旦检测到上行链路信号us后以噪声少的状态进行上行链路信号us的检测。另外,由于能够从笔尖电极21和环电极22双方发送下行链路信号ds,所以能够利用主动笔2的倾斜。

111.以上,虽然对本发明的优选的实施方式进行了说明,但本发明丝毫不限定于这样的实施方式,本发明当然能够在不脱离其主旨的范围内以各种方案来实施。

112.例如,在上述实施方式中,拿出使用是脉冲波的上行链路信号us1的情况进行了说明,但本发明也能够适宜地应用于使用由以正弦波为基础的信号构成的上行链路信号us的情况。在该情况下,在使用图6所示的阻止滤波器26a的情况下,上行链路信号us设为以不包含于由阻止滤波器26a阻止的特定频段的频率的正弦波为基础的信号即可。

113.另外,在上述实施方式中,说明了向环电极22与集成电路25之间固定地插入阻止滤波器26的例子,但也可以设置经由阻止滤波器26的第一路径、不经由阻止滤波器26的第二路径及切换它们的开关,通过从集成电路25控制该开关,在同时进行上行链路信号us1的检测动作和下行链路信号ds2a的发送的情况下(发现模式)将第一路径有效化,在其他的情况下(第一及第二模式)将第二路径有效化。

114.另外,在上述实施方式中,说明了对是双模式触控笔的主动笔2应用了本发明的例子,但本发明能够对需要同时进行下行链路信号ds的发送和上行链路信号us的接收的主动笔2广泛地应用。

115.标号说明

[0116]1ꢀꢀ

位置检测系统

[0117]2ꢀꢀ

主动笔

[0118]3ꢀꢀ

电子设备

[0119]

3a

ꢀꢀ

触摸面

[0120]

20

ꢀꢀ

芯体

[0121]

21

ꢀꢀ

笔尖电极

[0122]

22

ꢀꢀ

环电极

[0123]

23

ꢀꢀ

压力传感器

[0124]

24

ꢀꢀ

电池

[0125]

25

ꢀꢀ

集成电路

[0126]

26、26a~26e

ꢀꢀ

阻止滤波器

[0127]

30

ꢀꢀ

传感器电极群

[0128]

31

ꢀꢀ

传感器控制器

[0129]

32

ꢀꢀ

主机处理器

[0130]

40

ꢀꢀ

放大电路

[0131]

41

ꢀꢀ

δσ调制部

[0132]

41a

ꢀꢀ

相减电路

[0133]

41b

ꢀꢀ

相加电路

[0134]

41c

ꢀꢀ

比较电路

[0135]

41d、41e

ꢀꢀ

延迟电路

[0136]

42

ꢀꢀ

脉冲密度检测部

[0137]

43

ꢀꢀ

增益控制部

[0138]

44

ꢀꢀ

边沿匹配滤波器

[0139]

45

ꢀꢀ

图案存储部

[0140]

46

ꢀꢀ

上行链路信号复原部

[0141]

50

ꢀꢀ

高通滤波器

[0142]

51

ꢀꢀ

静默电路

[0143]

52

ꢀꢀ

增益电路

[0144]

53

ꢀꢀ

差动电路

[0145]

54

ꢀꢀ

fir滤波器

[0146]

55

ꢀꢀ

减法器

[0147]

56

ꢀꢀ

反馈电路

[0148]

c2

ꢀꢀ

静电容

[0149]

clk

ꢀꢀ

时钟电路

[0150]

cx

ꢀꢀ

静电容

[0151]

cy

ꢀꢀ

寄生电容

[0152]

ds、ds1a、ds1b、ds2a、ds2b

ꢀꢀ

下行链路信号

[0153]

e1、e2

ꢀꢀ

边沿期间

[0154]

sw

ꢀꢀ

开关元件

[0155]

us、us1

ꢀꢀ

上行链路信号。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。