1.本公开的实施例大体上涉及半导体领域,且更具体来说涉及刷新逻辑电路布局。

背景技术:

2.本公开大体上涉及半导体装置,且更具体来说涉及半导体存储器装置。特定来说,本公开涉及易失性存储器,例如动态随机存取存储器(dram)。信息可作为物理信号(例如,电容元件上的电荷)存储在存储器的个别存储器单元上。存储器可为易失性存储器,且物理信号可随时间衰减(这可使存储在存储器单元中的信息降级或破坏所述信息)。可需要通过例如重写信息以周期性地刷新存储器单元中的信息来将物理信号恢复到初始值。

3.随着存储器组件的尺寸减小,存储器单元的密度已经大大增加。对特定存储器单元或存储器单元组的重复存取(通常称为“行锤击(row hammer)”)可导致附近存储器单元中的数据降级速率增加。可希望识别和刷新受行锤击影响的存储器单元。然而,用于改善行锤击效应的电路可需要包含存储器的裸片上的显著布局区域。

技术实现要素:

4.本公开的实施例中的一者提供一种设备,其包括:多个存储体;存储体逻辑区域,其位于所述多个存储体的中央;第二区域,其与所述存储体逻辑区域分离;侵略者检测器电路,其位于所述第二区域中,其中所述侵略者检测器电路经配置以产生对应于侵略行的匹配地址;及刷新地址产生器,其位于所述存储体逻辑区域中,其中所述刷新地址产生器经配置以至少部分基于所述匹配地址产生刷新地址。

5.本公开的实施例中的另一者提供一种方法,其包括:用对应的多个侵略者检测器电路监测多个存储体的行存取操作;用所述多个侵略者检测器电路产生多个匹配地址,所述多个匹配地址中的每一者对应于所述多个存储体中的一者;响应于全存储体目标刷新命令,将来自所述侵略者检测器电路的所述多个匹配地址提供到多路复用器;及以时间交错的方式从所述多路复用器输出所述多个匹配地址中的个别者。

6.本公开的实施例中的另一者提供一种存储器装置,其包括:多个存储体;及刷新控制电路,其包括位于定位在所述多个存储体的中央的存储体逻辑区域中的刷新电路组件,和位于与所述存储体逻辑区域分离的第二区域中的行锤击刷新(rhr)电路组件。

附图说明

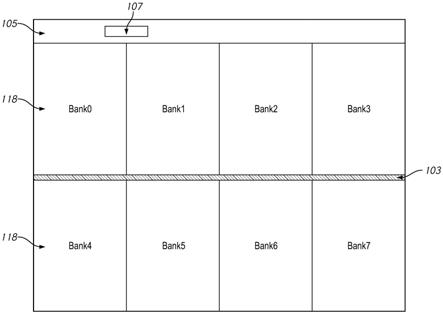

7.图1是根据本公开的实施例的半导体装置的布局图。

8.图2是根据本公开的实施例的半导体装置的框图。

9.图3是根据本公开的实施例的刷新控制电路的框图。

10.图4是根据本公开的实施例的时序图。

11.图5是根据本公开的实施例的刷新控制电路的部分的框图。

具体实施方式

12.特定实施例的以下描述本质上仅是示范性的,且绝不希望限制本公开的范围或其应用或使用。在本系统及方法的实施例的以下详细描述中,参考附图,附图形成本系统及方法的一部分且通过说明来展示可实践所描述系统及方法的特定实施例。足够详细地描述这些实施例以使所属领域的技术人员能够实践当前揭示的系统及方法,且应理解,可利用其它实施例且可在不背离本公开的精神及范围的情况下进行结构及逻辑改变。此外,为了清楚起见,在某些特征对于所属领域的技术人员来说是显而易见时,将不对所述特征进行详细论述,以便不使本公开的实施例的描述模糊。因此,以下详细描述不应以限制意义来理解,且本公开的范围仅由所附权利要求书定义。

13.易失性存储器装置中的信息可存储在存储器单元中(例如,作为电容元件上的电荷),且可随时间衰减。存储器单元可被组织成行(字线)和列(位线),且存储器单元可逐行地刷新。对存储器的特定行(例如,侵略行)的重复存取可导致相邻行(例如,受害行)中的衰减速率增加,这是由于例如行之间的电磁耦合。为了防止信息丢失,可需要识别侵略行,使得可刷新对应的受害行以减少信息衰减。

14.可监测行存取操作以确定哪些行是侵略者或潜在侵略者。为了简洁起见,作为潜在侵略者的行在本文中也将称为侵略者或侵略行。在一些应用中,可监测每个存取操作以识别侵略行。例如,可基于给定时间段内对行的存取次数来识别侵略行。在一些应用中,行锤击事件可通过对经存取行地址进行取样而不是监测每个存取来识别。例如,可产生取样布防(arming)信号,且每次激活取样布防信号时,可对行地址总线上的行地址的当前值进行取样(例如,锁存)。可基于经取样行地址中的一或多者来识别(若干)侵略行。使用任一技术,可使用经识别侵略行来计算受害行。可刷新受害行以减少信息衰减。用于识别侵略行、受害行且导致受害行被刷新的电路可统称为行锤击刷新电路。

15.存储器阵列可被分成称为存储体的部分。可为每一存储体提供用于特定功能的电路。也就是说,每一存储体可具有其自身的用于特定功能的专用电路。例如,每一存储体可具有其自身的行锤击刷新电路。因此,随着存储体的数量增加,行锤击刷新电路的数量也增加,这可增加行锤击电路的布局区域。通常,每一存储体的电路设置在距不同存储体近似等距的位置中(例如,靠近存储体),有时被称为存储体逻辑区域。将所有存储体的电路放置在存储体逻辑区域中可减小跨存储体的信号时间的差,这可使存储器操作的同步更容易。但是,对于在存储体层级控制的许多功能,存储体逻辑区域可能挤满了许多电路。因此,增加存储体逻辑区域中的电路可需要增加包含存储器阵列的裸片的尺寸。因此,可希望将电路放置在裸片上的较不拥挤的另一位置中和/或在存储体之间共享电路。

16.图1是根据本公开的实施例的半导体装置的布局图。布局图展示半导体装置100的八个存储体118(bank0-7)的布局。在其它实例实施例的布局中,可包含更多或更少的存储体。在靠近存储体118的区域中是存储体逻辑区域103。用于控制存储体118的存储器操作的一或多个电路可位于此区域中。例如,用于每一存储体118的行解码器和/或列解码器可设置在存储体逻辑区域103中。通常,每一存储体的行锤击刷新电路(其可为刷新控制电路(图1中未展示,更多细节参见图2)的组件)可设置在存储体逻辑区域103中。存储体逻辑区域103可为受晶体管的实际区域尺寸限制(例如,aa限制)的间距区域。因此,增加存储体逻辑区域103中的电路的数量可需要增加存储体逻辑区域103的尺寸,这反过来可增加裸片尺

寸。

17.半导体装置100可包含在与存储体逻辑区域103分离的区域中的中央命令区域105。在一些实例中,中央命令区域105可在半导体装置100的外围处或附近。在一些实例中,中央命令区域105可接近或邻近(例如,靠近)半导体装置100的dq垫(图1中未展示,更多细节参见图2)。中央命令区域105可包含用于控制半导体装置100的存储器操作的电路。例如,中央命令区域105可包含命令地址输入电路和/或io电路(图1中未展示,更多细节参见图2)。在一些应用中,中央命令区域105可至少部分基于存储器阵列的大小且并非aa限制的。因此,在一些应用中,中央命令区域105中可存在未使用的区域。尽管在图1中,中央命令区域105被展示为在半导体装置100的顶部部分的外围处,但在其它实施例中,中央命令区域105可位于半导体装置100的其它区域中。

18.根据本公开的实施例,行锤击刷新电路107的至少一些组件可定位在存储体逻辑区域103的外部。例如,如图1中展示,行锤击刷新电路107的至少一些组件可位于中央命令区域105中而不是在存储体逻辑区域103中。在一些应用中,定位行锤击刷新电路107的一些组件可允许跨存储体共享组件中的一或多者。在一些应用中,此可减少存储体逻辑区域103中的拥挤和/或减小裸片尺寸。在一些应用中,行锤击刷新电路的时序要求可使得将行锤击刷新电路107的至少一些组件定位在存储体逻辑区域103外部可能不会对行锤击刷新电路的性能产生有害影响。

19.图2是根据本公开的实施例的半导体装置的框图。半导体装置200可为半导体存储器装置,例如集成在单个半导体芯片上的dram装置。在一些实施例中,半导体装置200可包含在半导体装置100中。在一些实施例中,半导体装置200可具有如在图1中展示的布局图中展示的布局。

20.半导体装置200包含存储器阵列218。存储器阵列218被展示为包含多个存储体。在图2的实施例中,存储器阵列218被展示为包含八个存储体bank0到bank7。在一些实施例中,bank0-7可包含在图1的bank0-7中。更多或更少的存储体可包含在其它实施例的存储器阵列218中。每一存储体包含多个字线wl、多个位线bl及/bl,以及布置在多个字线wl与多个位线bl及/bl的交叉点处的多个存储器单元mc。字线wl的选择是由行解码器208执行,且位线bl及/bl的选择是由列解码器210执行。在图2的实施例中,行解码器208包含用于每一存储体的相应行解码器,且列解码器210包含用于每一存储体的相应列解码器。位线bl及/bl耦合到相应感测放大器(samp)。从位线bl或/bl读取的数据由感测放大器samp放大,且通过互补局部数据线(liot/b)、传送门(tg)和互补主数据线(miot/b)传送到读/写放大器220。相反地,从读/写放大器220输出的写入数据通过互补主数据线miot/b、传送门tg和互补局部数据线liot/b传送到感测放大器samp,并写入耦合到位线bl或/bl的存储器单元mc中。

21.半导体装置200可采用多个外部端子,其包含耦合到命令和地址(c/a)总线以接收命令和地址以及cs信号的命令和地址端子、接收时钟ck和/ck的时钟端子、提供数据的数据端子dq,以及接收电力供应电势vdd、vss、vddq和vssq的电力供应端子。

22.时钟端子被供应提供到输入电路212的外部时钟ck和/ck。外部时钟可为互补的。输入电路212基于ck和/ck时钟产生内部时钟iclk。iclk时钟被提供给命令解码器206和内部时钟产生器214。内部时钟产生器214基于iclk时钟提供各种内部时钟lclk。lclk时钟可用于各种内部电路的时序操作。内部数据时钟lclk经提供到输入/输出电路222以定时包含

在输入/输出电路222中的电路的操作,例如经提供到数据接收器以定时写入数据的接收。

23.c/a端子可被供应存储器地址。供应到c/a端子的存储器地址经由命令/地址输入电路202传送到地址解码器204。地址解码器204接收地址且将经解码的行地址xadd供应到行解码器208,且将经解码的列地址yadd供应到列解码器210。地址解码器204还可供应经解码的存储体地址badd,存储体地址badd可指示包含经解码的行地址xadd和列地址yadd的存储器阵列218的存储体。c/a端子可被供应命令。命令的实例包含用于控制各种操作的时序的时序命令、用于存取存储器的存取命令(例如用于执行读取操作的读取命令和用于执行写入操作的写入命令)以及其它命令和操作。存取命令可与一或多个行地址xadd、列地址yadd和存储体地址badd相关联,以指示要存取的(若干)存储器单元。

24.命令可作为内部命令信号经由命令/地址输入电路202提供到命令解码器206。命令解码器206包含用于解码内部命令信号以产生用于执行操作的各种内部信号和命令的电路。例如,命令解码器206可提供用于选择字线的行命令信号及用于选择位线的列命令信号。

25.装置200可接收存取命令,所述存取命令是读取命令。当接收读取命令且适时用读取命令供应存储体地址、行地址及列地址时,从对应于行地址和列地址的存储器阵列218中的存储器单元读取读取数据。读取命令由命令解码器206接收,命令解码器206提供内部命令,使得将来自存储器阵列218的读取数据提供到读/写放大器220。读取数据经由输入/输出电路222从数据端子dq输出到外部。

26.装置200可接收存取命令,所述存取命令是写入命令。当接收写入命令且适时用写入命令供应存储体地址、行地址及列地址时,将供应到数据端子dq的写入数据写入到对应于行地址和列地址的存储器阵列218中的存储器单元。写入命令由命令解码器206接收,命令解码器206提供内部命令,使得写入数据由输入/输出电路222中的数据接收器接收。还可将写入时钟提供到外部时钟端子,以对输入/输出电路222的数据接收器接收写入数据进行定时。写入数据经由输入/输出电路222供应到读/写放大器220,并由读/写放大器220供应到存储器阵列218,以写入到存储器单元mc中。

27.装置200还可接收命令而导致其实行一或多个刷新操作作为自刷新模式的部分。在一些实施例中,自刷新模式命令可从外部发出到存储器装置200。在一些实施例中,自刷新模式命令可由装置的组件周期性地产生。在一些实施例中,当外部信号指示自刷新进入命令时,也可激活刷新信号aref。刷新信号aref可为当命令解码器206接收到指示进入自刷新模式的信号时激活的脉冲信号。刷新信号aref可在命令输入之后立即激活一次,且此后可在所要内部时序循环地激活。刷新信号aref可用于控制自刷新模式期间的刷新操作的时序。因此,刷新操作可自动地继续。自刷新退出命令可导致刷新信号aref的自动激活停止。

28.刷新信号aref被供应到刷新控制电路216。刷新控制电路216将刷新行地址rxadd供应到行解码器208,行解码器208可刷新由刷新行地址rxadd指示的一或多个字线wl。在一些实施例中,刷新地址rxadd可表示单个字线。在一些实施例中,刷新地址rxadd可表示多个字线,这些字线可由行解码器208循序地或同时地刷新。在一些实施例中,由刷新地址rxadd表示的字线的数量可因刷新地址而异。刷新控制电路216可控制刷新操作的时序,且可产生并提供刷新地址rxadd。刷新控制电路216可受控制以改变刷新地址rxadd的细节(例如,如何计算刷新地址、刷新地址的时序、由地址表示的字线的数量),或可基于内部逻辑进行操

作。

29.刷新控制电路216可选择性地输出目标刷新地址(例如,受害地址)或自动刷新地址(automatic refresh address(auto-refresh address))作为刷新地址rxadd。自动刷新地址可来自基于刷新信号aref的激活而提供的地址序列。刷新控制电路216可以由aref确定的速率循环通过自动刷新地址序列。在一些实施例中,自动刷新操作通常可以使得循环自动刷新地址序列的时序发生,使得在给定字线的自动刷新操作之间的时间内,预期没有信息降级。换句话说,可执行自动刷新操作使得每一字线以比预期的信息衰减速率更快的速率刷新。

30.刷新控制电路216还可基于存储器阵列218中的附近地址(例如,对应于侵略行的侵略地址)的存取模式来确定作为需要刷新的地址(例如,对应于受害行的受害地址)的目标刷新地址。刷新控制电路216可使用装置200的一或多个信号来计算目标刷新地址rxadd。例如,刷新地址rxadd可为基于由地址解码器提供的行地址xadd计算的。刷新控制电路216可沿着行地址总线对由地址解码器204提供的行地址xadd的当前值进行取样,并基于经取样地址中的一或多者确定目标刷新地址。

31.虽然一般来说,本公开涉及确定侵略和受害字线和地址,但应当理解,如本文中使用,侵略字线不一定需要导致相邻字线中的数据降级,而受害字线不一定需要经受此降级。刷新控制电路216可使用一些准则来判断地址是否是侵略地址,这可捕获潜在的侵略地址而不是明确地确定哪些地址是侵略者。例如,刷新控制电路216可基于对地址的存取模式来确定潜在的侵略地址,且此准则可包含并非侵略者的一些地址,并且遗漏是侵略者的一些地址。类似的受害地址可基于哪些字线预期受侵略者影响来确定,而不是明确地确定哪些字线正在经历数据衰减速率的增加。

32.刷新地址rxadd可具有基于刷新信号aref的时序的时序。刷新控制电路216可具有对应于aref的时序的时隙,且可在每一时隙期间提供一或多个刷新地址rxadd。在一些实施例中,目标刷新地址可在时隙中发出(例如,“窃取”所述时隙),所述时隙原本将被分配给自动刷新地址。在一些实施例中,可为目标刷新地址保留特定时隙,且刷新控制电路216可确定是否提供目标刷新地址,不在所述时隙期间提供地址,或代替性地在所述时隙期间提供自动刷新地址。

33.目标刷新地址可基于从地址解码器204接收的经取样行地址xadd的随时间的特征。刷新控制电路216可在于行地址总线上提供当前行地址xadd时对其进行取样,以确定其随时间的特性。取样可间歇地发生,其中每一样本基于随机或半随机时序获得。刷新控制电路216可使用不同方法来基于经取样的行地址xadd计算目标刷新地址。例如,刷新控制电路216可确定给定行是否是侵略地址,然后计算并提供对应于侵略地址的受害地址相的地址作为目标刷新地址。在一些实施例中,多于一个受害地址可对应于给定的侵略地址。在此情况下,刷新控制电路可将多个目标刷新地址排队,并在确定应提供目标刷新地址时循序地提供。刷新控制电路216可立刻提供目标刷新地址,或可将目标刷新地址排队以在稍后时间(例如,在可用于目标刷新的下一个时隙中)提供。

34.如图2中展示,刷新控制电路216中的至少一些可包含在半导体装置200的存储体逻辑区域203中。在一些实施例中,存储体逻辑区域203可对应于图1中展示的存储体逻辑区域103。位于存储体逻辑区域203中的刷新控制电路216的电路组件被展示为刷新电路组件

228。根据本公开的实施例,刷新控制电路216的一些rhr电路组件226可位于与存储体逻辑区域203分离的区域中。例如,中央命令区域(例如,图1中的中央命令区域105)在io电路222和/或dq垫附近。在一些实施例中,rhr电路组件226可包含用于从行地址xadd确定侵略行地址并将侵略行地址提供到刷新电路组件228的电路。在一些应用中,将rhr电路组件226中的至少一些定位在存储体逻辑区域203外部可防止裸片尺寸增加和/或减小裸片尺寸。

35.电力供应端子被供应电力供应电势vdd及vss。电力供应电势vdd和vss供应到内部电压产生器电路224。内部电压产生器电路224基于供应到电力供应端子的电力供应电势vdd和vss产生各种内部电势vpp、vod、vary、vperi及类似者。内部电势vpp主要用于行解码器208中,内部电势vod及vary主要用于包含在存储器阵列218中的感测放大器samp中,且内部电势vperi用于许多外围电路块中。

36.电力供应端子也被供应电力供应电势vddq和vssq。将电力供应电势vddq及vssq供应到输入/输出电路222。在本公开的实施例中,供应到电力供应端子的电力供应电势vddq和vssq可为与供应到电力供应端子的电力供应电势vdd和vss相同的电势。在本公开的另一实施例中,供应到电力供应端子的电力供应电势vddq和vssq可为与供应到电力供应端子的电力供应电势vdd和vss不同的电势。供应到电力供应端子的电力供应电势vddq及vssq用于输入/输出电路222,使得由输入/输出电路222产生的电力供应噪声不会传播到其它电路块。

37.图3是根据本公开的实施例的刷新控制电路的框图。在一些实施例中,刷新控制电路316可包含在图2的刷新控制电路216中。展示刷新控制电路316的某些内部组件和信号以说明刷新控制电路316的操作。刷新控制电路316可包含取样时序电路330、取样电路331、侵略者检测器电路332、行锤击刷新(rhr)状态控制电路336和刷新地址产生器334。刷新控制电路316可从命令解码器(例如,命令解码器206)接收一或多个信号,例如刷新信号aref和存取信号,例如激活信号act和预充电信号pre。刷新信号aref可为周期性信号,其可指示何时将要发生自动刷新操作。存取信号act和pre通常可与行地址xadd一起作为存取操作的部分提供。可提供激活信号act以激活存储器的给定存储体。可提供预充电信号pre以对存储器的给定存储体预充电。刷新控制电路316可从地址解码器(例如,地址解码器204)接收行地址xadd。行地址xadd可为包含多位(它们可串行或并行传输)的信号,且可对应于经激活的存储体的特定行。刷新控制电路316以基于刷新信号aref的时序例如向行解码器(例如行解码器208)提供刷新地址rxadd,其中刷新地址中的一些是基于经接收的行地址xadd。

38.如图3中展示,刷新控制电路316的一些组件可位于存储体逻辑区域303外部的分离区域305中。在一些实施例中,分离区域305可对应于中央命令区域105,且存储体逻辑区域303可对应于存储体逻辑区域103。在一些实施例中,位于分离区域305中的刷新控制电路316的组件可包含rhr电路组件326。在图3中展示的实例中,取样时序电路330、取样电路331、侵略者检测器电路332和rhr控制电路336位于分离区域305中。在一些实施例中,可为包含在包含刷新控制电路316的半导体装置中的每一存储体提供包含在分离区域305中的rhr电路组件326。在一些实施例中,rhr电路组件326的一些或全部组件可跨多个存储体共享。在图3中展示的实例中,取样时序电路330、取样电路331和rhr控制电路336跨所有存储体共享。如由多个框指示,可为每一存储体提供侵略者检测器电路332。

39.在一些实施例中,侵略者检测器电路332可响应于取样信号sample的激活而对当

前行地址xadd进行取样。在一些实施例中,经取样地址可存储在侵略者电路332中和/或与先前存储的地址进行比较。侵略者检测器电路332可基于当前取样的行地址xadd和/或先前取样的行地址提供匹配地址hitxadd。rhr状态控制电路336可提供信号rhr以指示应发生行锤击刷新(例如,对应于经识别的侵略行的受害行的刷新)。rhr状态控制电路336还可提供内部刷新信号iref,以指示应发生自动刷新。响应于rhr或iref的激活,刷新地址产生器334可提供刷新地址rxadd,其可为自动刷新地址,或可为对应于与匹配地址hitxadd相对应的侵略行的受害行的一或多个受害地址。行解码器可响应于刷新地址rxadd和行锤击刷新信号rhr而执行刷新操作。行解码器可基于刷新地址rxadd和内部刷新信号iref来执行自动刷新操作。

40.在其中通过取样(与监测每个存取操作相反)来监测行存取的实施例中,取样时序电路330提供取样布防信号armsample。信号armsample可为二进制信号,其可处于高逻辑电平(其可由第一电压表示,例如vdd)或低逻辑电平(其可由第二电压表示,例如接地或vss)。armsample的激活可为“脉冲”,其中armsample升高到高逻辑电平然后返回到低逻辑电平。取样时序电路330可具有提供armsample的激活的概率。

41.取样电路331可接收取样布防信号armsample以及存取信号act和pre。基于这些信号,取样电路331可提供取样信号sample的激活。取样电路331可使用信号act和pre中的一者或两者来确保信号sample的每一次激活与存取操作相关联。取样电路331可响应于信号act/pre和armsample而随机地确定何时(和/或如何)提供信号sampling的一或多次激活。在其它实例中,取样电路331可以部分随机或非随机方式激活信号sampling。

42.侵略者检测器电路332可从地址解码器接收行地址xadd且从取样电路331接收信号sample。当地址解码器和命令解码器将存取操作(例如,读取和写入操作)指引到存储器单元阵列(例如,图2的存储器单元阵列218)的不同行时,行地址总线上的行地址xadd可改变。每次侵略者检测器电路332接收信号sample的激活(例如,脉冲)时,侵略者检测器电路332可对xadd的当前值进行取样。在一些实施例中,侵略者检测器电路332可提供xadd的当前取样的值作为匹配地址hitxadd。如将在本文更详细地描述,刷新地址产生器334可提供与匹配地址hitxadd相关联的一或多个受害地址作为刷新地址rxadd。

43.在一些实施例中,响应于取样信号sample的激活,侵略者检测器电路332可基于经取样的行地址xadd来确定一或多个行是否是侵略行,且可提供经识别的侵略行作为匹配地址hitxadd。作为此确定的部分,侵略者检测器电路332可响应于sample的激活而记录(例如,通过在寄存器中锁存和/或以其它方式存储)xadd的当前值。可将xadd的当前值与侵略者检测器电路332中的先前记录的地址(例如,存储在锁存器/寄存器中的地址)进行比较,以确定经取样地址随时间的存取模式。如果侵略者检测器电路332确定地址(在一些实施例中,其可为当前地址或者先前存储的地址)是侵略地址,那么可将经识别的侵略者提供为匹配地址hitxadd。在一些实施例中,可响应于信号sampling而提供匹配地址hitxadd。在一些实施例中,匹配地址(例如,侵略地址)hitxadd可存储在锁存器电路中,以稍后在刷新地址产生器334确定需要匹配地址时供刷新地址产生器334检索。

44.在一个实例实施例中,为了确定当前地址xadd是否是侵略地址,可存储当前行地址xadd的经取样值(例如,锁存在锁存器电路中)。sample的激活还可导致侵略者检测器电路332将当前取样的行地址xadd与侵略者检测器电路332中的先前存储的地址进行比较。如

果当前行地址xadd与经存储地址匹配,那么可将当前行地址xadd提供为匹配地址hitxadd。

45.在另一实例实施例中,侵略者检测器电路332可将经取样地址的值存储在寄存器中,且可具有与经存储地址中的每一者相关联的计数器。当激活sample时,如果当前行地址xadd与经存储地址中的一者匹配,那么计数器的值可递增。响应于sample的激活,侵略者检测器电路332可提供与最高值计数器相关联的地址作为匹配地址hitxadd。在其它实例中,可使用识别侵略地址的其它方法。

46.在其中监测每个行存取命令的实施例中,可省略取样时序电路330和取样电路331。在这些实施例中,侵略者检测器电路332可响应于act/pre信号而不是sample信号而执行上述功能。

47.rhr状态控制电路336可接收刷新信号aref并提供行锤击刷新信号rhr。刷新信号aref可周期性地产生,且可用于控制刷新操作的时序。存储器装置可实行一序列自动刷新操作,以便周期性地刷新存储器装置的行。可产生rhr信号以指示装置应刷新特定的目标行(例如,受害行)而不是来自自动刷新地址序列中的地址。rhr状态控制电路336可使用内部逻辑来提供rhr信号。在一些实施例中,rhr状态控制电路336可基于aref的特定激活次数(例如,aref的每4次激活)提供rhr信号。在一些实施例中,rhr状态控制电路336可基于与侵略字线相关联的受害字线的数量来提供行中的信号rhr的激活次数。rhr状态控制电路336还可提供内部刷新信号iref,其可指示应发生自动刷新操作。在一些实施例中,可产生信号rhr和iref使得它们不同时活动(例如,两者不同时处于高逻辑电平)。

48.在一些实施例中,刷新控制电路316可响应于刷新信号aref的每次激活而执行多个刷新操作。例如,每次接收到刷新信号aref时,刷新控制电路316可通过提供n个不同的刷新地址rxadd来执行n个不同的刷新操作。每次刷新操作可被称为“泵”。在一些实施例中,刷新控制电路316可具有固定模式,其中一些泵被分配给自动刷新操作且一些泵被分配给目标刷新操作。在一些实施例中,刷新控制电路316可动态地确定给定泵是否与自动刷新操作、目标刷新操作或无刷新操作相关联。

49.在一些实施例中,例如图3中展示的实施例中,刷新控制电路316的刷新控制电路组件328可包含在包含刷新控制电路316的半导体装置的存储体逻辑区域303中。在图3中展示的实例中,刷新地址产生器334可包含在存储体逻辑区域303中。如多个框指示,在一些实施例中,可为每一存储体提供刷新控制电路组件328,例如刷新地址产生器334。

50.刷新地址产生器334可接收行锤击刷新信号rhr和匹配地址hitxadd。匹配地址hitxadd可表示侵略行。刷新地址产生器334可基于匹配地址hitxadd确定一或多个受害行的位置,并在信号rhr指示目标刷新操作时将所述位置提供为刷新地址rxadd。在一些实施例中,受害行可包含与侵略行物理上相邻的行(例如,hitxadd 1及hitxadd-1)。在一些实施例中,受害行也可包含与侵略行的物理相邻行物理上相邻的行(例如,hitxadd 2及hitxadd-2)。在其它实例中,可使用受害行与经识别的侵略行之间的其它关系。例如,也可刷新 /-3、 /-4和/或其它行。

51.刷新地址产生器334可基于行锤击刷新信号rhr来确定刷新地址rxadd的值。

52.在一些实施例中,当信号rhr不活动时,刷新地址产生器334可提供一序列自动刷新地址中的一者。当信号rhr活动时,刷新地址产生器334可提供目标刷新地址(例如受害地址)作为刷新地址rxadd。在一些实施例中,刷新地址产生器334可计数信号rhr的激活,且可

比离侵略地址更远的受害行(例如,hitxadd /-2)更频繁地提供更近的受害行(例如,hitxadd /-1)。

53.在图3中展示的实例中,包含刷新控制电路316的半导体装置包含分成八个存储体的存储器阵列。因此,刷新控制电路316可包含八个侵略者检测器电路332和八个刷新地址产生器334。侵略者检测器电路332可分别提供匹配地址hitxadd0-7。当侵略者检测器电路332位于存储体逻辑区域303中的与刷新地址产生器334分离的区域305中时,可使用额外控制逻辑来将匹配地址hitxadd0-7路由到适当的刷新地址产生器334。例如,在一些实施例中,例如图3中展示的实施例中,可包含多路复用器340以向刷新地址产生器334提供hitxadd0-7的适当匹配地址。

54.多路复用器340可接收每一存储体的匹配地址(hitxadd0-7)。可对单个存储体或多个存储体执行刷新操作,例如在全存储体刷新操作期间对所有存储体执行刷新操作。在一些应用中,可同时刷新多个存储体中的一或多个行。在其它应用中,为了减小峰值电流消耗,多个存储体中的一或多个行的刷新可随着时间交错(例如,以时间交错的方式刷新)。为了对单个存储体执行目标刷新操作,仅为被刷新为hitxaddsel的存储体提供匹配地址hitxadd0-7中的一个地址。但是,在要执行目标刷新操作的全存储体刷新操作期间,要对半导体装置的每一存储体刷新的(若干)受害行可为不同的。因此,可提供每一存储体的匹配地址。多路复用器340可响应于来自rhr控制电路336的rhr信号而在不同的时间输出不同的匹配地址hitxadd0-7作为hitxaddsel。多路复用器340可将选定的匹配地址hitxaddsel输出到另一多路复用器342。

55.多路复用器342可用于将来自分离区域305的hitxaddsel或者行地址xadd提供到刷新地址产生器334。hitxaddsel或xadd可作为行地址信号graf从第二多路复用器342输出。多路复用器342是否将hitxaddsel或行地址xadd输出为行地址graf基于是否执行目标刷新地址。例如,当rhr信号活动时,可将hitxaddsel提供为graf,且当rhr信号不活动时,可将xadd提供为graf。

56.在一些实施例中,刷新电路组件328可包含地址锁存器344以将行地址graf提供到刷新地址产生器334。在目标刷新操作期间,存储体逻辑区域303的地址锁存器344可锁存graf。地址锁存器344可将经锁存地址提供到刷新地址产生器334,刷新地址产生器334可使用经锁存地址来确定刷新地址rxadd,如本文中所描述。在一些应用中,地址锁存器344可增加用于将行地址信号从分离区域305提供到存储体逻辑区域303和/或执行rhr操作的时序容差。在一些实施例中,刷新电路组件328可包含多路复用器346,多路复用器346从地址锁存器344接收xadd且从刷新地址产生器334接收rxadd。多路复用器346可基于是否已接收到刷新命令来输出xadd或者rxadd。在一些实施例中,可将多路复用器346的输出提供到行解码器。

57.行解码器可基于经接收的信号和地址对存储器阵列(未展示)执行一或多个操作。例如,响应于激活信号act和行地址xadd(以处于低逻辑电平的iref和rhr),行解码器可指引对指定的行地址xadd的一或多个存取操作(例如,读取操作)。响应于rhr信号是活动的,行解码器可刷新刷新地址rxadd。

58.图4是根据本公开的实施例的时序图。时序图400说明当要执行目标刷新操作时在全存储体刷新操作期间各种信号的状态。在一些实施例中,时序图400可说明例如半导体装

置200的半导体装置的各种信号的状态,在一些实例中,半导体装置200可包含刷新控制电路316。

59.时序图400的第一线指示刷新操作,例如全存储体刷新操作发生的周期。周期的长度可至少部分基于半导体装置的规格。接下来的线402指示存储体刷新信号(bras_0-7)的状态。当半导体装置的存储体开始执行刷新操作时,存储体刷新信号bras0-7可从非活动状态(例如,低逻辑)转变到活动状态(例如,高逻辑),且可在刷新操作之后转变回到非活动状态。如图4中展示,存储体刷新信号可以时间交错的方式从非活动状态转变到活动状态。换句话说,在全存储体刷新操作期间,并非所有存储体都可同时执行刷新操作。在一些应用中,交错可减少半导体装置的电流消耗。

60.线403指示在多路复用器,例如多路复用器340和/或342的输出处提供的匹配地址。线404指示由地址锁存器,例如地址锁存器344提供到刷新地址产生器,例如刷新地址产生器334的地址。如图4中展示,存储体0(b0)的匹配地址可由多路复用器在t0或大约t0时提供,此可与bras_0转变到活动状态同时或大约同时。在由多路复用器提供匹配地址b0的同时或大约同时,匹配地址b0可被锁存并提供到刷新地址产生器。类似地,当bras_1信号转变到活动状态时,可在时间t1或大约时间t1提供存储体1(b1)的匹配地址,从而导致用于存储体1的地址锁存器锁存地址b1。此可继续,直到已经为半导体装置的所有存储体提供和锁存匹配地址为止。

61.经锁存地址b0-7可用于为每一存储体的刷新地址产生器播种(seed)以产生刷新地址。在一些实施例中,这些地址可对应于对应存储体中的侵略行的受害行。

62.图5是根据本公开的实施例的刷新控制电路的部分的框图。在一些实施例中,刷新控制电路516可包含在刷新控制电路216和/或316中。

63.在一些应用中,包含刷新控制电路516的半导体装置的存储体可包含额外的行。这些额外的行可用于替换存储体中的故障行。这有时被称为冗余。当使用额外的行来替换存储体中的行时,将所述行的地址映射到额外的行。此映射可通过编程熔丝和/或反熔丝来执行。存储在熔丝和/或反熔丝中的冗余信息560可位于半导体装置的存储体逻辑区域503中。在一些应用中,冗余信息560对于在与半导体装置的存储体逻辑区域503(例如,图5中未展示的中央命令区域)分离的区域中的电路而言可不容易获得。因此,如果行已经被额外的行替换,那么可需要校正由定位在分离区域中的行锤击刷新电路(例如,rhr电路组件226、326)提供的存储体的匹配地址(graf)。

64.如图5中展示,行地址graf可从行锤击刷新电路(例如,图3中展示的多路复用器342)接收并由地址锁存器544存储。可将经锁存地址与冗余信息560进行比较,以查看由经锁存地址指示的行是否已被额外的行替换。如果冗余信息560不指示与经锁存地址相关联的行已经被替换,那么多路复用器562可将最初接收的graf地址输出到行地址锁存器564,行地址锁存器564将所述地址提供到刷新地址产生器534。如果冗余信息560确实指示与经锁存地址相关联的行已被额外的行替换,那么多路复用器562可至少部分基于冗余信息560输出与用于替换原始行的额外的行相关联的地址(例如,额外行地址)。额外行地址可由行地址锁存器564锁存并提供到刷新地址产生器534。基于graf地址或者额外行地址,刷新地址产生器534可输出刷新地址rxadd。

65.可选地,在一些实施例中,为了确保提供足够的时间以在经锁存地址与冗余信息

560之间进行比较,可添加一个刷新循环延迟566。这可延迟目标刷新地址的刷新地址的输出,直到下一个目标刷新操作。

66.如本文中描述,在存储体逻辑区域外部的半导体装置的区域中包含刷新控制电路的行锤击刷新电路的至少一些组件可通过利用半导体装置的较不拥挤的区域来降低裸片尺寸要求。在一些应用中,将组件定位在存储体逻辑外部可允许共享一些行锤击刷新电路组件,此可进一步降低裸片尺寸要求。

67.当然,应了解,根据本系统、装置及方法,本文中描述的实例、实施例或过程中的任一者可与一或多个其它实例、实施例及/或过程组合,或在分离装置或装置部分当中分离和/或执行。

68.最后,以上讨论意在仅说明本系统且不应被解释为将所附权利要求书限于任何特定实施例或实施例组。因此,虽然已经参考示范性实施例对本系统进行特别详细描述,但还应了解,在不背离如随后在所附权利要求书中阐述的本系统的更广泛及预期的精神及范围的情况下,所属领域的一般技术人员可设计出许多修改及替代实施例。因此,说明书及附图应被视为说明性方式且不希望限制所附权利要求书的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。