1.本发明主要涉及随机数产生,特别是涉及使用多个随机数产生器以产生随机数位序列的方法及系统。

背景技术:

2.多种随机数产生的技术已为本领域所习知。举例来说,美国专利4,905,176叙述一种随机数产生器,可阻绝加密攻击(cryptographic attack)。该随机数产生器的运作原则是基于虚拟随机数产生器输出的低频取样,该虚拟随机数产生器是以自由运转的环式震荡器(ring oscillator)的变动频率所运作。

技术实现要素:

3.在此所叙述的本发明的实施例提供一种随机数产生器(random-number generator;rng),包含多个高频(high-frequency;hf)时钟脉冲产生器、多个低频(low-frequency;lf)时钟脉冲产生器、多个数字随机数产生器(digital random-number generator circuit;drng),及多工器(multiplexer)。高频时钟脉冲产生器设置以产生在第一频率范围内的高频时钟脉冲信号。低频时钟脉冲产生器设置以产生在第二频率范围内、低于第一频率范围的低频时钟脉冲信号。每一drng设置以(i)从高频时钟脉冲信号中所提取的高频时钟脉冲信号及(ii)从高频时钟脉冲信号中所提取的低频时钟脉冲信号,借此取得随机数位序列。多工器设置以从drng所产生的随机数位序列,产生随机数位的输出序列。

4.在某些实施例中,一给定的drng包含:(i)线性回馈移位寄存器(linear feedback shift register;lfsr),由高频时钟脉冲信号所进行时钟脉冲控制;及(ii)正反器(flip-flop;ff),设置以根据低频时钟脉冲信号,取样lfsr的输出。在各种实施例中,lfsr中的至少两者在以下特征中的一或多个会彼此不同:(i)初始的种值(seed)、(ii)回馈分接头(feedback-tap)组态,及(iii)多个串联正反器(cascaded flip-flop)。在一替代的实施例中,一给定的drng包含正反器,设置以根据低频时钟脉冲信号,取样高频时钟脉冲信号。

5.在所揭露的实施例中,drng接收不同的输入时钟脉冲信号对,每一对包含高频时钟脉冲信号及低频时钟脉冲信号。在一实施例中,高频时钟脉冲产生器、低频时钟脉冲产生器及drng,在空间上分散于集成电路(integrated circuit;ic)的某一区域上。在某些实施例中,随机数产生器更包含一或多个模拟噪声源(analog noise source),设置以添加模拟噪声至低频时钟脉冲产生器及高频时钟脉冲产生器中的一或多个。

6.在某些实施例中,多工器设置以执行在drng之间交替的多工顺序,以多工传输随机数位序列。在一范例实施例中,多工器设置以从随机数位序列中的一或多个随机数位序列的选定的位,取得多工顺序。

7.在一实施例中,高频时钟脉冲产生器及该等低频时钟脉冲产生器是以成对的方式所设置,每一对包含高频时钟脉冲产生器及低频时钟脉冲产生器。在另一实施例中,高频时

generator circuit;drng)。每一drng具有选定的一对{高频时钟脉冲信号,低频时钟脉冲信号}作为输入。通常,不同的drng具有不同配对的{高频时钟脉冲信号,低频时钟脉冲信号},即使任何独立的时钟脉冲信号(高频或低频)可用以驱动不仅一个drng。

26.每一drng设置以使用其所具有的高频时钟脉冲信号及低频时钟脉冲信号,以产生随机数位序列。在某些实施例中,每一drng包括由高频时钟脉冲信号所进行时钟脉冲控制的线性回馈移位寄存器(linear feedback shift register;lfsr),以及根据低频时钟脉冲信号取样lfsr的输出的正反器(flip-flop;ff)。由于lfsr的输出是以远低于实际的lfsr时钟脉冲频率进行取样,且由于低频取样时钟脉冲通常是带有噪声的,因此产出的随机数位序列的确是高度随机的。

27.随机数产生器更包括多工器,设置以从drng所产生的随机数位序列,产生随机数位的输出序列。借由多工传输(multiplexing)多个drng的输出,所揭露的随机数产生器可提供高吞吐量的随机数。在某些实施例中,多工器更借由使用在多个drng之间交替的多工顺序,以强化其输出的随机性。

28.由于时钟脉冲产生器(高频及低频)是自由运作的,彼此之间并没有同步,且又带有噪声,再加上由于每一drng具有不同配对的{高频时钟脉冲信号,低频时钟脉冲信号},因此不同的drng所产生的随机数位序列彼此之间几乎没有或者完全没有相关。如此一来,多工器所产生的位的多工序列具有高度的随机性。

29.借由在不同的组合中重复使用相同的高频时钟脉冲信号及低频时钟脉冲信号,若干高频时钟脉冲产生器及低频时钟脉冲信产生器可用以驱动大量的drng,而毋须牺牲随机性。此特征降低了随机数产生器的成本、尺寸及耗电量。

30.在某些实施例中,随机数产生器是以部分的集成电路(integrated circuit;ic)所执行,且各种随机数产生器的元件(高频时钟脉冲产生器、低频时钟脉冲产生器,及drng)在空间上分散于ic区域上。因此,不同的时钟脉冲产生器负责改善具有不同统计数值的噪声,协助降低不同时钟脉冲信号之间的相关性。此外,即使攻击顺利导致特定的drng输出决定性的序列,但整体的随机数产生器仍会维持高度的随机。当多工顺序为随机时,此特性更是得到强化。

31.在此叙述所揭露的随机数产生器的各种范例实施及变化。

32.系统叙述

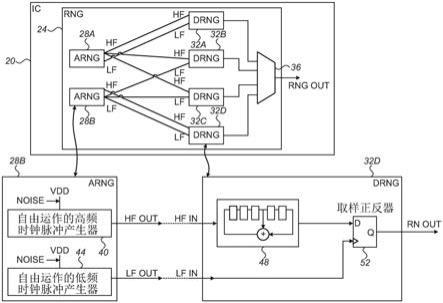

33.图1是根据本发明的实施例所绘示,包括分散式随机数产生器(random-number generator;rng)24的一种集成电路(integrated circuit;ic)20的方块图。在各种实施例中,ic 20可包括例如安全的控制器、安全的存储器装置,或者利用随机数的任何其他种类的ic。出于明确性的考量,图式中省略了rng 24以外的电路。在其他实施例中,ic 20可专门用于产生随机数。

34.rng 24包括两个或更多个模拟随机数产生器电路(arng)28,在本范例中是以arng 28a及arng 28b表示两个arng。每一arng设置以产生高频(在图1中以hf表示)时钟脉冲信号及低频(在图1中以lf表示)时钟脉冲信号。在某些实施例中,低频时钟脉冲信号频率约为千赫(khz),而高频时钟脉冲信号频率约为百万赫(mhz),惟可使用任何其他合适的频率范围。

35.rng 24更包括两个或更多个数字随机数产生器电路(drng)32,在本范例中是以32a-32d表示四个drng。每一drng 32设置以从高频时钟脉冲信号及低频时钟脉冲信号取得

随机数位序列。提供给一给定的drng 32的高频时钟脉冲信号及低频时钟脉冲信号,可由相同的arng 28或不同的arng 28所产生。一给定的时钟脉冲信号(高频时钟脉冲信号或低频时钟脉冲信号)可提供给单独的drng 32或者多个drng 32。通常,不同的drng 32具有不同配对的{高频时钟脉冲信号,低频时钟脉冲信号}。

36.rng 24更包括多工器36,也称为组合器(combiner)。多工器36设置以多工传输drng 32所产生的随机数位序列,以输出随机数位(在图1中以rng out表示)的高频率的序列。此序列被提供作为rng 24的输出。以下将解释,多工器36通常并非是从多个输入中择其一的简单的多工器,而是一种电路,将位或位群组进行串接以形成随机数位流(random bit stream)。

37.位于图1底部的插图绘示出arng 28及drng 32的内部结构。arng 28b及drng 32d被描绘作为范例;其他的arng及drng通常也分别具有类似的内部结构。

38.如左侧的插图所示,每一arng 28包括(i)高频自由运作的时钟脉冲产生器40,产生高频时钟脉冲信号(在图1中以hf out表示),及(ii)低频自由运作的时钟脉冲产生器44,产生低频时钟脉冲信号(在图1中以lf out表示)。通常,给定的arng28中的时钟脉冲产生器40及时钟脉冲产生器44彼此之间并没有同步,而且也并没有与其他arng 28的时钟脉冲产生器40及时钟脉冲产生器44同步。

39.为了提升随机性,在某些实施例中,模拟噪声(在图1中以noise表示)被添加至时钟脉冲产生器40及时钟脉冲产生器44中的其中一者或两者。模拟噪声可刻意由专门为此目的的电路所产生。噪声可被添加至时钟脉冲产生器的供给电压(在图1中以vdd表示),或者添加在协助使时钟脉冲产生器输出随机化的任何其他点。又或者,时钟脉冲产生器可负责改善来自其周边环境的模拟噪声,而毋须额外的电路。

40.如右侧的插图所示,每一drng 32包括线性回馈移位寄存器(linear feedback shift register;lfsr)48,及取样正反器(flip-flop;ff)52。每一lfsr 48包括多个正反器的串联,并带有一或多个回馈分接头(feedback-tap)。在每一drng中,lfsr 48是由提供给drng(以hf in)的高频时钟脉冲信号所进行时钟脉冲控制,且因此以高频时钟脉冲信号的频率输出虚拟随机数序列。正反器52根据提供给drng(在图1中以lf in表示)的低频时钟脉冲信号,取样出此频率下的一部分lfsr48的输出。位于正反器52的输出(在图1中以q表示)的随机数位序列被提供作为drng的输出(在图1中以rn out表示)。rn out与低频时钟脉冲信号(lf in)的频率相同。

41.多个drng 32所产生的多个rn out,被提供作为多工器36的输入。多工器36多工传输多个rn out随机数位序列,以产生高频率的rng out随机数位序列。

42.在某些实施例中,arng 28及drng 32刻意不被放置在一起,而是在空间上分散于ic 20的区域上。此空间分配是有利的,其原因有很多。举例来说,当在空间上分散时,不同的arng负责改善具有不同统计数值的模拟噪声,协助降低不同时钟脉冲信号(高频或低频)之间的相关性。如另一范例,对ic 20的特定区域的恶意攻击不太可能对单独的arng或drng除外的部分造成伤害。即使对arng或drng造成伤害而导致arng或drng输出固定的或决定性的位序列,但由于其他arng及drng仍正常运作,故整体rng out序列的随机性降低的可能性很小。

43.在各种实施例中,多工器36可用各种方式,多工传输drng 32所产生的随机数位序

列。请参考图1的设置,假设drng 32a-32d的输出分别以stream1-stream4代表。在某些实施例中,多工器36以预先定义的、决定性的、循环的多工顺序,多工传输随机数位序列。举例来说,多工器36可从stream1输出n个位(例如n=2),再从stream2输出n个位、从stream3输出n个位、从stream4输出n个位,然后再次从stream1输出n个位,依此类推。在替代的实施例中,可使用任何其他合适的决定性的多工顺序。

44.在其他实施例中,多工器36可用在多个drng之间随机交替的多工顺序,多工传输drng 32所产生的随机数位序列。在本情境中,“随机交替”一词意指(i)从一个随机数位序列交替到另一个随机数位序列的顺序是随机的,及/或(ii)从被访问时的给定的随机数位序列所提取的位个数是随机的。在另一实施例中,多工器36从一或多个随机数位序列的选定的位,取得随机数多工顺序。举例来说,多工器36可执行以下程序:

45.■

从stream1提取一个位。若该位值为"0”,则从stream2提取两个位、串接stream3的两个位、串接stream4的两个位、串接stream1的两个位。若该位值为"1”,则从stream3提取两个位、串接stream1的两个位、串接stream2的两个位、串接stream4的两个位。

46.■

从stream2提取一个位。若该位值为"0”,则从stream1提取两个位、串接stream3的两个位、串接stream4的两个位、串接stream2的两个位。若该位值为"1”,则从stream3提取两个位、串接stream2的两个位、串接stream4的两个位、串接stream1的两个位。

47.■

从stream3提取一个位,然后以类似的方式继续执行该程序。

48.以上给出的范例多工顺序,仅作为示例。在替代的实施例中,多工器36可使用任何其他合适的多工顺序,及任何其他合适的取得多工顺序的程序,例如从一或多个drng 32所产生的随机数位序列的选定的位。

49.如图1所示的rng 24及其元件,仅是为了概念上的明确性所描绘出的范例设置。在替代的实施例中,可使用任何其他合适的设置。举例来说,rng 24可包括任何其他合适数量的arng 28,及任何其他合适数量的drng 32。armg及drng之间的互连方案(即选择将哪个高频时钟脉冲信号即哪个低频时钟脉冲信号提供给每一drng)也可以任何其他合适的方式作设定。又或者,高频时钟脉冲产生器40及低频时钟脉冲产生器44并无必要被安排在组合配对中。更概括地说,高频时钟脉冲产生器40的数量可异于低频时钟脉冲产生器44的数量。

50.在某些实施例中,高频时钟脉冲产生器40产生全部具有相同频率的高频时钟脉冲信号。在其他实施例中,高频时钟脉冲产生器中的至少两者产生彼此之间频率相异的高频时钟脉冲信号。相应地,在某些实施例中,低频时钟脉冲产生器44产生全部具有相同频率的低频时钟脉冲信号。在其他实施例中,低频时钟脉冲产生器中的至少两者产生彼此之间频率相异的低频时钟脉冲信号。

51.在某些实施例中,为了提升随机性,高频时钟脉冲产生器40中的至少两者设置以在不同的时间触发。额外地或替代地,低频时钟脉冲产生器44中的至少两者可设置以在不同的时间触发。

52.在某些实施例中,所有drng 32中的所有lfsr 48被初始为相同的种值(复归值)。在其他实施例中,lfsr中的至少两者(可能是所有的lfsr)被初始至不同的种值。在一范例实施例中,lfsr 48彼此之间独立地被初始至相应的随机数值。随机数种值的初始化,可例如是借由在无需重置逻辑的情况下执行lfsr的一或多个正反器所实施,使得这些正反器在重置时被设定为任意值。

53.在某些实施例中,所有drng 32中的所有lfsr 48具有相同的回馈分接头组态(相同的序列产生多项式)。在其他实施例中,lfsr中的至少两者(可能是所有的lfsr),彼此之间的回馈分接头组态不同。在某些实施例中,所有drng 32中的所有lfsr 48具有相同数量的串接正反器。在其他实施例中,lfsr中的至少两者(可能是所有的lfsr),彼此之间的串接正反器的数量不同。

54.在另一实施例中,drng 32中的至少一者中的lfsr 48可被完整地省略。在这种drng中,正反器52使用低频时钟脉冲信号,直接对高频时钟脉冲信号进行取样。

55.在各种实施例中,rng 24及其元件可使用任何合适的硬件来实作,像是特殊应用集成电路(application-specific integrated circuit;asic)或场域可程序化逻辑闸阵列(field-programmable gate array;fpga)。在其他实施例中,可借由通用处理器实施rng 24的某些功能,通用处理器以软件中的程序执行在此所述的功能。该软件可以电子的形式,例如透过网路,而下载到处理器。或者,该软件可替代地或额外地被提供及/或储存在非暂态的有形媒体上,像是磁存储器、光存储器或电子存储器。

56.随机数产生方法叙述

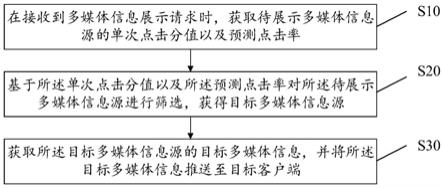

57.图2是根据本发明的实施例所绘示,使用ic 20中的rng 24的一种分散式随机数产生的方法的流程图。该方法起始于高频时钟脉冲产生的步骤60,自由运作的高频时钟脉冲产生器40产生多个高频时钟脉冲信号。同时,于低频时钟脉冲产生的步骤64,自由运作的低频时钟脉冲产生器44产生多个带有噪声的低频时钟脉冲信号。

58.于选择的步骤68,选取多对{高频时钟脉冲信号,低频时钟脉冲信号}。于序列产生步骤的步骤72,每一drng 32使用其具有的{高频时钟脉冲信号,低频时钟脉冲信号}配对,产生一随机数位序列。对于一给定的drng,使用高频时钟脉冲信号来为lfsr 48进行时钟脉冲控制,使用低频时钟脉冲信号来为正反器52进行时钟脉冲控制(即取样lfsr输出)。

59.于多工的步骤76,多工器36多工传输drng 32所产生的随机数位序列,并且输出被多工传输的随机数位序列。如以上所解释,多工顺序可以是决定性的,或者是随机的。

60.应被理解的是,上述实施例是被引用作为范例,而本发明并非限于上文所具体展示或叙述的内容。反之,本发明的范围包含上文所叙述的各种特征的组合及子组合,以及本领域的技术人员在阅读以上叙述时所能设想到,且未于现有技术中所揭露的其变化及修改。本专利申请中所参考而并入的文件应被理解为本技术不可或缺的部分,除非是已达到任何用语在这些被并入的文件中,是以与本说明书中所明示或暗示的定义冲突的方式所定义的程度,则仅应考虑本说明书中的定义。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。