1.本发明涉及接口测试技术领域,具体涉及一种多种接口时序兼容性通用验证方法。

背景技术:

2.随着物联网发展,各接口应用领域越来越广泛,应用环境越来越复杂,对于接口从设备需要应对各种各样的主设备,接口兼容性验证需求也是越来越高。

3.由于市场上的各类接口厂家不同,设计也存在着不同,所以一款推向市面的接口产品,会面对诸多接口兼容性问题风险,需要有较高的接口兼容性性能才能满足市场需求。需要把兼容性问题拦截在验证阶段,以减少投入市场后的兼容性风险。对于从设备接口的兼容性测试是十分必要的,但目前市场上缺乏灵活、方便、可控的兼容性时序拉偏测试方法,以满足各种接口的兼容性时序拉偏测试。

4.根据上述问题,本文提出一种设计方法,利用上位机软件下发测试命令,通过fpga芯片电路设计应用,灵活的输出可控制的接口验证时序,将时序测试结果返回上位机,从而满足对从设备进行接口兼容性时序的拉偏测试需求,直观准确的测试出从设备的时序兼容性性能。

技术实现要素:

5.本发明的方法解决问题是:

6.本发明的目的是解决多种接口时序兼容性验证。

7.本发明的方法解决方案是:

8.一种多种接口时序兼容性验证方法,配置上位机与fpga芯片电路的通讯接口,使用上位机软件下发接口验证时序向量存储指令,通过接口解析模块解析上位机命令,并通过主控电路单元模块将验证时序向量放在存储模块中。使用上位机软件下发时钟配置指令,接口解析模块解析上位机时钟配置命令,通过主控电路单元模块选择高频时钟源并通过时钟处理模块对时钟信号进行处理,以得到满足接口时序验证需求的时钟信号。上位机下发接口协议选择指令,接口解析模块解析接口协议选择指令,并使用主控电路单元模块调用协议处理模块对目标接口时序进行配置。上位机下发测试指令,接口解析模块解析接口测试指令,主控电路单元模块调用存储模块中已存储的验证时序向量,通过协议处理模块灵活的输出可控制的接口验证时序,并采集时序测试结果,通过主控电路单元模块存储在存储模块中。上位机发送测试结果读取命令,接口解析模块解析指令,通过主控电路单元模块调用存储模块中的测试结果,经过接口解析模块解析,由fpga芯片电路与上位机连接的通讯接口返回给上位机,从而满足对从设备接口时序验证测试的要求,直观准确的测试出从设备的时序兼容性,以满足从设备接口时序兼容性的验证需求。以满足设备接口时序拉偏性能的测试,以对未来市场应用环境有所评估。

9.本解决方案共有5个模块,以下介绍各模块功能。

10.1、接口解析模块:选择并配置上位机与fpga芯片电路的通讯接口,上位机软件发下指令,接口解析模块对指令进行解析,根据接口解析模块对命令的解析结果,通过主控电路单元模块控制调用其他模块,完成指令功能。接口解析模块也可以将测试结果进行解析,并通过与上位机连接的接口返回给上位机。

11.2、fpga存储模块:上位机下发存储指令,接口解析模块对指令进行解析,由主控电路单元将目标接口验证时序向量存储在存储模块中。

12.上位机下发测试指令,由主控电路单元调取存储模块中已存储的目标接口验证时序向量,通过协议处理模块输出验证时序向量,并且将采集的从接口返回的测试结果,通过主控电路单元模块存储在存储模块中,待上位机发送测试结果读取指令时调用。

13.3、时钟处理模块:上位机下发时钟配置指令,接口解析模块对指令进行解析,通过主控电路单元模块选择将高频时钟源,并经过时钟处理模块进行处理,以得到满足目标时钟时序需求的时钟时序。

14.4、主控电路单元模块:主控电路单元模块用于控制调用各模块工作。上位机下发存储指令,接口解析模块对指令进行解析,由主控电路单元将目标接口验证时序向量存储在存储模块中。上位机软件下发时钟配置指令,接口解析模块对指令进行解析,由主控电路单元模块调用选择高频时钟源,并调用时钟处理模块对时钟源进行信号处理,以得到满足目标时钟时序需求的时钟时序。上位机软件下发协议选择指令,接口解析模块对指令进行解析,由主控电路单元模块调用协议处理模块进行接口协议配置。上位机软件下发测试指令,接口解析模块对指令进行解析,由主控电路单元模块调用存储模块中已存储的接口验证时序向量,并调用协议处理模块,输出验证时序,同时协议处理模块采集测试结果,通过主控电路单元模块存储在存储模块中。上位机下发测试结果读取指令,接口解析模块对指令解析后,由主控电路单元模块调用存储模块中存储的测试结果,经过接口解析模块进行解析,通过fpga芯片电路与上位机连接的接口返回给上位机。

15.5、协议处理模块:在上位机发送协议选择指令时,接口解析模块对指令解析后,由主控电路单元模块调用协议处理模块,根据目标接口协议,对接口性能进行相应配置。在上位机发送测试指令时,经过接口解析模块解析命令后,由主控电路单元模块调用存储模块中的接口验证时序向量,经过协议处理模块输出接口验证时序,并经过协议处理模块采集从接口时序测试结果,通过主控电路单元模块存储在存储模块中。

附图说明

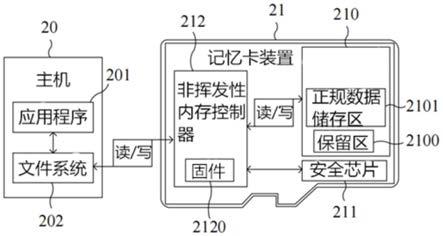

16.图1为本发明的模块框图整体流程图;

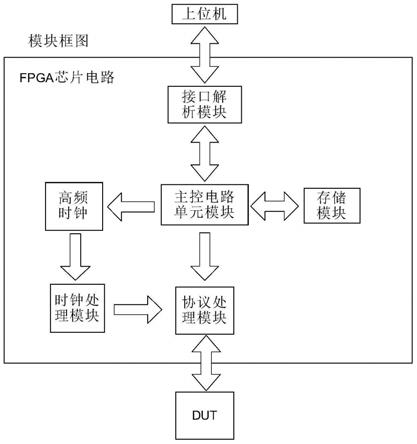

17.图2为本发明的具体实施中列举的上位机接口通讯结构图;

18.图3为本发明的具体实施中列举的高频时钟处理结构图;

19.图4为本发明的整体流程图;

具体实施方式

20.这里仅描述一个示例来说明本发明的具体实施方式,(本文中所使用软硬件实现方式,可由实现者在实际操作时指定,文中仅举例说明)

21.图1为本发明的模块框图,结合图4目标接口时序测试流程图,本发明的实施过程

如下:

22.第一步,计并开发fpga芯片电路,如图1所示,主要包括5个模块,分别是接口解析模块、存储模块、主控电路单元模块、时钟处理模块、协议处理模块。

23.第二步,pc机通过usb接口向fpga芯片电路发送i2c接口验证时序向量存储指令,接口解析模块对命令进行解析,如图2所示。接口解析模块对命令进行解析后,通过主控电路单元模块调用存储模块,将接收到的i2c接口验证时序向量存储在内部ram中。

24.第三步,pc机通过usb接口向fpga芯片电路发送i2c接口时钟配置指令,接口解析模块对命令进行解析后,主控电路单元模块选择时钟源,并调用时钟处理模块将高频时钟源进行信号处理,如图3所示,以得到满足接口时序验证需求的时钟时序。

25.第四步,pc机通过usb接口向fpga芯片电路发送i2c接口协议选择指令,接口解析模块对命令进行解析。由主控电路单元模块调用协议处理模块,按照i2c协议要求,配置接口设置。

26.第五步,pc机通过usb接口向fpga芯片电路发送i2c接口测试指令,接口解析模块对命令进行解析。由主控电路单元模块调用存储模块,读取内部ram中已存储的接口验证时序向量。通过协议处理模块,按照i2c协议要求,输出接口验证时序。从设备接收验证时序后进行响应,通过协议处理模块采集响应结果,并通过主控电路单元模存储在内部ram中。

27.第六步,pc机通过usb接口向fpga芯片电路发送测试结果读取指令,接口解析模块对命令进行解析,主控电路单元模块调用存储模块,读取内部ram中已存储的测试结果,接口解析模块对测试结果进行解析,并从usb接口向pc机返回测试结果。

28.本发明说明书中未作详细描述的内容属本领域技术人员的公知技术。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。