技术特征:

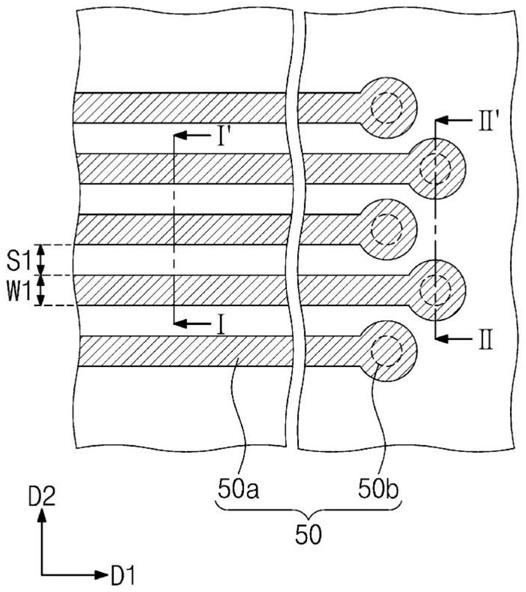

1.一种半导体封装件,包括:重分布衬底,其包括电介质层中的多个重分布线图案;以及半导体芯片,其位于所述重分布衬底上,所述半导体芯片包括电连接至所述多个重分布线图案的多个芯片焊盘,其中,所述多个重分布线图案中的每一个包括实质上平面的顶表面和非平面的底表面,并且其中,所述多个重分布线图案中的每一个包括中心部分和位于所述中心部分的相对侧上的边缘部分,并且所述多个重分布线图案中的每一个在所述中心部分处具有第一厚度作为最小厚度,并且在所述边缘部分处具有第二厚度作为最大厚度。2.根据权利要求1所述的半导体封装件,其中,所述多个重分布线图案中的每一个的所述第一厚度与所述第二厚度之间的差在0.1μm至0.2μm的范围内。3.根据权利要求1所述的半导体封装件,其中,所述多个重分布线图案中的每一个的底表面在所述中心部分处向上凸出。4.根据权利要求1所述的半导体封装件,其中,所述多个重分布线图案中的每一个的底表面在所述边缘部分处具有第一曲率半径,并且在所述中心部分处具有第二曲率半径,所述第二曲率半径不同于所述第一曲率半径。5.根据权利要求1所述的半导体封装件,其中,所述多个重分布线图案中的每一个的边缘部分包括圆的边缘。6.根据权利要求5所述的半导体封装件,其中,所述圆的边缘具有0.1μm至0.3μm的曲率半径。7.根据权利要求1所述的半导体封装件,其中,所述多个重分布线图案彼此间隔开第一间隔,所述多个重分布线图案中的每一个具有第一宽度,并且所述第一宽度和所述第一间隔各自具有1.5μm至2.5μm的范围。8.根据权利要求1所述的半导体封装件,其中,所述多个重分布线图案中的每一个包括相对于所述电介质层的顶表面以第一角度取向的侧壁,其中,所述第一角度具有85

°

至95

°

的范围。9.根据权利要求1所述的半导体封装件,其中,所述多个重分布线图案中的每一个包括:金属图案;以及阻挡金属图案,其具有覆盖所述金属图案的相对侧壁和所述金属图案的底表面的实质上均匀的厚度。10.根据权利要求1所述的半导体封装件,其中,所述多个重分布线图案中的每一个的顶表面与所述电介质层的顶表面实质上共面。11.根据权利要求1所述的半导体封装件,其中,所述多个重分布线图案中的每一个的第二厚度具有2.5μm至4.0μm的范围。12.根据权利要求1所述的半导体封装件,其中,所述电介质层包括选自聚酰亚胺、聚苯并噁唑、酚醛聚合物和苯并环丁烯聚合物中的至少一个。13.一种半导体封装件,包括:

重分布衬底,其包括电介质层中的多个重分布图案;以及半导体芯片,其位于所述重分布衬底上,所述半导体芯片包括电连接至所述多个重分布图案的多个芯片焊盘,其中,所述多个重分布图案中的每一个包括:线部,其位于所述电介质层中;以及穿通件部分,其穿透所述电介质层,并且连接至所述线部,其中,所述多个重分布图案中的每一个的线部在第一方向上平行于彼此延伸,其中,所述多个重分布图案的线部中的至少一些在垂直于所述第一方向的第二方向上具有第一宽度,并且其中,所述多个重分布图案中的每一个的线部包括中心部分和位于所述中心部分的相对侧上的边缘部分,并且所述多个重分布图案中的每一个的线部包括在所述中心部分上向上凸出的底表面。14.根据权利要求13所述的半导体封装件,其中,所述多个重分布图案中的每一个包括实质上平面的顶表面。15.根据权利要求13所述的半导体封装件,其中,所述多个重分布图案中的每一个的线部包括在该线部的底表面与该线部的相对侧壁之间的圆的边缘。16.根据权利要求13所述的半导体封装件,其中,所述多个重分布图案中的每一个的线部在所述中心部分处具有第一厚度作为最小厚度,并且在所述边缘部分处具有第二厚度作为最大厚度。17.根据权利要求13所述的半导体封装件,其中,所述多个重分布图案包括:多个第一重分布图案,所述多个第一重分布图案中的每一个具有所述第一宽度;以及多个第二重分布图案,所述多个第二重分布图案中的每一个具有大于所述第一宽度的第二宽度,其中,所述多个第一重分布图案和所述多个第二重分布图案中的每一个的线部在该线部的底表面与该线部的相对侧壁之间具有圆的边缘,其中,所述多个第一重分布图案中的每一个的圆的边缘具有第一曲率半径,并且其中,所述多个第二重分布图案中的每一个的圆的边缘具有与所述第一曲率半径不同的第二曲率半径。18.一种半导体封装件,包括:封装衬底;重分布衬底,其位于所述封装衬底上,所述重分布衬底包括光敏聚合物层和位于所述光敏聚合物层中的多个重分布图案;第一半导体芯片,其位于所述重分布衬底上;第二半导体芯片,其位于所述重分布衬底上,并且与所述第一半导体芯片间隔开,所述第二半导体芯片包括多个竖直堆叠的存储器芯片;多个第一连接端子,其位于所述重分布衬底与所述第一半导体芯片之间以及所述重分布衬底与所述第二半导体芯片之间;多个第二连接端子,其将所述封装衬底连接至所述重分布衬底;模制层,其位于所述重分布衬底上,所述模制层至少部分地覆盖所述第一半导体芯片

和所述第二半导体芯片;以及热辐射结构,其位于所述封装衬底上,所述热辐射结构覆盖或盖住所述重分布衬底、所述第一半导体芯片以及所述第二半导体芯片,其中,所述多个重分布图案中的每一个包括:线部,其在电介质层中沿着一个方向延伸;以及穿通件部分,其穿透所述电介质层,并且连接至所述线部,其中,所述多个重分布图案中的每一个的线部包括实质上平面的顶表面、非平面的底表面以及位于所述线部的底表面与相对的第一侧壁和第二侧壁之间的第一圆的边缘与第二圆的边缘,其中,所述多个重分布图案中的每一个的线部包括中心部分以及位于所述中心部分的相对侧上的第一边缘部分和第二边缘部分,并且其中,所述多个重分布图案中的每一个的线部在所述中心部分处具有第一厚度作为最小厚度,并且在所述第一边缘部分和所述第二边缘部分处具有第二厚度作为最大厚度。19.根据权利要求18所述的半导体封装件,其中,在所述多个重分布图案中的每一个的线部的中心部分上,所述底表面在朝向所述第一半导体芯片和所述第二半导体芯片的方向上凸出。20.根据权利要求18所述的半导体封装件,其中,在所述多个重分布图案中的每一个的线部的中心部分上,所述底表面相对于所述第一半导体芯片和所述第二半导体芯片凹陷。

技术总结

公开了半导体封装件及其制造方法。半导体封装件包括重分布衬底,其包括电介质层中的重分布线图案;以及半导体芯片,其位于重分布衬底上。半导体芯片包括芯片焊盘,其电连接至重分布线图案。重分布线图案中的每一个具有基本上共面的顶表面和非共面的底表面。重分布线图案中的每一个包括中心部分和位于中心部分的相对侧上的边缘部分。重分布线图案中的每一个在中心部分处具有作为最小厚度的第一厚度,并且在边缘部分处作为最大厚度的第二厚度。且在边缘部分处作为最大厚度的第二厚度。且在边缘部分处作为最大厚度的第二厚度。

技术研发人员:黄贤洙 权俊润 朴点龙 安振镐 吴东俊 李忠善 崔朱逸

受保护的技术使用者:三星电子株式会社

技术研发日:2021.07.29

技术公布日:2022/2/18

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。