用于减少差分到差分远端串扰的系统和方法

1.相关申请的交叉引用

2.本专利申请基于并要求于2020年7月29日提交的美国临时专利申请第63/058,326号的优先权,出于所有目的,其公开内容通过引用整体并入本文。

技术领域

3.本公开内容整体涉及电气系统,并且更具体地,涉及用于减少远端串扰诸如差分到差分远端串扰(ddfext)的系统和方法。

背景技术:

4.fext的减少对于高速数字通信系统可能是重要的。随着在电信行业中对更高带宽的需求不断增长,每个装置可能需要更大量的计算能力和路由能力。每个信号通道的数据速率不断增加,信号密度也是如此。因此,在相邻信道之间发生的不想要的噪声或电磁耦合显著增加。与单端数据线相比,为了高速适用性和噪声的减少,差分信号已经成为用于数据传输的优选相关技术方法。

5.对于所考虑的差分受害者对(victimpair),当这些相邻对中的至少一个是活动的时,在整个数据传输通路中都出现来自相邻攻击者对(aggressor pair)的不想要的电磁耦合(即,串扰)。当攻击者的发射器和受害者的接收器物理上彼此远离(例如,位于不同的芯片处)时,在与信号相同的方向上感应的串扰被称为远端串扰或fext。

技术实现要素:

6.本文描述的示例实现方式涉及用于平衡公共延迟和差分延迟使得串扰的累积效应互相抵消从而导致差分到差分fext的减少的系统和方法。

7.本公开内容的方面可以包括一种用于减少远端串扰(fext)的电气系统,该电气系统包括:第一电气系统;以及与第一电气系统串联级联的第二电气系统,第二电气系统被配置成移位第一电气系统的传播延迟以减少fext。在这样的示例实现方式中,第一电气系统和第二电气系统可以是连接器、线缆、印刷电路板(pcb)或芯片封装中的一个或更多个。在本文描述的任何示例实现方式中,第二电气系统可以包括可重新配置的硬件。在用于减少差分到差分fext(ddfext)的任何示例实现方式中,可重新配置的硬件可以通过包括以下操作的处理来进行配置:将表示第一电气系统的设计的第一s参数转换为仅差分s参数;生成第二仅差分s参数,该参数被配置成将仅差分s参数的、电气系统的偶模传播延迟和奇模传播延迟移位至基本相等;以及根据仅差分s参数和第二仅差分s参数来重新配置第二电气系统。根据如上所述的任何示例实现方式,第二电气系统可以被配置成移位第一电气系统的传播延迟以减少差分到差分fext(ddfext)。根据如上所述的示例实现方式,第二电气系统可以被配置成移位第一电气系统的传播延迟以减少单端fext。

8.本公开内容的方面可以包括一种制造用于减少远端串扰(fext)的电气系统的方法,该电气系统包括:第一电气系统;以及与第一电气系统串联级联的第二电气系统,第二

电气系统被配置成移位第一电气系统的传播延迟以减少fext,该方法包括:将表示第一电气系统的设计的第一s参数转换为仅差分s参数;生成第二仅差分s参数,该参数被配置成将仅差分s参数的、电气系统的偶模传播延迟和奇模传播延迟移位至基本相等;以及根据仅差分s参数和第二仅差分s参数来重新配置第二电气系统。根据如上所述的任何示例实现方式,第二电气系统可以被配置成移位第一电气系统的传播延迟以减少差分到差分fext(ddfext)。根据如上所述的示例实现方式,第二电气系统可以被配置成移位第一电气系统的传播延迟以减少单端fext。

9.本公开内容的方面可以包括一种用于减少远端串扰(fext)的电气系统,该电气系统包括:第一电气系统;以及与第一电气系统串联级联的第二电气系统,第二电气系统被配置成补偿第一电气系统的偶模传播延迟和奇模传播延迟的差以减少fext。

10.本公开内容的方面可以包括一种制造用于减少差分到差分远端串扰(ddfext)的电气系统的方法,该电气系统包括:第一电气系统;以及与第一电气系统串联级联的第二电气系统,第二电气系统被配置成向第一电气系统添加仅差分s参数的偶模传播延迟和奇模传播延迟,以减少ddfext,该方法包括:将表示第一电气系统的设计的第一s参数转换为仅差分s参数;生成第二仅差分s参数,该参数被配置成添加仅差分s参数的、电气系统的偶模传播延迟和奇模传播延迟,使得仅差分s参数的总的偶模传播延迟和总的奇模传播延迟基本相等;以及根据仅差分s参数和第二仅差分s参数来重新配置第二电气系统。

11.本公开内容的方面包括一种制造用于减少远端串扰(fext)的电气系统的方法,该电气系统包括:第一电气系统;以及与第一电气系统串联级联的第二电气系统,第二电气系统被配置成向第一电气系统添加偶模传播延迟和奇模传播延迟以减少fext,该方法包括:生成第二s参数,该参数被配置成添加电气系统的偶模传播延迟和奇模传播延迟,使得总的偶模传播延迟和总的奇模传播延迟基本相等;以及根据s参数和第二s参数来重新配置第二电气系统。

附图说明

12.图1示出了根据示例实现方式的对耦合差分对进行解耦以将偶模分析/奇模分析扩展至对到对耦合的示例。

13.图2示出了根据示例实现方式的为了减少ddfext而要减少的传播延迟的示例。

14.图3(a)至图3(c)示出了根据示例实现方式的具有1英寸微带的示例设计。

15.图4(a)至图4(c)示出了根据示例实现方式的通过1/2英寸微带的延迟移位器的示例系统。

16.图5示出了根据示例实现方式的导致ddfext减少的图4(a)的系统与图3(a)的系统的一半的示例级联。

17.图6(a)至图6(d)示出了根据示例实现方式的ddfext和ddnext的示例比较。

18.图7示出了根据示例实现方式的示例级联系统。

19.图8示出了具有适于在一些示例实现方式中使用的示例计算机装置的示例计算环境,例如用于生成设计的设计工具软件和如本文所描述的延迟移位器/反相器。

具体实施方式

20.以下详细描述提供了本技术的附图和示例实现方式的其他细节。为了清楚起见,省略了附图之间的冗余元件的附图标记和描述。在整个说明书中使用的术语是作为示例提供的,并且不旨在是限制性的。本文描述的示例实现方式可以单独使用,或与本文描述的其他示例实现方式结合使用,或与任何其他期望的实现方式结合使用。

21.图1示出了根据示例实现方式的对耦合差分对进行解耦以将偶模分析/奇模分析扩展至对到对耦合的示例。在示例实现方式中,假设差分对是对称的以简化分析。如图1中所示,两个对称差分对(对1、对2)可以表示为差分端口1、差分端口2、差分端口3和差分端口4。为了分析系统,对称差分对被分成两个耦合对,然后可以通过使用偶模分析和奇模分析对两个耦合对进行分析。可以将偶模分析和奇模分析的结果进行结合以得到ddfext以及差分到差分近端串扰(ddnext)。

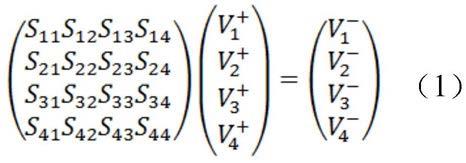

22.为了促进对于减少ddfext的分析,分析确定s参数与入射电压的乘积等于输出电压,如下:

[0023][0024]

在以上式(1)中,输出电压用负上标符号表示,而入射电压用正上标符号表示。因此,在图1的示例中,如果存在四个差分端口,则存在进入每个端口的入射电压和从每个端口出来的输出电压。分析被扩展至如图所示的差分信号,因为在此具有相同值的s参数(例如,s11)表示相同差分端口内的差分信号,而具有不同端口的s参数表示对应差分端口之间的传输或耦合(例如,s12表示从差分端口2至差分端口1的差分耦合)。需要注意的是,对于单端应用,具有相同值的s参数(例如,s11)表示同一端口内的单端信号,而具有不同端口的s参数表示对应单端端口之间的传输或耦合(例如,s12表示从单端端口2至单端端口1的耦合)。

[0025]

对于偶模分析,将进入两个对应端口的入射电压设置为相同,并且让v

2

=v

1

;v

4

=v

3

。因为入射电压相同,偶模分析因此可以将原始4x4矩阵简化为2x2矩阵,并且可以确定如下:

[0026][0027]

对于奇模分析,将进入两个对应端口的入射电压设置为180度相位反转,并且让v

2

=-v

1

;v

4

=-v

3

。奇模分析因此可以将原始4x4矩阵简化为2x2矩阵,如下所示:

[0028][0029]

在示例实现方式中,为了确定ddnext,分析可以朝向从发射侧进入接收侧的传播简化。因此,假设不存在从接收侧进入的入射电压,就让接收端处的入射电压等于零,使得ddnext是从发射端出来的攻击者对的偶模电压和奇模电压的差(v

2-),如下所示:

[0030]

[0031]

类似地,ddfext因此可以被表示为从接收端出来的攻击者对的偶模分析和奇模分析的差(v

4-),如下所示:

[0032][0033]

图2示出了根据示例实现方式的为了减少ddfext而要被调整的传播延迟的示例。如图2中所示,当偶模传播延迟与奇模传播延迟之间的差不同时,由于偶模与奇模之间的差将不为零,耦合将在接收端处引起ddfext。然而,如果耦合相同并且ddfext为零,则偶模传播延迟与奇模传播延迟之间的差也将为零。因此,本文所描述的示例实现方式涉及消除偶模传播延迟与奇模传播延迟之间的差以减少ddfext。

[0034]

参照图1,偶模传播延迟和奇模传播延迟可以被表示为:

[0035][0036]

其中l是自感,c是自电容,并且lm是互感,cm是互电容。

[0037]

因此:

[0038]

如果

[0039]

当时,则t

偶

<t

奇

,这将导致ddfext大于零,因为

[0040]

因此,在如本文所描述的示例实现方式中,一种分析和减少ddfext的技术是将多端口系统的模拟的或测量的touchstone文件(例如,.snp)转换为仅差分的touchstone文件(.snp)(n=n/2),并且然后修改设计以使仅差分s参数的偶模传播延迟和奇模传播延迟彼此接近,这可以通过检查仅差分s参数的公共相位和差分相位或群延迟或时域传输(tdt)延迟来进行。为此,示例实现方式将考虑以下术语:

[0041]

sdd-仅差分s参数

[0042]

sdd的sdd-仅差分s参数的差模

[0043]

sdd的scc-仅差分s参数的共模

[0044]

图3(a)至图3(c)示出了根据示例实现方式的具有1英寸微带的示例设计。具体地,图3(a)示出了1英寸微带的示例横截面。在该设计中存在两个差分对,因此包括四个信号线。四个信号线通常是沉积在衬底的顶部上的金属线,并且包括用于八个端口的四线输入、四线输出系统。

[0045]

图3(b)示出了图3(a)中的单端s参数的示例。通过以上描述的示例,取8个端口s参数并将其转换为仅差分模式,可以绘制奇模的延迟和偶模的延迟并且可以确定差值,如指示差分延迟大于共模延迟的图3(c)的sdd12中所示。图3(c)示出了仅差分s参数的sdd12和scc12的相位延迟的示例。

[0046]

图4(a)至图4(c)示出了根据示例实现方式的通过1/2英寸微带的延迟移位器的示例系统。假设图3(a)的系统被分成包括1/2英寸原始微带的两个部分,并且然后另一1/2英寸被用作如图4(a)中所示的延迟移位器或延迟反相器。这样的结构可以包括例如在条带之间使用具有较大介电常数(dk2)的材料等。

[0047]

在如图4(a)中所示的示例实现方式中,其中在信号线之间使用较大介电材料,在

图4(b)中示出单端s参数,并且如图4(c)中所示延迟反转;如图4(c)中所示,与图3(c)中的延迟相比,sdd的scc12现在具有比sdd的sdd12更大的延迟,即,sdd的共模延迟现在具有比sdd的差分延迟更大的延迟。因此,当该系统与图3(a)的系统的一半级联时,图4(a)的结构将使延迟从图3(a)的结构的一半偏离,由于延迟的消除而导致ddfext消除。

[0048]

图5示出了根据示例实现方式的导致ddfext减少的图4(a)的系统与图3(a)的系统的一半的示例级联。通过将图4(a)的系统的1/2英寸微带设计与图3(a)的设计级联,可以使sdd的scc传播延迟和sdd的sdd传播延迟相似,并且因此可以减少ddfext。

[0049]

图6(a)至图6(d)示出了根据示例实现方式的ddfext和ddnext的示例比较。如图6(a)至图6(b)中所示,可以通过将图3(a)系统的一半与图4(a)的系统级联来减少ddfext,因为从每个系统感应的ddfext将具有相反的极性。图6(c)至图6(d)示出了根据示例实现方式的ddnext,ddnext可能增加,但是对于减少ddfext是很好的折衷。

[0050]

因此,通过如本文所描述的实现方式,示例实现方式可以包括仅差分s参数的公共延迟和差分延迟的平衡以减少ddfext。

[0051]

另外,示例实现方式可以包括改变设计(例如,通过在适当的位置处应用气隙/袋或具有较高介电常数的材料、调整中心接地位置等),来平衡仅差分s参数的公共延迟和差分延迟以减少ddfext。

[0052]

示例实现方式可以包括利用离散或嵌入块来用作延迟移位器或延迟反相器,以根据期望实现方式针对任何部件(例如,连接器、封装、印刷电路板等)减少ddfext。

[0053]

虽然本文描述的示例实现方式是针对ddfext提供的,但是本文描述的示例实现方式还可以用于通过类似的级联系统减少单端fext以实现适当的传播延迟。

[0054]

图7示出了根据示例实现方式的示例级联系统。在本文描述的示例实现方式中,任何电气系统700可以与延迟反相器/移位器701级联,该延迟反相器/移位器701被配置成移位差分传播延迟来平衡公共延迟和差分延迟,以减少差分fext。根据期望的实现方式,电气系统可以是包括微带迹线的任何电气系统,例如但不限于芯片封装、连接器、印刷电路板、线缆等。类似地,延迟反相器/移位器701可以通过任何电气系统来实现,电气系统例如但不限于芯片封装、连接器、印刷电路板、线缆等。在示例实现方式中,延迟反相器/移位器701可以采用根据期望的实现方式的嵌入式或单个部件形式的任何固定硬件的形式。

[0055]

此外,电气系统700和延迟反相器/移位器701可以是整个系统的子系统或子部分的形式。例如,电气系统700可以包括特定线缆或连接器的多个部分,并且延迟反相器/移位器701可以包括相同线缆或连接器内的多个级联部分。电气系统700和延迟反相器/移位器701的设计可以根据期望的实现方式来设置。

[0056]

在示例实现方式中,延迟反相器/移位器701可以是被配置成根据期望的差分延迟特性而改变的可重新配置系统的形式。例如,可重新配置系统可以是具有可重新配置互连的现场可编程门阵列(fpga)的形式,该可重新配置互连可以基于具有如图8中所描述的计算装置的配置根据期望的差分延迟特性被重新路由。在另一示例实现方式中,可重新配置系统可以是微带迹线的形式,该微带迹线具有具备根据期望的实现方式的可配置介电常数(例如,由电压、由超声等驱动)的材料。这样的材料可以包括但不限于p/n掺杂硅。其他可重新配置硬件可以用于延迟反相器/移位器701以促进期望的实现方式,并且本公开内容不特别限定于此。

[0057]

在另一示例实现方式中,延迟反相器/移位器701可以是被设计成解决电气系统700的fext的静态形成的部件。延迟反相器/移位器701可以基于第一电气系统的设计通过本领域已知的任何期望的实现方式通过包括以下操作的处理来制造:将表示第一电气系统的设计的第一s参数转换为仅差分s参数;生成第二仅差分s参数,该第二仅差分s参数被配置成将电气系统的仅差分s参数的偶模传播延迟和奇模传播延迟移位至基本相等;以及根据仅差分s参数和第二仅差分s参数来重新配置第二电气系统。虽然本文描述的示例针对ddfext,但是示例实现方式也可以扩展至单端fext。本领域的普通技术人员可以基于本文描述的示例,根据本领域中已知的任何期望的实现方式来配置或调整延迟反相器/移位器701,以解决单端fext而不是ddfext,或者将单端fext与ddfext结合解决。

[0058]

图8示出了具有适于在一些示例实现方式中使用的示例计算机装置的示例计算环境,例如用于生成设计的设计工具和如本文所描述的延迟移位器/反相器。计算环境800中的计算机装置805可以包括一个或更多个处理单元、核或处理器810、存储器815(例如,ram、rom等)、内部存储装置820(例如,磁存储装置、光存储装置、固态存储装置和/或有机存储装置)和/或io接口825,以上各项中的任何一个可以耦接在用于传送信息的通信机构或总线830上或嵌入在计算机装置805中。根据期望的实现方式,io接口825还被配置成从摄像机接收图像或向投影仪或显示器提供图像。

[0059]

计算机装置805可以通信地耦接至输入/用户接口835和输出装置/接口840。输入/用户接口835和输出装置/接口840中的一个或两个可以是有线或无线接口,并且可以是可拆卸的。输入/用户接口835可以包括可以用于提供输入的物理的或虚拟的任何装置、部件、传感器或接口(例如,按钮、触摸屏界面、键盘、指向/光标控制、麦克风、摄像机、盲文(braille)、运动传感器、光学阅读器等)。输出装置/接口840可以包括显示器、电视、监视器、打印机、扬声器、盲文等。在一些示例实现方式中,输入/用户接口835和输出装置/接口840可以嵌入或物理地耦接至计算机装置805。在其他示例实现方式中,其他计算机装置可以用作用于计算机装置805的输入/用户接口835和输出装置/接口840或提供用于计算机装置805的输入/用户接口835和输出装置/接口840的功能。

[0060]

计算机装置805的示例可以包括但不限于高度移动装置(例如,智能电话、车辆和其他机器中的装置、由人和动物携带的装置等)、移动装置(例如,平板电脑、笔记本电脑、膝上型计算机、个人计算机、便携式电视、收音机等)和不是针对移动性设计的装置(例如,台式计算机、其他计算机、信息亭、其中嵌入和/或耦接有一个或更多个处理器的电视、无线电装置等)。

[0061]

计算机装置805可以通信地耦接(例如,经由io接口825)至外部存储装置845和网络850,以用于与任何数量的联网部件、装置和系统(包括相同或不同配置的一个或更多个计算机装置)通信。计算机装置805或任何连接的计算机装置可以用作服务器、客户端、瘦服务器、通用机器、专用机器或其他标签,提供服务器、客户端、瘦服务器、通用机器、专用机器或其他标签的服务或被称为服务器、客户端、瘦服务器、通用机器、专用机器或其他标签。

[0062]

io接口825可以包括但不限于使用任何通信或io协议或标准(例如,以太网、802.11x、通用系统总线、wimax、调制解调器、蜂窝网络协议等)的有线和/或无线接口,以用于向和/或从计算环境800中的至少所有连接的部件、装置和网络传送信息。网络850可以是任何网络或网络的组合(例如,因特网、局域网、广域网、电话网络、蜂窝网络、卫星网络等)。

[0063]

计算机装置805可以使用包括暂态介质和非暂态介质的计算机可用或计算机可读介质和/或使用包括暂态介质和非暂态介质的计算机可用或计算机可读介质进行通信。暂态介质包括传输介质(例如,金属线缆、光纤)、信号、载波等。非暂态介质包括磁介质(例如,磁盘和磁带)、光学介质(例如,cd rom、数字视频光盘、蓝光光盘)、固态介质(例如,ram、rom、闪存、固态存储装置)和其他非易失性存储装置或存储器。

[0064]

计算机装置805可以用于在一些示例计算环境中实现技术、方法、应用、处理或计算机可执行指令。计算机可执行指令可以从暂态介质中检索,并且存储在非暂态介质上并从非暂态介质中检索。可执行指令可以源自任何编程、脚本和机器语言(例如,c、c 、c#、java、visual basic、python、perl、javascript等)中的一种或更多种。

[0065]

处理器810可以在本地环境或虚拟环境中在任何操作系统(os)(未示出)下执行。可以部署包括逻辑单元860、应用编程接口(api)单元865、输入单元870、输出单元875和单元间通信机构895的一个或更多个应用,以用于不同单元彼此通信、与os通信以及与其他应用(未显示)通信。所描述的单元和元件可以在设计、功能、配置或实现方式方面变化,并且不限于所提供的描述。处理器810可以是硬件处理器诸如中央处理单元(cpu)的形式或硬件和软件单元的组合。

[0066]

在一些示例实现方式中,当信息或执行指令被api单元865接收时,其可以被传送至一个或更多个其他单元(例如,逻辑单元860、输入单元870、输出单元875)。在一些情况下,在以上所描述的一些示例实现方式中,逻辑单元860可以被配置成控制单元之间的信息流并且指导由api单元865、输入单元870、输出单元875提供的服务。例如,一个或更多个处理或实现方式的流可以由逻辑单元860单独地或结合api单元865来控制。输入单元870可以被配置成获得用于在示例实现方式中所描述的计算的输入,并且输出单元875可以被配置成基于示例实现方式中所描述的计算来提供输出。

[0067]

处理器810可以被配置成将表示第一电气系统的设计的第一s参数转换为仅差分s参数;生成第二仅差分s参数,该第二仅差分s参数被配置成将电气系统的仅差分s参数的偶模传播延迟和奇模传播延迟移位成基本相等;以及如图1至图7中所示的根据仅差分s参数和第二仅差分s参数重新配置第二电气系统。第二电气系统可以经由寄存器传输级(rtl)格式、硬件描述语言(hdl)格式或用于并入如图7中所示的可重新配置的延迟移位器/反相器系统701中的其他格式来输出。

[0068]

根据计算机内的操作的算法和符号表示来呈现详细描述的一些部分。这些算法描述和符号表示是由数据处理领域的技术人员用来向本领域的其他技术人员传达他们的创新的本质的手段。算法是导致期望的最终状态或结果的一系列定义的步骤。在示例实现方式中,所执行的步骤需要具体数量的物理操纵以用于实现具体结果。

[0069]

除非另外特别说明,否则根据讨论明显的,应当理解,在整个说明书中,使用诸如“处理”、“计算”、“运算”、“确定”、“显示”等术语的讨论可以包括计算机系统或其他信息处理装置的动作和处理,计算机系统或其他信息处理装置将计算机系统的寄存器和存储器内的表示为物理(电子)量的数据操纵并转换为计算机系统的存储器或寄存器或其他信息存储、传输或显示装置内的类似地表示为物理量的其他数据。

[0070]

示例实现方式还可以涉及用于执行本文的操作的设备。该设备可以出于所需目的而特别构造,或者该设备可以包括由一个或更多个计算机程序选择性地激活或重新配置的

一个或更多个通用计算机。这样的计算机程序可以存储在计算机可读介质中,例如计算机可读存储介质或计算机可读信号介质。计算机可读存储介质可以包括有形介质,例如但不限于光盘、磁盘、只读存储器、随机存取存储器、固态装置和驱动器,或者适于存储电子信息的任何其他类型的有形或非暂态介质。计算机可读信号介质可以包括诸如载波的介质。本文呈现的算法和显示并非固有地与任何特定的计算机或其他设备相关。计算机程序可以包括纯软件实现方式,该纯软件实现方式包括执行期望的实现方式的操作的指令。

[0071]

各种通用系统可以与根据本文的示例的程序和模块一起使用,或者可以证明构造更专用的设备来执行期望的方法步骤是方便的。另外,示例实现方式未参照任何特定的编程语言进行描述。应当理解,可以使用各种编程语言来实现如本文所描述的示例实现方式的教导。编程语言的指令可以由一个或更多个处理装置(例如,中央处理单元(cpu)、处理器或控制器)来执行。

[0072]

如本领域中已知的,以上所描述的操作可以通过硬件、软件或软件和硬件的某种组合来执行。示例实现方式的各个方面可以使用电路和逻辑装置(硬件)来实现,而其他方面可以使用存储在机器可读介质(软件)上的指令来实现,所述指令如果由处理器执行,则将使处理器执行实现本技术的实现方式的方法。此外,本技术的一些示例实现方式可以仅在硬件中执行,而其他示例实现方式可以仅在软件中执行。此外,所描述的各种功能可以在单个单元中执行,或者可以以多种方式分布在多个部件上。当通过软件执行时,方法可以由诸如通用计算机的处理器基于存储在计算机可读介质上的指令来执行。如果需要,指令可以以压缩和/或加密格式存储在介质上。

[0073]

在第一方面,可以存在一种用于减少差分到差分远端串扰(ddfext)的电气系统,该电气系统包括:第一电气系统;以及与第一电气系统串联级联的第二电气系统,第二电气系统被配置成移位第一电气系统的传播延迟以减少ddfext。

[0074]

在第二方面,可以存在根据第一方面中所公开的电气系统,其中,第一电气系统和第二电气系统是连接器、线缆、印刷电路板(pcb)或芯片封装中的一个或更多个。

[0075]

在第三方面,可以存在根据第一方面和第二方面中任一项所公开的电气系统,其中,第二电气系统包括可重新配置的硬件。

[0076]

在第四方面,可以存在根据第一方面、第二方面和第三方面中任一项所公开的电气系统,其中,可重新配置的硬件通过包括以下操作的处理来进行配置:将表示第一电气系统的设计的第一s参数转换为仅差分s参数;生成第二仅差分s参数,该参数被配置成将电气系统的仅差分s参数的偶模传播延迟和奇模传播延迟移位至基本相等;以及根据仅差分s参数和第二仅差分s参数来重新配置第二电气系统。

[0077]

在第五方面,可以存在根据第一方面至第四方面中任一项所公开的电气系统,其中,第二电气系统被配置成移位第一电气系统的传播延迟以减少差分到差分fext。

[0078]

在第六方面,可以存在根据第一方面至第四方面中任一项所公开的电气系统,其中,第二电气系统被配置成移位第一电气系统的传播延迟以减少单端fext。

[0079]

在第七方面,可以存在一种制造如第一方面至第六方面中任一项所公开的电气系统的方法。

[0080]

在第八方面,存在一种用于减少远端串扰(fext)的电气系统,该电气系统包括:第一电气系统;以及与第一电气系统串联级联的第二电气系统,第二电气系统被配置成补偿

第一电气系统的偶模传播延迟和奇模传播延迟的差以减少fext。

[0081]

在第九方面,存在根据第八方面所述的电气系统,其中,第一电气系统和第二电气系统是连接器、线缆、印刷电路板(pcb)或芯片封装中的一个或更多个。

[0082]

在第十方面,存在根据第八方面至第九方面中任一项所述的电气系统,其中,第二电气系统包括可重新配置的硬件。

[0083]

在第十一方面,存在根据第十方面所述的电气系统,其中,可重新配置的硬件通过包括以下操作的处理来进行配置:将表示第一电气系统的设计的第一s参数转换为仅差分s参数;生成第二仅差分s参数,该参数被配置成添加至电气系统的仅差分s参数的偶模传播延迟和奇模传播延迟,使得总的偶模传播延迟和总的奇模传播延迟基本相等;以及根据仅差分s参数和第二仅差分s参数来重新配置第二电气系统。

[0084]

在第十二方面,存在根据第八方面至第十方面中任一项所述的电气系统,其中,第二电气系统被配置成向第一电气系统添加仅差分s参数的偶模传播延迟和奇模传播延迟,以减少差分到差分fext。

[0085]

在第十三方面,存在根据第八方面至第十二方面中任一项所述的电气系统,其中,第二电气系统被配置成向第一电气系统添加偶模传播延迟和奇模传播延迟以减少单端fext。

[0086]

在第十三方面,存在一种制造用于减少差分到差分远端串扰(ddfext)的电气系统的方法,该电气系统包括:第一电气系统;以及与第一电气系统串联级联的第二电气系统,第二电气系统被配置成向第一电气系统添加仅差分s参数的偶模传播延迟和奇模传播延迟以减少ddfext,该方法包括:将表示第一电气系统的设计的第一s参数转换为仅差分s参数;生成第二仅差分s参数,该参数被配置成添加电气系统的仅差分s参数的偶模传播延迟和奇模传播延迟,使得仅差分s参数的总的偶模传播延迟和总的奇模传播延迟基本相等;以及根据仅差分s参数和第二仅差分s参数来重新配置第二电气系统。

[0087]

在第十四方面,存在根据第十三方面所述的方法,其中,第二电气系统被配置成移位第一电气系统的传播延迟以减少差分到差分fext。

[0088]

在第十五方面,存在一种制造用于减少远端串扰(fext)的电气系统的方法,该电气系统包括:第一电气系统;以及与第一电气系统串联级联的第二电气系统,第二电气系统被配置成向第一电气系统添加偶模传播延迟和奇模传播延迟以减少fext,该方法包括:生成第二s参数,该参数被配置成添加电气系统的偶模传播延迟和奇模传播延迟,使得总的偶模传播延迟和总的奇模传播延迟基本相等;以及根据s参数和第二s参数来重新配置第二电气系统。

[0089]

在第十六方面,存在根据第十五方面所述的方法,其中,第二电气系统被配置成移位第一电气系统的传播延迟以减少单端fext。

[0090]

此外,根据考虑本技术的说明书和教导的实践,本技术的其他实现方式对于本领域技术人员将是明显的。所描述的示例实现方式的各个方面和/或部件可以单独使用或以任何组合方式使用。说明书和示例实现方式旨在仅被视为示例,其中本技术的真实范围和精神由所附权利要求指示。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。