技术特征:

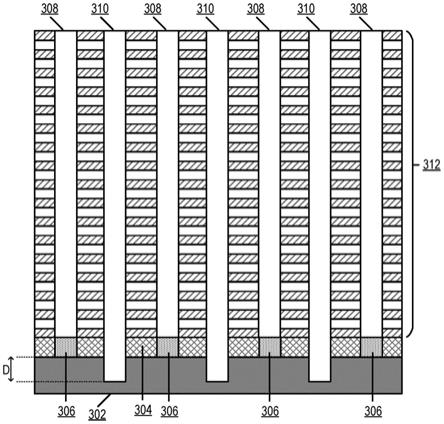

1.一种半导体装置,其包括:源极板;多个插塞,其在所述源极板上制造或至少部分地形成于所述源极板中;堆叠,其形成于所述衬底及多个插塞上,所述堆叠包括交替的绝缘层及导电层;由一种工艺形成的第一组支柱,其延伸穿过所述堆叠,所述工艺包含蚀刻所述交替的绝缘层及导电层,及将支柱材料沉积在其中,其中所述第一组支柱中的每个支柱在所述多个插塞中的相应插塞顶上终止,并且形成延伸穿过所述绝缘层及导电层的沟道材料存储器单元串;及由一种工艺形成的第二组支柱,其延伸穿过所述堆叠,所述工艺包含蚀刻所述交替的绝缘层及导电层,及将支柱材料沉积在其中,其中所述第二组支柱中的每个支柱在所述源极板中终止。2.根据权利要求1所述的装置,其中所述源极板包括硅衬底。3.根据权利要求2所述的装置,其中所述源极板进一步包括形成源极栅极的一或多个层。4.根据权利要求3所述的装置,其中所述源极栅极导电地接触所述第一组支柱中的每一个。5.根据权利要求4所述的装置,其中所述源极栅极不导电地接触所述第二组支柱中的任一个。6.根据权利要求1所述的装置,其中所述多个插塞包括多个钨插塞。7.根据权利要求1所述的装置,其中所述绝缘材料包括氮化硅并且所述导电材料包括氧化硅。8.一种制造半导体装置的方法,其包括:将氧化硅层沉积在源极板上;将光致抗蚀剂层沉积在所述氧化硅层上;经由放置于所述光致抗蚀剂层的顶部上的掩模图案在所述氧化硅层中形成多个孔,所述多个孔形成于所述源极板上或至少部分地形成于所述源极板中;将导电材料层沉积在所述多个孔中;将堆叠沉积在所述氧化硅层及多个孔上,所述堆叠包括交替的绝缘层及导电层;通过蚀刻所述交替的绝缘层及导电层及将支柱材料沉积在其中而在所述插塞上形成第一组支柱;及通过蚀刻所述交替的绝缘层及导电层及将支柱材料沉积在其中而在所述源极板中形成第二组支柱。9.根据权利要求8所述的方法,其中所述源极板通过以下操作制造:将硅化钨wsix层沉积在硅衬底上;将多晶硅层沉积在所述wsix层上;将光致抗蚀剂沉积在所述多晶硅层上;经由干式或湿式蚀刻在所述源极板中形成多个源极线。10.根据权利要求8所述的方法,其中经由原硅酸四乙酯teos沉积来沉积所述氧化硅层。

11.根据权利要求8所述的方法,所述光致抗蚀剂层包括光聚合、光分解或光交联光致抗蚀剂层。12.根据权利要求8所述的方法,其中所述多个孔形成于延伸穿过所述绝缘层及导电层的存储器单元的沟道材料串下方。13.根据权利要求8所述的方法,所述导电材料包括钨。14.根据权利要求13所述的方法,其进一步包括在沉积所述钨层之后应用钨插塞化学机械抛光wcmp。15.根据权利要求8所述的方法,其中形成所述第一及第二组支柱包括将硬掩模沉积在所述堆叠上,所述硬掩模包括限定所述第一及第二组支柱的支柱图案。16.根据权利要求15所述的方法,其中蚀刻所述第一及第二组支柱包括执行穿过所述堆叠的高纵横比蚀刻。17.根据权利要求1所述的方法,其进一步包括移除经由由内而外钨沉积工艺将钨沉积在所述导电层钨上的所述堆叠的所述绝缘层。18.根据权利要求1所述的方法,其进一步包括将多晶硅涂层沉积在所述第一及第二组支柱中。19.根据权利要求17所述的方法,其进一步包括将二氧化硅沉积在所述多晶硅涂层上。20.根据权利要求1所述的方法,其中所述绝缘层包括氮化硅并且所述导电层包括氧化硅。

技术总结

本申请涉及NAND闪存块架构增强以防止块提升。公开一种三维存储器装置。在一个实施例中,公开一种装置,所述装置包括:源极板;插塞,其在所述源极板上制造或部分地形成于所述源极板中;堆叠,其形成于衬底及插塞上,所述堆叠包括交替的绝缘层及导电层,及延伸穿过所述绝缘层及导电层的存储器单元的沟道材料串;由一种工艺形成的第一组支柱,其延伸穿过所述堆叠,所述工艺包含蚀刻所述交替的绝缘层及导电层,及将支柱材料沉积在其中,其中所述第一组支柱中的每个支柱在多个插塞中的相应插塞顶上终止;及由一种工艺形成的第二组支柱,其延伸穿过所述堆叠,所述工艺包含蚀刻所述交替的绝缘层及导电层,及将支柱材料沉积在其中,其中所述第二组支柱中的每个支柱在所述源极板中终止。中终止。中终止。

技术研发人员:M

受保护的技术使用者:美光科技公司

技术研发日:2021.07.29

技术公布日:2022/2/18

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。