经由os接口表的单numa域内的多虚拟numa域

技术领域:

:1.实施例概括而言涉及非统一存储器访问(non-uniformmemoryaccess,numa)体系结构。更具体而言,实施例涉及经由操作系统(os)接口表的单个numa域内的多个虚拟numa域的建立。

背景技术:

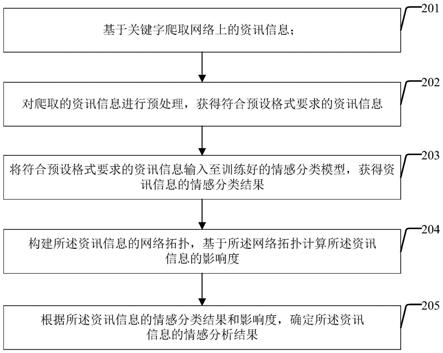

::2.在现代cpu(中央处理单元)体系结构中,核心计数大幅增加,达到了这样的水平,即os和/或应用创建虚拟numa节点,以通过在每个numa域划分竞争的软件对象,来实现易于管理和改善的性能。为了向后兼容,可能也需要在os级别的这种虚拟numa创建。windows使用一个叫做group的概念,将两个或更多个numa节点虚拟化,每个节点最多有六十四个逻辑线程,以支持具有多于六十四个逻辑线程的单个多处理器numa节点。这种方案可能会导致group之间可用存储器的不平衡,以及group之间逻辑线程数目的不平衡,这对于涉及每个numa域的高存储器带宽以及高核心计数的工作负载是不利的。技术实现要素:3.根据本公开的一方面,提供了一种计算系统,包括:插座;与所述插座耦合的处理器;以及与所述处理器耦合的存储器,所述存储器包括一组可执行程序指令,所述指令当被所述处理器执行时,使得所述处理器:识别非统一存储器访问(numa)节点,在所述numa节点内定义第一虚拟邻近域,并且在所述numa节点内定义第二虚拟邻近域,其中所述第一虚拟邻近域和所述第二虚拟邻近域是经由一个或多个操作系统(os)接口表来定义的。4.根据本公开的一方面,提供了一种半导体装置,包括:一个或多个衬底;以及与所述一个或多个衬底耦合的逻辑,其中所述逻辑至少部分实现在可配置逻辑或者固定功能硬件逻辑的一个或多个中,与所述一个或多个衬底耦合的所述逻辑用于:识别非统一存储器访问(numa)节点;在所述numa节点内定义第一虚拟邻近域;并且在所述numa节点内定义第二虚拟邻近域,其中所述第一虚拟邻近域和所述第二虚拟邻近域是经由一个或多个操作系统(os)接口表来定义的。5.根据本公开的一方面,提供了至少一个计算机可读存储介质,其包括一组可执行程序指令,所述指令当被计算系统执行时,使得所述计算系统:识别非统一存储器访问(numa)节点;在所述numa节点内定义第一虚拟邻近域;并且在所述numa节点内定义第二虚拟邻近域,其中所述第一虚拟邻近域和所述第二虚拟邻近域是经由一个或多个操作系统(os)接口表来定义的。6.根据本公开的一方面,提供了一种方法,包括:识别非统一存储器访问(numa)节点;在所述numa节点内定义第一虚拟邻近域;并且在所述numa节点内定义第二虚拟邻近域,其中所述第一虚拟邻近域和所述第二虚拟邻近域是经由一个或多个操作系统(os)接口表来定义的。附图说明7.通过阅读以下说明书和所附权利要求,并且通过参考以下附图,实施例的各种优点将对本领域技术人员变得清楚,附图中:8.图1是传统的os和bios(基本输入/输出系统)报告和根据一实施例的os和bios报告的示例的比较图示;9.图2a是没有亚numa集群(sub-numaclustering,snc)的传统体系结构和根据一实施例的没有snc的体系结构的示例的比较框图;10.图2b是根据一实施例的具有两个亚numa集群的体系结构和具有两个虚拟邻近域的体系结构的示例的比较框图;11.图2c是根据一实施例的具有四个亚numa集群的体系结构和具有四个虚拟邻近域的体系结构的示例的比较框图;12.图3是根据一实施例的操作性能增强计算系统的方法的示例的流程图;13.图4是根据一实施例的性能增强计算系统的示例的框图;14.图5是根据一实施例的半导体装置的示例的图示;15.图6是根据一实施例的处理器的示例的框图;并且16.图7是根据一实施例的基于多处理器的计算系统的示例的框图。具体实施方式17.现在转到图1,对于启用了超线程并且禁用了snc的36核单插座(socket)系统,示出了传统的bios和os报告10。在图示的示例中,biosacpi(高级配置和电源接口)将正确描述单个存储器邻近域中的七十二个线程。然而,传统的操作系统,比如windows,当前通过创建两个处理器群组和两个存储器节点来处理这种情形。线程0-63在群组0中,具有所有可用的存储器,而线程64-71在群组1中,没有存储器。其结果是不正确的存储器分配和每个numa节点的逻辑核心数目的不平衡。该问题对于较大的核心计数而言尤其重要。18.正如将更详细论述的那样,acpibios中的虚拟numa模式可为一个物理多处理器在诸如系统资源亲和表(systemresourceaffinitytable,srat)之类的os接口表中创建多个虚拟邻近域,而不改变存储器控制器/通道交织或者llc(最后一级缓存)分组。os解释os接口表以创建多个处理器群组/多个numa。如增强的os和bios报告12中所示,这种虚拟numa概念解决了存储器分配不当和每个numa节点的逻辑核心数目不平衡的问题。更特别的是,实施例可克服每群组六十四个逻辑线程的os限制,克服每群组逻辑线程数目的不平衡,并且提供比硬分区高得多的带宽/numa。19.现在转到图2a,示出了传统体系结构20,其中snc被禁用。一般而言,每个cpu多处理器的核心和存储器被划分为单独的集群,os使用这些集群来创建具有少于六十四个逻辑线程的group对象。在图示的示例中,体系结构20包括两个“假”的cpu和存储器节点,并且os具有一个大小为零的存储器节点。20.相比之下,系统固件实施例描述了经由acpi表在单个numa节点内的多个“虚拟numa”存储器域。例如,系统固件可生成acpi表,以将一numa节点中的逻辑处理器的子集与属于该物理numa节点的存储器的相应子集联系起来。在操作系统对每个numa存储器范围所允许的逻辑核心的数目有限制的情况下,这样的方案能够适当地平衡和利用单个numa存储器节点内的所有逻辑处理器。从而,增强型体系结构22不包括假的cpu和存储器节点,或者具有大小为零的一个存储器节点的os。图示的体系结构20、22的通道带宽都是8。21.图2b表明,具有两个亚numa集群的传统体系结构30的通道带宽为4,而具有两个虚拟邻近域的增强型体系结构32的通道带宽为8。从而,增强型体系结构32维持了初始(例如,snc启用前)的交织配置和缓存分组。22.图2c表明,具有四个亚numa集群的传统体系结构40的通道带宽为2,而具有四个虚拟邻近域的增强型体系结构42的通道带宽为8。从而,存储器带宽分布在物理numa节点内的所有交织的存储器通道上,并且增强型体系结构42维持了初始(例如,snc启用前)的交织配置和缓存分组。23.图3示出了操作性能增强的计算系统的方法50。方法50可实现在作为存储在诸如随机访问存储器(randomaccessmemory,ram)、只读存储器(readonlymemory,rom)、可编程rom(programmablerom,prom)、固件、闪存等等之类的机器或计算机可读存储介质中的逻辑指令集合的一个或多个模块中,实现在诸如可编程逻辑阵列(programmablelogicarray,pla)、现场可编程门阵列(fieldprogrammablegatearray,fpga)、复杂可编程逻辑器件(complexprogrammablelogicdevice,cpld)之类的可配置逻辑中,利用诸如专用集成电路(applicationspecificintegratedcircuit,asic)、互补金属氧化物半导体(complementarymetaloxidesemiconductor,cmos)或晶体管-晶体管逻辑(transistor-transistorlogic,ttl)技术之类的电路技术实现在固定功能逻辑硬件中,或者这些的组合。24.例如,可以以一种或多种编程语言的任何组合来编写用于执行方法50中所示的操作的计算机程序代码,所述编程语言包括面向对象的编程语言,比如java、smalltalk、c 之类的,还包括传统的过程式编程语言,比如“c”编程语言或类似的编程语言。此外,逻辑指令可包括汇编指令、指令集体系结构(instructionsetarchitecture,isa)指令、机器指令、机器相关指令、微代码、状态设置数据、用于集成电路的配置数据、个性化电子电路和/或硬件原生的其他结构组件(例如,主机处理器、中央处理单元/cpu、微控制器等等)的状态信息。25.图示的bios处理块52识别numa节点,其中在bios块54处定义第一虚拟邻近域。在一实施例中,numa节点专门用于单个物理多处理器。bios块56在numa节点内定义第二虚拟邻近域。在图示的示例中,第一虚拟邻近域和第二虚拟邻近域是经由一个或多个os接口表定义的,例如静态资源亲和表(staticresourceaffinitytable,srat)、系统定位信息表(systemlocalityinformationtable,slit),等等,或者其任何组合。在一个示例中,物理多处理器具有初始交织配置(例如,八个通道带宽),并且定义第一虚拟邻近域和第二虚拟邻近域包括维持初始交织配置。此外,物理多处理器可具有初始缓存分组(例如,llc分组)。在这种情况下,定义第一虚拟邻近域和第二虚拟邻近域可包括维持初始缓存分组。26.虽然在图示的示例中定义了两个虚拟邻近域以方便论述,但虚拟邻近域的数目不限于两个。从而,方法50可经由一个或多个os接口表在numa节点内定义多于两个虚拟邻近域。此外,在cpu封装被设计为每个插座有多于一个物理numa节点的情况下,这些物理numa节点中的每一个可被表示为两个或更多个虚拟numa节点。因此,方法50还可识别第二numa节点,其中第二numa节点专用于物理插座,并且在第二numa节点内定义两个或更多个虚拟邻近域(例如,经由一个或多个os接口表)。27.在一实施例中,os块58创建处理器的第一群组,其中处理器的第一群组在os块60处与第一虚拟邻近域相关联。os块60可包括将与处理器的第一群组相对应的一个或多个逻辑线程映射到第一虚拟邻近域。此外,os块62创建处理器的第二群组,并且os块64将处理器的第二群组与第二虚拟邻近域相关联。os块64可包括将与处理器的第二群组相对应的一个或多个逻辑线程映射到第二虚拟邻近域。图示的方法50因此通过克服对于每群组逻辑线程数目的os限制,克服每群组逻辑线程数目的不平衡,以及提供比硬分区高得多的每numa节点的带宽,来增强了性能。28.现在转到图4,示出了性能增强的计算系统110。系统110一般可以是电子设备/平台的一部分,具有计算功能(例如,个人数字助理/pda、笔记本计算机、平板计算机、可转换平板设备、服务器)、通信功能(例如,智能电话)、成像功能(例如,相机、摄像机)、媒体播放功能(例如,智能电视/tv)、可穿戴功能(例如,手表、眼镜、头饰、鞋类、珠宝)、车辆功能(例如,汽车、卡车、摩托车)、机器人功能(例如,自主机器人)、物联网(internetofthings,iot)功能,等等,或者这些的任何组合。在图示的示例中,系统110包括具有多个核心113的主机处理器112(例如,中央处理单元/cpu)和与系统存储器116耦合的集成存储器控制器(integratedmemorycontroller,imc)114。29.图示的系统110还包括输入输出(io)模块118,与主机处理器112和图形处理器120(例如,图形处理单元/gpu)一起作为片上系统(systemonchip,soc)实现在半导体芯片122上。图示的io模块118与例如显示器124(例如,触摸屏、液晶显示器/lcd、发光二极管/led显示器)、网络控制器126(例如,有线和/或无线)以及大容量存储装置128(例如,硬盘驱动器/hdd、光盘、固态驱动器/ssd、闪存)进行通信。30.在一实施例中,主机处理器112、图形处理器120和/或io模块118执行从系统存储器116和/或大容量存储装置128取回的程序指令134,以执行已经论述过的方法50(图3)的一个或多个方面。从而,指令134的执行可使得半导体芯片122和/或计算系统110识别numa节点,在numa节点内定义第一虚拟邻近域,并且在numa节点内定义第二虚拟邻近域,其中第一虚拟邻近域和第二虚拟邻近域是经由一个或多个os接口表定义的。系统110因此至少在以下程度上是性能增强的:系统110克服了对于每群组逻辑线程数目的os限制,克服了每群组逻辑线程数目的不平衡,并且提供了比硬分区高得多的每numa节点的带宽。31.图5示出了半导体封装装置140。图示的装置140包括一个或多个衬底142(例如,硅、蓝宝石、砷化镓)和耦合到(一个或多个)衬底142的逻辑144(例如,晶体管阵列和其他集成电路/ic组件)。图示的一个或多个衬底142耦合(例如,插入)到插座146(例如,直接或经由一个或多个中间组件)。逻辑144可至少部分在可配置逻辑或固定功能逻辑硬件中实现。在一个示例中,逻辑144实现已经论述过的方法50(图3)的一个或多个方面。从而,逻辑144可识别numa节点,在numa节点内定义第一虚拟邻近域,并且在numa节点内定义第二虚拟邻近域,其中第一虚拟邻近域和第二虚拟邻近域是经由一个或多个os接口表定义的。装置140因此至少在以下程度上是性能增强的:装置140克服了对于每群组逻辑线程数目的os限制,克服了每群组逻辑线程数目的不平衡,并且提供了比硬分区高得多的每numa节点的带宽。32.在一个示例中,逻辑144包括被定位(例如,嵌入)在(一个或多个)衬底142内的晶体管沟道区域。从而,逻辑144和(一个或多个)衬底142之间的界面可能不是突变结。逻辑144也可被认为包括在(一个或多个)衬底142的初始晶片上生长的外延层。33.图6根据一个实施例图示了处理器核心200。处理器核心200可以是用于任何类型的处理器的核心,例如微处理器、嵌入式处理器、数字信号处理器(digitalsignalprocessor,dsp)、网络处理器或者其他执行代码的设备。虽然在图6中只图示了一个处理器核心200,但处理元件可改为包括多于一个图6中所示的处理器核心200。处理器核心200可以是单线程核心,或者对于至少一个实施例,处理器核心200可以是多线程的,因为其对于每个核心可包括多于一个硬件线程情境(或者说“逻辑处理器”)。34.图6还图示了耦合到处理器核心200的存储器270。存储器270可以是本领域技术人员已知的或者以其他方式可获得的各种存储器(包括存储器层次体系的各种层)中的任何一者。存储器270可包括要被处理器核心200执行的一个或多个代码213指令,其中代码213可实现已经论述过的方法50(图3)的一个或多个方面。处理器核心200遵循由代码213指示的指令的程序序列。每个指令可进入前端部分210并且被一个或多个解码器220处理。解码器220可生成诸如预定格式的固定宽度微操作之类的微操作作为其输出,或者可生成其他指令、微指令或者反映原始代码指令的控制信号。图示的前端部分210还包括寄存器重命名逻辑225和调度逻辑230,它们一般分配资源并且对与转换指令相对应的操作排队以便执行。35.处理器核心200被示为包括具有一组执行单元255-1至255-n的执行逻辑250。一些实施例可包括专用于特定功能或功能集合的若干个执行单元。其他实施例可只包括一个执行单元或者可执行特定功能的一个执行单元。图示的执行逻辑250执行由代码指令指定的操作。36.在代码指令指定的操作执行完成之后,后端逻辑260让代码213的指令引退。在一个实施例中,处理器核心200允许指令的无序执行,但要求指令的有序引退。引退逻辑265可采取本领域技术人员已知的多种形式(例如,重排序缓冲器之类的)。这样,处理器核心200在代码213的执行期间被变换,至少就由解码器生成的输出、被寄存器重命名逻辑225利用的硬件寄存器和表格和被执行逻辑250修改的任何寄存器(未示出)而言。37.虽然在图6中没有图示,但处理元件可包括与处理器核心200一起在芯片上的其他元件。例如,处理元件可包括与处理器核心200一起的存储器控制逻辑。处理元件可包括i/o控制逻辑和/或可包括与存储器控制逻辑集成的i/o控制逻辑。处理元件也可包括一个或多个缓存。38.现在参考图7,示出了根据一实施例的计算系统1000的框图。图7中所示的是多处理器系统1000,其包括第一处理元件1070和第二处理元件1080。虽然示出了两个处理元件1070和1080,但要理解系统1000的实施例也可包括仅一个这种处理元件。39.系统1000被示为点到点互连系统,其中第一处理元件1070和第二处理元件1080经由点到点互连1050耦合。应当理解,图7中所示的任何或所有互连可实现为多点分支总线,而不是点到点互连。40.如图7中所示,处理元件1070和1080的每一者可以是多核处理器,包括第一和第二处理器核心(即,处理器核心1074a和1074b和处理器核心1084a和1084b)。这种核心1074a、1074b、1084a、1084b可被配置为以与上文联系图6所述类似的方式来执行指令代码。41.每个处理元件1070、1080可包括至少一个共享缓存1896a、1896b。共享缓存1896a、1896b可存储被处理器的一个或多个组件利用的数据(例如,指令),所述组件例如分别是核心1074a、1074b和1084a、1084b。例如,共享缓存1896a、1896b可在本地缓存存储器1032、1034中存储的数据,供处理器的组件更快速访问。在一个或多个实施例中,共享缓存1896a、1896b可包括一个或多个中间级别缓存,例如第2级(l2)、第3级(l3)、第4级(l4)或其他级别的缓存,最后一级缓存(lastlevelcache,llc),和/或这些的组合。42.虽然示为只具有两个处理元件1070、1080,但要理解实施例的范围不限于此。在其他实施例中,一个或多个额外的处理元件可存在于给定的处理器中。或者,处理元件1070、1080中的一个或多个可以是除了处理器以外的元件,例如加速器或者现场可编程门阵列。例如,(一个或多个)额外的处理元件可包括与第一处理器1070相同的(一个或多个)额外处理器,与第一处理器1070异构或非对称的(一个或多个)额外处理器,加速器(例如,图形加速器或者数字信号处理(dsp)单元),现场可编程门阵列,或者任何其他处理元件。在处理元件1070、1080之间,就包括体系结构特性、微体系结构特性、热特性、功率消耗特性等等在内的价值度量的范围而言可以有多种差异。这些差异可实际上将其自身展现为处理元件1070、1080之间的非对称性和异构性。对于至少一个实施例,各种处理元件1070、1080可存在于相同的晶粒封装中。43.第一处理元件1070还可包括存储器控制器逻辑(mc)1072和点到点(p-p)接口1076和1078。类似地,第二处理元件1080可包括mc1082和p-p接口1086和1088。如图7中所示,mc1072和1082将处理器耦合到各自的存储器,即存储器1032和存储器1034,存储器1032和存储器1034可以是在本地附接到各个处理器的主存储器的一部分。虽然mc1072和1082被示为集成到处理元件1070、1080中,但对于替换实施例,mc逻辑可以是在处理元件1070、1080之外的分立逻辑,而不是集成在其中。44.第一处理元件1070和第二处理元件1080可分别经由p-p互连1076、1086耦合到i/o子系统1090。如图7中所示,i/o子系统1090包括p-p接口1094和1098。此外,i/o子系统1090包括接口1092来将i/o子系统1090与高性能图形引擎1038耦合。在一个实施例中,总线1049可用于将图形引擎1038耦合到i/o子系统1090。或者,点到点互连可耦合这些组件。45.进而,i/o子系统1090可经由接口1096耦合到第一总线1016。在一个实施例中,第一总线1016可以是外围组件互连(peripheralcomponentinterconnect,pci)总线,或者诸如快速pci总线或另一种第三代i/o互连总线之类的总线,虽然实施例的范围不限于此。46.如图7中所示,各种i/o设备1014(例如,生物计量扫描仪、扬声器、相机、传感器)可耦合到第一总线1016,以及可将第一总线1016耦合到第二总线1020的总线桥1018。在一个实施例中,第二总线1020可以是低引脚数(lowpincount,lpc)总线。各种设备可耦合到第二总线1020,例如包括键盘/鼠标1012、(一个或多个)通信设备1026和数据存储单元1019,例如盘驱动器或者其他大容量存储设备,它们在一个实施例中可包括代码1030。图示的代码1030可实现已经论述过的方法50(图3)的一个或多个方面。另外,音频i/o1024可耦合到第二总线1020并且电池1010可向计算系统1000供应电力。47.注意设想了其他实施例。例如,取代图7的点到点体系结构,系统可实现多点分支总线或者另外的这种通信拓扑。另外,图7的元件可改为利用比图7中所示更多或更少的集成芯片来划分。48.附加注释和示例:49.示例1包括一种性能增强的计算系统,包括插座,与所述插座耦合的处理器,以及与所述处理器耦合的存储器,所述存储器包括一组可执行程序指令,所述指令当被所述处理器执行时,使得所述处理器识别非统一存储器访问(numa)节点,在所述numa节点内定义第一虚拟邻近域,并且在所述numa节点内定义第二虚拟邻近域,其中所述第一虚拟邻近域和所述第二虚拟邻近域是经由一个或多个操作系统(os)接口表来定义的。50.示例2包括如示例1所述的计算系统,其中所述一个或多个os接口表是从由静态资源亲和表和系统定位信息表组成的群组中选择的。51.示例3包括如示例1所述的计算系统,其中所述numa节点专用于所述插座。52.示例4包括如示例3所述的计算系统,其中所述插座具有初始交织配置,并且其中为了定义所述第一虚拟邻近域和所述第二虚拟邻近域,所述指令当被执行时使得所述处理器维持所述初始交织配置。53.示例5包括如示例3所述的计算系统,其中所述插座具有初始缓存分组,并且其中为了定义所述第一虚拟邻近域和所述第二虚拟邻近域,所述指令当被执行时使得所述处理器维持所述初始缓存分组。54.示例6包括如示例1至5的任何一项所述的计算系统,其中所述指令当被执行时还使得所述处理器创建处理器的第一群组,将所述处理器的第一群组与所述第一虚拟邻近域相关联,创建处理器的第二群组,并且将所述处理器的第二群组与所述第二虚拟邻近域相关联。55.示例7包括一种半导体装置,其包括一个或多个衬底,以及与所述一个或多个衬底耦合的逻辑,其中所述逻辑至少部分实现在可配置逻辑或者固定功能硬件逻辑的一个或多个中,与所述一个或多个衬底耦合的逻辑用于识别非统一存储器访问(numa)节点,在所述numa节点内定义第一虚拟邻近域,并且在所述numa节点内定义第二虚拟邻近域,其中所述第一虚拟邻近域和所述第二虚拟邻近域是经由一个或多个操作系统(os)接口表来定义的。56.示例8包括如示例7所述的装置,其中所述一个或多个os接口表是从由静态资源亲和表和系统定位信息表组成的群组中选择的。57.示例9包括如示例7所述的装置,其中所述numa节点专用于物理插座。58.示例10包括如示例9所述的装置,其中所述物理插座具有初始交织配置,并且其中为了定义所述第一虚拟邻近域和所述第二虚拟邻近域,与所述一个或多个衬底耦合的所述逻辑用于维持所述初始交织配置。59.示例11包括如示例9所述的装置,其中所述物理插座具有初始缓存分组,并且其中为了定义所述第一虚拟邻近域和所述第二虚拟邻近域,与所述一个或多个衬底耦合的所述逻辑用于维持所述初始缓存分组。60.示例12包括如示例7至11的任何一项所述的装置,其中与所述一个或多个衬底耦合的所述逻辑用于创建处理器的第一群组,将所述处理器的第一群组与所述第一虚拟邻近域相关联,创建处理器的第二群组,并且将所述处理器的第二群组与所述第二虚拟邻近域相关联。61.示例13包括如示例7至11的任何一项所述的装置,其中与所述一个或多个衬底耦合的所述逻辑包括定位在所述一个或多个衬底内的晶体管沟道区域。62.示例14包括至少一个计算机可读存储介质,其包括一组可执行程序指令,所述指令当被计算系统执行时,使得所述计算系统识别非统一存储器访问(numa)节点,在所述numa节点内定义第一虚拟邻近域,并且在所述numa节点内定义第二虚拟邻近域,其中所述第一虚拟邻近域和所述第二虚拟邻近域是经由一个或多个操作系统(os)接口表来定义的。63.示例15包括如示例14所述的至少一个计算机可读存储介质,其中所述一个或多个os接口表是从由静态资源亲和表和系统定位信息表组成的群组中选择的。64.示例16包括如示例14所述的至少一个计算机可读存储介质,其中所述numa节点专用于物理插座。65.示例17包括如示例16所述的至少一个计算机可读存储介质,其中所述物理插座具有初始交织配置,并且其中为了定义所述第一虚拟邻近域和所述第二虚拟邻近域,所述指令当被执行时使得所述计算系统维持所述初始交织配置。66.示例18包括如示例16所述的至少一个计算机可读存储介质,其中所述物理插座具有初始缓存分组,并且其中为了定义所述第一虚拟邻近域和所述第二虚拟邻近域,所述指令当被执行时使得所述计算系统维持所述初始缓存分组。67.示例19包括如示例14所述的至少一个计算机可读存储介质,其中所述指令当被执行时还使得所述计算系统识别第二numa节点,其中所述第二numa节点专用于所述物理插座,并且在所述第二numa节点内定义两个或更多个虚拟邻近域,其中所述两个或更多个虚拟邻近域是经由所述一个或多个os接口表来定义的。68.示例20包括如示例14至19的任何一项所述的至少一个计算机可读存储介质,其中所述指令当被执行时还使得所述计算系统创建处理器的第一群组,将所述处理器的第一群组与所述第一虚拟邻近域相关联,创建处理器的第二群组,并且将所述处理器的第二群组与所述第二虚拟邻近域相关联。69.示例21包括如示例14至20的任何一项所述的至少一个计算机可读存储介质,其中所述指令当被执行时还使得所述计算系统经由所述一个或多个os接口表在所述numa节点内定义多于两个虚拟邻近域。70.示例22包括一种操作性能增强的计算系统的方法,所述方法包括识别非统一存储器访问(numa)节点,在所述numa节点内定义第一虚拟邻近域,并且在所述numa节点内定义第二虚拟邻近域,其中所述第一虚拟邻近域和所述第二虚拟邻近域是经由一个或多个操作系统(os)接口表来定义的。71.示例23包括如示例22所述的方法,其中所述一个或多个os接口表是从由静态资源亲和表和系统定位信息表组成的群组中选择的。72.示例24包括如示例22所述的方法,其中所述numa节点专用于物理插座,其中所述物理插座具有初始交织配置,其中定义所述第一虚拟邻近域和所述第二虚拟邻近域包括维持所述初始交织配置,其中所述物理插座具有初始缓存分组,并且其中定义所述第一虚拟邻近域和所述第二虚拟邻近域包括维持所述初始缓存分组。73.示例25包括如示例22至24的任何一项所述的方法,还包括创建处理器的第一群组,将所述处理器的第一群组与所述第一虚拟邻近域相关联,创建处理器的第二群组,并且将所述处理器的第二群组与所述第二虚拟邻近域相关联。74.示例26包括用于执行如示例22至25的任何一项所述的方法的装置。75.本文描述的技术因此提供了系统固件acpi表的新颖使用来描述特定物理numa实现中的存储器。acpi表,例如slit和srat,可被利用于平台和cpu特征。例如,邻近域可被用于slit和srat表中来模拟多处理器系统上的单个物理numa节点内的多个虚拟numa节点。76.实施例适用于与所有类型的半导体集成电路(“ic”)芯片一起使用。这些ic芯片的示例包括但不限于处理器、控制器、芯片集组件、可编程逻辑阵列(programmablelogicarray,pla)、存储器芯片、网络芯片,片上系统(systemsonchip,soc)、ssd/nand控制器asic,等等。此外,在一些附图中,用线条来表示信号导线。某些可能是不同的,以指示更多的构成信号路径,具有数字标注,以指示构成信号路径的数目,和/或在一端或多端具有箭头,以指示主要信息流方向。然而,这不应当以限制方式来解释。更确切地说,这种添加的细节可联系一个或多个示范性实施例使用来促进对电路的更容易理解。任何表示的信号线,无论是否具有附加信息,都可实际上包括一个或多个信号,这一个或多个信号可在多个方向上行进并且可利用任何适当类型的信号方案来实现,例如利用差动对实现的数字或模拟线路、光纤线路和/或单端线路。77.可能给出了示例大小/型号/值/范围,虽然实施例不限于此。随着制造技术(例如,光刻术)随着时间流逝而成熟,预期能够制造具有更小大小的器件。此外,为了图示和论述的简单,并且为了不模糊实施例的某些方面,在附图内可能示出或不示出到ic芯片和其他组件的公知电源/接地连接。另外,可能以框图形式示出布置以避免模糊实施例,并且同时也考虑到了如下事实:关于这种框图布置的实现的具体细节是高度取决于在其内实现实施例的计算系统的,即,这种具体细节应当完全在本领域技术人员的视野内。在阐述具体细节(例如,电路)以便描述示例实施例的情况下,本领域技术人员应当清楚,没有这些具体细节,或者利用这些具体细节的变体,也可实现实施例。从而说明书应当被认为是说明性的,而不是限制性的。78.术语“耦合”在本文中可用于指所涉组件之间的任何类型的关系,无论是直接的还是间接的,并且可应用到电的、机械的、液体的、光的、电磁的、机电的或者其他连接。此外,除非另外指出,否则术语“第一”、“第二”等等在本文中可只用于促进论述,而不带有特定的时间或先后意义。79.就在本技术中和权利要求中使用的而言,由术语“…中的一个或多个”联接的项目的列表可意指列出的术语的任何组合。例如,短语“a、b或c中的一个或多个”可意指a;b;c;a和b;a和c;b和c;或者a、b和c。80.本领域技术人员从前述描述将会明白,实施例的宽广技术可按多种形式实现。因此,虽然已联系其特定示例描述了实施例,但实施例的真实范围不应当限于此,因为本领域技术人员在研习了附图、说明书和所附权利要求后将清楚其他修改。当前第1页12当前第1页12

技术领域:

:1.实施例概括而言涉及非统一存储器访问(non-uniformmemoryaccess,numa)体系结构。更具体而言,实施例涉及经由操作系统(os)接口表的单个numa域内的多个虚拟numa域的建立。

背景技术:

::2.在现代cpu(中央处理单元)体系结构中,核心计数大幅增加,达到了这样的水平,即os和/或应用创建虚拟numa节点,以通过在每个numa域划分竞争的软件对象,来实现易于管理和改善的性能。为了向后兼容,可能也需要在os级别的这种虚拟numa创建。windows使用一个叫做group的概念,将两个或更多个numa节点虚拟化,每个节点最多有六十四个逻辑线程,以支持具有多于六十四个逻辑线程的单个多处理器numa节点。这种方案可能会导致group之间可用存储器的不平衡,以及group之间逻辑线程数目的不平衡,这对于涉及每个numa域的高存储器带宽以及高核心计数的工作负载是不利的。技术实现要素:3.根据本公开的一方面,提供了一种计算系统,包括:插座;与所述插座耦合的处理器;以及与所述处理器耦合的存储器,所述存储器包括一组可执行程序指令,所述指令当被所述处理器执行时,使得所述处理器:识别非统一存储器访问(numa)节点,在所述numa节点内定义第一虚拟邻近域,并且在所述numa节点内定义第二虚拟邻近域,其中所述第一虚拟邻近域和所述第二虚拟邻近域是经由一个或多个操作系统(os)接口表来定义的。4.根据本公开的一方面,提供了一种半导体装置,包括:一个或多个衬底;以及与所述一个或多个衬底耦合的逻辑,其中所述逻辑至少部分实现在可配置逻辑或者固定功能硬件逻辑的一个或多个中,与所述一个或多个衬底耦合的所述逻辑用于:识别非统一存储器访问(numa)节点;在所述numa节点内定义第一虚拟邻近域;并且在所述numa节点内定义第二虚拟邻近域,其中所述第一虚拟邻近域和所述第二虚拟邻近域是经由一个或多个操作系统(os)接口表来定义的。5.根据本公开的一方面,提供了至少一个计算机可读存储介质,其包括一组可执行程序指令,所述指令当被计算系统执行时,使得所述计算系统:识别非统一存储器访问(numa)节点;在所述numa节点内定义第一虚拟邻近域;并且在所述numa节点内定义第二虚拟邻近域,其中所述第一虚拟邻近域和所述第二虚拟邻近域是经由一个或多个操作系统(os)接口表来定义的。6.根据本公开的一方面,提供了一种方法,包括:识别非统一存储器访问(numa)节点;在所述numa节点内定义第一虚拟邻近域;并且在所述numa节点内定义第二虚拟邻近域,其中所述第一虚拟邻近域和所述第二虚拟邻近域是经由一个或多个操作系统(os)接口表来定义的。附图说明7.通过阅读以下说明书和所附权利要求,并且通过参考以下附图,实施例的各种优点将对本领域技术人员变得清楚,附图中:8.图1是传统的os和bios(基本输入/输出系统)报告和根据一实施例的os和bios报告的示例的比较图示;9.图2a是没有亚numa集群(sub-numaclustering,snc)的传统体系结构和根据一实施例的没有snc的体系结构的示例的比较框图;10.图2b是根据一实施例的具有两个亚numa集群的体系结构和具有两个虚拟邻近域的体系结构的示例的比较框图;11.图2c是根据一实施例的具有四个亚numa集群的体系结构和具有四个虚拟邻近域的体系结构的示例的比较框图;12.图3是根据一实施例的操作性能增强计算系统的方法的示例的流程图;13.图4是根据一实施例的性能增强计算系统的示例的框图;14.图5是根据一实施例的半导体装置的示例的图示;15.图6是根据一实施例的处理器的示例的框图;并且16.图7是根据一实施例的基于多处理器的计算系统的示例的框图。具体实施方式17.现在转到图1,对于启用了超线程并且禁用了snc的36核单插座(socket)系统,示出了传统的bios和os报告10。在图示的示例中,biosacpi(高级配置和电源接口)将正确描述单个存储器邻近域中的七十二个线程。然而,传统的操作系统,比如windows,当前通过创建两个处理器群组和两个存储器节点来处理这种情形。线程0-63在群组0中,具有所有可用的存储器,而线程64-71在群组1中,没有存储器。其结果是不正确的存储器分配和每个numa节点的逻辑核心数目的不平衡。该问题对于较大的核心计数而言尤其重要。18.正如将更详细论述的那样,acpibios中的虚拟numa模式可为一个物理多处理器在诸如系统资源亲和表(systemresourceaffinitytable,srat)之类的os接口表中创建多个虚拟邻近域,而不改变存储器控制器/通道交织或者llc(最后一级缓存)分组。os解释os接口表以创建多个处理器群组/多个numa。如增强的os和bios报告12中所示,这种虚拟numa概念解决了存储器分配不当和每个numa节点的逻辑核心数目不平衡的问题。更特别的是,实施例可克服每群组六十四个逻辑线程的os限制,克服每群组逻辑线程数目的不平衡,并且提供比硬分区高得多的带宽/numa。19.现在转到图2a,示出了传统体系结构20,其中snc被禁用。一般而言,每个cpu多处理器的核心和存储器被划分为单独的集群,os使用这些集群来创建具有少于六十四个逻辑线程的group对象。在图示的示例中,体系结构20包括两个“假”的cpu和存储器节点,并且os具有一个大小为零的存储器节点。20.相比之下,系统固件实施例描述了经由acpi表在单个numa节点内的多个“虚拟numa”存储器域。例如,系统固件可生成acpi表,以将一numa节点中的逻辑处理器的子集与属于该物理numa节点的存储器的相应子集联系起来。在操作系统对每个numa存储器范围所允许的逻辑核心的数目有限制的情况下,这样的方案能够适当地平衡和利用单个numa存储器节点内的所有逻辑处理器。从而,增强型体系结构22不包括假的cpu和存储器节点,或者具有大小为零的一个存储器节点的os。图示的体系结构20、22的通道带宽都是8。21.图2b表明,具有两个亚numa集群的传统体系结构30的通道带宽为4,而具有两个虚拟邻近域的增强型体系结构32的通道带宽为8。从而,增强型体系结构32维持了初始(例如,snc启用前)的交织配置和缓存分组。22.图2c表明,具有四个亚numa集群的传统体系结构40的通道带宽为2,而具有四个虚拟邻近域的增强型体系结构42的通道带宽为8。从而,存储器带宽分布在物理numa节点内的所有交织的存储器通道上,并且增强型体系结构42维持了初始(例如,snc启用前)的交织配置和缓存分组。23.图3示出了操作性能增强的计算系统的方法50。方法50可实现在作为存储在诸如随机访问存储器(randomaccessmemory,ram)、只读存储器(readonlymemory,rom)、可编程rom(programmablerom,prom)、固件、闪存等等之类的机器或计算机可读存储介质中的逻辑指令集合的一个或多个模块中,实现在诸如可编程逻辑阵列(programmablelogicarray,pla)、现场可编程门阵列(fieldprogrammablegatearray,fpga)、复杂可编程逻辑器件(complexprogrammablelogicdevice,cpld)之类的可配置逻辑中,利用诸如专用集成电路(applicationspecificintegratedcircuit,asic)、互补金属氧化物半导体(complementarymetaloxidesemiconductor,cmos)或晶体管-晶体管逻辑(transistor-transistorlogic,ttl)技术之类的电路技术实现在固定功能逻辑硬件中,或者这些的组合。24.例如,可以以一种或多种编程语言的任何组合来编写用于执行方法50中所示的操作的计算机程序代码,所述编程语言包括面向对象的编程语言,比如java、smalltalk、c 之类的,还包括传统的过程式编程语言,比如“c”编程语言或类似的编程语言。此外,逻辑指令可包括汇编指令、指令集体系结构(instructionsetarchitecture,isa)指令、机器指令、机器相关指令、微代码、状态设置数据、用于集成电路的配置数据、个性化电子电路和/或硬件原生的其他结构组件(例如,主机处理器、中央处理单元/cpu、微控制器等等)的状态信息。25.图示的bios处理块52识别numa节点,其中在bios块54处定义第一虚拟邻近域。在一实施例中,numa节点专门用于单个物理多处理器。bios块56在numa节点内定义第二虚拟邻近域。在图示的示例中,第一虚拟邻近域和第二虚拟邻近域是经由一个或多个os接口表定义的,例如静态资源亲和表(staticresourceaffinitytable,srat)、系统定位信息表(systemlocalityinformationtable,slit),等等,或者其任何组合。在一个示例中,物理多处理器具有初始交织配置(例如,八个通道带宽),并且定义第一虚拟邻近域和第二虚拟邻近域包括维持初始交织配置。此外,物理多处理器可具有初始缓存分组(例如,llc分组)。在这种情况下,定义第一虚拟邻近域和第二虚拟邻近域可包括维持初始缓存分组。26.虽然在图示的示例中定义了两个虚拟邻近域以方便论述,但虚拟邻近域的数目不限于两个。从而,方法50可经由一个或多个os接口表在numa节点内定义多于两个虚拟邻近域。此外,在cpu封装被设计为每个插座有多于一个物理numa节点的情况下,这些物理numa节点中的每一个可被表示为两个或更多个虚拟numa节点。因此,方法50还可识别第二numa节点,其中第二numa节点专用于物理插座,并且在第二numa节点内定义两个或更多个虚拟邻近域(例如,经由一个或多个os接口表)。27.在一实施例中,os块58创建处理器的第一群组,其中处理器的第一群组在os块60处与第一虚拟邻近域相关联。os块60可包括将与处理器的第一群组相对应的一个或多个逻辑线程映射到第一虚拟邻近域。此外,os块62创建处理器的第二群组,并且os块64将处理器的第二群组与第二虚拟邻近域相关联。os块64可包括将与处理器的第二群组相对应的一个或多个逻辑线程映射到第二虚拟邻近域。图示的方法50因此通过克服对于每群组逻辑线程数目的os限制,克服每群组逻辑线程数目的不平衡,以及提供比硬分区高得多的每numa节点的带宽,来增强了性能。28.现在转到图4,示出了性能增强的计算系统110。系统110一般可以是电子设备/平台的一部分,具有计算功能(例如,个人数字助理/pda、笔记本计算机、平板计算机、可转换平板设备、服务器)、通信功能(例如,智能电话)、成像功能(例如,相机、摄像机)、媒体播放功能(例如,智能电视/tv)、可穿戴功能(例如,手表、眼镜、头饰、鞋类、珠宝)、车辆功能(例如,汽车、卡车、摩托车)、机器人功能(例如,自主机器人)、物联网(internetofthings,iot)功能,等等,或者这些的任何组合。在图示的示例中,系统110包括具有多个核心113的主机处理器112(例如,中央处理单元/cpu)和与系统存储器116耦合的集成存储器控制器(integratedmemorycontroller,imc)114。29.图示的系统110还包括输入输出(io)模块118,与主机处理器112和图形处理器120(例如,图形处理单元/gpu)一起作为片上系统(systemonchip,soc)实现在半导体芯片122上。图示的io模块118与例如显示器124(例如,触摸屏、液晶显示器/lcd、发光二极管/led显示器)、网络控制器126(例如,有线和/或无线)以及大容量存储装置128(例如,硬盘驱动器/hdd、光盘、固态驱动器/ssd、闪存)进行通信。30.在一实施例中,主机处理器112、图形处理器120和/或io模块118执行从系统存储器116和/或大容量存储装置128取回的程序指令134,以执行已经论述过的方法50(图3)的一个或多个方面。从而,指令134的执行可使得半导体芯片122和/或计算系统110识别numa节点,在numa节点内定义第一虚拟邻近域,并且在numa节点内定义第二虚拟邻近域,其中第一虚拟邻近域和第二虚拟邻近域是经由一个或多个os接口表定义的。系统110因此至少在以下程度上是性能增强的:系统110克服了对于每群组逻辑线程数目的os限制,克服了每群组逻辑线程数目的不平衡,并且提供了比硬分区高得多的每numa节点的带宽。31.图5示出了半导体封装装置140。图示的装置140包括一个或多个衬底142(例如,硅、蓝宝石、砷化镓)和耦合到(一个或多个)衬底142的逻辑144(例如,晶体管阵列和其他集成电路/ic组件)。图示的一个或多个衬底142耦合(例如,插入)到插座146(例如,直接或经由一个或多个中间组件)。逻辑144可至少部分在可配置逻辑或固定功能逻辑硬件中实现。在一个示例中,逻辑144实现已经论述过的方法50(图3)的一个或多个方面。从而,逻辑144可识别numa节点,在numa节点内定义第一虚拟邻近域,并且在numa节点内定义第二虚拟邻近域,其中第一虚拟邻近域和第二虚拟邻近域是经由一个或多个os接口表定义的。装置140因此至少在以下程度上是性能增强的:装置140克服了对于每群组逻辑线程数目的os限制,克服了每群组逻辑线程数目的不平衡,并且提供了比硬分区高得多的每numa节点的带宽。32.在一个示例中,逻辑144包括被定位(例如,嵌入)在(一个或多个)衬底142内的晶体管沟道区域。从而,逻辑144和(一个或多个)衬底142之间的界面可能不是突变结。逻辑144也可被认为包括在(一个或多个)衬底142的初始晶片上生长的外延层。33.图6根据一个实施例图示了处理器核心200。处理器核心200可以是用于任何类型的处理器的核心,例如微处理器、嵌入式处理器、数字信号处理器(digitalsignalprocessor,dsp)、网络处理器或者其他执行代码的设备。虽然在图6中只图示了一个处理器核心200,但处理元件可改为包括多于一个图6中所示的处理器核心200。处理器核心200可以是单线程核心,或者对于至少一个实施例,处理器核心200可以是多线程的,因为其对于每个核心可包括多于一个硬件线程情境(或者说“逻辑处理器”)。34.图6还图示了耦合到处理器核心200的存储器270。存储器270可以是本领域技术人员已知的或者以其他方式可获得的各种存储器(包括存储器层次体系的各种层)中的任何一者。存储器270可包括要被处理器核心200执行的一个或多个代码213指令,其中代码213可实现已经论述过的方法50(图3)的一个或多个方面。处理器核心200遵循由代码213指示的指令的程序序列。每个指令可进入前端部分210并且被一个或多个解码器220处理。解码器220可生成诸如预定格式的固定宽度微操作之类的微操作作为其输出,或者可生成其他指令、微指令或者反映原始代码指令的控制信号。图示的前端部分210还包括寄存器重命名逻辑225和调度逻辑230,它们一般分配资源并且对与转换指令相对应的操作排队以便执行。35.处理器核心200被示为包括具有一组执行单元255-1至255-n的执行逻辑250。一些实施例可包括专用于特定功能或功能集合的若干个执行单元。其他实施例可只包括一个执行单元或者可执行特定功能的一个执行单元。图示的执行逻辑250执行由代码指令指定的操作。36.在代码指令指定的操作执行完成之后,后端逻辑260让代码213的指令引退。在一个实施例中,处理器核心200允许指令的无序执行,但要求指令的有序引退。引退逻辑265可采取本领域技术人员已知的多种形式(例如,重排序缓冲器之类的)。这样,处理器核心200在代码213的执行期间被变换,至少就由解码器生成的输出、被寄存器重命名逻辑225利用的硬件寄存器和表格和被执行逻辑250修改的任何寄存器(未示出)而言。37.虽然在图6中没有图示,但处理元件可包括与处理器核心200一起在芯片上的其他元件。例如,处理元件可包括与处理器核心200一起的存储器控制逻辑。处理元件可包括i/o控制逻辑和/或可包括与存储器控制逻辑集成的i/o控制逻辑。处理元件也可包括一个或多个缓存。38.现在参考图7,示出了根据一实施例的计算系统1000的框图。图7中所示的是多处理器系统1000,其包括第一处理元件1070和第二处理元件1080。虽然示出了两个处理元件1070和1080,但要理解系统1000的实施例也可包括仅一个这种处理元件。39.系统1000被示为点到点互连系统,其中第一处理元件1070和第二处理元件1080经由点到点互连1050耦合。应当理解,图7中所示的任何或所有互连可实现为多点分支总线,而不是点到点互连。40.如图7中所示,处理元件1070和1080的每一者可以是多核处理器,包括第一和第二处理器核心(即,处理器核心1074a和1074b和处理器核心1084a和1084b)。这种核心1074a、1074b、1084a、1084b可被配置为以与上文联系图6所述类似的方式来执行指令代码。41.每个处理元件1070、1080可包括至少一个共享缓存1896a、1896b。共享缓存1896a、1896b可存储被处理器的一个或多个组件利用的数据(例如,指令),所述组件例如分别是核心1074a、1074b和1084a、1084b。例如,共享缓存1896a、1896b可在本地缓存存储器1032、1034中存储的数据,供处理器的组件更快速访问。在一个或多个实施例中,共享缓存1896a、1896b可包括一个或多个中间级别缓存,例如第2级(l2)、第3级(l3)、第4级(l4)或其他级别的缓存,最后一级缓存(lastlevelcache,llc),和/或这些的组合。42.虽然示为只具有两个处理元件1070、1080,但要理解实施例的范围不限于此。在其他实施例中,一个或多个额外的处理元件可存在于给定的处理器中。或者,处理元件1070、1080中的一个或多个可以是除了处理器以外的元件,例如加速器或者现场可编程门阵列。例如,(一个或多个)额外的处理元件可包括与第一处理器1070相同的(一个或多个)额外处理器,与第一处理器1070异构或非对称的(一个或多个)额外处理器,加速器(例如,图形加速器或者数字信号处理(dsp)单元),现场可编程门阵列,或者任何其他处理元件。在处理元件1070、1080之间,就包括体系结构特性、微体系结构特性、热特性、功率消耗特性等等在内的价值度量的范围而言可以有多种差异。这些差异可实际上将其自身展现为处理元件1070、1080之间的非对称性和异构性。对于至少一个实施例,各种处理元件1070、1080可存在于相同的晶粒封装中。43.第一处理元件1070还可包括存储器控制器逻辑(mc)1072和点到点(p-p)接口1076和1078。类似地,第二处理元件1080可包括mc1082和p-p接口1086和1088。如图7中所示,mc1072和1082将处理器耦合到各自的存储器,即存储器1032和存储器1034,存储器1032和存储器1034可以是在本地附接到各个处理器的主存储器的一部分。虽然mc1072和1082被示为集成到处理元件1070、1080中,但对于替换实施例,mc逻辑可以是在处理元件1070、1080之外的分立逻辑,而不是集成在其中。44.第一处理元件1070和第二处理元件1080可分别经由p-p互连1076、1086耦合到i/o子系统1090。如图7中所示,i/o子系统1090包括p-p接口1094和1098。此外,i/o子系统1090包括接口1092来将i/o子系统1090与高性能图形引擎1038耦合。在一个实施例中,总线1049可用于将图形引擎1038耦合到i/o子系统1090。或者,点到点互连可耦合这些组件。45.进而,i/o子系统1090可经由接口1096耦合到第一总线1016。在一个实施例中,第一总线1016可以是外围组件互连(peripheralcomponentinterconnect,pci)总线,或者诸如快速pci总线或另一种第三代i/o互连总线之类的总线,虽然实施例的范围不限于此。46.如图7中所示,各种i/o设备1014(例如,生物计量扫描仪、扬声器、相机、传感器)可耦合到第一总线1016,以及可将第一总线1016耦合到第二总线1020的总线桥1018。在一个实施例中,第二总线1020可以是低引脚数(lowpincount,lpc)总线。各种设备可耦合到第二总线1020,例如包括键盘/鼠标1012、(一个或多个)通信设备1026和数据存储单元1019,例如盘驱动器或者其他大容量存储设备,它们在一个实施例中可包括代码1030。图示的代码1030可实现已经论述过的方法50(图3)的一个或多个方面。另外,音频i/o1024可耦合到第二总线1020并且电池1010可向计算系统1000供应电力。47.注意设想了其他实施例。例如,取代图7的点到点体系结构,系统可实现多点分支总线或者另外的这种通信拓扑。另外,图7的元件可改为利用比图7中所示更多或更少的集成芯片来划分。48.附加注释和示例:49.示例1包括一种性能增强的计算系统,包括插座,与所述插座耦合的处理器,以及与所述处理器耦合的存储器,所述存储器包括一组可执行程序指令,所述指令当被所述处理器执行时,使得所述处理器识别非统一存储器访问(numa)节点,在所述numa节点内定义第一虚拟邻近域,并且在所述numa节点内定义第二虚拟邻近域,其中所述第一虚拟邻近域和所述第二虚拟邻近域是经由一个或多个操作系统(os)接口表来定义的。50.示例2包括如示例1所述的计算系统,其中所述一个或多个os接口表是从由静态资源亲和表和系统定位信息表组成的群组中选择的。51.示例3包括如示例1所述的计算系统,其中所述numa节点专用于所述插座。52.示例4包括如示例3所述的计算系统,其中所述插座具有初始交织配置,并且其中为了定义所述第一虚拟邻近域和所述第二虚拟邻近域,所述指令当被执行时使得所述处理器维持所述初始交织配置。53.示例5包括如示例3所述的计算系统,其中所述插座具有初始缓存分组,并且其中为了定义所述第一虚拟邻近域和所述第二虚拟邻近域,所述指令当被执行时使得所述处理器维持所述初始缓存分组。54.示例6包括如示例1至5的任何一项所述的计算系统,其中所述指令当被执行时还使得所述处理器创建处理器的第一群组,将所述处理器的第一群组与所述第一虚拟邻近域相关联,创建处理器的第二群组,并且将所述处理器的第二群组与所述第二虚拟邻近域相关联。55.示例7包括一种半导体装置,其包括一个或多个衬底,以及与所述一个或多个衬底耦合的逻辑,其中所述逻辑至少部分实现在可配置逻辑或者固定功能硬件逻辑的一个或多个中,与所述一个或多个衬底耦合的逻辑用于识别非统一存储器访问(numa)节点,在所述numa节点内定义第一虚拟邻近域,并且在所述numa节点内定义第二虚拟邻近域,其中所述第一虚拟邻近域和所述第二虚拟邻近域是经由一个或多个操作系统(os)接口表来定义的。56.示例8包括如示例7所述的装置,其中所述一个或多个os接口表是从由静态资源亲和表和系统定位信息表组成的群组中选择的。57.示例9包括如示例7所述的装置,其中所述numa节点专用于物理插座。58.示例10包括如示例9所述的装置,其中所述物理插座具有初始交织配置,并且其中为了定义所述第一虚拟邻近域和所述第二虚拟邻近域,与所述一个或多个衬底耦合的所述逻辑用于维持所述初始交织配置。59.示例11包括如示例9所述的装置,其中所述物理插座具有初始缓存分组,并且其中为了定义所述第一虚拟邻近域和所述第二虚拟邻近域,与所述一个或多个衬底耦合的所述逻辑用于维持所述初始缓存分组。60.示例12包括如示例7至11的任何一项所述的装置,其中与所述一个或多个衬底耦合的所述逻辑用于创建处理器的第一群组,将所述处理器的第一群组与所述第一虚拟邻近域相关联,创建处理器的第二群组,并且将所述处理器的第二群组与所述第二虚拟邻近域相关联。61.示例13包括如示例7至11的任何一项所述的装置,其中与所述一个或多个衬底耦合的所述逻辑包括定位在所述一个或多个衬底内的晶体管沟道区域。62.示例14包括至少一个计算机可读存储介质,其包括一组可执行程序指令,所述指令当被计算系统执行时,使得所述计算系统识别非统一存储器访问(numa)节点,在所述numa节点内定义第一虚拟邻近域,并且在所述numa节点内定义第二虚拟邻近域,其中所述第一虚拟邻近域和所述第二虚拟邻近域是经由一个或多个操作系统(os)接口表来定义的。63.示例15包括如示例14所述的至少一个计算机可读存储介质,其中所述一个或多个os接口表是从由静态资源亲和表和系统定位信息表组成的群组中选择的。64.示例16包括如示例14所述的至少一个计算机可读存储介质,其中所述numa节点专用于物理插座。65.示例17包括如示例16所述的至少一个计算机可读存储介质,其中所述物理插座具有初始交织配置,并且其中为了定义所述第一虚拟邻近域和所述第二虚拟邻近域,所述指令当被执行时使得所述计算系统维持所述初始交织配置。66.示例18包括如示例16所述的至少一个计算机可读存储介质,其中所述物理插座具有初始缓存分组,并且其中为了定义所述第一虚拟邻近域和所述第二虚拟邻近域,所述指令当被执行时使得所述计算系统维持所述初始缓存分组。67.示例19包括如示例14所述的至少一个计算机可读存储介质,其中所述指令当被执行时还使得所述计算系统识别第二numa节点,其中所述第二numa节点专用于所述物理插座,并且在所述第二numa节点内定义两个或更多个虚拟邻近域,其中所述两个或更多个虚拟邻近域是经由所述一个或多个os接口表来定义的。68.示例20包括如示例14至19的任何一项所述的至少一个计算机可读存储介质,其中所述指令当被执行时还使得所述计算系统创建处理器的第一群组,将所述处理器的第一群组与所述第一虚拟邻近域相关联,创建处理器的第二群组,并且将所述处理器的第二群组与所述第二虚拟邻近域相关联。69.示例21包括如示例14至20的任何一项所述的至少一个计算机可读存储介质,其中所述指令当被执行时还使得所述计算系统经由所述一个或多个os接口表在所述numa节点内定义多于两个虚拟邻近域。70.示例22包括一种操作性能增强的计算系统的方法,所述方法包括识别非统一存储器访问(numa)节点,在所述numa节点内定义第一虚拟邻近域,并且在所述numa节点内定义第二虚拟邻近域,其中所述第一虚拟邻近域和所述第二虚拟邻近域是经由一个或多个操作系统(os)接口表来定义的。71.示例23包括如示例22所述的方法,其中所述一个或多个os接口表是从由静态资源亲和表和系统定位信息表组成的群组中选择的。72.示例24包括如示例22所述的方法,其中所述numa节点专用于物理插座,其中所述物理插座具有初始交织配置,其中定义所述第一虚拟邻近域和所述第二虚拟邻近域包括维持所述初始交织配置,其中所述物理插座具有初始缓存分组,并且其中定义所述第一虚拟邻近域和所述第二虚拟邻近域包括维持所述初始缓存分组。73.示例25包括如示例22至24的任何一项所述的方法,还包括创建处理器的第一群组,将所述处理器的第一群组与所述第一虚拟邻近域相关联,创建处理器的第二群组,并且将所述处理器的第二群组与所述第二虚拟邻近域相关联。74.示例26包括用于执行如示例22至25的任何一项所述的方法的装置。75.本文描述的技术因此提供了系统固件acpi表的新颖使用来描述特定物理numa实现中的存储器。acpi表,例如slit和srat,可被利用于平台和cpu特征。例如,邻近域可被用于slit和srat表中来模拟多处理器系统上的单个物理numa节点内的多个虚拟numa节点。76.实施例适用于与所有类型的半导体集成电路(“ic”)芯片一起使用。这些ic芯片的示例包括但不限于处理器、控制器、芯片集组件、可编程逻辑阵列(programmablelogicarray,pla)、存储器芯片、网络芯片,片上系统(systemsonchip,soc)、ssd/nand控制器asic,等等。此外,在一些附图中,用线条来表示信号导线。某些可能是不同的,以指示更多的构成信号路径,具有数字标注,以指示构成信号路径的数目,和/或在一端或多端具有箭头,以指示主要信息流方向。然而,这不应当以限制方式来解释。更确切地说,这种添加的细节可联系一个或多个示范性实施例使用来促进对电路的更容易理解。任何表示的信号线,无论是否具有附加信息,都可实际上包括一个或多个信号,这一个或多个信号可在多个方向上行进并且可利用任何适当类型的信号方案来实现,例如利用差动对实现的数字或模拟线路、光纤线路和/或单端线路。77.可能给出了示例大小/型号/值/范围,虽然实施例不限于此。随着制造技术(例如,光刻术)随着时间流逝而成熟,预期能够制造具有更小大小的器件。此外,为了图示和论述的简单,并且为了不模糊实施例的某些方面,在附图内可能示出或不示出到ic芯片和其他组件的公知电源/接地连接。另外,可能以框图形式示出布置以避免模糊实施例,并且同时也考虑到了如下事实:关于这种框图布置的实现的具体细节是高度取决于在其内实现实施例的计算系统的,即,这种具体细节应当完全在本领域技术人员的视野内。在阐述具体细节(例如,电路)以便描述示例实施例的情况下,本领域技术人员应当清楚,没有这些具体细节,或者利用这些具体细节的变体,也可实现实施例。从而说明书应当被认为是说明性的,而不是限制性的。78.术语“耦合”在本文中可用于指所涉组件之间的任何类型的关系,无论是直接的还是间接的,并且可应用到电的、机械的、液体的、光的、电磁的、机电的或者其他连接。此外,除非另外指出,否则术语“第一”、“第二”等等在本文中可只用于促进论述,而不带有特定的时间或先后意义。79.就在本技术中和权利要求中使用的而言,由术语“…中的一个或多个”联接的项目的列表可意指列出的术语的任何组合。例如,短语“a、b或c中的一个或多个”可意指a;b;c;a和b;a和c;b和c;或者a、b和c。80.本领域技术人员从前述描述将会明白,实施例的宽广技术可按多种形式实现。因此,虽然已联系其特定示例描述了实施例,但实施例的真实范围不应当限于此,因为本领域技术人员在研习了附图、说明书和所附权利要求后将清楚其他修改。当前第1页12当前第1页12

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。