1.本发明涉及一种像素阵列基板。

背景技术:

2.随着显示科技的发达,人们对显示装置的需求,不再满足于高分辨率、高对比、广视角等光学特性,人们还期待显示装置具有优雅的外观。举例而言,人们期待显示装置的边框窄,甚至无边框。

3.一般而言,显示装置包括设置于显示区的多个像素结构、设置于显示区的下方的数据驱动电路以及设置于显示区的左侧、右侧或左右两侧的栅极驱动电路。为减少显示装置的边框的左右两侧的宽度,可将栅极驱动电路与数据驱动电路均设置于显示区的下侧。当栅极驱动电路设置于显示区的下侧时,在垂直方向上排列的栅极线须通过在水平方向上排列的转接线方能电性连接至栅极驱动电路。然而,转接线的栅极开启脉冲信号会影响还在充电中的其它像素结构的电位,进而造成显示异常(例如:斜向亮线)。因此,如何改善所述显示异常的问题,为当前的超窄边框显示装置所面临的挑战之一。此外,如何提升显示装置的开口率,并使其不易出现气泡问题,又是另一项课题。

技术实现要素:

4.本发明提供一种像素阵列基板,具有高开口率。

5.本发明的像素阵列基板,包括基底及设置于基底上的多个像素结构。每一像素结构包括第一共用电极、薄膜晶体管、导电图案、第一绝缘层、彩色滤光图案、第二绝缘层及像素电极。导电图案电性连接至薄膜晶体管,其中导电图案的第一部设置于第一共用电极上。第一绝缘层设置于导电图案上,且具有与导电图案重叠的开口。彩色滤光图案设置于第一绝缘层上,且具有与导电图案重叠的开口。第二绝缘层设置于彩色滤光图案上,且具有与导电图案重叠的开口。像素电极设置于第二绝缘层上,且通过第一绝缘层的开口及第二绝缘层的开口电性连接至导电图案。在像素阵列基板的俯视图中,导电图案的第一部覆盖第一共用电极的位于彩色滤光图案的开口内的所有边缘。

6.在本发明的一实施例中,上述的每一像素结构还包括第二共用电极。第二共用电极与第一共用电极分离。导电图案的第二部设置于第二共用电极上。在像素阵列基板的俯视图中,导电图案的第二部覆盖第二共用电极的位于彩色滤光图案的开口内的所有边缘。

7.在本发明的一实施例中,上述的导电图案还具有第三部;在像素阵列基板的俯视图中,导电图案的第三部位于第一共用电极与第二共用电极之间,且第一绝缘层的开口及第二绝缘层的开口位于导电图案的第三部上。

8.在本发明的一实施例中,在上述的像素阵列基板的俯视图中,第一绝缘层的开口及第二绝缘层的开口位于第一共用电极与第二共用电极之间且不重叠于第一共用电极与第二共用电极。

9.在本发明的一实施例中,上述的每一像素结构还包括第三共用电极。第三共用电

极与第一共用电极及第二共用电极分离。导电图案的第四部设置于第三共用电极上。在像素阵列基板的俯视图中,导电图案的第四部覆盖第三共用电极的位于彩色滤光图案的开口内的所有边缘。

10.在本发明的一实施例中,上述的导电图案的第一部的边缘与彩色滤光图案的开口的边缘实质上切齐。

11.在本发明的一实施例中,上述的导电图案还具有第五部;在像素阵列基板的俯视图中,导电图案的第五部与第一共用电极重叠且位于彩色滤光图案的开口外。

12.在本发明的一实施例中,上述的薄膜晶体管具有栅极,与第一共用电极分离;导电图案的第二部设置于栅极上;在像素阵列基板的俯视图中,导电图案的第二部覆盖栅极的位于彩色滤光图案的开口内的所有边缘。

13.在本发明的一实施例中,上述的导电图案还具有第三部;在像素阵列基板的俯视图中,导电图案的第三部位于第一共用电极与栅极之间,且第一绝缘层的开口及第二绝缘层的开口位于导电图案的第三部上。

14.在本发明的一实施例中,在上述的像素阵列基板的俯视图中,第一绝缘层的开口及第二绝缘层的开口位于第一共用电极与栅极之间,且第一绝缘层的开口及第二绝缘层的开口不重叠于第一共用电极与栅极。

15.在本发明的一实施例中,上述的多个像素结构排成多个像素行,且多个像素行在第一方向上排列。像素阵列基板还包括多条扫描线、多条数据线及多条转接线。多条扫描线在第二方向上排列,且电性连接至多个像素结构,其中第一方向与第二方向交错。多条数据线在第一方向上排列,且电性连接至多个像素行。多条转接线在第一方向上排列,且电性连接至多条扫描线。多条扫描线包括在第二方向上按序排列的第x-n条扫描线至第x条扫描线,x为大于或等于2的正整数,n为正整数且小于x,第x条扫描线的栅极驱动信号的开启时间与第x-n条的栅极驱动信号的关闭时间于时序上重叠。多条转接线包括第x-n转接线及第x转接线,分别电性连接至第x-n条扫描线及第x条扫描线。多个像素行包括在第一方向上按序排列第k-1个像素行、第k个像素行及第k 1个像素行,k为大于或等于2的正整数。多条数据线包括第k-1数据线、第k数据线及第k 1数据线,分别电性连接至第k-1个像素行、第k个像素行及第k 1个像素行。在像素阵列基板的俯视图中,第x-n转接线设置于第k-1数据线与第k数据线之间,且第x转接线设置于第k数据线与第k 1数据线之间。

16.在本发明的一实施例中,上述的多条扫描线包括在第二方向上按序排列的第x-n条扫描线至第x n条扫描线。第x条扫描线的栅极脉冲信号的结束时间与第x n条扫描线的栅极脉冲信号的开始时间于时序上重叠。多条转接线还包括第x n转接线,电性连接至第x n条扫描线。多个像素行还包括第k 2个像素行。第k-1个像素行、第k个像素行、第k 1个像素行及第k 2个像素行在第一方向上按序排列。多条数据线还包括第k 2数据线,电性连接至第k 2个像素行。在像素阵列基板的俯视图中,第x n转接线设置于第k 1数据线与第k 2数据线之间。

17.在本发明的一实施例中,上述的多个像素行还包括第k 2个像素行。第k-1个像素行、第k个像素行、第k 1个像素行及第k 2个像素行在第一方向上按序排列。多条数据线还包括第k 2数据线,电性连接至第k 2个像素行。像素阵列基板还包括第一共用线。在像素阵列基板的俯视图中,第一共用线设置于第k 1数据线及第k 2数据线之间。

18.在本发明的一实施例中,上述的多个像素行还包括第k 2个像素行。第k-1个像素行、第k个像素行、第k 1个像素行及第k 2个像素行在第一方向上按序排列。多条数据线还包括第k 2数据线,电性连接至第k 2个像素行。多条扫描线包括第m条扫描线。多条转接线还包括第m转接线,电性连接至第m条扫描线。m为大于2的正整数,且|x-m|不等于n。在像素阵列基板的俯视图中,第m转接线设置于第k 1数据线与第k 2数据线之间。

19.在本发明的一实施例中,上述的多条扫描线包括在第二方向上按序排列的第y-n条扫描线至第y条扫描线,y为大于或等于2的正整数,n为正整数且小于y,第y条扫描线的栅极脉冲信号的开始时间与第y-n条扫描线的栅极脉冲信号的结束时间于时序上重叠。多条转接线包括第y-n转接线及第y转接线,分别电性连接至第y-n条扫描线及第y条扫描线。多个像素行包括在第一方向上按序排列的第q-1个像素行、第q个像素行及第q 1个像素行,且q为大于或等于2的正整数。多条数据线包括第q-1数据线、第q数据线及第q 1数据线,分别电性连接至第q-1个像素行、第q个像素行及第q 1个像素行。在像素阵列基板的俯视图中,第y转接线设置于第q-1数据线与第q数据线之间,且第y-n转接线设置于第q数据线与第q 1数据线之间。

20.在本发明的一实施例中,上述的多个像素行还包括第q 2个像素行。第q-1个像素行、第q个像素行、第q 1个像素行及第q 2个像素行在第一方向上按序排列。多条数据线还包括第q 2数据线,电性连接至第q 2个像素行。像素阵列基板还包括第二共用线。在像素阵列基板的俯视图中,第二共用线设置于第q 1数据线及第q 2数据线之间。

21.在本发明的一实施例中,上述的多个像素行还包括第q 2个像素行。第q-1个像素行、第q个像素行、第q 1个像素行及第q 2个像素行在第一方向上按序排列。多条数据线还包括第q 2数据线,电性连接至第q 2个像素行。多条扫描线包括第p条扫描线。多条转接线还包括第p转接线,电性连接至第p条扫描线。p为大于2的正整数,且|y-p|不等于n。在像素阵列基板的俯视图中,第p转接线设置于第q 1数据线与第q 2数据线之间。

22.在本发明的一实施例中,上述的n=4。

23.在本发明的一实施例中,上述的n=8。

24.在本发明的一实施例中,上述的多条扫描线的一者属于第一导电层。多条转接线的一者属于第二导电层。像素阵列基板还包括一绝缘层,设置于第一导电层与第二导电层之间,且具有一接触窗。多条扫描线的一者通过绝缘层的接触窗电性连接至多条转接线的一者。

附图说明

25.图1为本发明一实施例的像素阵列基板100的一处的俯视示意图。

26.图2示出图1的第x-n条扫描线hgx-n~第x n条扫描线hgx n的多个栅极脉冲信号s

hgx-n

~s

hgx n

。

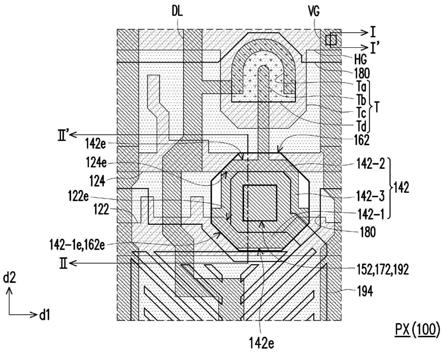

27.图3为本发明一实施例的像素阵列基板100的像素结构px的布局(layout)的俯视示意图。

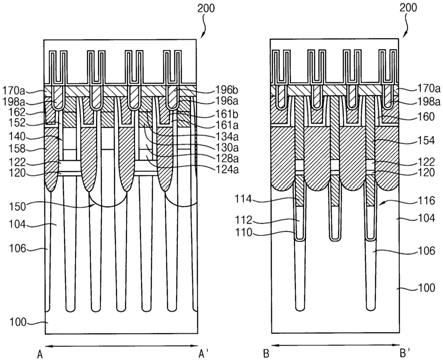

28.图4为本发明一实施例的像素阵列基板100的剖面示意图。

29.图5为本发明一实施例的像素阵列基板100的俯视示意图。

30.图6示出本发明一实施例的第1条扫描线hg1~第18条扫描线hg18的多个栅极脉冲

信号s

hg1

~s

hg18

。

31.图7为本发明一实施例的像素阵列基板100的一处的俯视示意图。

32.图8示出图7的第x-n条扫描线hgx-n~第x n条扫描线hgx n的多个栅极脉冲信号s

hgx-n

~s

hgx n

。

33.图9为本发明一实施例的像素阵列基板100的一处的俯视示意图。

34.图10示出图9的第x-n条扫描线hgx-n~第x n条扫描线hgx n的多个栅极脉冲信号s

hgx-n

~s

hgx n

。

35.图11为本发明一实施例的像素阵列基板100的一处的俯视示意图。

36.图12示出图11的第y-n条扫描线hgy-n~第y条扫描线hgy的多个栅极脉冲信号s

hgy-n

~s

hgy

。

37.图13为本发明一实施例的像素阵列基板100的一处的俯视示意图。

38.图14示出图13的第y-n条扫描线hgy-n~第y条扫描线hgy的多个栅极脉冲信号s

hgy-n

~s

hgy

。

39.图15为本发明一实施例的像素阵列基板100a的一处的俯视示意图。

40.图16示出图15的第1条扫描线hg1~第9条扫描线hg9的多个栅极脉冲信号s

hg1

~s

hg9

。

41.图17为本发明一实施例的像素阵列基板100的像素结构px的剖面示意图。

42.图18为本发明一实施例的像素阵列基板100b的像素结构px的布局(layout)的俯视示意图。

43.图19为本发明一实施例的像素阵列基板100b的像素结构px的剖面示意图。

44.图20为本发明一实施例的像素阵列基板100c的像素结构px的布局(layout)的俯视示意图。

45.图21为本发明一实施例的像素阵列基板100c的像素结构px的剖面示意图。

46.图22为本发明一实施例的像素阵列基板100d的像素结构px的布局(layout)的俯视示意图。

47.图23为本发明一实施例的像素阵列基板100d的像素结构px的剖面示意图。

48.附图标记说明:

49.100、100a、100b、100c、100d:像素阵列基板

50.110:基底

51.122:第一共用电极

52.122e、124e、126e、142e、142-1e、162e、tcs:边缘

53.124:第二共用电极

54.126:第三共用电极

55.130:绝缘层

56.132:接触窗

57.142:导电图案

58.142-1:第一部

59.142-2:第二部

60.142-3:第三部

61.142-4:第四部

62.142-5:第五部

63.150:第一绝缘层

64.152、172、162、192:开口

65.160:彩色滤光图案

66.164:侧壁

67.170:第二绝缘层

68.180:透明导电层

69.190:第三绝缘层

70.194:像素电极

71.a:区域

72.dl、dlk-1、dlk、dlk 1、dlk 2、dlq-1、dlq、dlq 1、dlq 2、dl1~dl23:数据线

73.d1:第一方向

74.d2:第二方向

75.hg、hgm、hgp、hgx-n~hgx n、hgy-n~hgy、hg1~hg18:扫描线

76.px:像素结构

77.r、rk-1、rk、rk 1、rk 2、rq-1、rq、rq 1、rq 2、r1~r23:像素行

78.s

hgx-n

~s

hgx n

、s

hgy-n

~s

hgy

、s

hg1

~s

hg18

、s

vgx-n

、s

vgx

、s

vgx n

、s

vg1

~s

vg18

:栅极脉冲信号

79.t:薄膜晶体管

80.ta:源极

81.tb:漏极

82.tc:栅极

83.td:半导体图案

84.tp:脉冲时间长度

85.t:时间延迟的时间长度

86.tonx、tonx n、tony、ton1、ton3、ton5、ton7、ton9、ton11、ton13、ton14、ton15、ton16、ton17、ton18:开始时间

87.toffx-n、toffx、toffy-n、toff1、toff3、toff5、toff6、toff7、toff8、toff9、toff10:结束时间

88.vg、vgp、vgm、vgx-n、vgx、vgx n、vgy-n、vgy、vg1~vg18:转接线

89.vga:至少一部分

90.vgh:高电位

91.vgl:低电位

92.vss1、vss1a、vss1b、vss1c、vss1d:第一共用线

93.vss2:第二共用线

94.i-i’、ii-ii’、iii-iii’、iv-iv’、v-v’:剖线

具体实施方式

95.现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只

要有可能,相同元件符号在附图和描述中用来表示相同或相似部分。

96.应当理解,当诸如层、膜、区域或基板的元件被称为在另一元件“上”或“连接到”另一元件时,其可以直接在另一元件上或与另一元件连接,或者中间元件可以也存在。相反,当元件被称为“直接在另一元件上”或“直接连接到”另一元件时,不存在中间元件。如本文所使用的,“连接”可以指物理及/或电性连接。再者,“电性连接”或“耦合”可以是二元件间存在其它元件。

97.本文使用的“约”、“近似”、或“实质上”包括所述值和在本领域普通技术人员确定的特定值的可接受的偏差范围内的平均值,考虑到所讨论的测量和与测量相关的误差的特定数量(即,测量系统的限制)。例如,“约”可以表示在所述值的一个或多个标准偏差内,或

±

30%、

±

20%、

±

10%、

±

5%内。再者,本文使用的“约”、“近似”或“实质上”可依光学性质、蚀刻性质或其它性质,来选择较可接受的偏差范围或标准偏差,而可不用一个标准偏差适用全部性质。

98.除非另有定义,本文使用的所有术语(包括技术和科学术语)具有与本发明所属领域的普通技术人员通常理解的相同的含义。将进一步理解的是,诸如在通常使用的字典中定义的那些术语应当被解释为具有与它们在相关技术和本发明的上下文中的含义一致的含义,并且将不被解释为理想化的或过度正式的意义,除非本文中明确地这样定义。

99.图1为本发明一实施例的像素阵列基板100的一处的俯视示意图。

100.图2示出图1的第x-n条扫描线hgx-n~第x n条扫描线hgx n的多个栅极脉冲信号s

hgx-n

~s

hgx n

。

101.图3为本发明一实施例的像素阵列基板100的像素结构px的布局(layout)的俯视示意图。图3对应图1的区域a。

102.图4为本发明一实施例的像素阵列基板100的剖面示意图。图4对应图3的剖线i-i’。

103.请参照图1及图4,像素阵列基板100包括基底110。举例而言,在本实施例中,基底110的材质可为玻璃。然而,本发明不限于此,在其它实施例中,基底110的材质也可为石英、有机聚合物、不透光/反射材料(例如:晶圆、陶瓷等)、或是其它可适用的材料。

104.请参照图1,像素阵列基板100还包括多个像素结构px,设置于基底110上。多个像素结构px排成多个像素行r。多个像素行r在第一方向d1上排列。

105.请参照图1及图3,每一像素结构px包括一薄膜晶体管t及一像素电极194。薄膜晶体管t具有源极ta、漏极tb、栅极tc及半导体图案td。绝缘层130(绘于图4)夹设于栅极tc与半导体图案td之间。绝缘层130又可称闸绝缘层。源极ta和漏极tb分别与半导体图案td的不同两区电性连接,且像素电极194电性连接至漏极tb。

106.举例而言,在本实施例中,薄膜晶体管t的栅极tc可属于第一导电层,薄膜晶体管t的源极ta与漏极tb可属于第二导电层,但本发明不以此为限。

107.在本实施例中,所述第一导电层可为第一金属层;也就是说,所述第一导电层的材质可为金属。然而,本发明不限于此,在其他实施例中,所述第一导电层的材质可为其他导电材料,例如:合金、金属材料的氮化物、金属材料的氧化物、金属材料的氮氧化物、或是金属材料与其它导电材料的堆叠层。

108.在本实施例中,所述第二导电层可为第二金属层;也就是说,所述第二导电层的材

质可为金属。然而,本发明不限于此,在其他实施例中,所述第二导电层的材质也可为其他导电材料,例如:合金、金属材料的氮化物、金属材料的氧化物、金属材料的氮氧化物、或是金属材料与其它导电材料的堆叠层。

109.请参照图1及图3,像素阵列基板100还包括在第二方向d2上排列的多条扫描线hg,其中第一方向d1与第二方向d2交错。举例而言,在本实施例中,第一方向d1与第二方向d2可垂直,但本发明不以此为限。多条扫描线hg电性连接至多个像素结构px。详细而言,多条扫描线hg电性连接至多个像素结构px的多个薄膜晶体管t的多个栅极tc。在本实施例中,扫描线hg可属于所述第一导电层,但本发明不以此为限。

110.请参照图1及图3,像素阵列基板100还包括多条数据线dl,在第一方向d1上排列,且电性连接至多个像素行r。详细而言,在本实施例中,多条数据线dl电性连接至多个像素行r的多个薄膜晶体管t的多个源极ta,且同一像素行r的多个像素结构px的多个源极ta电性连接至同一条数据线dl。在本实施例中,数据线dl可属于所述第二导电层,但本发明不以此为限。

111.请参照图1及图3,像素阵列基板100还包括多条转接线vg,在第一方向d1上排列,且电性连接至多条扫描线hg。请参照图1、图3及图4,举例而言,在本实施例中,扫描线hg属于所述第一导电层,转接线vg的至少一部分vga(标示于图4)属于所述第二导电层;绝缘层130设置于所述第一导电层与所述第二导电层之间,且具有一接触窗132(标示于图4);转接线vg的至少一部分vga是通过绝缘层130的接触窗132电性连接至扫描线hg。

112.请参照图1,多条扫描线hg包括在第二方向d2上按序排列的第x-n条扫描线hgx-n至第x n条扫描线hgx n,其中x为大于或等于2的正整数,n为正整数且小于x。

113.请参照图1及图2,第x-n条扫描线hgx-n至第x n条扫描线hgx n分别具有栅极脉冲信号s

hgx-n

至栅极脉冲信号s

hgx n

。详细而言,第x-n条扫描线hgx-n具有栅极脉冲信号s

hgx-n

,第x-n 1条扫描线hgx-n 1具有栅极脉冲信号s

hgx-n 1

,第x-n 2条扫描线hgx-n 2具有栅极脉冲信号s

hgx-n 2

,

…

,第x条扫描线hgx具有栅极脉冲信号s

hgx

,第x 1条扫描线hgx 1具有栅极脉冲信号s

hgx 1

,第x 2条扫描线hgx 2具有栅极脉冲信号s

hgx 2

,

…

,第x n条扫描线hgx n具有栅极脉冲信号s

hgx n

。

114.请参照图1及图2,在本实施例中,以一时间延迟按序开启第x-n条扫描线hgx-n至第x n条扫描线hgx n,其中时间延迟的时间长度为t(绘于图2),栅极脉冲信号s

hgx-n

至栅极脉冲信号s

hgx n

的每一者的脉冲时间长度为tp(绘于图2),且n=tp/t。第x条扫描线hgx的栅极脉冲信号s

hgx

的开始时间tonx与第x-n条扫描线hgx-n的栅极脉冲信号s

hgx-n

的结束时间toffx-n于时序上重叠。也就是说,第x条扫描线hgx的栅极脉冲信号s

hgx

由低电位vgl上升至高电位vgh的一时段与第x-n条扫描线hgx-n的栅极脉冲信号s

hgx-n

由高电位vgh下降至低电位vgl的一时段于时序上至少部分重叠。第x条扫描线hgx的栅极脉冲信号s

hgx

的结束时间toffx与第x n条扫描线hgx n的栅极脉冲信号s

hgx n

的开始时间tonx n于时序上重叠。也就是说,第x条扫描线hgx的栅极脉冲信号s

hgx

由高电位vgh下降至低电位vgl的一时段与第x n条扫描线hgx n的栅极脉冲信号s

hgx n

由低电位vgl上升至高电位vgh的一时段于时序上至少部分重叠。

115.请参照图1,多条转接线vg包括第x-n转接线vgx-n、第x转接线vgx及第x n转接线vgx n,分别电性连接至第x-n条扫描线hgx-n、第x条扫描线hgx及第x n条扫描线hgx n。请

参照图1及图2,第x-n转接线vgx-n、第x转接线vgx及第x n转接线vgx n分别具有栅极脉冲信号s

vgx-n

、栅极脉冲信号s

vgx

及栅极脉冲信号s

vgx n

,其中第x-n转接线vgx-n的栅极脉冲信号s

vgx-n

、第x转接线vgx的栅极脉冲信号s

vgx

及第x n转接线vgx n的栅极脉冲信号s

vgx n

分别与第x-n条扫描线hgx-n的栅极脉冲信号s

hgx-n

、第x条扫描线hgx的栅极脉冲信号s

hgx

及第x n条扫描线hgx n的栅极脉冲信号s

hgx n

相同。

116.请参照图1,多个像素行r包括在第一方向d1上按序排列的第k-1个像素行rk-1、第k个像素行rk及第k 1个像素行rk 1,k为大于或等于2的正整数;多条数据线dl包括第k-1数据线dlk-1、第k数据线dlk及第k 1数据线dlk 1,分别电性连接至第k-1个像素行rk-1、第k个像素行rk及第k 1个像素行rk 1。

117.请参照图1,值得注意的是,在像素阵列基板100的俯视图中,第x-n转接线vgx-n设置于第k-1数据线dlk-1与第k数据线dlk之间,且第x转接线vgx设置于第k数据线dlk与第k 1数据线dlk 1之间。换言之,第x-n转接线vgx-n与第x转接线vgx相邻于同一第k数据线dlk,且分别位于同一第k数据线dlk的左右两侧。请参照图1及图2,特别是,由于第x转接线vgx的栅极脉冲信号s

vgx

的开始时间tonx与第x-n条转接线vgx-n的栅极脉冲信号s

vgx-n

的结束时间toffx-n于时序上重叠,因此,第x-n转接线vgx-n与第k数据线dlk之间的电容耦合效应和第x转接线vgx与第k数据线dlk之间的电容耦合效应可相抵销,使得位于第k个像素行rk且电性连接至第x条扫描线hgx的像素结构px的像素电极194(绘于图3)的电位不易因设置于其左右两旁的多条转接线vg而过度偏离于理想值。因此,位于第k个像素行rk且电性连接至第x条扫描线hgx的像素结构px不易出现异常的亮度(例如:过亮),进而使现有技术所述的斜向亮线的问题获得改善。以下配合其它附图具体举例说明。

118.图5为本发明一实施例的像素阵列基板100的俯视示意图。

119.图6示出本发明一实施例的第1条扫描线hg1~第18条扫描线hg18的多个栅极脉冲信号s

hg1

~s

hg18

。

120.请参照图5,多个像素结构px设置于基底110上,且排成第1个像素行r1至第23个像素行r23,其中第1个像素行r1至第23个像素行r23在第一方向d1上排列。多条扫描线hg包括第1条扫描线hg1至第18条扫描线hg18,在第二方向d2上按序排列。多条数据线dl包括第1数据线dl1至第23数据线dl23,分别电性连接至第1个像素行r1至第23个像素行r23。

121.请参照图5及图6,第1条扫描线hg1至第18条扫描线hg18分别具有栅极脉冲信号s

hg1

至栅极脉冲信号s

hg18

。在本实施例中,以一时间延迟按序开启第1条扫描线hg1至第18条扫描线hg18,其中时间延迟的时间长度为t(绘于图6),栅极脉冲信号s

hg1

至栅极脉冲信号s

hg18

的每一者的脉冲时间长度为tp(绘于图6),n=tp/t,n例如为8,但本发明不以此为限。

122.请参照图5,多条转接线vg包括第1转接线vg1至第18转接线vg18,分别电性连接至第1条扫描线hg1至第18条扫描线hg18。请参照图5及图6,第1转接线vg1至第18转接线vg18分别具有栅极脉冲信号s

vg1

至栅极脉冲信号s

vg18

,其中第1转接线vg1的栅极脉冲信号s

vg1

至第18转接线vg18的栅极脉冲信号s

vg18

分别与第1条扫描线hg1的栅极脉冲信号s

hg1

至第18扫描线hg18的栅极脉冲信号s

hg18

相同。

123.请再参照图1及图2,多条扫描线hg包括在第二方向d2上按序排列的第x-n条扫描线hgx-n至第x n条扫描线hgx n,x为大于或等于2的正整数,n为正整数且小于x;第x条扫描线hgx的栅极脉冲信号s

hgx

的开始时间tonx与第x-n条扫描线hg的栅极脉冲信号s

hgx-n

的结束

时间toffx-n于时序上重叠;第x条扫描线hg的栅极脉冲信号s

hgx

的结束时间toffx与第x n条扫描线hg的栅极脉冲信号s

hgx n

的开始时间tonx n于时序上重叠;多条转接线vg包括第x-n转接线vgx-n、第x转接线vgx及第x n转接线vgx n,分别电性连接至第x-n条扫描线hgx-n、第x条扫描线hgx及第x n条扫描线hgx n;多个像素行r包括在第一方向d1上按序排列的第k-1个像素行rk-1、第k个像素行rk及第k 1个像素行rk 1,k为大于或等于2的正整数;多条数据线dl包括第k-1数据线dlk-1、第k数据线dlk及第k 1数据线dlk 1,分别电性连接至第k-1个像素行rk-1、第k个像素行rk及第k 1个像素行rk 1。在像素阵列基板100的俯视图中,第x-n转接线vgx-n设置于第k-1数据线dlk-1与第k数据线dlk之间,且第x转接线vgx设置于第k数据线dlk与第k 1数据线dlk 1之间;以下以图5及图6为例说明。

124.请参照图5及图6,在本实施例的像素阵列基板100的一处中,可将上一段所述的n、x、k分别视为8、9、2(即,n=8,x=9,k=2)。请参照图5及图6,在本实施例的像素阵列基板100的一处中,多条扫描线hg包括在第二方向d2上按序排列的第1条扫描线hg1至第17条扫描线hg17;第9条扫描线hg9的栅极脉冲信号s

hg9

的开始时间ton9与第1条扫描线hg1的栅极脉冲信号s

hg1

的结束时间toff1于时序上重叠;第9条扫描线hg9的栅极脉冲信号s

hg9

的结束时间toff9与第17条扫描线hg17的栅极脉冲信号s

hg17

的开始时间ton17于时序上重叠;多条转接线vg包括第1转接线vg1、第9转接线vg9及第17转接线vg17,分别电性连接至第1条扫描线hg1、第9条扫描线hg9及第17条扫描线hg17;多个像素行r包括在第一方向d1上按序排列的第1个像素行r1、第2个像素行r2及第3个像素行r3;多条数据线dl包括第1数据线dl1、第2数据线dl2及第3数据线dl3,分别电性连接至第1个像素行r1、第2个像素行r2及第3个像素行r3。在像素阵列基板100的俯视图中,第1转接线vg1设置于第1数据线dl1与第2数据线dl2之间,且第9转接线vg设置于第2数据线dl2与第3数据线dl3之间。

125.请参照图5,换言之,第1转接线vg1与第9转接线vg9相邻于第2数据线dl2且分别位于第2数据线dl2的左右两侧。请参照图5及图6,特别是,由于第9转接线vg9的栅极脉冲信号s

vg9

的开始时间ton9与第1条转接线vg1的栅极脉冲信号s

vg1

的结束时间toff1于时序上重叠,因此第1转接线vg1与第2数据线dl2之间的电容耦合效应和第9转接线vg9与第2数据线dl2之间的电容耦合效应可相抵销,使得位于第2个像素行r2且电性连接至第9条扫描线hg9的像素结构px的像素电极194(绘于图3)的电位不易因设置于其左右两旁的多条转接线vg而过度偏离于理想值。因此,位于第2个像素行r2且电性连接至第9条扫描线hg9的像素结构px不易出现异常的亮度(例如:偏亮),进而使现有技术中所述的斜向亮线的问题获得改善。

126.请再参照图1及图2,多条扫描线hg包括在第二方向d2上按序排列的第x-n条扫描线hgx-n至第x n条扫描线hgx n,第x条扫描线hgx的栅极脉冲信号s

hgx

的结束时间toffx与第x n条扫描线hgx n的栅极脉冲信号s

hgx n

的开始时间tonx n于时序上重叠;多条转接线vg还包括第x n转接线vgx n,电性连接至第x n条扫描线hgx n;多个像素行r还包括第k 2个像素行rk 2,第k-1个像素行rk-1、第k个像素行rk、第k 1个像素行rk 1及第k 2个像素行rk 2在第一方向d1上按序排列;多条数据线dl还包括第k 2数据线dlk 2,电性连接至第k 2个像素行rk 2;在像素阵列基板100的俯视图中,第x n转接线vgx n设置于第k 1数据线dlk 1与第k 2数据线dlk 2之间;以下以图5及图6为例说明。

127.请参照图5及图6,在本实施例的像素阵列基板100的一处中,可将上一段所述的n、x、k分别视为8、9、2(即,n=8,x=9,k=2)。请参照图5及图6,在本实施例的像素阵列基板

100的一处中,多条扫描线hg包括在第二方向d2上按序排列的第1条扫描线hg1至第17条扫描线hg17,第9条扫描线hg9的栅极脉冲信号s

hg9

的结束时间toff9与第17条扫描线hg17的栅极脉冲信号s

hg17

的开始时间ton17于时序上重叠;多条转接线vg还包括第17转接线vg17,电性连接至第17条扫描线hg17;多个像素行r还包括第4个像素行r4,第1个像素行r1、第2个像素行r2、第3个像素行r3及第4个像素行r4在第一方向d1上按序排列;多条数据线dl还包括第4数据线dl4,电性连接至第4个像素行r4;在像素阵列基板100的俯视图中,第17转接线vg17设置于第3数据线dl3与第4数据线dl4之间。

128.请参照图5,换言之,第9转接线vg9与第17转接线vg17相邻于第3数据线dl3且分别位于第3数据线dl3的左右两侧。请参照图5及图6,类似地,由于第9条转接线vg9的栅极脉冲信号s

vg9

的结束时间toff9与第17条转接线vg17的栅极脉冲信号s

vg17

的开始时间ton17于时序上重叠,因此第9转接线vg9与第3数据线dl3之间的电容耦合效应和第17转接线vg9与第3数据线dl3之间的电容耦合效应可相抵销,使得位于第3个像素行r3且电性连接至第17条扫描线hg17的像素结构px的像素电极194(绘于图3)的电位不易因设置于其左右两旁的多条转接线vg而过度偏离于理想值。因此,位于第3个像素行r3且电性连接至第17条扫描线hg17的像素结构px不易出现异常的亮度(例如:偏亮),进而使现有技术中所述的斜向亮线的问题获得改善。

129.图7为本发明一实施例的像素阵列基板100的一处的俯视示意图。

130.图8示出图7的第x-n条扫描线hgx-n~第x n条扫描线hgx n的多个栅极脉冲信号s

hgx-n

~s

hgx n

。

131.请参照图7及图8,多条扫描线hg包括在第二方向d2上按序排列的第x-n条扫描线hgx-n至第x条扫描线hgx,x为大于或等于2的正整数,n为正整数且小于x,第x条扫描线hgx的栅极脉冲信号s

hgx

的开始时间tonx与第x-n条扫描线hgx-n的栅极脉冲信号s

hgx-n

的结束时间toffx-n于时序上重叠;多条转接线vg包括第x-n转接线vgx-n及第x转接线vgx,分别电性连接至第x-n条扫描线hgx-n及第x条扫描线hgx;多个像素行r包括在第一方向d1上按序排列的第k-1个像素行rk-1、第k个像素行rk、第k 1个像素行rk 1及第k 2个像素行rk 2,k为大于或等于2的正整数;多条数据线dl包括第k-1数据线dlk-1、第k数据线dlk、第k 1数据线dlk 1及第k 2数据线dlk 2,分别电性连接至第k-1个像素行rk-1、第k个像素行rk、第k 1个像素行rk 1及第k 2个像素行rk 2;像素阵列基板100还包括第一共用线vss1;在像素阵列基板100的俯视图中,第x-n转接线vgx-n设置于第k-1数据线dlk-1与第k数据线dlk之间,第x转接线vgx设置于第k数据线dlk与第k 1数据线dlk 1之间,且第一共用线vss1设置于第k 1数据线dlk 1及第k 2数据线dlk 2之间;以下以图5及图6为例说明。

132.请参照图5及图6,在本实施例的像素阵列基板100的一处中,可将前一段所述的n、x、k分别视为8、17、3(即,n=8,x=17,k=3)。请参照图5及图6,多条扫描线hg包括在第二方向d2上按序排列的第9条扫描线hg9至第17条扫描线hg17,第17条扫描线hg17的栅极脉冲信号s

hg17

的开始时间ton17与第9条扫描线hg9的栅极脉冲信号s

hg9

的结束时间toff9于时序上重叠;多条转接线vg包括第9转接线vg9及第17转接线vg17,分别电性连接至第9条扫描线hg9及第17条扫描线hg17;多个像素行r包括在第一方向d1上按序排列的第2个像素行r2、第3个像素行r3、第4个像素行r4及第5个像素行r5;多条数据线dl包括第2数据线dl2、第3数据线dl3、第4数据线dl4及第5数据线dl5,分别电性连接至第2个像素行r2、第3个像素行r3、第

4个像素行r4及第5个像素行r5;像素阵列基板100还包括第一共用线vss1a;在像素阵列基板100的俯视图中,第9转接线vg9设置于第2数据线dl2与第3数据线dl3之间,第17转接线vg17设置于第3数据线dl3与第4数据线dl4之间,且第一共用线vss1a设置于第4数据线dl4及第5数据线dl5之间。

133.请参照图5及图6,在本实施例的像素阵列基板100的另一处中,也可将前二段所述的n、x、k分别视为8、11、11(即,n=8,x=11,k=11)。请参照图5及图6,多条扫描线hg包括在第二方向d2上按序排列的第3条扫描线hg3至第11条扫描线hg11,第11条扫描线hg11的栅极脉冲信号s

hg11

的开始时间ton11与第3条扫描线hg3的栅极脉冲信号s

hg3

的结束时间toff3于时序上重叠;多条转接线vg包括第3转接线vg3及第11转接线vg11,分别电性连接至第3条扫描线hg3及第11条扫描线hg11;多个像素行r包括在第一方向d1上按序排列的第10个像素行r10、第11个像素行r11、第12个像素行r12及第13个像素行r13;多条数据线dl包括第10数据线dl10、第11数据线dl11、第12数据线dl12及第13数据线dl13,分别电性连接至第10个像素行r10、第11个像素行r11、第12个像素行r12及第13个像素行r13;像素阵列基板100还包括第一共用线vss1b;在像素阵列基板100的俯视图中,第3转接线vg3设置于第10数据线dl10与第11数据线dl11之间,第11转接线vg11设置于第11数据线dl11与第12数据线dl12之间,且第一共用线vss1b设置于第12数据线dl12及第13数据线dl13之间。

134.请参照图5及图6,在本实施例的像素阵列基板100的又一处中,也可将前三段所述的n、x、k分别视为8、18、15(即,n=8,x=18,k=15)。请参照图5及图6,多条扫描线hg包括在第二方向d2上按序排列的第10条扫描线hg10至第18条扫描线hg18,第18条扫描线hg18的栅极脉冲信号s

hg18

的开始时间ton18与第10条扫描线hg10的栅极脉冲信号s

hg10

的结束时间toff10于时序上重叠;多条转接线vg包括第10转接线vg10及第18转接线vg18,分别电性连接至第10条扫描线hg10及第18条扫描线hg18;多个像素行r包括在第一方向d1上按序排列的第14个像素行r14、第15个像素行r15、第16个像素行r16及第17个像素行r17;多条数据线dl包括第14数据线dl14、第15数据线dl15、第16数据线dl16及第17数据线dl17,分别电性连接至第14个像素行r14、第15个像素行r15、第16个像素行r16及第17个像素行r17;像素阵列基板100还包括第一共用线vss1c;在像素阵列基板100的俯视图中,第10转接线vg10设置于第14数据线dl14与第15数据线dl15之间,第18转接线vg18设置于第15数据线dl15与第16数据线dl16之间,且第一共用线vss1c设置于第16数据线dl16及第17数据线dl17之间。

135.请参照图5及图6,在本实施例的像素阵列基板100的又一处中,也可将前四段所述的n、x、k分别视为8、14、18(即,n=8,x=14,k=18)。请参照图5及图6,多条扫描线hg包括在第二方向d2上按序排列的第6条扫描线hg6至第14条扫描线hg14,第14条扫描线hg14的栅极脉冲信号s

hg14

的开始时间ton14与第6条扫描线hg6的栅极脉冲信号s

hg6

的结束时间toff6于时序上重叠;多条转接线vg包括第6转接线vg6及第14转接线vg14,分别电性连接至第6条扫描线hg6及第14条扫描线hg14;多个像素行r包括在第一方向d1上按序排列的第17个像素行r17、第18个像素行r18、第19个像素行r19及第20个像素行r20;多条数据线dl包括第17数据线dl17、第18数据线dl18、第19数据线dl19及第20数据线dl20,分别电性连接至第17个像素行r17、第18个像素行r18、第19个像素行r19及第20个像素行r20;像素阵列基板100还包括第一共用线vss1d;在像素阵列基板100的俯视图中,第6转接线vg6设置于第17数据线dl17与第18数据线dl18之间,第14转接线vg14设置于第18数据线dl18与第19数据线dl19之间,

且第一共用线vss1d设置于第19数据线dl19及第20数据线dl20之间。

136.图9为本发明一实施例的像素阵列基板100的一处的俯视示意图。

137.图10示出图9的第x-n条扫描线hgx-n~第x n条扫描线hgx n的多个栅极脉冲信号s

hgx-n

~s

hgx n

。

138.请参照图9及图10,多条扫描线hg包括在第二方向d2上按序排列的第x-n条扫描线hgx-n至第x条扫描线hgx,x为大于或等于2的正整数,n为正整数且小于x,第x条扫描线hgx的栅极脉冲信号s

hgx

的开始时间tonx与第x-n条扫描线hgx-n的栅极脉冲信号s

hgx-n

的结束时间toffx-n于时序上重叠;多条扫描线hg还包括第m条扫描线hgm,m为大于2的正整数,|x-m|不等于n;多条转接线vg包括第x-n转接线vgx-n、第x转接线vgx及第m转接线vgm,分别电性连接至第x-n条扫描线hgx-n、第x条扫描线hgx及第m扫描线hgm;多个像素行r包括在第一方向d1上按序排列的第k-1个像素行rk-1、第k个像素行rk、第k 1个像素行rk 1及第k 2个像素行rk 2,k为大于或等于2的正整数;多条数据线dl包括第k-1数据线dlk-1、第k数据线dlk、第k 1数据线dlk 1及第k 2数据线dlk 2,分别电性连接至第k-1个像素行rk-1、第k个像素行rk、第k 1个像素行rk 1及第k 2个像素行rk 2;在像素阵列基板100的俯视图中,第x-n转接线vgx-n设置于第k-1数据线dlk-1与第k数据线dlk之间,第x转接线vgx设置于第k数据线dlk与第k 1数据线dlk 1之间,第m转接线vgm设置于第k 1数据线dlk 1与第k 2数据线dlk 2之间;以下以图5及图6为例说明。

139.请参照图5及图6,在本实施例的像素阵列基板100的一处中,可将前一段所述的n、x、k、m分别视为8、16、21、4(即,n=8,x=16,k=21,m=4)。请参照图5及图6,多条扫描线hg包括在第二方向d2上按序排列的第8条扫描线hg8至第16条扫描线hg16,第16条扫描线hg16的栅极脉冲信号s

hg16

的开始时间ton16与第8条扫描线hg8的栅极脉冲信号s

hg8

的结束时间toff8于时序上重叠;多条扫描线hg还包括第4条扫描线hg4,4为大于2的正整数,|16-4|不等于8;多条转接线vg包括第8转接线vg8、第16转接线vg16及第4转接线vg4,分别电性连接至第8条扫描线hg8、第16条扫描线hg16及第4扫描线hg4;多个像素行r包括在第一方向d1上按序排列的第20个像素行r20、第21个像素行r21、第22个像素行r22及第23个像素行r23;多条数据线dl包括第20数据线dl20、第21数据线dl21、第22数据线dl22及第23数据线dl23,分别电性连接至第20个像素行r20、第21个像素行r21、第22个像素行r22及第23个像素行r23;在像素阵列基板100的俯视图中,第8转接线vg8设置于第20数据线dl20与第21数据线dl21之间,第16转接线vg16设置于第21数据线dl21与第22数据线dl22之间,第4转接线vg4设置于第22数据线dl22与第23数据线dl23之间。

140.也就是说,在本实施例中,于像素阵列基板100的一处,位于同一数据线dl(例如:第21数据线dl21)左右两侧的多条转接线vg(例如:第8转接线vg8及第16转接线vg16)的栅极脉冲信号(例如:s

vg8

、s

vg16

)的开始时间(例如:ton8、ton16)可相差n个所述时间延迟的时间长度t(例如:8个t);但,在像素阵列基板100的另一处,位于同一数据线dl(例如:第22数据线dl22)左右两侧的多条转接线vg(例如:第16转接线vg16及第4转接线vg4)的栅极脉冲信号(例如:s

vg16

、s

vg4

)的开始时间(例如:ton16、ton4)可不相差n个t(例如:相差12个t)。

141.图11为本发明一实施例的像素阵列基板100的一处的俯视示意图。

142.图12示出图11的第y-n条扫描线hgy-n~第y条扫描线hgy的多个栅极脉冲信号s

hgy-n

~s

hgy

。

143.请参照图11,多条扫描线hg包括在第二方向d2上按序排列的第y-n条扫描线hgy-n至第y条扫描线hgy,y为大于或等于2的正整数,n为正整数且小于y。

144.请参照图11及图12,第y-n条扫描线hgy-n至第y条扫描线hgy分别具有栅极脉冲信号s

hgy-n

至栅极脉冲信号s

hgy

。详细而言,第y-n条扫描线hgy-n具有栅极脉冲信号s

hgy-n

,第y-n 1条扫描线hgy-n 1具有栅极脉冲信号s

hgy-n 1

,第y-n 2条扫描线hgy-n 2具有栅极脉冲信号s

hgy-n 2

,

…

,第y条扫描线hgy具有栅极脉冲信号s

hgy

。

145.请参照图11及图12,以一时间延迟按序开启第y-n条扫描线hgy-n至第y条扫描线hgy,其中时间延迟的时间长度为t(绘于图12),栅极脉冲信号s

hgy-n

至栅极脉冲信号s

hgy

的每一者的脉冲时间长度为tp(绘于图12),且n=tp/t。第y条扫描线hgy的栅极脉冲信号s

hgy

的开始时间tony与第y-n条扫描线hgy-n的栅极脉冲信号s

hgy-n

的结束时间toffy-n于时序上重叠。

146.请参照图11,多条转接线vg包括第y-n转接线vgy-n及第y转接线vgy,分别电性连接至第y-n条扫描线hgy-n及第y条扫描线hgy。请参照图11及图12,第y-n转接线vgy-n及第y转接线vgy分别具有栅极脉冲信号s

vgy-n

及栅极脉冲信号s

vgy

,其中第y-n转接线vgy-n的栅极脉冲信号s

vgy-n

及第y转接线vgy的栅极脉冲信号s

vgy

分别与第y-n条扫描线hgy-n的栅极脉冲信号s

hgy-n

及第y条扫描线hgy的栅极脉冲信号s

hgy

相同。

147.请参照图11,多个像素行r包括在第一方向d1上按序排列的第q-1个像素行rq-1、第q个像素行rq、第q 1个像素行rq 1及第q 2个像素行rq 2,q为大于或等于2的正整数;多条数据线dl包括第q-1数据线dlq-1、第q数据线dlq、第q 1数据线dlq 1及第q 2数据线dlq 2,分别电性连接至第q-1个像素行rq-1、第q个像素行rq、第q 1个像素行rq 1及第q 2个像素行rq 2,q为大于或等于2的正整数。

148.请参照图11,值得注意的是,在像素阵列基板100的俯视图中,第y转接线vgy设置于第q-1数据线dlq-1与第q数据线dlq之间,且第y-n转接线vgy-n设置于第q数据线dlq与第q 1数据线dlq 1之间;以下以图5及图6为例说明。

149.请参照图5及图6,在本实施例的像素阵列基板100的一处中,可将前述的对应图11及图12的n、y、q分别视为8、13、6(即,n=8,y=13,q=6)。请参照图5及图6,在本实施例的像素阵列基板100的一处中,多条扫描线hg包括在第二方向d2上按序排列的第5条扫描线hg5至第13条扫描线hg13;第13条扫描线hg13的栅极脉冲信号s

hg13

的开始时间ton13与第5条扫描线hg5的栅极脉冲信号s

hg5

的结束时间toff5于时序上重叠。多条转接线vg包括第5转接线vg5及第13转接线vg13,分别电性连接至第5条扫描线hg5及第13条扫描线hg13。第5转接线vg5及第13转接线vg13分别具有栅极脉冲信号s

vg5

及栅极脉冲信号s

vg13

,其中第5转接线vg5的栅极脉冲信号s

vg5

及第13转接线vg13的栅极脉冲信号s

vg13

分别与第5条扫描线hg5的栅极脉冲信号s

hg5

及第13条扫描线hg13的栅极脉冲信号s

hg13

相同。多个像素行r包括在第一方向d1上按序排列的第5个像素行r5、第6个像素行r6、第7个像素行r7及第8个像素行r8;多条数据线dl包括第5数据线dl5、第6数据线dl6、第7数据线dl7及第8数据线dl8,分别电性连接至第5个像素行r5、第6个像素行r6、第7个像素行r7及第8个像素行r8。

150.请参照图5,值得注意的是,在像素阵列基板100的俯视图中,第13转接线vg13设置于第5数据线dl5与第6数据线dl6之间,且第5转接线vg5设置于第6数据线dl6与第7数据线dl7之间。类似地,第13转接线vg13与第5转接线vg5相邻于第6数据线dl6且分别位于第6数

据线dl6的左右两侧。请参照图5及图6,类似地,由于第5条转接线vg5的栅极脉冲信号s

vg5

的结束时间toff5与第13条转接线vg13的栅极脉冲信号s

vg13

的开始时间ton13于时序上重叠,因此第13转接线vg13与第6数据线dl6之间的电容耦合效应和第5转接线vg5与第6数据线dl6之间的电容耦合效应可相抵销,使得位于第6个像素行r6且电性连接至第13条扫描线hg13的像素结构px的像素电极194(绘于图3)的电位不易因设置于其左右两旁的多条转接线vg而过度偏离于理想值。因此,位于第6个像素行r6且电性连接至第13条扫描线hg13的像素结构px不易出现异常的亮度(例如:偏亮),进而使现有技术中所述的斜向亮线的问题获得改善。

151.须说明的是,位于同一条数据线dl左右两侧且在第一方向d1上按序排列的两条转接线vg,其与所述同一条数据线dl的多个电容效应可相抵销;但本发明并不限制,在第一方向d1上先排列的其中一条转接线vg的栅极脉冲信号的开始时间必须早于后排列的另一条转接线vg的栅极脉冲信号的开始时间;本发明也不限制,在第一方向d1上先排列的其中一条转接线vg的栅极脉冲信号的开始时间必须晚于后排列的另一条转接线vg的栅极脉冲信号的开始时间。

152.举例而言,在图5的像素阵列基板100的一处,设置于同一条数据线(例如:第2数据线dl2)左右两侧且在第一方向d1上按序排列的两条转接线(例如:第1转接线vg1及第9转接线vg9),其与所述同一条数据线(例如:第2数据线dl2)的多个电容效应可相抵销,在第一方向d1上先排列的其中一条转接线vg的栅极脉冲信号的开始时间可早于后排列的另一条转接线vg的栅极脉冲信号的开始时间(例如:在第一方向d1上先排列的第1转接线vg1的栅极脉冲信号s

vg1

的开始时间ton1可早于后排列的第9转接线vg9的栅极脉冲信号s

vg9

的开始时间ton9);但在图5的像素阵列基板100的另一处,设置于同一条数据线(例如:第6数据线dl6)左右两侧且在第一方向d1上按序排列的多条转接线(例如:第13转接线vg13及第5转接线vg5),其与所述同一条数据线(例如:第6数据线dl6)的多个电容效应可相抵销,在第一方向d1上先排列的一条转接线vg的栅极脉冲信号的开始时间可晚于后排列的另一条转接线vg的栅极脉冲信号的开始时间(例如:在第一方向d1上先排列的第13转接线vg13的栅极脉冲信号s

vg13

的开始时间ton13可晚于后排列的第5转接线vg5的栅极脉冲信号s

vg5

的开始时间ton5)。

153.请再参照图11及图12,像素阵列基板100还包括第二共用线vss2;在像素阵列基板100的俯视图中,第y转接线vgy设置于第q-1数据线dlq-1与第q数据线dlq之间,第y-n转接线vgy-n设置于第q数据线dlq与第q 1数据线dlq 1之间,且第二共用线vss2设置于第q 1数据线dlq 1及第q 2数据线dlq 2之间;以下以图5及图6为例说明。

154.请参照图5,在本实施例的像素阵列基板100的一处中,可将前述的对应图11及图12的n、y、q分别视为8、13、6(即,n=8,y=13,q=6)。请参照图5,在像素阵列基板100的俯视图中,第13转接线vg13设置于第5数据线dl5与第6数据线dl6之间,第5转接线vg5设置于第6数据线dl6与第7数据线dl7之间,且第二共用线vss2设置于第7数据线dl7及第8数据线dl8之间。

155.图13为本发明一实施例的像素阵列基板100的一处的俯视示意图。

156.图14示出图13的第y-n条扫描线hgy-n~第y条扫描线hgy的多个栅极脉冲信号s

hgy-n

~s

hgy

。

157.请参照图13及图14,多条扫描线hg包括在第二方向d2上按序排列的第y-n条扫描线hgy-n至第y条扫描线hgy,y为大于或等于2的正整数,n为正整数且小于y,第y条扫描线hgy的栅极脉冲信号s

hgy

的开始时间tony与第y-n条扫描线hgy-n的栅极脉冲信号s

hgy-n

的结束时间toffy-n于时序上重叠;多条扫描线hg还包括第p条扫描线hgp;多条转接线vg包括第y-n转接线vgy-n及第y转接线vgy,分别电性连接至第y-n条扫描线hgy-n及第y条扫描线hgy;多条转接线vg还包括第p转接线vgp,电性连接至第p条扫描线hgp;多条像素行r包括在第一方向d1上按序排列的第q-1个像素行rq-1、第q个像素行rq、第q 1个像素行rq 1及第q 2个像素行rq 2,q为大于或等于2的正整数;多条数据线dl包括第q-1数据线dlq-1、第q数据线dlq、第q 1数据线dlq 1及第q 2数据线dlq 2,分别电性连接至第q-1个像素行rq-1、第q个像素行rq、第q 1个像素行rq 1及第q 2个像素行rq 2;在像素阵列基板100的俯视图中,第y转接线vgy设置于第q-1数据线dlq-1与第q数据线dlq之间,第y-n转接线vgy-n设置于第q数据线dlq与第q 1数据线dlq 1之间,第p转接线vgp设置于第q 1数据线dlq 1与第q 2数据线dlq 2之间;特别是,p为大于2的正整数,且|y-p|不等于n;以下以图5及图6为例说明。

158.请参照图5及图6,在本实施例的像素阵列基板100的一处中,可将前述的对应图13及图14的n、y、q、p分别视为8、15、9、3(即,n=8,y=15,q=9,p=3)。请参照图5及图6,在像素阵列基板100的俯视图中,多条扫描线hg包括在第二方向d2上按序排列的第7条扫描线hg7至第15条扫描线hg15,第15条扫描线hg15的栅极脉冲信号s

hg15

的开始时间ton15与第7条扫描线hg7的栅极脉冲信号s

hg7

的结束时间toff7于时序上重叠;多条扫描线hg还包括第3条扫描线hg3;多条转接线vg包括第7转接线vg7及第15转接线vg15,分别电性连接至第7条扫描线hg7及第15条扫描线hg15;多条转接线vg还包括第3转接线vg3,电性连接至第3条扫描线hg3;多条像素行r包括在第一方向d1上按序排列的第8个像素行r8、第9个像素行r9、第10个像素行r10及第11个像素行r11;多条数据线dl包括第8数据线dl8、第9数据线dl9、第10数据线dl10及第11数据线dl11,分别电性连接至第8个像素行r8、第9个像素行r9、第10个像素行r10及第11个像素行r11;在像素阵列基板100的俯视图中,第15转接线vg15设置于第8数据线dl8与第9数据线dl9之间,第7转接线vg7设置于第9数据线dl9与第10数据线dl10之间,第3转接线vg3设置于第10数据线dl10与第11数据线dl11之间;特别是,3为大于2的正整数,且|15-3|不等于8。

159.也就是说,在本实施例中,于像素阵列基板100的一处,位于同一数据线dl(例如:第9数据线dl9)左右两侧的两条转接线vg(例如:第15转接线vg15及第7转接线vg7)的栅极脉冲信号(例如:s

vg15

、s

vg7

)的开始时间(例如:ton15、ton7)可相差n个所述时间延迟的时间长度t(例如:8个t;但在像素阵列基板100的另一处,位于同一数据线dl(例如:第10数据线dl10)左右两侧的多条转接线vg(例如:第7转接线vg7及第3转接线vg3)的栅极脉冲信号(例如:s

vg7

、s

vg3

)的开始时间(例如:ton7、ton3)也可不相差n个t(例如是,相差4个t)。

160.在前述的说明中,是以tp/t=n=8为例说明。然而,本发明不限于此,在其它实施例中,tp/t=n,且n也可以是除了8以外的其它正整数,以下配合图15及图16举例说明。

161.图15为本发明一实施例的像素阵列基板100a的一处的俯视示意图。

162.图16示出图15的第1条扫描线hg1~第9条扫描线hg9的多个栅极脉冲信号s

hg1

~s

hg9

。

163.请再参照图1及图2,多条扫描线hg包括在第二方向d2上按序排列的第x-n条扫描

线hgx-n至第x n条扫描线hgx n,x为大于或等于2的正整数,n为正整数且小于x;第x条扫描线hgx的栅极脉冲信号s

hgx

的开始时间tonx与第x-n条扫描线hg的栅极脉冲信号s

hgx-n

的结束时间toffx-n于时序上重叠;第x条扫描线hgx的栅极脉冲信号s

hgx

的结束时间toffx与第x n条扫描线hgx n的栅极脉冲信号s

hgx n

的开始时间tonx n于时序上重叠;多条转接线vg包括第x-n转接线vgx-n、第x转接线vgx及第x n转接线vgx n,分别电性连接至第x-n条扫描线hgx-n、第x条扫描线hgx及第x n条扫描线hgx n;多个像素行r包括在第一方向d1上按序排列的第k-1个像素行rk-1、第k个像素行rk、第k 1个像素行rk 1及第k 2个像素行rk 2,k为大于或等于2的正整数;多条数据线dl包括第k-1数据线dlk-1、第k数据线dlk、第k 1数据线dlk 1及第k 2数据线dlk 2,分别电性连接至第k-1个像素行rk-1、第k个像素行rk、第k 1个像素行rk 1及第k 2个像素行rk 2。在像素阵列基板100的俯视图中,第x-n转接线vgx-n设置于第k-1数据线dlk-1与第k数据线dlk之间,第x转接线vgx设置于第k数据线dlk与第k 1数据线dlk 1之间,且第x n转接线vgx n设置于第k 1数据线dlk 1与第k 2数据线dlk 2之间;以下以图15及图16为例说明。

164.在本实施例的像素阵列基板100a的一处中,可将上一段所述的n、x、k分别视为4、5、2(即,n=4,x=5,k=2)。请参照图15及图16,多条扫描线hg包括在第二方向d2上按序排列的第1条扫描线hg1至第9条扫描线hg9;第5条扫描线hg5的栅极脉冲信号s

hg5

的开始时间ton5与第1条扫描线hg的栅极脉冲信号s

hg1

的结束时间toff1于时序上重叠;第5条扫描线hg5的栅极脉冲信号s

hg5

的结束时间toff5与第9条扫描线hg9的栅极脉冲信号s

hg9

的开始时间ton9于时序上重叠;多条转接线vg包括第1转接线vg1、第5转接线vg5及第9转接线vg9,分别电性连接至第1条扫描线hg1、第5条扫描线hg5及第9条扫描线hg9;多个像素行r包括在第一方向d1上按序排列的第1个像素行r1、第2个像素行r2、第3个像素行r3及第4个像素行r4;多条数据线dl包括第1数据线dl1、第2数据线dl2、第3数据线dl3及第4数据线dl4,分别电性连接至第1个像素行r1、第2个像素行r2、第3个像素行r3及第4个像素行r4。在像素阵列基板100的俯视图中,第1转接线vg1设置于第1数据线dl1与第2数据线dl2之间,第5转接线vg5设置于第2数据线dl2与第3数据线dl3之间,且第9转接线vg9设置于第3数据线dl3与第4数据线dl4之间。

165.图17为本发明一实施例的像素阵列基板100的像素结构px的剖面示意图。图17对应图3的剖线ii-ii’。

166.以下配合图3及图17举例说明本发明一实施例的像素结构px的具体构造。像素结构px可选择性地被应用在前述像素阵列基板100或100a中。

167.请参照图3及图17,像素结构px除了包括前述的薄膜晶体管t和电性连接至薄膜晶体管t的像素电极194外,像素结构px还包括第一共用电极122。第一共用电极122与像素电极194部分地重叠,以形成一存储电容。

168.在本实施例中,像素结构px可选择性地包括第二共用电极124,与第一共用电极122分离。请参照图3,在像素阵列基板100的俯视图中,第一共用电极122、第二共用电极124及扫描线hg在第二方向d2上排列且彼此分离。

169.举例而言,在本实施例中,第一共用电极122、第二共用电极124及扫描线hg可属于所述第一导电层且彼此分离,薄膜晶体管t的栅极tc可属于所述第一导电层,且薄膜晶体管t的栅极tc与扫描线hg可直接连接;薄膜晶体管t的源极ta和漏极tb可属于第二导电层且彼

此分离,数据线dl可属于第二导电层,且数据线dl与薄膜晶体管t的源极ta可直接连接;但本发明不以此为限。

170.请参照图3及图17,像素结构px还包括导电图案142,电性连接至薄膜晶体管t。具体而言,导电图案142电性连接至薄膜晶体管t的漏极tb。举例而言,在本实施例中,导电图案142与薄膜晶体管t的漏极tb可属于同一第二导电层且可直接连接,但本发明不以此为限。

171.导电图案142具有第一部142-1,设置于第一共用电极122上。具体而言,导电图案142设置于绝缘层130上,且导电图案142的第一部142-1与第一共用电极122重叠。在本实施例中,导电图案142还具有第二部142-2,设置于第二共用电极124上。具体而言,导电图案142设置于绝缘层130上,且导电图案142的第二部142-2与第二共用电极124重叠。在本实施例中,导电图案142还具有第三部142-3,连接于第一部142-1与第二部142-2之间。在像素阵列基板100的俯视图中,导电图案142的第三部142-3位于第一共用电极122与第二共用电极124之间,且不重叠于第一共用电极122及第二共用电极124。

172.请参照图3及图17,像素结构px还包括第一绝缘层150,设置于导电图案142上,且具有与导电图案142重叠的一开口152。在本实施例中,第一绝缘层150的开口152可重叠于导电图案142的第三部142-3。举例而言,在本实施例中,第一绝缘层150的材质可为无机材料(例如:氧化硅、氮化硅、氮氧化硅、或上述至少二种材料的堆叠层)、有机材料或上述的组合。

173.请参照图3及图17,像素结构px还包括彩色滤光图案160,设置于第一绝缘层150上,且具有与导电图案142重叠的一开口162。请参照图3,举例而言,在像素阵列基板100的俯视图中,第一绝缘层150的开口152可位于彩色滤光图案160的开口162以内。

174.请参照图3及图17,像素结构px还包括第二绝缘层170,设置于彩色滤光图案160上,且具有与导电图案142重叠的一开口172。举例而言,在本实施例中,第二绝缘层170的材质可为无机材料(例如:氧化硅、氮化硅、氮氧化硅、或上述至少二种材料的堆叠层)、有机材料或上述的组合。

175.在本实施例中,像素阵列基板100可选择性地包括一透明导电层180,设置于第二绝缘层170上。透明导电层180设置于转接线vg所属的膜层与像素电极194所属的膜层之间,以屏蔽像素电极194,使像素电极194的电位不易受转接线vg的影响。举例而言,在本实施例中,透明导电层180的材质可包括金属氧化物,例如:铟锡氧化物、铟锌氧化物、铝锡氧化物、铝锌氧化物、铟锗锌氧化物、其它合适的氧化物、或者是上述至少二者的堆叠层,但本发明不以此为限。

176.像素电极194设置于第二绝缘层170上,且通过第一绝缘层150的开口152及第二绝缘层170的开口172电性连接至导电图案142。举例而言,在本实施例中,像素结构px可选择性地包括第三绝缘层190,设置于第二绝缘层170上,且覆盖透明导电层180;第三绝缘层190具有开口192,重叠于导电图案142;像素电极194可设置于第三绝缘层190上,且通过第三绝缘层190的开口192、第二绝缘层170的开口172及第一绝缘层150的开口152电性接触于导电图案142的第三部142-3,但本发明不以此为限。

177.在本实施例中,第三绝缘层190的开口192、第二绝缘层170的开口172及第一绝缘层150的开口152可位于导电图案142的第三部142-3上;第三绝缘层190的开口192、第二绝

缘层170的开口172及第一绝缘层150的开口152实质上可切齐;但本发明不以此为限。

178.在本实施例中,于像素阵列基板100的俯视图中,第一绝缘层150的开口152及第二绝缘层170的开口172可位于第一共用电极122与第二共用电极124之间且不重叠于第一共用电极122与第二共用电极124。

179.请参照图3,值得注意的是,在像素阵列基板100的俯视图中,导电图案142的第一部142-1覆盖第一共用电极122的位于彩色滤光图案160的开口162内的所有边缘122e。请参照图3及图17,也就是说,在彩色滤光图案160的开口162内,不会出现导电图案142的边缘142e与第一共用电极122的边缘122e的重合处或交错处,而第一共用电极122、导电图案142及夹设于两者之间的绝缘层130不易形成具有陡峭侧壁的堆叠结构。在第一共用电极122的边缘122e附近,第二绝缘层170不需形成在具有陡峭侧壁的堆叠结构上,而能良好地设置在第一绝缘层150上。因此,第二绝缘层170能良好地包覆彩色滤光图案160及其侧壁164,使得彩色滤光图案160内的气体不易穿过第二绝缘层170而泄漏至像素阵列基板100外,造成显示面板的气泡问题。

180.请参照图3,在本实施例中,于像素阵列基板100的俯视图中,导电图案142的第二部142-2覆盖第二共用电极124的位于彩色滤光图案160的开口162内的所有边缘124e。请参照图3及图17,也就是说,在彩色滤光图案160的开口162内,不会出现导电图案142的边缘142e与第二共用电极124的边缘124e的重合处或交错处,而第二共用电极124、导电图案142及夹设于两者之间的绝缘层130不易形成具有陡峭侧壁的堆叠结构。在第二共用电极124的边缘124e附近,第二绝缘层170不需形成在具有陡峭侧壁的堆叠结构上,而能良好地设置在第一绝缘层150上。因此,第二绝缘层170能良好地包覆彩色滤光图案160及其侧壁164,使得彩色滤光图案160内的气体不易穿过第二绝缘层170而泄漏至像素阵列基板100外,造成显示面板的气泡问题。

181.图18为本发明一实施例的像素阵列基板100b的像素结构px的布局(layout)的俯视示意图。

182.图19为本发明一实施例的像素阵列基板100b的像素结构px的剖面示意图。图19对应图18的剖线iii-iii’。

183.图18及图19的像素结构px也可选择性地被应用在前述像素阵列基板100或100a中。

184.图18及图19的像素结构px与图3及图17的像素结构px类似,因此相同或相似的元件以相同或相似的标号表示,以下说明两者的差异,两者相同或相似处请参照前述说明,于此便不再重述。

185.请参照图18及图19,在本实施例中,像素结构px可不包括图3及图17的实施例的第二共用电极124。此外,像素结构px可不包括图3及图17的实施例的第三绝缘层190及透明导电层180。

186.请参照图18及图19,在本实施例中,导电图案142的第二部142-2可设置于薄膜晶体管t的栅极tc上。请参照图18,在像素阵列基板100b的俯视图中,导电图案142的第二部142-2可覆盖栅极tc的位于彩色滤光图案160的开口162内的所有边缘tcs。

187.在像素阵列基板100b的俯视图中,导电图案142的第三部142-3位于第一共用电极122与栅极tc之间,第一绝缘层150的开口152及第二绝缘层170的开口172位于导电图案142

的第三部142-3上,且第一绝缘层150的开口152及第二绝缘层170的开口172不重叠于第一共用电极122与栅极tc。

188.图20为本发明一实施例的像素阵列基板100c的像素结构px的布局(layout)的俯视示意图。

189.图21为本发明一实施例的像素阵列基板100c的像素结构px的剖面示意图。图21对应图20的剖线iv-iv’。

190.图20及图21的像素结构px也可选择性地被应用在前述像素阵列基板100或100a中。

191.图20及图21的像素结构px与图3及图17的像素结构px类似,因此相同或相似的元件以相同或相似的标号表示,以下说明两者的差异,两者相同或相似处请参照前述说明,于此便不再重述。

192.与图3及图17的像素结构px不同的是,在图20及图21的实施例中,像素结构px还包括第三共用电极126,与第一共用电极122及第二共用电极124分离。在本实施例中,第三共用电极126可属于所述第一导电层。请参照图20,导电图案142还包括第四部142-4设置于第三共用电极126上。在像素阵列基板100c的俯视图中,导电图案142的第四部142-4覆盖第三共用电极126的位于彩色滤光图案160的开口162内的所有边缘126e。

193.图22为本发明一实施例的像素阵列基板100d的像素结构px的布局(layout)的俯视示意图。

194.图23为本发明一实施例的像素阵列基板100d的像素结构px的剖面示意图。图23对应图22的剖线v-v’。

195.图22及图23的像素结构px也可选择性地被应用在前述像素阵列基板100或100a中。

196.图22及图23的像素结构px与图3及图17的像素结构px类似,因此相同或相似的元件以相同或相似的标号表示,以下说明两者的差异,两者相同或相似处请参照前述说明,于此便不再重述。

197.在图3及图17的实施例中,导电图案142的第一部142-1的一边缘142-1e(标示于图3)与彩色滤光图案160的开口162的一边缘162e(标示于图3)实质上切齐。也就是说,在图3及图17的实施例中,导电图案142的第一部142-1未超出彩色滤光图案160的开口162。

198.在图22及图23的实施例中,导电图案142还具有第五部142-5;在像素阵列基板100d的俯视图中,导电图案142的第五部142-5与第一共用电极122重叠且位于彩色滤光图案160的开口162外。也就是说,在图22及图23的实施例中,导电图案142可超出彩色滤光图案160的开口162。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。