1.本发明涉及一种基于复合介质栅双晶体管光敏探测器的行列电流减法读出电路,属于集成电路领域。

背景技术:

2.在成像领域中常用的成像器件有ccd以及cmos-aps,但二者在实际应用中仍有许多的不足。对于ccd,出于转移效率的考虑,其尺寸很难做小。对于cmos-aps,由于其读出电路的复杂性,所占面积较大,导致实际感光区域很难做大,满阱电荷量小。

3.公告号为cn 102938409b的中国发明专利提出了一种双晶体管光敏探测器。其特点是单个器件即可实现复位、感光以及读出,相比于ccd以及cmos-aps,所述双晶体管光敏探测器不需要复杂的读出部分,面积可以大大减小,感光面积可以做的更大,满阱电荷量大。但对于现有的光敏探测器,其输出一般都是在数字域做减法,会带来大面积、大功耗、高噪声以及低精度等问题。

技术实现要素:

4.本发明的目的在于提供一种基于复合介质栅双晶体管光敏探测器的行列电流减法读出电路,可实现像素行与行之间以及列与列之间的电流减法读出。

5.本发明的技术方案如下:

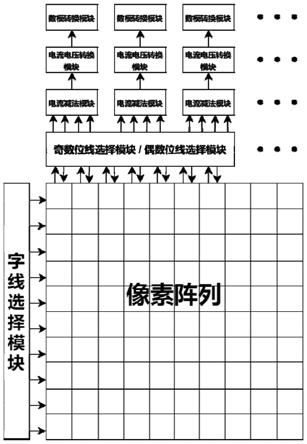

6.基于复合介质栅双晶体管光敏探测器的行列减法读出电路,包括由多个复合栅介质晶体管构成的晶体管阵列、字线选择模块、奇数位线选择模块、偶数位线选择模块、电流减法模块、电流电压转换模块和数模转换模块;所述晶体管阵列中同行的所有晶体管栅极相连,构成字线,并与所述字线选择模块的输出端相连;所述晶体管阵列中奇数行同列的所有晶体管漏极相连,构成奇数位线,并与所述奇数位线选择模块的输出端相连;所述晶体管阵列中偶数行同列的所有晶体管漏极相连,构成偶数位线,并与所述偶数位线选择模块的输出端相连;所述晶体管阵列同列的所有晶体管源极相连,构成源线;所述奇数位线选择模块的输出端和所述偶数位线选择模块的输出端均与所述电流减法模块的输入端相连,所述电流减法模块的输出端与所述电流电压转换模块的输入端相连,所述电流电压转换模块的输出端与所述数模转换模块的输入端相连。

7.进一步地,所述字线选择模块包括字线选择译码器和字线电平转换电路,所述字线选择译码器的输入端与字线地址信号相连,其输出端与所述字线电平转换电路的输入端一一对应相连;所述字线电平转换电路的输出端作为所述字线选择模块的输出端且与所述晶体管阵列的字线一一对应相连。

8.进一步地,所述奇数位线选择模块包括奇数位线选择译码器和奇数位线电平转换电路,所述奇数位线选择译码器的输入端与奇数位线地址信号相连,其输出端与所述奇数位线电平转换电路的输入端一一对应相连;所述奇数位线电平转换电路的输出端作为所述奇数位线选择模块的输出端且与所述晶体管阵列的奇数位线一一对应相连。

9.进一步地,所述偶数位线选择模块包括偶数位线选择译码器和偶数位线电平转换电路,所述偶数位线选择译码器的输入端与偶数位线地址信号相连,其输出端与所述偶数位线电平转换电路的输入端一一对应相连;所述偶数位线电平转换电路的输出端作为偶数位线选择模块的输出端且与所述晶体管阵列的偶数位线一一对应相连。

10.进一步地,所述电流减法模块包括奇偶行电流镜减法电路、奇数行奇偶列电流镜减法电路和偶数行奇偶列电流镜减法电路;所述奇偶行电流镜减法电路的输入端与同列所述奇数位线和所述偶数位线相连,其输出端作为电流减法模块的输出端;所述奇数行奇偶列电流镜减法电路的输入端与所述晶体管阵列中每两个相邻列的奇数位线相连,其输出端作为电流减法模块的输出端;所述偶数行奇偶列电流镜减法电路的输入端与所述晶体管阵列中每两个相邻列的偶数位线相连,其输出端作为电流减法模块的输出端且与电流电压转换模块的输入端相连。

11.进一步地,所述电流电压转换模块为带预充电功能的电容模块,且输出端与数模转换模块的输入端相连,所述数模转换模块为单斜坡数模转换器。

12.进一步地,所述晶体管阵列使用一个电流减法模块;在晶体管阵列中,每列的奇数位线和偶数位线使用一个奇偶行电流镜减法电路,每两个相邻列的奇数位线使用一个所述奇数行奇偶列电流镜减法电路,每两个相邻列的偶数位线使用一个所述偶数行奇偶列电流镜减法电路。

13.本发明提出了模拟域的行列电流减法读出电路,具有以下技术效果:

14.读出模式下,一个读出周期内通过字线地址信号控制复合栅介质晶体管阵列相邻两行的字线选通,通过奇数位线地址信号和偶数位线地址信号分别控制复合栅介质晶体管阵列的所有奇数位线和偶数位线选通。通过奇偶行电流镜减法电路、奇数行奇偶列电流镜减法电路和偶数行奇偶列电流镜减法电路,实现奇数行与偶数行、奇数列与偶数列的电流减法读出。本发明的行列电流减法读出电路具有小面积、低功耗、低噪声以及高精度的优势。

附图说明

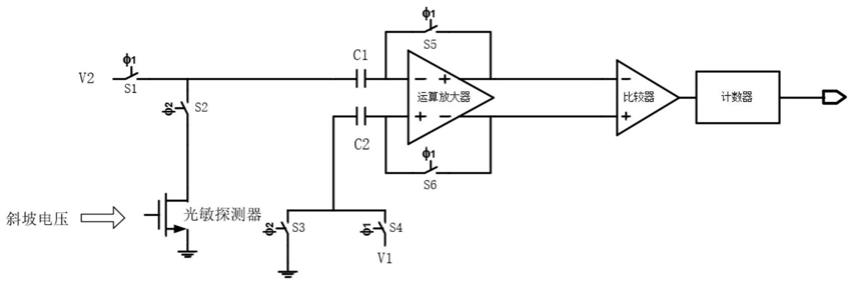

15.图1为复合介质栅双晶体管光敏探测器阵列以及各电路模块框图,

16.图2为复合介质栅双晶体管光敏探测器阵列在读出模式下的各端口连接方式示意图。

具体实施方式

17.本实施例提供一种基于复合介质栅双晶体管光敏探测器的行列电流减法读出电路,包括由多个复合栅介质晶体管构成的阵列、字线选择模块、奇数位线选择模块、偶数位线选择模块、电流减法模块、电流电压转换模块和数模转换模块。晶体管阵列中同行的所有晶体管栅极相连,构成字线(记作wl),与字线选择模块的输出端相连。晶体管阵列中奇数行同列的所有晶体管漏极相连,构成奇数位线(记作blo),与奇数位线选择模块的输出端相连。晶体管阵列中偶数行同列的所有晶体管漏极相连,构成偶数位线(记作ble),与偶数位线选择模块的输出端相连。晶体管阵列同列的所有晶体管源极相连,构成源线(记作sl)。奇数位线选择模块的输出端和偶数位线选择模块的输出端均与电流减法模块的输入端相连。

电流减法模块的输出端与电流电压转换模块的输入端相连,电流电压转换模块的输出端与数模转换模块的输入端相连。

18.其中,字线选择模块包括字线选择译码器和字线电平转换电路。字线选择译码器的输入端与字线地址信号相连,输出端与字线电平转换电路的输入端一一对应相连。字线电平转换电路的输出端与晶体管阵列的字线一一对应相连。

19.奇数位线选择模块包括奇数位线选择译码器和奇数位线电平转换电路。奇数位线选择译码器的输入端与奇数位线地址信号相连,输出端与奇数位线电平转换电路的输入端一一对应相连。奇数位线电平转换电路的输出端与晶体管阵列的奇数位线一一对应相连。

20.偶数位线选择模块包括偶数位线选择译码器和偶数位线电平转换电路。偶数位线选择译码器的输入端与偶数位线地址信号相连,输出端与偶数位线电平转换电路的输入端一一对应相连。偶数位线电平转换电路的输出端与晶体管阵列的偶数位线一一对应相连。

21.电流减法模块包括奇偶行电流镜减法电路、奇数行奇偶列电流镜减法电路和偶数行奇偶列电流镜减法电路。奇偶行电流镜减法电路的输入端与同列奇数位线和偶数位线相连,输出端与电流电压转换模块的输入端相连。奇数行奇偶列电流镜减法电路的输入端与晶体管阵列中每两个相邻列的奇数位线相连,输出端与电流电压转换模块的输入端相连。偶数行奇偶列电流镜减法电路的输入端与晶体管阵列中每两个相邻列的偶数位线相连,输出端与电流电压转换模块的输入端相连。电流电压转换模块的输出端与数模转换模块的输入端相连。

22.上述由多个复合栅介质晶体管所构成的晶体管阵列的字线对应一个字线选择模块,字线选择模块内有唯一的字线选择译码器。由多个复合栅介质晶体管所构成的晶体管阵列的奇数位线对应一个奇数位线选择模块,奇数位线选择模块内有唯一的奇数位线选择译码器。所述由多个复合栅介质晶体管所构成的阵列的偶数位线对应一个所述偶数位线选择模块,偶数位线选择模块内有唯一的偶数位线选择译码器。由多个复合栅介质晶体管所构成的晶体管阵列对应一个电流减法模块。由多个复合栅介质晶体管所构成的晶体管阵列中每列的奇数位线和偶数位线对应一个奇偶行电流镜减法电路。由多个复合栅介质晶体管所构成的晶体管阵列中每两个相邻列的奇数位线对应一个奇数行奇偶列电流镜减法电路。由多个复合栅介质晶体管所构成的晶体管阵列中每两个相邻列的偶数位线对应一个所述偶数行奇偶列电流镜减法电路。

23.优选地,电流电压转换模块为带预充电功能的电容模块。数模转换模块为单斜坡数模转换器。

24.读出模式下,一个读出周期内通过字线地址信号控制复合栅介质晶体管阵列相邻两行的字线选通,通过奇数位线地址信号和偶数位线地址信号分别控制复合栅介质晶体管阵列的所有奇数位线和偶数位线选通。

25.如图2所示,以wl《0》、wl《1》blo《0》、blo《1》、ble《0》、ble《1》选通为例,则位于所述复合栅介质晶体管阵列左上角的四个晶体管(即位于第1行第1、2列和第2行第1、2列的晶体管,分别记为m11、m12、m21、m22)导通,导通电流进入电流减法模块。则通过奇偶行电流镜减法电路,实现m11与m21的电流减法以及m12、m22的电流减法;通过奇数行奇偶列电流镜减法电路,实现m11与m12的电流减法;通过偶数行奇偶列电流镜减法电路,实现m21与m22的电流减法。以上输出的减法电流通过电流电压转换模块和数模转换模块输出。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。