1.本发明涉及一种基于开关电容的复合介质栅双晶体管像素读出电路。

背景技术:

2.在中国专利cn201210442007中提出了一种双晶体管光敏探测器,该探测器的特点是单个半导体器件即可实现完整的复位、感光以及读出的功能,构成一个完整的像素,可以极大地提高像素的填充因子。这种复合介质栅双晶体管光敏探测器作为新一代的成像器件,mosfet区是一个阈值可变的n型mosfet,但由于工艺特殊性,对第二端的电压值有严格的要求。虽然利用常规稳压器结构可以实现电压的钳位功能,但是会带来环路稳定性问题,因此需要设计更加稳定、简易的读出电路。

技术实现要素:

3.有鉴于此,本发明提供一种基于开关电容的复合介质栅双晶体管像素读出电路,以解决环路稳定性问题。

4.本发明采用的技术方案如下:

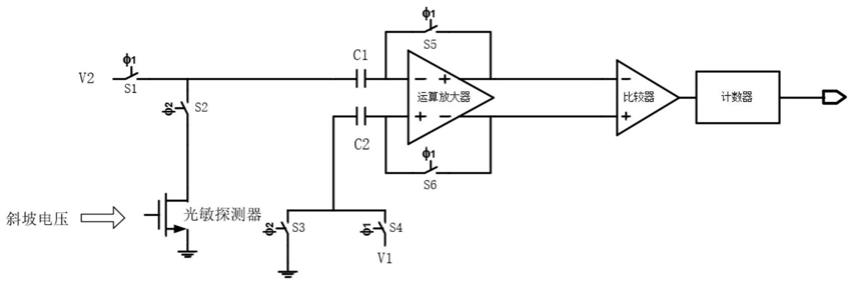

5.基于开关电容的复合介质栅双晶体管像素读出电路,包括复合介质栅双晶体管光敏探测器像素、电容、开关、运算放大器、比较器和计数器,复合介质栅双晶体管光敏探测器像素第一端接地,其第二端通过第二开关与第一电容第二端连接;第一电容与第二电容的第一端分别与运算放大器输入端的正负接口连接;第一电容的第二端还通过第一开关与第二电压v2连接;第二电容的第二端通过第三开关与第四开关分别与第一电压v1以及电源地连接;运算放大器通过第五开关和第六开关形成单位负反馈连接方式;运算放大器输出端的正负接口分别与比较器输入端的负正接口连接,比较器的输出端接计数器的使能信号。

6.进一步地,所述复合介质栅双晶体管光敏探测器像素包括mos-c部分和mosfet部分,在曝光阶段,mos-c部分在栅衬偏压的作用下产生耗尽区,收集光生载流子;在读出阶段,mosfet部分的阈值电压根据所收集的光生电荷量产生相应的变化;所述mosfet部分为n型,包括所述第一端、第二端和一个控制端。

7.进一步地,所述第一开关、第四开关、第五开关和第六开关属于使能信号为的开关,所述第二开关和第三开关属于使能信号为的开关,这两类开关不同时导通。

8.进一步地,所述第一电压v1和第二电压v2由电路内部模块产生或者由外部接入,第一电压v1小于第二电压v2。

9.进一步地,所述运算放大器输入端的正负接口和输出端的正负接口的电压值分别记为vinp、vinn、voutp、voutn,它们之间满足公式:(vinp-vinn vos)

×

a=voutp-voutn,其中,a表示运算放大器的增益,vos为运算放大器输入端的offset电压。

10.进一步地,所述单位负反馈连接方式为:运算放大器的输出端的正接口和输入端的负接口连接,输出端的负接口和输入端的正接口连接。

11.进一步地,所述比较器输入端的正负接口的电压值分别记为vinp、vinn,输出端的

信号为out,同时运算放大器有一个输入offset电压记作vos,那么它们之间满足的关系为:当vinp vos》vinn时out=逻辑1;当vinp vos《vinn时out=逻辑0。

12.进一步地,当计数器的使能信号为逻辑1时,计数器开始计时,每一个时钟周期结束,计数器输出端口数值增加1。

13.本发明的电路结构简单可靠,可以消除运算放大器自身offset电压的影响,且可以通过控制电压v2的大小实现复合介质栅双晶体管光敏探测器的漏端电压自定义,有较高的自由度。

附图说明

14.图1为本发明基于开关电容的复合介质栅双晶体管光敏探测器像素读出电路示意图。

具体实施方式

15.以下将参照附图更详细地描述本发明的技术方案。

16.应当理解,以下的描述中,运算放大器的输入 -端口和输出 -端口的电压值分别记作vinp、vinn、voutp、voutn,它们之间满足的公式为(vinp-vinn)

×

a=voutp-voutn。比较器的输入 -端口电压值分别记作vinpc、vinnc,它们之间满足的关系为:当vinp vos》vinn时out=逻辑1;当vinp vos《vinn时out=逻辑0。

17.在本申请中mosfet(metal-oxide-semiconductor field-effect transistor,金属氧化物半导体场效应晶体管)包括第一端、第二端和控制端,在mosfet的导通状态,电流从第一端流至第二端。p型mosfet的第一端、第二端和控制端分别为源极、漏极和栅极,n型mosfet的第一端、第二端和控制端分别为漏极、源极和栅极。

18.本实施例的像素读出电路包括复合介质栅双晶体管光敏探测器像素、电容、开关、运算放大器、比较器和计数器。其中,复合介质栅双晶体管光敏探测器像素的具体结构如专利cn201210442007中的描述。复合介质栅双晶体管光敏探测器像素mosfet部分第一端接地,第二端通过开关s2与电容c1第二端连接。电容c1与电容c2的第一端分别与运算放大器的输入 -端口连接。电容c1的第二端通过开关s1和开关s2分别与电压v2以及复合介质栅双晶体管光敏探测器第二端连接。电容c2的第二端通过开关s3与开关分s4别与电压v1以及电源地连接。运算放大器通过开关s5和开关s6形成单位负反馈连接方式,即运算放大器的输出 端口和输入-端口连接,输出-端口和输入 端口连接。运算放大器的 -输出端分别与比较器的- 输入端连接,比较器的输出端接计数器的使能信号。

19.在电路工作过程中,分为两个时间段,使能信号为的开关导通(也称作相位)和使能信号为的开关导通(也称作相位)。相位为重置阶段,相位为读出阶段。

20.在相位中,开关s1、s4、s5、s6导通,电容c1、c2的第二端分别连接至电压v2、v1。同时运算放大器为单位负反馈连接方式。此时vinp=vinn。电压v1、v2可以由电路内部其他模块产生,也可以外部接入电压,但需保证v1小于v2。

21.在相位中,开关s2、s3导通,电容c2由于第一端的电荷量不可改变,且电容c2第二端的电压值由v1转为0,所以电容c2第一端的电压值下降v1。此时vinp《vinn因此voutp《voutn,vinpc》vinnc比较器输出为逻辑1,计数器开始计数。直到斜坡电压扫过复合介质栅

双晶体管光敏探测器的阈值电压,电容c1由于第一端的电荷量不可改变,且电容c1第二端的电压值由v2转为0,所以电容c1第一端的电压值下降v2。令v1《v2,此时vinp》vinn因此voutp》voutn,vinpc《vinnc比较器输出为逻辑0,计数器停止计数。计数器数值即为复合介质栅双晶体管光敏探测器的灰度值体现。

技术特征:

1.基于开关电容的复合介质栅双晶体管像素读出电路,包括复合介质栅双晶体管光敏探测器像素、电容、开关、运算放大器、比较器和计数器,其特征在于,复合介质栅双晶体管光敏探测器像素第一端接地,其第二端通过第二开关与第一电容第二端连接;第一电容与第二电容的第一端分别与运算放大器输入端的正负接口连接;第一电容的第二端还通过第一开关与第二电压v2连接;第二电容的第二端通过第三开关与第四开关分别与第一电压v1以及电源地连接;运算放大器通过第五开关和第六开关形成单位负反馈连接方式;运算放大器输出端的正负接口分别与比较器输入端的负正接口连接,比较器的输出端接计数器的使能信号。2.根据权利要求1所述的基于开关电容的复合介质栅双晶体管像素读出电路,其特征在于,所述复合介质栅双晶体管光敏探测器像素包括mos-c部分和mosfet部分,在曝光阶段,mos-c部分在栅衬偏压的作用下产生耗尽区,收集光生载流子;在读出阶段,mosfet部分的阈值电压根据所收集的光生电荷量产生相应的变化;所述mosfet部分为n型,包括所述第一端、第二端和一个控制端。3.根据权利要求1所述的基于开关电容的复合介质栅双晶体管像素读出电路,其特征在于,所述第一开关、第四开关、第五开关和第六开关属于使能信号为的开关,所述第二开关和第三开关属于使能信号为的开关,这两类开关不同时导通。4.根据权利要求1所述的基于开关电容的复合介质栅双晶体管像素读出电路,其特征在于,所述第一电压v1和第二电压v2由电路内部模块产生或者由外部接入,第一电压v1小于第二电压v2。5.根据权利要求1所述的基于开关电容的复合介质栅双晶体管像素读出电路,其特征在于,所述运算放大器输入端的正负接口和输出端的正负接口的电压值分别记为vinp、vinn、voutp、voutn,它们之间满足公式:(vinp-vinn vos)

×

a=voutp-voutn,其中,a表示运算放大器的增益,vos为运算放大器输入端的offset电压。6.根据权利要求1所述的基于开关电容的复合介质栅双晶体管像素读出电路,其特征在于,所述单位负反馈连接方式为:运算放大器的输出端的正接口和输入端的负接口连接,输出端的负接口和输入端的正接口连接。7.根据权利要求1所述的基于开关电容的复合介质栅双晶体管像素读出电路,其特征在于,所述比较器输入端的正负接口的电压值分别记为vinp、vinn,输出端的信号为out,同时运算放大器有一个输入offset电压记作vos,那么它们之间满足的关系为:当vinp vos>vinn时out=逻辑1;当vinp vos<vinn时out=逻辑0。8.根据权利要求1所述的基于开关电容的复合介质栅双晶体管像素读出电路,其特征在于,当计数器的使能信号为逻辑1时,计数器开始计时,每一个时钟周期结束,计数器输出端口数值增加1。

技术总结

本发明公开了一种基于开关电容的复合介质栅双晶体管像素读出电路。该电路包括复合介质栅双晶体管光敏探测器像素、电容、开关、运算放大器、比较器和计数器,其中,复合介质栅双晶体管光敏探测器像素第一端接地,第二端与第一电容第二端连接;第一电容与第二电容的第一端分别与运算放大器输入端的正负接口连接;第一电容的第二端与第二电压连接;第二电容的第二端分别与第一电压以及电源地连接;运算放大器通过第五开关和第六开关形成单位负反馈连接方式;运算放大器输出端的正负接口分别与比较器输入端的负正接口连接,比较器的输出端接计数器的使能信号。本发明电路结构稳定,可以消除运算放大器自身offset电压的影响。除运算放大器自身offset电压的影响。除运算放大器自身offset电压的影响。

技术研发人员:闫锋 柴智 王凯 吴永杰 吴天泽 常峻淞 王一鸣 陈辉 李龙飞

受保护的技术使用者:南京大学

技术研发日:2021.11.10

技术公布日:2022/2/18

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。