基于fpga的低时延数据处理方法

技术领域

1.本发明属于电子信息与通信技术领域,尤其涉及到一种基于fpga的低时延数据处理方法。

背景技术:

2.现代通信系统中,为了保证数据通信的实时性,系统综合控制模块往往对系统中的各个子模块数据处理都有着严格的时间阈值限制。如果某个子模块在数据处理过程中超过了时间阈值,系统综合控制模块认为该子模块故障。在某些苛刻的使用环境下(如航空、航天环境),要求子模块的体积小、功耗低、数据处理实时性高。因此无法选择高性能处理器(体积大,功耗高)进行数据处理,只能选择而小型化、低功耗的芯片。小型化、低功耗的芯片在处理性能上往往存在着一定的瓶颈,如果需要大数据量处理,就会存在处理时间临界甚至超出规定的时间阈值的情况。

技术实现要素:

3.本发明的一个目的是提供一种基于fpga的低时延数据处理方法,并提供至少后面将说明的优点。

4.本发明的另一个目的是提供一种基于fpga的低时延数据处理方法,软、硬件协同,流水分割,使用fpga实现收/发分帧、定时发送、指令发送与软件数据并行处理,尽可能地提升了数据处理速度。

5.本发明的技术方案如下:基于fpga的低时延数据处理方法,其包括以下步骤:fpga处理单元检测接收使能信号是否有效,当所述接收使能信号有效时向接收fifo存储器中写入帧同步符syn,并将数据写入所述接收fifo存储器中;fpga处理单元检测接收使能信号是否有效,当所述接收使能信号无效时向所述接收fifo存储器中写入帧结束符end,记录为一帧;预先设定帧数阈值,当接收到的数据帧数达到所述帧数阈值时,所述数据处理单元读取所述接收fifo存储期内的数据并进行处理,并将处理后的数据通过所述fpga处理单元写入发送fifo存储器;fpga处理单元在处理后的数据中检测到发送标识符send_en时,从所述发送fifo存储器中调取所述处理后的数据进行发送;或者所述fpga处理单元在向所述接收fifo存储器中写入帧同步符时启动定时器开始计时并将其作为处理时间;预先设定一处理时间阈值,当所述处理时间达到所述处理时间阈值时,所述fpga处理单元从所述发送fifo处理器中调取所述处理后的数据进行发送。

6.优选的是,所述的基于fpga的低时延数据处理方法中,所述fpga处理单元将数据写入所述接收fifo存储器时,所述接收fifo存储器的读写数据位宽的最高bit位用于指示数据有效性,1为无效,0位有效;次高bit位及低8bit相结合指示syn和end;最高bit和次高

bit都为0时,低8bit指示为数据。

7.优选的是,所述的基于fpga的低时延数据处理方法中,所述接收fifo存储器的读写数据位宽为16bit, syn定义为0x40ff,end定义为0x4000,无效数据定义为0x8000,有效数据定义为0x00xx。

8.优选的是,所述的基于fpga的低时延数据处理方法中,所述数据处理单元处理数据包括:从所述接收fifo存储器中读取数据,将syn和end之间的无效数据丢弃,有效数据拷贝至缓存buf存储器处理,处理完写入发送fifo存储器;写入最后一个数据后,向fpga处理单元写入发送标识符send_en。

9.本发明具有以下有益效果:通过采用中断发送和定时发送两种同时工作机制,可以实现很高的实时性处理性能。

10.本发明的其它优点、目标和特征将部分通过下面的说明体现,部分还将通过对本发明的研究和实践而为本领域的技术人员所理解。

附图说明

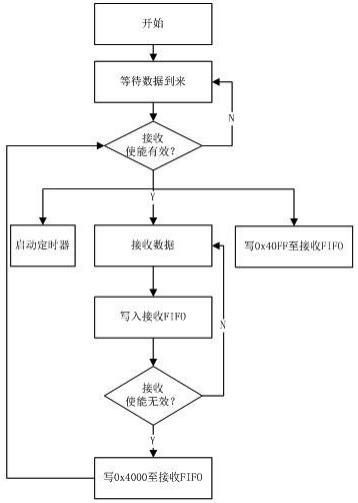

11.图1为本发明提供的基于fpga的低时延数据处理方法的一个实施例中的数据接收处理框图;图2为本发明提供的基于fpga的低时延数据处理方法的一个实施例中的接收数据结构图;图3为本发明提供的基于fpga的低时延数据处理方法的一个实施例中的数据处理指令发送时序图;图4为本发明提供的基于fpga的低时延数据处理方法的一个实施例中的发送数据结构图;图5为本发明提供的基于fpga的低时延数据处理方法的一个实施例中的数据发送处理框图;图6为本发明提供的基于fpga的低时延数据处理方法的一个实施例中的数据处理指令超时发送时序图。

具体实施方式

12.下面结合附图对本发明做进一步的详细说明,以令本领域技术人员参照说明书文字能够据以实施。

13.应当理解,本文所使用的诸如“具有”、“包含”以及“包括”术语并不配出一个或多个其它元件或其组合的存在或添加。

14.在数据处理机的处理算法和收/发接口性能都已确定的情况下,为了尽可能的加快数据处理速度,在数据的收/发的过程中,采用软、硬件协同工作的方式,对数据的处理过程进行流水分割设计,使得进行一次完整数据帧的传输达到了最大的性能。本发明提供了一种使用fpga实现收/发分帧、定时发送、指令发送与软件数据并行处理,以流水方式进行数据处理的方法。

15.如图1所示,本发明提供的基于fpga的低时延数据处理方法中,fpga接收过程:

fpga在检测到接收使能有效(同步接口)或帧同步头(异步接口)后,向接收fifo中写入帧同步符syn,指示一帧的开始。fpga在检测接收使能无效或帧结束符(异步接口)后,向接收fifo中写入帧结束符end。fpga在接收过程中,如果接收到的数据计数达到用户设置的接收中断阈值,则向数据处理单元产生中断信号,通知数据处理单元从接收fifo中读取数据进行处理。

16.fpga在向接收fifo中写入数据时,fifo的最高bit位用于指示数据有效性(1为无效,0位有效);次高bit位及低8bit相结合指示syn和end;最高bit和次高bit都为0时,低8bit指示为数据。以上各bit位功能可以根据硬件平台情况自定义。例如fifo读写数据位宽16bit,那么syn可以定义为0x40ff,end可以定义为0x4000,无效数据指示为0x8000,有效数据可以定义为0x00xx,结构如图2所示。

17.数据处理单元在初始化的过程中,需要设置fpga的超时发送时间time_out_val,接收中断阈值intr_val。time_out_va和intr_val具体参数需要根据指标的时延要求进行设置。

18.数据处理单元接收到fpga产生的接收中断后,从接收fifo读取数据,将syn和end之间的无效数据(0x8000)丢弃,有效数据(0x00xx)拷贝至缓存buf,在读取数据时,对可以处理的数据立即处理,处理完写入fpga发送fifo,如图4所示。数据处理单元写入最后一个数据后,向fpga发送使能寄存器写入发送使能控制符send_en(0x2a00),通知fpga可以执行发送操作。

19.fpga发送过程为:fpga在数据发送处理时,采用两种发送方式:中断发送和定时发送。

20.数据处理单元指令发送:此种情况适用于数据处理单元处理短帧数据的情况。如图5所示,数据处理单元将处理完成的数据写入fpga发送fifo,最后写入发送标志符send_en。fpga检测到send_en有效后,不等待定时器超时中断,直接启动数据操作。

21.定时器超时发送:此种情况适用于数据处理单元处理长帧数据的情况。如图6所示,fpga在检测到收数据同步信号有效后,使能发送定时器。如果定时器计数达到了用户设定的时间阈值,不等待send_en信号有效,立即从发送fifo取出数据进行发送。

22.通过采用中断发送和定时发送两种同时工作机制,可以实现很高的实时性处理性能。例如系统要求处理时延不得超过15ms,用户可以设置超时阈值为13ms。数据处理单元在对长度较短数据帧进行处理时,在13ms内即可完成,所以只要数据处理单元下发发送指令,fpga就立即进行发送操作。对于长数据帧,数据处理单元在处理时可能会超过13ms,通过合理软件设计,将数据进行分段处理,处理好的数据及时写入发送fifo,保证fpga发送fifo为非空,利用超时发送机制,即可已实现数据按要求传输。

23.传统的软件处理数据方法包含了:接收数据、判断数据完整性、处理数据、发送数据等一系列操作,本方法对以上过程进行了流水分割,大大提升了数据的处理速度。用户可以根据实际情况自由配置超时时间。

24.此方法已应用于多型设备的工程实践中,有效地提高了设备的实时处理能力,具有很高的参考价值。

25.尽管本发明的实施方案已公开如上,但其并不仅仅限于说明书和实施方式中所列运用,它完全可以被适用于各种适合本发明的领域,对于熟悉本领域的人员而言,可容易地

实现另外的修改,因此在不背离权利要求及等同范围所限定的一般概念下,本发明并不限于特定的细节和这里示出与描述的图例。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。