技术特征:

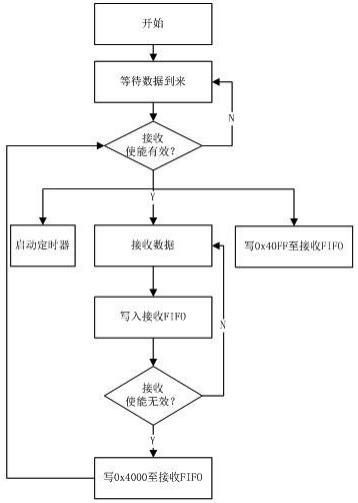

1.基于fpga的低时延数据处理方法,其特征在于,包括以下步骤:fpga处理单元检测接收使能信号是否有效,当所述接收使能信号有效时向接收fifo存储器中写入帧同步符syn,并将数据写入所述接收fifo存储器中;fpga处理单元检测接收使能信号是否有效,当所述接收使能信号无效时向所述接收fifo存储器中写入帧结束符end,记录为一帧;预先设定帧数阈值,当接收到的数据帧数达到所述帧数阈值时,所述数据处理单元读取所述接收fifo存储期内的数据并进行处理,并将处理后的数据通过所述fpga处理单元写入发送fifo存储器;fpga处理单元在处理后的数据中检测到发送标识符send_en时,从所述发送fifo存储器中调取所述处理后的数据进行发送;或者所述fpga处理单元在向所述接收fifo存储器中写入帧同步符时启动定时器开始计时并将其作为处理时间;预先设定一处理时间阈值,当所述处理时间达到所述处理时间阈值时,所述fpga处理单元从所述发送fifo处理器中调取所述处理后的数据进行发送。2.如权利要求1所述的基于fpga的低时延数据处理方法,其特征在于,所述fpga处理单元将数据写入所述接收fifo存储器时,所述接收fifo存储器的读写数据位宽的最高bit位用于指示数据有效性,1为无效,0位有效;次高bit位及低8bit相结合指示syn和end;最高bit和次高bit都为0时,低8bit指示为数据。3.如权利要求2所述的基于fpga的低时延数据处理方法,其特征在于,所述接收fifo存储器的读写数据位宽为16bit, syn定义为0x40ff,end定义为0x4000,无效数据定义为0x8000,有效数据定义为0x00xx。4.如权利要求1所述的基于fpga的低时延数据处理方法,其特征在于,所述数据处理单元处理数据包括:从所述接收fifo存储器中读取数据,将syn和end之间的无效数据丢弃,有效数据拷贝至缓存buf存储器处理,处理完写入发送fifo存储器;写入最后一个数据后,向fpga处理单元写入发送标识符send_en。

技术总结

本发明提供一种基于FPGA的低时延数据处理方法,其包括以下步骤:FPGA处理单元检测接收使能信号是否有效,当接收使能信号有效时向接收FIFO存储器中写入帧同步符SYN,并将数据写入接收FIFO存储器中;FPGA处理单元检测接收使能信号是否有效,当接收使能信号无效时向接收FIFO存储器中写入帧结束符END,记录为一帧;预先设定帧数阈值,当接收到的数据帧数达到所述帧数阈值时,数据处理单元读取接收FIFO存储期内的数据并进行处理,并将处理后的数据通过FPGA处理单元写入发送FIFO存储器。本发明提供的基于FPGA的低时延数据处理方法,软、硬件协同,流水分割,使用FPGA实现收/发分帧、定时发送、指令发送与软件数据并行处理,尽可能地提升了数据处理速度。升了数据处理速度。升了数据处理速度。

技术研发人员:李云飞 王秋生 周建锋 周凯

受保护的技术使用者:山西银河电子设备厂

技术研发日:2020.08.05

技术公布日:2022/2/18

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。