1.本公开涉及一种半导体装置及该半导体装置的制造方法,并且更具体地,涉及一种三维半导体装置及该三维半导体装置制造方法。

背景技术:

2.半导体存储器装置包括能够存储数据的存储器单元。三维半导体存储器装置包括以三维形式布置的存储器单元,从而减小了基板的每单位面积被存储器单元占用的面积。

3.为了提高三维半导体存储器装置的集成度,可以增加存储器单元的层叠数量。随着存储器单元的层叠数量的增加,三维半导体存储器装置的操作可靠性可能降低。

技术实现要素:

4.根据本公开的实施方式的半导体装置可以包括:层叠体,其包括彼此交替层叠的绝缘图案和导电图案;沟道层,其包括从层叠体突出的第一沟道部分和在层叠体中的第二沟道部分,并且穿过层叠体;以及导电线路,其围绕第一沟道部分,并且第一沟道部分可以包括金属硅化物。

5.根据本公开的实施方式的半导体装置可以包括:层叠体,其包括彼此交替层叠的绝缘图案和导电图案;沟道层,其包括从层叠体突出的第一沟道部分和在层叠体中的第二沟道部分,并且穿过层叠体;以及导电线路,其围绕第一沟道部分,并且第一沟道部分、第二沟道部分和导电线路可以包括不同的材料。

6.根据本公开的实施方式的制造半导体装置的方法可以包括以下步骤:形成支撑结构;在支撑结构上形成层叠体;形成穿过层叠体的沟道层;去除支撑结构以暴露沟道层的第一突出部;形成与第一突出部接触的扩散金属层;执行热处理以将第一突出部改变为第一沟道部分;以及去除扩散金属层。

7.根据本公开的实施方式的制造半导体装置的方法可以包括以下步骤:形成支撑结构;在支撑结构上形成层叠体;形成穿过层叠体的沟道层;去除支撑结构以暴露沟道层的第一突出部的上表面和侧壁;形成覆盖第一突出部的上表面和侧壁的扩散金属层;以及执行热处理以将第一突出部改变为第一沟道部分。

附图说明

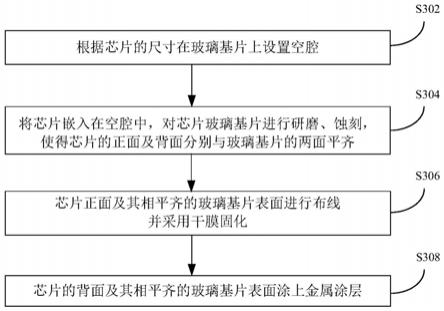

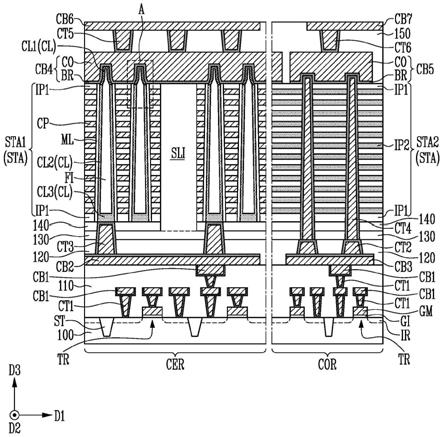

8.图1a是根据本公开的实施方式的半导体装置的截面图。

9.图1b是图1a的区域a的放大图。

10.图2、图3、图4、图5、图6、图7、图8、图9、图10a、图11a、图12a、图13a、图14a和图15是示出根据图1a和图1b的半导体装置的制造方法的截面图。

11.图10b是图10a的区域b的放大图。

12.图11b是图11a的区域c的放大图。

13.图12b是图12a的区域d的放大图。

14.图13b是图13a的区域e的放大图。

15.图14b是图14a的区域f的放大图。

16.图16是示出根据本公开的实施方式的存储器系统的配置的框图。

17.图17是示出根据本公开的实施方式的计算系统的配置的框图。

具体实施方式

18.在本说明书或本技术中公开的对根据构思的实施方式的具体结构或功能描述仅为描述根据本公开的构思的实施方式而进行说明。根据本公开的构思的实施方式可以以各种形式来执行,并且不应被解释为限于本说明书或申请中描述的实施方式。

19.将理解,尽管术语第一、第二和第三等可能在本文中被用于描述各种元件、组件、区域、层和/或部分,但是这些元件、组件、区域、层和/或部分不应受到这些术语的限制。这些术语仅用于区分一个元件、组件、区域、层或部分与另一区域、层或部分。因此,在不脱离本公开的教导的情况下,下面讨论的第一元件、组件、区域、层或部分可以被称为第二元件、组件、区域、层或部分。

20.将理解的是,当一个元件或层被称为被另一元件或层“围绕”、被另一元件或层“覆盖”、“在”另一元件或层“上”、“连接至”另一元件或层、“联接至”另一元件或层或“与另一元件或层接触”时,它可以直接在另一个元件或层上、与其连接、与其联接、被其覆盖、被其围绕或与其接触,或者可以存在中间元件或层。相反,当一个元件被称为“直接”被另一元件或层“围绕”、“直接”在另一元件或层“上”、“直接连接至”另一元件或层、“直接被”另一元件或层“覆盖”或“直接联接至”另一元件或层时,不存在中间元件或层。贯穿全文,相似的附图标记表示相似的元件。

21.本公开的实施方式提供了一种能够提高操作可靠性的半导体装置和该半导体装置的制造方法。

22.在根据本技术的实施方式的半导体装置中,沟道层的与导电线路接触的部分可以由金属硅化物形成,并且因此,导电线路可以由金属材料形成。

23.图1a是根据本公开的实施方式的半导体装置的截面图。图1b是图1a的区域a的放大图。

24.参照图1a和图1b,半导体装置可以包括单元区域cer和连接区域cor。单元区域cer和连接区域cor可以是在平面上划分的区域。

25.半导体装置可以包括基板100。基板100可以具有沿着由第一方向dl和第二方向d2限定的平面延伸的板的形状。第一方向d1和第二方向d2可以彼此相交。例如,第一方向d1和第二方向d2可以彼此正交。基板100可以从单元区域cer延伸至连接区域cor。例如,基板100可以在第一方向d1上延伸。基板100可以包括半导体材料。例如,基板100可以包括硅。

26.第一绝缘层110可以被设置在基板100上。第一绝缘层110可以覆盖基板100。第一绝缘层110可以包括绝缘材料。例如,第一绝缘层110可以包括氧化物。

27.外围晶体管tr可以被设置在基板100和第一绝缘层110之间。外围晶体管tr可以是构成半导体装置的外围电路的晶体管。

28.外围晶体管tr可以包括杂质区域ir、栅极绝缘层gi和栅极gm。杂质区域ir可以被设置在基板100中。可以通过将杂质掺杂到基板100中来形成杂质区域ir。外围晶体管tr的

沟道可以形成在杂质区域ir之间。栅极gm可以利用插置在其间的栅极绝缘层gi与基板100间隔开。栅极gm可以包括导电材料,并且栅绝缘层gi可以包括绝缘材料。

29.元件隔离层st可以被设置在基板100中。元件隔离层st可以将构成外围电路的外围晶体管tr彼此电隔离。元件隔离层st可以包括绝缘材料。

30.第一接触部(contact)ct1和第一导体(conductor)cb1可以被设置在第一绝缘层110中。外围晶体管tr的栅极gm和杂质区域ir可以与第一接触部ct1接触。第一接触部ct1和第一导体cb1可以电连接至外围晶体管tr。第一接触部ct1和第一导体cb1中的每一个可以包括导电层和围绕导电层的屏障层。例如,导电层可以包括铜、钨或铝。例如,屏障层可以包括钛、氮化钛、钽或氮化钽。第一接触部ct1的宽度可以随着第一接触部ct1靠近外围晶体管tr而减小。第一接触部ct1可以在第三方向d3上延伸。第三方向d3可以与第一方向d1和第二方向d2相交。例如,第三方向d3可以与第一方向d1和第二方向d2正交。

31.第二绝缘层120可以被设置在第一绝缘层110上。第二绝缘层120可以覆盖第一绝缘层110。第二绝缘层120可以包括绝缘材料。例如,第二绝缘层120可以包括氧化物。

32.第二导体cb2、第三导体cb3和第二接触部ct2可以被设置在第二绝缘层120中。第二导体cb2可以被设置在单元区域cer中。第二导体cb2可以与被设置在单元区域cer中的第一导体cb1接触。第二导体cb2可以是在第一方向d1上延伸的导电线路。第二导体cb2可以被用作半导体装置的位线。

33.第三导体cb3可以被设置在连接区域cor中。第三导体cb3可以与被设置在连接区域cor中的第一导体cb1接触。

34.第二接触部ct2可以与第三导体cb3接触。第二接触部ct2可以被设置在连接区域cor中。第二接触部ct2可以在第三方向d3上延伸。第二接触部ct2的宽度可以随着第二接触部ct2靠近外围晶体管tr而增大。

35.第二导体cb2和第三导体cb3以及第二接触部ct2中的每一个可以包括导电层和屏障层。

36.第三绝缘层130可以被设置在第二绝缘层120上。第三绝缘层130可以覆盖第二绝缘层120。第三绝缘层130可以包括绝缘材料。例如,第三绝缘层130可以包括氧化物。

37.第四绝缘层140可以被设置在第三绝缘层130上。第四绝缘层140可以覆盖第三绝缘层130。第四绝缘层140可以包括绝缘材料。例如,第四绝缘层140可以包括氧化物。

38.第三接触部ct3可以被设置在第二至第四绝缘层120、130和140中。第三接触部ct3可以穿过第三绝缘层130和第四绝缘层140。第三接触部ct3可以与第二导体cb2接触。第三接触部ct3可以被设置在单元区域cer中。每个第三接触部ct3可以包括导电层和屏障层。第三接触部ct3可以在第三方向d3上延伸。第三接触部ct3的宽度可以随着第三接触部ct3靠近外围晶体管tr而增大。

39.层叠体(stack)sta可以被设置在第四绝缘层140上。层叠体sta可以包括单元区域cer中的第一层叠部分sta1和连接区域cor中的第二层叠部分sta2。

40.第一层叠部分sta1可以包括在第三方向d3上彼此交替层叠的第一绝缘图案ip1和导电图案cp。第一绝缘图案ip1可以包括绝缘材料。例如,第一绝缘图案ip1可以包括氧化物。导电图案cp可以包括栅极导电层。栅极导电层可以包括导电材料。例如,栅极导电层可以包括掺杂硅层、金属硅化物层、钨、镍和钴中的至少一者。栅极导电层可以被用作连接至

存储器单元的字线或连接至选择晶体管的选择线。第一层叠部分sta1的导电图案cp还可以包括围绕栅极导电层的栅极屏障层。例如,栅极屏障层可以包括钛、氮化钛、钽或氮化钽。

41.第二层叠部分sta2可以包括在第三方向d3上彼此交替层叠的第一绝缘图案ip1和第二绝缘图案ip2。第一绝缘图案ip1可以包括绝缘材料。例如,第一绝缘图案ip1可以包括氧化物。第二绝缘图案ip2可以包括与第一绝缘图案ip1的材料不同的材料。例如,第二绝缘图案ip2可以包括氮化物。

42.第二层叠部分sta2的第一绝缘图案ip1可以与第一层叠部分sta1的第一绝缘图案ip1被设置在相同的水平处。第二层叠部分sta2的第一绝缘图案ip1和第一层叠部分sta1的第一绝缘图案ip1可以无边界地连续(successively)形成。第二层叠部分sta2的第二绝缘图案ip2可以与第一层叠部分sta1的导电图案cp被设置在相同的水平处。

43.可以设置穿过层叠体sta的第一层叠部分sta1的填充层fi。填充层fi可以在第三方向d3上延伸。填充层fi可以穿过层叠体sta的第一层叠部分sta1的第一绝缘图案ip1和导电图案cp。层叠体sta的第一层叠部分sta1的第一绝缘图案ip1和导电图案cp可以围绕填充层fi。填充层fi可以包括绝缘材料。例如,填充层fi可以包括氧化物。

44.可以设置穿过层叠体sta的第一层叠部分sta1的沟道层cl。沟道层cl可以在第三方向d3上延伸。沟道层cl可以穿过层叠体sta的第一层叠部分sta1的第一绝缘图案ip1和导电图案cp。层叠体sta的第一层叠部分sta1的第一绝缘图案ip1和导电图案cp可以围绕沟道层cl。沟道层cl可以围绕填充层fi。

45.沟道层cl可以通过第三接触部ct3连接至第二导体cb2。半导体装置可以包括图1a所示的第三接触部ct3和第二导体cb2,并且可以包括图1a中未示出的第三接触部和第二导体。未连接至图1a所示的第三接触部ct3和第二导体cb2的沟道层cl可以连接至图1a中未示出的第三接触部和第二导体。沟道层cl可以通过第三接触部ct3、第二导体cb2、第一导体cb1和第一接触部ct1电连接至外围晶体管tr。

46.沟道层cl可以包括从层叠体sta的第一层叠部分sta1突出的第一沟道部分cl1,以及在层叠体sta的第一层叠部分sta1中的第二沟道部分cl2和第三沟道部分cl3。第一沟道部分cl1可以是在层叠体sta的第一层叠部分sta1上方突出的部分。第一沟道部分cl1可以是围绕填充层fi的侧壁的部分。第三沟道部分cl3可以是在层叠体sta的第一层叠部分sta1下方与第三接触部ct3接触的部分。第三沟道部分cl3可以是覆盖填充层fi的下表面的部分。第二沟道部分cl2可以是在第一沟道部分cl1和第三沟道部分cl3之间连接第一沟道部分cl1和第三沟道部分cl3的部分。第二沟道部分cl2可以在第三方向d3上延伸并且穿过多个导电图案cp和第一绝缘图案ip1。第二沟道部分cl2可以是围绕填充层fi的侧壁的部分。

47.第一沟道部分cl1可以包括与第二沟道部分cl2和第三沟道部分cl3的材料不同的材料。第二沟道部分cl2和第三沟道部分cl3可以包括多晶硅。第一沟道部分cl1可以包括金属硅化物。例如,第一沟道部分cl1可以包括可以在450℃或更低的温度下形成的金属硅化物。例如,第一沟道部分cl1可以包括可以通过在450℃或更低的温度下结合金属和硅而形成的金属硅化物。例如,第一沟道部分cl1可以包括硅化镍。例如,包括在第一沟道部分cl1中的硅化镍的成分可以是nisi。第一沟道部分cl1和第二沟道部分cl2可以形成欧姆接触(ohmic contact)。

48.可以设置穿过层叠体sta的第一层叠部分sta1的存储器层ml。存储器层ml可以在

第三方向d3上延伸。存储器层ml可以穿过层叠体sta的第一层叠部分sta1的第一绝缘图案ip1和导电图案cp。层叠体sta的第一层叠部分sta1的第一绝缘图案ip1和导电图案cp可以围绕存储器层ml。存储器层ml可以围绕沟道层cl的第二沟道部分cl2和第三沟道部分cl3。

49.存储器层ml可以包括围绕沟道层cl的隧道绝缘层、围绕隧道绝缘层的数据储存层以及围绕数据储存层的阻挡层。隧道绝缘层可以包括能够进行电荷隧穿的材料。例如,隧道绝缘层可以包括氧化物。在一个实施方式中,数据储存层可以包括能够捕获(trapping)电荷的材料。例如,数据储存层可以包括氮化物。在另一实施方式中,根据数据储存方法,数据储存层可以包括各种材料。例如,数据存储层可以包括硅、相变材料或纳米点。阻挡层可以包括能够阻挡电荷移动的材料。例如,阻挡层可以包括氧化物。

50.可以设置穿过第三绝缘层130、第四绝缘层140和层叠体sta的第二层叠部分sta2的第四接触部ct4。第四接触部ct4可以在第三方向d3上延伸。第四接触部ct4可以穿过层叠体sta的第二层叠部分sta2的第一绝缘图案ip1和第二绝缘图案ip2。层叠体sta的第二层叠部分sta2的第一绝缘图案ip1和第二绝缘图案ip2可以围绕第四接触部ct4。第四接触部ct4的一部分可以在层叠体sta的第二层叠部分sta2上方突出。第四接触部ct4可以包括导电层和屏障层。第四接触部ct4可以与第二接触部ct2接触。

51.可以设置穿过第四绝缘层140和层叠体sta的第一层叠部分sta1的狭缝绝缘层sli。狭缝绝缘层sli可以在第二方向d2和第三方向d3上延伸。狭缝绝缘层sli可以穿过层叠体sta的第一层叠部分sta1的第一绝缘图案ip1和导电图案cp。狭缝绝缘层sli的两侧的导电图案cp可以通过狭缝绝缘层sli在第一方向d1上彼此间隔开。狭缝绝缘层sli的两侧的第一绝缘图案ip1可以通过狭缝绝缘层sli在第一方向d1上彼此间隔开。

52.狭缝绝缘层sli可以与第三绝缘层130包括相同的材料。例如,狭缝绝缘层sli可以包括氧化物。狭缝绝缘层sli可以与第三绝缘层130无边界地连续地形成。

53.可以设置覆盖层叠体sta的第一层叠部分sta1的第四导体cb4。第四导体cb4可以从单元区域cer延伸至连接区域cor。第四导体cb4可以是在第一方向d1上延伸的导电线路。第四导体cb4可以用作半导体装置的源极线。第四导体cb4可以与沟道层cl的第一沟道部分cl1接触。第四导体cb4可以围绕沟道层cl的第一沟道部分cl1。第四导体cb4可以包括与第一沟道部分cl1和第二沟道部分cl2的材料不同的材料。在一个实施方式中,第四导体cb4可以与第一沟道部分cl1直接接触。在一个实施方式中,第四导体cb4可以与第一沟道部分cl1的第二部分cl1b直接接触。在一个实施方式中,第四导体cb4的屏障层br可以与第一沟道部分cl1直接接触。在一个实施方式中,第四导体cb4的屏障层br可以与第一沟道部分cl1的第二部分cl1b直接接触。在一个实施方式中,第一部分cl1a可以与第二沟道部分cl2直接接触。在一个实施方式中,第二部分cl1b与第二沟道部分cl2间隔开。

54.第四导体cb4可以包括导电层co和屏障层br。导电层co和屏障层br可以包括不同的材料。导电层co可以包括与包括在屏障层br中的金属不同的金属。例如,导电层co可以包括铜、钨或铝。例如,屏障层br可以包括钛、氮化钛、钽或氮化钽。

55.第四导体cb4的屏障层br可以覆盖沟道层cl的第一沟道部分cl1。第四导体cb4的屏障层br可以与沟道层cl的第一沟道部分cl1接触。第四导体cb4的导电层co可以利用插置在其间的第四导体cb4的屏障层br与层叠体sta和沟道层cl的第一沟道部分cl1间隔开。

56.第五导体cb5可以被设置在层叠体sta的第二层叠部分sta2上。第五导体cb5可以

被设置在连接区域cor中。第五导体cb5可以与第四接触部ct4接触。第五导体cb5可以包括导电层co和屏障层br。第五导体cb5的屏障层br可以与第四接触部ct4接触。第五导体cb5的导电层co可以利用插置在其间的第五导体cb5的屏障层br与层叠体sta和第四接触部ct4间隔开。

57.可以设置覆盖第四导体cb4和第五导体cb5的第五绝缘层150。第五绝缘层150的一部分可以被设置在第四导体cb4和第五导体cb5之间。第四导体cb4和第五导体cb5可以通过第五绝缘层150在第一方向d1上彼此间隔开。第四导体cb4和第五导体cb5可以通过第五绝缘层150彼此电分离。第五绝缘层150可以包括绝缘材料。例如,第五绝缘层150可以包括氧化物。

58.第五接触部ct5和第六接触部ct6可以被设置在第五绝缘层150中。第五接触部ct5可以与第四导体cb4接触。第五接触部ct5可以被设置在单元区域cer中。第五接触部ct5可以在第三方向d3上延伸。第五接触部ct5的宽度可以随着第五接触部ct5靠近层叠体sta和外围晶体管tr而减小。

59.第六接触部ct6可以与第五导体cb5接触。第六接触部ct6可以被设置在连接区域cor中。第六接触部ct6可以在第三方向d3上延伸。第六接触部ct6的宽度可以随着第六接触部ct6靠近层叠体sta和外围晶体管tr而减小。第五接触部ct5和第六接触部ct6中的每一个可以包括导电层和屏障层。

60.第六导体cb6和第七导体cb7可以被设置在第五绝缘层150中。第六导体cb6可以与第五接触部ct5接触。第六导体cb6可以被设置在单元区域cer中。第六导体cb6可以在第一方向d1上延伸。例如,第六导体cb6可以包括铝。

61.第七导体cb7可以与第六接触部ct6接触。第七导体cb7可以被设置在连接区域cor中。第七导体cb7可以在第一方向d1上延伸。例如,第七导体cb7可以包括铝。

62.沟道层cl可以通过第四导体cb4和第五接触部ct5电连接至第六导体cb6。连接区域cor中的外围晶体管tr可以通过第一接触部ct1、第一导体cb1、第三导体cb3、第二接触部ct2、第四接触部ct4、第五导体cb5和第六接触部ct6而电连接至第七导体cb7。

63.参照图1b,沟道层cl的第一沟道部分cl1可以包括在层叠体sta的第一层叠部分sta1中的第一部分cl1a和在第四导体cb4中的第二部分cl1b。第一沟道部分cl1的第一部分cl1a可以被层叠体sta的第一层叠部分sta1围绕。第一沟道部分cl1的第二部分cl1b可以被第四导体cb4围绕。第一沟道部分cl1的第一部分cl1a和第二部分cl1b之间的边界的水平可以与层叠体sta的第一层叠部分sta1和第四导体cb4之间的边界的水平相同。第一沟道部分cl1的第二部分cl1b可以在层叠体sta的第一层叠部分sta1上方突出。第二沟道部分cl2和第一沟道部分cl1的第一部分cl1a之间的边界的水平可以低于层叠体sta的第一层叠部分sta1和第四导体cb4之间的边界的水平。第一沟道部分cl1的第二部分cl1b可以包括第一外壁sw1和第一上表面to1。

64.第四导体cb4的屏障层br可以包括与沟道层cl的第一沟道部分cl1接触的结部分(junction portion)br_c。结部分br_c可以围绕第一沟道部分cl1。结部分br_c可以沿着第一沟道部分cl1的表面形成。结部分br_c可以与第一沟道部分cl1的第二部分cl1b的第一外壁sw1和第一上表面to1接触。结部分br_c可以共形地形成在第一沟道部分cl1的第二部分cl1b的第一外壁sw1和第一上表面to1上。结部分br_c可以包括第二外壁sw2和第二上表面

to2。第四导体cb4的屏障层br可以包括与沟道层cl的第一沟道部分cl1和第二沟道部分cl2的材料不同的材料。

65.第四导体cb4的导电层co可以围绕结部分br_c。第四导体cb4的导电层co可以与结部分br_c的第二上表面to2和第二外壁sw2接触。第四导体cb4的导电层co可以包括与第四导体cb4的屏障层br、第一沟道部分cl1和第二沟道部分cl2的材料不同的材料。

66.填充层fi可以包括在第一沟道部分cl1中的第一填充部分fi1和在第二沟道部分cl2中的第二填充部分fi2。第一填充部分fi1可以被第一沟道部分cl1围绕。第二填充部分fi2可以被第二沟道部分cl2围绕。第一填充部分fi1的宽度可以小于第二填充部分fi2的宽度。第一填充部分fi1在第一方向d1上的宽度可以小于第二填充部分fi2在第一方向d1上的宽度。

67.第四导体cb4的导电层co的下表面可以凹入以限定第一凹部rc1。由第一凹部rc1限定的空间可以具有宽度不均匀的圆柱形形状。第一凹部rc1可以由结部分br_c、第一沟道部分cl1和第一填充部分fi1填充。结部分br_c、第一沟道部分cl1和第一填充部分fi1可以被设置在第一凹部rc1中。

68.在根据本公开的一个实施方式的半导体装置中,因为沟道层cl的第一沟道部分cl1由金属硅化物形成并且第二沟道部分cl2由多晶硅形成,所以可以在第一沟道部分cl1和第二沟道部分cl2之间形成欧姆接触。因此,不需要在第一沟道部分cl1和第四导体cb4的屏障层br之间形成欧姆接触,并且因此,第四导体cb4的屏障层br可以在不进行高温热处理的情况下直接形成在第一沟道部分cl1上。

69.在根据本公开的一个实施方式的半导体装置中,由于用作沟道层cl的结交叠区域(junction overlap region)的第一沟道部分cl1由金属硅化物形成,所以可以在不进行高温热处理的情况下形成沟道层cl的结交叠区域,并且可以防止由于高温热处理导致的选择晶体管的劣化而导致选择晶体管的特性改变。

70.在根据本公开的一个实施方式的半导体装置中,用作沟道层cl的结交叠区域的第一沟道部分cl1由金属硅化物形成。因此,与由多晶硅形成的沟道层中的晶界(grain boundary)相比,第一沟道部分cl1中的晶界可以相对较小。此外,第一沟道部分cl1可以被形成为具有均匀的厚度。因此,可以均匀地形成第一沟道部分cl1和第二沟道部分cl2之间的边界的水平。第一沟道部分cl1和第二沟道部分cl2之间的边界的水平可以被形成使得第一沟道部分cl1和第二沟道部分cl2之间的边界与选择线相邻,并且第一沟道部分cl1和第二沟道部分cl2之间的边界不与选择线水平交叠。因此,由于选择线与第一沟道部分cl1之间的距离可以是均匀的,所以可以生成相对均匀的单元电流,并且选择晶体管的特性可以是均匀的。

71.图2、图3、图4、图5、图6、图7、图8、图9、图10a、图11a、图12a、图13a、图14a和图15是示出根据图1a和图1b的半导体装置的制造方法的截面图。图10b是图10a的区域b的放大图。图11b是图11a的区域c的放大图。图12b是图12a的区域d的放大图。图13b是图13a的区域e的放大图。图14b是图14a的区域f的放大图。

72.为了简要描述,相同的附图标记被用于已参照图1a和图1b描述的组件,并且省略重复的描述。

73.以下描述的制造方法仅仅是根据图1a和图1b的半导体装置的制造方法的一个实

施方式,并且,根据图1a和图1b的半导体装置的制造方法不限于下述制造方法。

74.参照图2,可以形成支撑结构200。支撑结构200可以具有沿着由第一方向d1和第二方向d2限定的平面扩展的板的形状。支撑结构200可以包括针对氧化物和氮化物具有蚀刻选择性的材料。例如,支撑结构200可以包括硅。

75.层叠体sta可以形成在支撑结构200上。层叠体sta可以包括在第三方向d3上交替层叠的第一层叠绝缘层il1和第二层叠绝缘层il2。第一层叠绝缘层il1可以包括绝缘材料。例如,第一层叠绝缘层il1可以包括氧化物。第二层叠绝缘层il2可以包括与第一层叠绝缘层il1的材料不同的材料。例如,第二层叠绝缘层il2可以包括氮化物。

76.参照图3,可以形成在单元区域cer中穿过层叠体sta的存储器层ml、沟道层cl和填充层fi。形成存储器层ml、沟道层cl和填充层fi的步骤可以包括在单元区域cer中形成穿过层叠体sta的第一孔ho1,以及在第一孔ho1中形成存储器层ml、沟道层cl和填充层fi。

77.当形成穿过层叠体sta的第一孔ho1时,可以对第一层叠绝缘层il1和第二层叠绝缘层il2进行图案化。经图案化的第一层叠绝缘层il1和第二层叠绝缘层il2可以被定义为第一绝缘图案ip1和第二绝缘图案ip2。

78.第一孔ho1的最下部分可以被设置在支撑结构200中。第一孔ho1的最下部分可以被支撑结构200围绕。存储器层ml、沟道层cl和填充层fi中的每一个的一部分可以被设置在支撑结构200中。存储器层ml、沟道层cl和填充层fi中的每一个的上述一部分可以被支撑结构200围绕。

79.随后,第四绝缘层140可以形成在层叠体sta上。第四绝缘层140可以覆盖存储器层ml和沟道层cl。

80.参照图4,单元区域cer中的第二绝缘图案ip2可以被导电图案cp代替,并且可以形成狭缝绝缘层sli和第三绝缘层130。

81.例如,可以形成在单元区域cer中穿过层叠体sta的狭缝sl,并且可以去除通过狭缝sl暴露的第二绝缘图案ip2。导电图案cp可以形成在去除了第二绝缘图案ip2的空的空间中。

82.连接区域cor中的第二绝缘图案ip2可以不被导电图案cp代替并且可以保留。层叠体sta的包括导电图案cp和第一绝缘图案ip1的部分可以被定义为第一层叠部分sta1。层叠体sta的包括第一绝缘图案ip1和第二绝缘图案ip2的部分可以被定义为第二层叠部分sta2。

83.在形成导电图案cp之后,可以形成狭缝绝缘层sli和第三绝缘层130。狭缝绝缘层sli和第三绝缘层130可以通过沉积一种沉积材料而同时形成。在形成狭缝绝缘层sli和第三绝缘层130之后,可以对第三绝缘层130的上表面进行抛光。

84.参照图5,可以形成穿过层叠体sta的第二层叠部分sta2、第四绝缘层140和第三绝缘层130的第四接触部ct4。形成第四接触部ct4的步骤可以包括以下步骤:形成穿过层叠体sta的第二层叠部分sta2、第四绝缘层140和第三绝缘层130的第二孔ho2,以及在第二孔ho2中形成第四接触部ct4。第二孔ho2的最下部分可以被设置在支撑结构200中。第二孔ho2的最下部分可以被支撑结构200围绕。第四接触部ct4的一部分可以被设置在支撑结构200中。第四接触部ct4的上述一部分可以被支撑结构200围绕。

85.参照图6,第二绝缘层120可以形成在第三绝缘层130上。可以形成连接至第四接触

部ct4的第二接触部ct2和连接至沟道层cl的第三接触部ct3。可以形成连接至第二接触部ct2的第三导体cb3和连接至第三接触部ct3的第二导体cb2。

86.参照图7,可以在基板100上形成外围晶体管tr、第一绝缘层110、第一接触部ct1和第一导体cb1。

87.参照图8,可以执行晶圆接合工艺。晶圆接合工艺可以包括以下步骤:翻转(inverting)支撑结构200,在单元区域cer中接合第二导体cb2和第一导体cb1,在连接区域cor中接合第三导体cb3和第一导体cb1,并且接合第一绝缘层110和第二绝缘层120。由于在单元区域cer中第二导体cb2和第一导体cb1接合,沟道层cl可以电连接至外围晶体管tr。

88.参照图9,可以去除支撑结构200。由于支撑结构200在晶圆接合工艺中被翻转,支撑结构200可以被暴露,并且可以通过蚀刻工艺去除支撑结构200。可以通过使用能够选择性地蚀刻支撑结构200的蚀刻材料来选择性地去除支撑结构200。

89.当支撑结构200被去除时,存储器层ml的第一突出部(protrusion)pt1可以被暴露。存储器层ml的第一突出部pt1可以是在层叠体sta的第一层叠部分sta1上方突出的部分。当支撑结构200被去除时,存储器层ml的第一突出部pt1的上表面和外壁可以被暴露。当支撑结构200被去除时,第四接触部ct4的第二突出部pt2可以被暴露。第四接触部ct4的第二突出部pt2可以是在层叠体sta的第二层叠部分sta2上方突出的部分。当支撑结构200被去除时,第四接触部ct4的第二突出部pt2的上表面和外壁可以被暴露。

90.参照图10a和图10b,可以去除存储器层ml的在层叠体sta的第一层叠部分sta1上方突出的第一突出部pt1。去除存储器层ml的第一突出部pt1的步骤可以包括依次去除阻挡层的一部分、数据储存层的一部分以及隧道绝缘层的一部分。存储器层ml的第一突出部pt1被去除,并且因此沟道层cl的第三突出部pt3可以被暴露。沟道层cl的第三突出部pt3可以是在层叠体sta的第一层叠部分sta1上方突出的部分。存储器层ml的第一突出部pt1被去除,并且因此沟道层cl的第三突出部pt3的上表面和外壁可以被暴露。第三突出部pt3的被暴露的外壁可以被定义为第三外壁sw3,并且第三突出部pt3的被暴露的上表面可以被定义为第三上表面to3。沟道层cl的第三突出部pt3可以是位于比层叠体sta的第一层叠部分sta1的水平更高的水平处的部分。沟道层cl的第三突出部pt3可以被设置在比被去除了第一突出部pt1的存储器层ml的水平更高的水平处。

91.参照图11a和图11b,可以在层叠体sta上形成扩散金属层(diffusion metal layer)dml。扩散金属层dml可以包括金属材料。例如,扩散金属层dml可以包括镍铂(nickel platinum)。例如,被包括在扩散金属层dml中的镍铂的成分可以是nipt。扩散金属层dml可以包括可以扩散到沟道层cl中的元素。例如,扩散金属层dml可以包括可以扩散到沟道层cl中的镍。扩散金属层dml可以共形地形成在层叠体sta上。扩散金属层dml可以覆盖层叠体sta的第一层叠部分sta1和第二层叠部分sta2。扩散金属层dml可以覆盖第三突出部pt3和第二突出部pt2。扩散金属层dml可以通过沉积工艺形成。扩散金属层dml可以与第三突出部pt3和第二突出部pt2接触。

92.扩散金属层dml可以包括围绕沟道层cl的第三突出部pt3的覆盖部分(capping portion)cap。覆盖部分cap可以是扩散金属层dml的与沟道层cl的第三突出部pt3的第三外壁sw3和第三上表面to3接触的部分。覆盖部分cap可以沿着沟道层cl的第三突出部pt3的第三外壁sw3和第三上表面to3形成,并且因此覆盖部分cap可以具有与沟道层cl的第三突出

部pt3相对应的形状。覆盖部分cap的外壁可以被定义为第四外壁sw4,并且覆盖部分cap的上表面可以被定义为第四上表面to4。

93.参照图12a和图12b,可以形成沟道层cl的第一沟道部分cl1。沟道层cl的一部分的成分可以被改变,并且因此可以形成第一沟道部分cl1。沟道层cl的第三突出部pt3和与第三突出部pt3相邻的一部分的成分可以被改变,并且因此可以形成第一沟道部分cl1。可以将沟道层cl的除了第一沟道部分cl1之外的部分定义为第二沟道部分cl2。

94.第一沟道部分cl1可以通过热处理形成。例如,第一沟道部分cl1可以通过快速热退火(rapid thermal annealing)(rta)工艺形成。可以在290℃至450℃的温度下执行热处理。

95.可以通过热处理将包括在扩散金属层dml中的元素扩散到沟道层cl的第三突出部pt3中,并且可以形成第一沟道部分cl1。例如,包括在扩散金属层dml中的镍可以通过热处理被扩散到沟道层cl中。例如,被扩散到沟道层cl中的镍可以与沟道层cl中的硅结合,并且以此方法形成的第一沟道部分cl1可以包括硅化镍(nickel silicide)。例如,包括在第一沟道部分cl1中的硅化镍的成分可以是nisi。第一沟道部分cl1和第二沟道部分cl2可以形成欧姆接触。第二沟道部分cl2和第一沟道部分cl1之间的边界的水平可以被设置为与用作选择线的最上导电图案cp相邻。第二沟道部分cl2和第一沟道部分cl1之间的边界的水平可以被设置在低于层叠体sta的上表面的水平处。

96.在成分改变的同时,可以增大沟道层cl的一部分的体积。因此,第一沟道部分cl1可以被形成为具有大于第三突出部pt3的体积的体积。例如,第一沟道部分cl1在第一方向d1上的宽度可以大于第三突出部pt3在第一方向d1上的宽度。并且第一沟道部分cl1在第三方向d3上的长度可以大于第三突出部pt3在第三方向d3上的长度。例如,第一沟道部分cl1在第一方向d1上的厚度可以大于第二沟道部分cl2在第一方向d1上的厚度。

97.参照图13a和图13b,可以去除扩散金属层dml。当扩散金属层dml被去除时,沟道层cl的第一沟道部分cl1可以被暴露,并且第四接触部ct2的第二突出部pt2可以被暴露。当扩散金属层dml被去除时,沟道层cl的第一沟道部分cl1的第一外壁sw1和第一上表面to1可以被暴露。例如,可以通过湿法蚀刻工艺去除扩散金属层dml。

98.参照图14a和图14b,可以在层叠体sta上形成初始导体pcb。初始导体pcb可以覆盖层叠体sta的第一层叠部分sta1和第二层叠部分sta2。初始导体pcb可以覆盖沟道层cl的第一沟道部分cl1和第四接触部ct4的第二突出部pt2。初始导体pcb可以包括覆盖层叠体sta的屏障层br和覆盖屏障层br的导电层co。初始导体pcb的屏障层br可以覆盖沟道层cl的第一沟道部分cl1的第一上表面to1和第一外壁sw1。形成初始导体pcb的步骤可以包括在层叠体sta上形成屏障层br,以及在屏障层br上形成导电层co。

99.参照图15,可以形成第四导体cb4和第五导体cb5。初始导体pcb可以被分离,并且因此可以形成第四导体cb4和第五导体cb5。形成第四导体cb4和第五导体cb5的步骤可以包括在初始导体pcb上形成包括开口的掩模图案mp,以及通过使用掩模图案mp作为蚀刻屏障来蚀刻初始导体pcb。在初始导体pcb被蚀刻之后,可以去除剩余的掩模图案mp。

100.随后,可以形成覆盖第四导体cb4和第五导体cb5的第五绝缘层150(参照图1a)。随后,可以在第五绝缘层150中形成连接至第四导体cb4的第五接触部ct5(参照图1a)和第六导体cb6(参照图1a),并且,可以形成连接至第五导体cb5第六接触部ct6(参照图1a)和第七

导体cb7(参照图1a)。

101.在根据本公开的一个实施方式的半导体装置的制造方法中,由于沟道层cl的第一沟道部分cl1由金属硅化物形成并且第二沟道部分cl2由多晶硅形成,所以可以在第一沟道部分cl1和第二沟道部分cl2之间形成欧姆接触。因此,不需要在第一沟道部分cl1与第四导体cb4的屏障层br之间形成欧姆接触,并且因此,第四导体cb4的屏障层br可以在不进行高温热处理的情况下直接形成在第一沟道部分cl1上。

102.在根据本公开的一个实施方式的半导体装置的制造方法中,由于可以在不进行高温热处理的情况下形成由金属硅化物形成的第一沟道部分cl1,所以可以防止由于高温热处理导致的选择晶体管的劣化而导致选择晶体管的特性改变。

103.在根据本公开的一个实施方式的半导体装置的制造方法中,可以通过调节第一沟道部分cl1的形成条件来调节第一沟道部分cl1和第二沟道部分cl2之间的边界的水平。可以通过调节热处理的温度、调节执行热处理所持续的时间、调节包括在金属扩散层dml中的材料的成分或调节金属扩散层dml的厚度来调节第一沟道部分cl1和第二沟道部分cl2之间的边界的水平。由于第一沟道部分cl1由金属硅化物形成,因此与由多晶硅形成的沟道层中的晶界相比,第一沟道部分cl1中的晶界可以相对较小。另外,第一沟道部分cl1可以被形成为具有均匀的厚度。因此,可以均匀地形成第一沟道部分cl1和第二沟道部分cl2之间的边界的水平。第一沟道部分cl1和第二沟道部分cl2之间的边界的水平可以被形成为使得在第一沟道部分cl1和第二沟道部分cl2之间的边界与选择线相邻,并且第一沟道部分cl1和第二沟道部分cl2之间的边界不与选择线水平交叠。因此,由于选择线与第一沟道部分cl1之间的距离可以是均匀的,所以可以生成相对均匀的单元电流,并且选择晶体管的特性可以是均匀的。

104.在根据本公开的一个实施方式的半导体装置的制造方法中,扩散金属层dml中的金属可以被扩散到沟道层cl中,并且可以与沟道层cl的硅以1:1的方式结合。由于金属和硅以1:1而不是1:2或1:3的方式结合,因此可以防止硅聚集在金属周围的现象。总之,由多晶硅形成的第二沟道部分cl2的硅可以移动到由金属硅化物形成的第一沟道部分cl1,并且因此,可以防止第一沟道部分cl1和第二沟道部分cl2彼此分离的现象。

105.图16是示出根据本公开的实施方式的存储器系统的配置的框图。

106.参照图16,根据本公开的一个实施方式的存储器系统1100包括存储器装置1120和存储器控制器1110。

107.存储器装置1120可以包括根据本公开的一个实施方式的半导体装置。存储器装置1120可以是由多个闪存存储器芯片构成的多芯片封装。

108.存储器控制器1110可以被配置为控制存储器装置1120,并且可以包括静态随机存取存储器(sram)1111、中央处理单元(cpu)1112、主机接口1113、纠错码(ecc)电路1114和存储器接口1115。sram 1111被用作cpu 1112的操作存储器,cpu 1112执行用于存储器控制器1110的数据交换的整体控制操作,并且主机接口1113包括与存储器系统1100连接的主机的数据交换协议。另外,ecc电路1114检测并校正从存储器装置1120读取的数据中包括的错误,并且存储器接口1115执行与存储器装置的1120接口连接。另外,存储器控制器1110还可以包括存储用于与主机接口连接的代码数据的只读存储器(rom)等。

109.如上所述的存储器系统1100可以是其中存储器装置1120与控制器1110彼此结合

的存储器卡或固态盘(ssd)。例如,当存储器系统1100是ssd时,存储器控制器1100可以通过诸如通用串行总线(usb)、多媒体卡(mmc)、外围组件互连express(pci-e)、串行高级技术附件(sata)、并行高级技术附件(pata)、小型计算机系统接口(scsi)、增强型小型磁盘接口(esdi)和集成驱动电子设备(ide)的各种接口协议之一与外部(例如,主机)进行通信。

110.图17是示出根据本公开的实施方式的计算系统的配置的框图。

111.参照图17,根据本公开的一个实施方式的计算系统1200可以包括电连接至系统总线1260的cpu 1220、随机存取存储器(ram)1230、用户接口1240、调制解调器1250和存储器系统1210。另外,当计算系统1200是移动装置时,可以进一步包括用于向计算系统1200提供操作电压的电池,并且可以进一步包括应用芯片集、相机图像处理器(cis)和移动d-ram等。

112.存储器系统1210可以由类似于参照图16描述的存储器装置1212和存储器控制器1211构成。

113.相关申请的交叉引用

114.本技术要求于2020年8月3日在韩国知识产权局提交的韩国专利申请第10-2020-0097015号的优先权,其全部公开内容通过引用合并于此。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。