1.本发明总体上涉及半导体,并且在特定实施例中,涉及半导体设备封装件以及用于组装的方法。

背景技术:

2.因为空气不是完美的绝缘体,所以空间中可能会发生介质击穿。当被暴露于高于介电强度的电场时,诸如空气的电介质发生击穿。气体分子在导体之间的空气空间中被电离并且在导体之间产生电流。导体之间的距离也是影响击穿的因素。随着空气密度的降低,形成电离和击穿所需的电场强度降低。气体的击穿特性可以通过帕邢定律和帕邢曲线(paschen law and paschen curve)来描述。帕邢曲线是气体击穿电压与气体压力之间的关系的图形表示。根据帕邢曲线,空气击穿电压在诸如高海拔的低气压环境下下降。当借助触头而被附接在一起的半导体设备进入空间时,触头之间的空气空间可能成为具有较低击穿电压的区域。

3.电晕效应是由带电导体周围的介质(诸如空气)电离引起的局部放电。因此,当电压应力(即,电压梯度)超过临界值时,电晕放电是由绝缘系统中的瞬态气体电离引起的一种局部发射类型。电离通常仅集中在绝缘系统的电极之间的距离的一部分之上。

4.尽管电晕效应是低能量过程,但它会将绝缘体显著降级并且由于介电击穿而导致系统故障。一般来说,电晕效应/放电是高压应用(诸如》10kv的电力线)中的问题,因为它可能导致电力损失/浪费并且降低电力传输线相关部件和设备的绝缘性。在许多应用中,电晕放电是破坏性电弧问题发生的先兆,可能对电路部件造成严重损坏。电晕效应是累积性和永久性的,并且故障可能会在没有警告的情况下发生。电晕效应通常可以通过将电压应力和电场梯度最小化来避免。

5.然而,电晕放电在诸如太空和高海拔等低压环境中变得更加成问题。随着空气密度的降低,空气的介电强度也会降低,从而导致在较低电场下的介电击穿。这在高压半导体设备中可能更成问题。具体地,在高压半导体芯片中,相邻电极(例如,偏压为正/负的电极与参考接地电极之间)可能具有大的电压差。当这些设备被暴露在诸如太空或高海拔等低压环境中时,电晕放电可能会成为问题。

6.另外,针对空间应用的高压系统必须确保地面操作不会降低空间可靠性。例如,在太空部署之前,高压半导体芯片的替换零件和部件可能会在地球上存储多年,因此必须对其进行设计来防止因环境退化(诸如腐蚀)和其他现象(诸如可能发生的脱气)而导致在存储期间故障。

7.通过将相邻触头之间的间隙最大化、避免具有锋利、尖头、不光滑边缘或形状的触头以及改进触头的清洁度,可以减少高压半导体部件中的电晕放电。此外,触头之间的间隙可以利用硅或环氧树脂的“无空隙(void-free)”灌封填充来有效地增加间隙/爬电距离。通过使用具有高介电强度的表面涂层(诸如,聚对二甲苯)来包围导电表面,从而增加间隙并降低相邻触头之间的电场,对电晕放电的敏感性已被改进。用于将导体绝缘的一个现有方

法是使用硅基填充物注入管芯和衬底之间,该方法也被称为glob top。

技术实现要素:

8.根据本技术的一个实施例,半导体设备包括功率半导体设备、电路板和绝缘衬底。功率半导体设备包括接触焊盘。接触焊盘中的相邻接触焊盘被多个间隙中的一个间隙间隔开。电路板可以包括用于与功率半导体设备的接触焊盘耦合的迹线。接触焊盘可以被物理地附接到迹线。绝缘衬底被设置在电路板与功率半导体设备之间,其中绝缘衬底的部分被设置在多个间隙中,并且绝缘衬底具有单片结构。

9.根据本技术的另一实施例,半导体设备包括增强型gan功率晶体管、印刷电路板和刚性绝缘衬底。增强型gan功率晶体管被配置为在20v至1000v之间的操作电压处操作并且包括接触焊盘。印刷电路板被配置为支持操作电压,并且包括用于与增强型gan功率晶体管的接触焊盘耦合的接触表面。刚性绝缘衬底被设置在印刷电路板与增强型gan功率晶体管之间。接触焊盘借助刚性绝缘衬底中的多个通孔而被物理地附接到接触表面。

10.根据本技术的另一实施例,组装半导体设备的方法包括:将绝缘衬底放置在电路板之上;将功率半导体设备放置在电路板和绝缘衬底之上;以及将电路板和功率半导体设备加热来使得绝缘衬底固化并且使用迹线来附接接触焊盘。绝缘衬底包括绝缘材料并且是单片结构。功率半导体设备包括接触焊盘并且电路板包括迹线。接触焊盘与用于将接触焊盘附接在电路板上的迹线对准。接触焊盘中的相邻接触焊盘被多个间隙中的一个间隙间隔开。

附图说明

11.为了更完整地理解本发明及其优点,现结合附图来参考以下描述,其中:

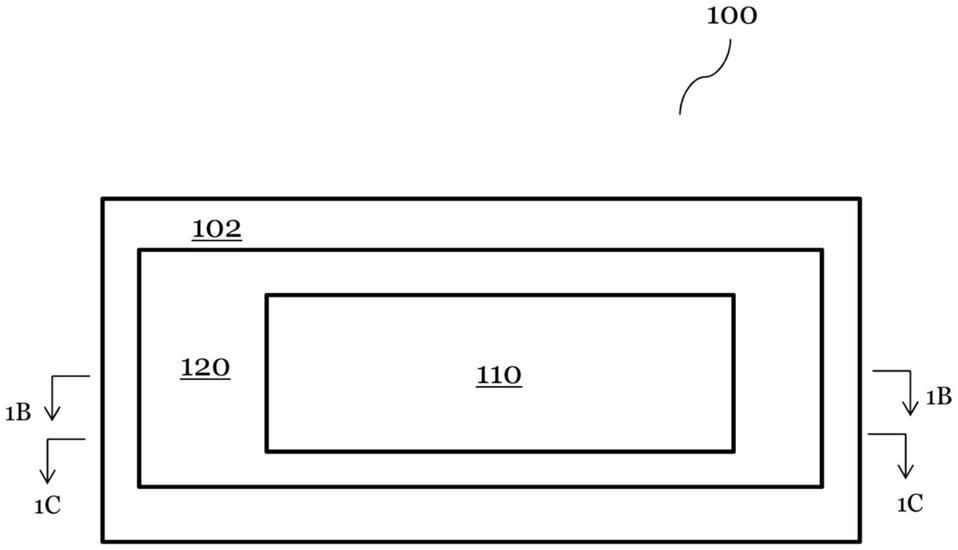

12.图1a-图1e示意性地图示了根据本公开的实施例的包括半导体设备的半导体组装件,其中图1a图示了俯视图,图1b和图1c图示了截面图,图1d是绝缘衬底的一个示例图示并且图1e是外壳的一个示例图示;

13.图2a-图2f图示了根据本公开的实施例的组装半导体设备200的过程的截面图;

14.图3a-图3d图示了功率半导体设备的实施例的俯视图,突出显示了不同的接触焊盘布置;

15.图4a-图4d图示了根据本公开的实施例的与图3a-图3d的接触焊盘布置相关联的绝缘衬底的投影视图;以及

16.图5图示了根据本公开的实施例的组装半导体设备的方法的流程图。

具体实施方式

17.以下详细讨论目前优选的实施例,包括它们的制作和使用。然而,应当理解,本技术提供了许多可应用的发明概念,这些概念可以体现在各种特定的上下文中。此处讨论的具体实施例仅描述了组装和使用本发明的具体方式。这些具体实施例不限制本发明的范围。

18.如前所述,在许多高压应用中,电晕放电是不需要的不良效应。当电流通过介质(诸如空气)从具有高电位的一个导体流到处于更低电位的另一导体时,会发生电晕放电,

从而使得导体周围的介质电离并且导致相邻导体之间的介电击穿。诸如导体之间的电位差、形状和直径以及表面不规则性的若干因素可能会影响导体的电表面梯度及其与电晕效应的关系。由于电晕效应,这些因素以及导体之间的介电击穿可能导致半导体设备不可逆转的过早老化和故障。

19.因此,需要用于防止空间应用的电晕放电效应的设备。本文中描述的本技术的各种实施例通过填充导体之间的空气空间来将相邻导体之间的电晕效应最小化或消除。减少电晕放电的一个现有方法是在触头之间注入硅基填充物。然而,由于填充物中使用的材料会脱气,因此该特殊方法可能不适合密封混合封装。

20.在各种实施例中,在正在被组装的半导体部件之间引入绝缘衬底,以使用具有较高介电强度的电介质材料来替换将被填充气体填充的空的空间。与在存储期间可能会继续脱气的填充物材料不同,绝缘衬底可以被制造为不会出现这个问题的更热力学稳定的状态。因此,本发明的各个实施例公开了可以被用于分离表面安装设备(诸如球栅阵列(bga)和线栅阵列(lga)设备)上的触头的绝缘衬底,以及将绝缘衬底组装在半导体设备上的方法。

21.将使用图1a-图1e来描述对电晕放电具有更好耐受性的半导体组装件的实施例,随后是使用图4a-图4d的备选实施例。将使用图2a-图2f和图5来描述组装该半导体组装件的各种方法。

22.图1a-图1e示意性地图示了根据本公开的实施例的包括半导体设备的半导体组装件,其中图1a图示了俯视图,图1b和图1c图示了截面图,图1d是绝缘衬底的一个示例图示并且图1e是外壳的一个示例图示。

23.参考图1a-图1c,半导体设备110可以是功率半导体设备。功率半导体设备可以被配置为在高电压处操作,在一个实施例中,电压例如在20v至600v之间或者高于20v。在某些实施例中,功率半导体设备可以被配置为在40v至200v之间的电压处操作。

24.在各种实施例中,半导体设备110可以包括由gan或者诸如碳化硅或氧化镓的其他宽带隙材料制成的半导体设备。在各种实施例中,半导体设备110包括诸如场效应晶体管的晶体管。在某些实施例中,半导体设备110包括分立场效应晶体管,诸如n沟道场效应晶体管或p沟道场效应晶体管。在一些实施例中,半导体设备110可以包括被配置为在40v至1000v之间的电压处操作的n型gan场效应晶体管。在一个实施例中,半导体设备110可以包括被配置为在20v至1000v之间的电压处操作的增强型gan功率晶体管。在一个实施例中,半导体设备110可以是硅衬底上形成的横向gan设备。

25.半导体设备110可以是半导体封装件,诸如球栅阵列封装件、连接盘网格阵列封装件(例如,没有突出焊球的bga)或者线栅阵列封装件。因此,半导体设备110可以包括半导体管芯,例如被附接到陶瓷衬底的gan半导体设备。

26.如图1b中更好地图示的,半导体设备110包括接触焊盘112,其中接触焊盘112中的相邻接触焊盘被多个间隙114中的一个间隙间隔开。在各种实施例中,半导体设备110可以包括各种接触焊盘112布置。

27.如图1a-图1c所示,半导体组装件100包括用于将半导体设备110连接到组装件的外部引线的电路板120。在某些实施例中,电路板120可以是印刷电路板并且可以包括多个金属层或厚膜。在某些实施例中,电路板120可以包括薄膜金属化衬底。电路板120可以被配

图1c和图1e所示,外壳102可以包括以密封的方式被附接到本体102b的盖102a。在各种实施例中,外壳102将半导体设备110和电路板120气密地密封与外部环境隔离。很明显,如果没有绝缘衬底130,多个间隙114将被密封在外壳102内的气体填充。换言之,绝缘衬底130替换了将接触焊盘112中的相邻接触焊盘以及迹线112中的相邻迹线间隔开的部分气体。

35.外壳102可以被气密地密封来保持气体和环境碎片远离电子部件。在各种实施例中,外壳102可以通过例如接缝密封或激光焊接来气密地密封。在一些实施例中,外壳102可以被气密地密封在包含惰性气体(诸如氮气)的室中,以使得低于阈值(诸如5000ppm)的水分水平干燥。在某些实施例中,外壳102可以被密封在具有氮气和氦气的环境(例如具有90%的n2和10%的he)中来测试气密性。氦气可以与作为示踪气体的氮气混合来检测外壳102中的泄漏。

36.外壳102还可以保护半导体组装件100免受污染、湿气、温度、辐射和腐蚀。在各种实施例中,经气密地密封的半导体组装件100可以通过保护部件免受腐蚀来延长半导体组装件100在存储期间的寿命。这样的半导体组装件100可以例如在空间中部署之前被安全地储存很多年,例如10-20年。

37.为了与外部部件接触,如图1e所示,半导体组装件100还包括延伸出外壳102的多个引线106。多个引线106可以被耦合到电路板120上的焊盘,并且在某些实施例可以被直接附接到电路板120。在一个或多个实施例中,多个引线106可以借助外壳102内的其他中间部件而被耦合到电路板120。

38.图2a-图2f图示了根据本发明的实施例的组装半导体设备200的过程的截面图。

39.图2a图示了在电路板120上对准绝缘衬底130的过程。在各种实施例中,电路板120包括混合集成电路。混合集成电路可以包括半导体设备和被导线键合或焊接到陶瓷或铍衬底的无源部件。在各种实施例中,电路板120可以包括具有连接不同金属化层的通孔的单侧、双侧或多层印刷电路板或单片集成电路。

40.电路板120包括迹线122以及被施加在迹线122之间的釉料224。在各种实施例中,迹线122包括导电金属,诸如铜、银、金或镍。迹线122可以包括在电路板120上的各种迹线之间耦合的内部通孔。釉料224可以被用于防止氧化并且防止在紧密间隔的迹线122之间形成焊桥。釉料224可以是用于在各种实施例中形成焊料掩模的材料。釉料224可以作为液体而被施加在电路板120上,液体诸如是丝网印刷到电路板120上的环氧树脂液体、液体光成像油墨、干膜光成像焊料掩模或激光直接成像。在某些实施例中,釉料224可以被对准而部分地形成在迹线122的边缘上,使得接触焊盘112的后续附接对称,同时避免短路。

41.还如图2a所示,绝缘衬底130在电路板120之上对准。绝缘衬底130是预制部件,例如,被制造为单片结构并且可以是绝缘材料。在某些实施例中,绝缘衬底130可以被模制或铸造成型,而在某些实施例中可以被3d打印为最终形式。在某些实施例中,绝缘衬底130可以是玻璃(例如,石英或氧化硅基玻璃)或陶瓷衬底,其中通孔是通过减成工艺(诸如蚀刻、冲压或用激光切割)而形成的开口。

42.在某些实施例中,在一个实施例中,绝缘衬底130可以包括诸如热固性材料的树脂。在一个实施例中,绝缘衬底130可以包括环氧树脂材料。包括树脂的绝缘衬底130可以使用诸如注射成型、3-d打印、铸造的模制工艺或者诸如激光切割或激光烧蚀的激光工艺而形成。

43.在不同的实施例中,绝缘衬底130经过热处理工艺,例如两阶段固化工艺,而达到稳定状态,在稳定状态下它可以保持数年而不会腐烂,例如,脱气或对外部环境作出反应。另外,绝缘衬底130包括能够经受与回流工艺相关的热处理工艺的材料。在各种实施例中,相关绝缘衬底可以由注入模具中以形成相关绝缘衬底的环氧树脂构成。在备选实施例中,相关绝缘衬底可以由介电强度大于3kv/mm并且在3kv/mm与10kv/mm之间的绝缘材料构成。

44.在各种实施例中,绝缘衬底130可以被对准来包围釉料224,而使得迹线122暴露。在备选实施例中,绝缘衬底130可以被对准来包围釉料224并且可以包围迹线122中的一些迹线。在一个实施例中,绝缘衬底130可以通过使用具有协调的z轴移动(在纸平面竖直)的真空抽吸工具而与拾放机对准。拾放机可以被编程为将绝缘衬底130精确地对准到电路板120并且被释放到电路板120上。

45.图2b图示了在将绝缘衬底130放置在电路板120上之后的半导体设备200。如图所示,绝缘衬底130被支撑在电路板120上。

46.图2c图示了将半导体设备110附接到绝缘衬底130和电路板120之上的过程。半导体设备110与绝缘衬底130对准,并且被布置在绝缘衬底130之上。半导体设备110包括接触焊盘112,接触焊盘112被布置在例如网格阵列和多个间隙114中。在一个实施例中(例如,在球栅阵列封装件的情况下),接触焊盘112可以包括焊球,但在另一实施例中,接触焊盘112可以包括与半导体设备110的主表面共面的平面焊盘(例如,在连接盘网格阵列封装件的情况下)。

47.因此,在该阶段,半导体设备110的接触焊盘112与电路板120的迹线122对准。在各种实施例中,半导体设备110可以与拾放机或芯片键合机系统对准,并且利用拾放机或芯片键合机系统来放置,从而将半导体设备110传送到电路板120上的精确位置。

48.图2d图示了在绝缘衬底130和半导体设备110已被放置在电路板120上之后半导体设备200的截面图。绝缘衬底130在半导体设备110的接触焊盘112之间占据多个间隙114。

49.图2e图示了如图2a-图2d的实施例中所述的将半导体设备110和绝缘衬底130附接到电路板120上的累积过程。随着半导体设备110与绝缘衬底130被组装在电路板120上,半导体设备200可以进行回流焊接来将半导体设备110的接触焊盘112键合至电路板120的迹线122,并且将绝缘衬底130键合到釉料224。回流焊接可以发生在例如回流炉中或红外灯下。在各种实施例中,真空焊接系统可以被用于将半导体设备110的接触焊盘112回流焊接并且同时将绝缘衬底130固化。在某些实施例中,附加的环氧树脂或聚合物涂层可以在回流焊接之前被引入,以填充绝缘衬底130与接触焊盘112之间的任何空隙。

50.回流焊接和固化过程包括若干阶段:预热阶段、热浸泡阶段、回流阶段和冷却阶段。在预热阶段,半导体设备200可以被加热到一致并且线性的预回流温度,以防止对部件的损坏并允许挥发性溶剂安全地脱气。半导体设备200然后经历热浸泡阶段来排出挥发性物质并用于助焊剂活化。在回流阶段,半导体设备200达到最大允许温度,以在不损坏易损部件的情况下,进行充分回流和固化。在冷却阶段,半导体设备200被逐渐冷却,以将绝缘衬底130与接触焊盘112固化至迹线122。

51.在绝缘衬底130就位的情况下,多个接触焊盘112和迹线122中的每个与多个接触焊盘112和迹线122中的下一个电隔离。换言之,相邻触头之间的路径被绝缘衬底130具有较高介电强度的区域间隔开。因此,当设备在空间中行进时,设备组装件能够将引起电晕放电

的可能性最小化。

52.图3a-图3d图示了各种半导体设备的俯视图,突出显示了接触焊盘布置,而图4a-图4d图示了根据本公开的一个实施例的相关绝缘衬底的投影图。图3a-图3d的半导体设备中的每个半导体设备可以是关于图1-图2所讨论的半导体设备110的一个实施例,而类似地,图4a-图4d的绝缘衬底中的每个绝缘衬底可以是在以上图1-图2中所讨论的绝缘衬底130的一个实施例。当然,如前所述,图1d的实施例绝缘衬底也可以与图3a-图3d的这些半导体设备一起使用。

53.整体参考图3a-图3d,如先前所讨论的,半导体设备包括由多个间隙中的一个间隙间隔开的接触焊盘。接触焊盘包括对应的接触焊盘尺寸和接触焊盘高度。多个间隙包括对应的竖直间隙间距和水平间隙间距。

54.半导体设备可以包括球栅阵列(bga)或线栅阵列(lga)设备。在一些实施例中,半导体设备可以包括各种预定义的封装尺寸,例如,3.5mm乘2mm或6.5mm乘2.3mm。接触焊盘和多个间隙可以以多种布置方式布置并且可以包括半导体设备的各种接触焊盘尺寸。

55.接触焊盘可以被布置在包括行和列的阵列中。半导体设备的中心区域中的接触焊盘与接触焊盘中沿阵列的行的第一相邻接触焊盘以及接触焊盘中沿阵列的列的第二相邻接触焊盘间隔开。多个接触焊盘与接触焊盘中的相邻接触焊盘间隔开多个间隙。在各种实施例中,多个间隙可以具有与第一相邻接触焊盘相邻的竖直间隙间距以及与第二相邻接触焊盘相邻的水平间隙间距。

56.在各种实施例中,例如,接触焊盘112可以被配置为具有针对源极和漏极的交替列,并且栅极可以被配置为位于半导体设备的角部上的单个(或几个)接触焊盘。在备选实施例中,接触焊盘可以是平行的列,平行的列由形成线栅阵列(lga)设备的每列之间的多个谷间隔开。

57.如图3a所示,第一半导体设备311包括被布置在行和列的球栅阵列中的第一接触焊盘321以及与第一接触焊盘321相邻的第一多个间隙341。第一接触焊盘321可以具有与接触焊盘的中心等距的接触焊盘尺寸331。第一多个间隙341在第一接触焊盘321的每列之间包括第一竖直间隙间距341a并且在第一接触焊盘321的每行之间包括第一水平间隙间距341b。第一竖直间隙间距341a与第一相邻接触焊盘321a相邻,并且第一竖直间隙间距341b与第二相邻接触焊盘321b相邻。第一竖直间隙间距341a和第一水平间隙间距341b可以具有相同的尺寸。

58.如图4a所示,第一相关绝缘衬底411包括由第一多个互连区域441间隔开的第一多个孔421。第一多个孔421是从第一相关绝缘衬底411的一侧完全延伸穿过而到达第一相关绝缘衬底411的另一侧的通孔。第一多个互连区域441被配置为被设置在第一半导体设备311的第一多个间隙341中。第一多个孔421根据第一接触焊盘321的布置而被布置在行和列的阵列中。

59.第一相关绝缘衬底411包括厚度431,厚度431小于第一接触焊盘321的高度,以在第一半导体设备311与第一相关绝缘衬底411接合时,将第一接触焊盘321附接到电路板上的迹线。第一相关绝缘衬底411的尺寸可以与第一半导体设备311的预定义封装尺寸相同。

60.如图3b所示,第二半导体设备312包括被布置在行和列的阵列中的第二接触焊盘322以及与第二接触焊盘322相邻的第二多个间隙342。第二接触焊盘322可以在每行或每列

中包括与相邻行或列中的接触焊盘数量不同数量的接触焊盘。第二多个间隙342在第二接触焊盘322的每列之间包括第二竖直间隙间距342a并且在第二接触焊盘322的每行之间包括第二水平间隙间距342b。第二竖直间隙间距342a和第二水平间隙间距342b可以在相邻接触焊盘之间具有不同尺寸。例如,第二竖直间隙间距342a可以大于第二水平间隙间距342b。

61.如图4b所示,第二相关绝缘衬底412包括由第二多个互连区域442间隔开的第二多个孔422。第二多个孔422是从第二相关绝缘衬底412的一侧完全延伸穿过而到达第二相关绝缘衬底412的另一侧的通孔。第二多个互连区域442被配置为被设置在第二半导体设备312的第二多个间隙342中。第二多个孔422根据第二接触焊盘332的布置而被布置在行和列的阵列中。

62.如图3c所示,第三半导体设备包括以行和列布置的第三接触焊盘323以及与第三接触焊盘323相邻的第三多个间隙343。第三接触焊盘323包括第三接触焊盘尺寸333。第三接触焊盘尺寸333可以具有细长形状。多个第三间隙343在第三接触焊盘323的每列之间包括第三竖直间隙间距343a并且在第三接触焊盘323的每行之间包括第三水平间隙间距343b。第三竖直间隙间距343a和第三水平间隙间距343b可以在相邻接触焊盘之间具有不同尺寸。第三竖直间隙间距343a可以小于第三水平间隙间距343b。

63.如图4c所示,第三相关绝缘衬底413包括第三多个孔423和第三多个互连区域443。第三多个孔423根据第三接触焊盘323的布置而布置。第三多个孔423可以具有细长形状来适应第三接触焊盘尺寸333的细长形状。第三多个孔423是从第三相关绝缘衬底413的一侧完全延伸穿过而到达第三相关绝缘衬底413的另一侧的通孔。第三多个互连区域443被配置为被设置在第三半导体设备313的第三多个间隙343中。

64.如图3d所示,第四半导体设备314包括以平行列布置的第四接触焊盘324以及与第四接触焊盘324相邻的第四多个间隙344。第四接触焊盘324可以包括具有多个接触焊盘行的列(例如第四接触焊盘324a)和单个行的接触焊盘的列(例如,第四列接触焊盘324b)。例如,第四接触焊盘324a可以被用于栅极接触,同时交替的第四列接触焊盘324b可以被用于源极或漏极接触。第四接触焊盘324可以包括多个第四接触焊盘尺寸。例如,包括多个接触焊盘行的接触焊盘列、第四接触焊盘324a可以具有第四接触焊盘尺寸334a,而单个行的接触焊盘列、第四列接触焊盘324b可以具有第四接触焊盘尺寸334b。第四多个间隙344包括第四竖直间隙间距344a和第四水平间隙间距344b。第四竖直间隙间距344a可以小于第四水平间隙间距344b。

65.如图4d所示,第四相关绝缘衬底414包括第四多个孔424和第四多个互连区域444。第四多个孔424根据图3d所示的第四接触焊盘324的布置进行布置。第四多个孔424是从第四相关绝缘衬底414的一侧完全延伸穿过而达到第四相关绝缘衬底414的另一侧的通孔。第四多个互连区域444被配置为被设置在第四半导体设备314的第四多个间隙344中。

66.图5图示了表示组装半导体组装件的方法的流程图500。

67.方法包括将绝缘衬底放置在电路板之上;将功率半导体设备放置在电路板和绝缘衬底之上;接触焊盘与电路板上的、用于功率半导体设备的迹线对准;接触焊盘中的相邻接触焊盘被多个间隙中的一个间隙间隔开;以及将电路板和功率半导体设备加热来使得绝缘衬底固化并且将接触焊盘与迹线附接。

68.在框501中,绝缘衬底如上文在各种实施例中所描述的来预制。例如,绝缘衬底被

设计为配合如图1d和图4a-图4d的示例性实施例所示的特定半导体设备封装设计。具体地,绝缘衬底包括允许特定半导体设备封装件的接触焊盘穿过的孔或沟槽。如以上各个实施例中所述,绝缘衬底可以是包括绝缘材料的预制单片结构。

69.如接下来在框503中所示,绝缘衬底与电路板对准,使得绝缘衬底中的多个孔/沟槽与电路板的接触焊盘(例如,迹线)对准。这也参考以上图2a-图2b进行了描述。因此,电路板的接触焊盘借助于绝缘衬底而暴露。

70.如接下来在框505中所示,功率半导体设备被放置在电路板和绝缘衬底之上。半导体设备包括与电路板上的迹线对准的接触焊盘。如上文所述和图2c-图2d中所示,功率半导体管芯可以被设置在电路板和绝缘衬底之上。

71.如接下来在框507中所示,电路板、绝缘衬底和半导体设备经历热处理过程。在热处理过程中,电路板、绝缘衬底和半导体设备从室温加热到大约200℃到400℃,例如250℃到350℃。在该过程期间,也如上文关于图2e所述,半导体管芯的接触焊盘中的焊料材料回流,并且与电路板的接触焊盘的材料反应而形成焊点。此外,绝缘衬底可以帮助控制焊料在电路板表面之上的流动。

72.以下提供了本技术的实施例的进一步示例。

73.示例1.一种半导体设备,包括:功率半导体设备,包括接触焊盘,接触焊盘中的相邻接触焊盘被多个间隙中的一个间隙间隔开;电路板,包括用于与功率半导体设备的接触焊盘耦合的迹线,接触焊盘被物理地附接到迹线;以及绝缘衬底,被设置在电路板与功率半导体设备之间,其中绝缘衬底的部分被设置在多个间隙中,并且绝缘衬底具有单片结构。

74.示例2.根据示例1所述的设备,还包括:外壳,电路板和功率半导体设备被设置在外壳中,外壳将功率半导体设备和电路板气密地密封从外部环境隔离。

75.示例3.根据示例1或2中任一项所述的设备,还包括:附接到电路板的低压集成电路芯片。

76.示例4.根据示例1至3中任一项所述的设备,其中功率半导体设备包括球栅阵列(bga)封装件或线栅阵列(lga)封装件。

77.示例5.根据示例1至4中任一项所述的设备,其中绝缘衬底由绝缘材料制成,绝缘材料包括大于3kv/mm的介电强度。

78.实施例6.根据示例1至5中任一项所述的设备,其中绝缘衬底由绝缘材料制成,绝缘材料包括在3kv/mm与10kv/mm之间的介电强度。

79.示例7.根据示例1至6中任一项所述的设备,其中绝缘衬底的绝缘材料包括环氧树脂材料。

80.示例8.根据示例1至7中任一项所述的设备,其中绝缘衬底的绝缘材料包括树脂或玻璃。

81.示例9.根据示例1至8中任一项所述的设备,其中接触焊盘以包括行和列的阵列而被布置,其中绝缘衬底包括多个通孔,多个通孔中的每个通孔与接触焊盘中的一个接触焊盘对准。

82.示例10.根据示例1至9中任一项所述的设备,其中接触焊盘以包括行和列的阵列而被布置,其中绝缘衬底包括多个平行沟槽,多个平行沟槽与行或列中的接触焊盘的子集对准,多个平行沟槽被多个脊中的一个脊间隔开。

83.示例11.一种半导体设备,包括:增强型gan功率晶体管,被配置为在20v至1000v之间的操作电压处操作,并且包括接触焊盘;印刷电路板,被配置为支持操作电压,并且包括用于与增强型gan功率晶体管的接触焊盘耦合的接触表面;以及刚性绝缘衬底,被设置在印刷电路板与增强型gan功率晶体管之间,接触焊盘借助刚性绝缘衬底中的多个通孔而被物理地附接到接触表面。

84.示例12.根据示例11所述的设备,还包括:外壳,印刷电路板和增强型gan功率晶体管被设置在外壳中,外壳将增强型gan功率晶体管和印刷电路板气密地密封从外部环境隔离。

85.示例13.根据示例11或12中任一项所述的设备,还包括低压集成电路芯片,附接到印刷电路板,其中增强型gan功率晶体管被配置为向低压集成电路芯片提供电源电压。

86.示例14.根据示例11至13中任一项所述的设备,其中增强型gan功率晶体管包括球栅阵列(bga)封装件或线栅阵列(lga)封装件。

87.示例15.根据示例11至14中任一项所述的设备,其中刚性绝缘衬底由绝缘材料制成,绝缘材料包括在3kv/mm与10kv/mm之间的介电强度。

88.示例16.一种组装半导体设备的方法,方法包括:将绝缘衬底放置在电路板之上,绝缘衬底包括绝缘材料并且是单片结构;将功率半导体设备放置在电路板和绝缘衬底之上,其中功率半导体设备的接触焊盘与迹线对准,所述迹线用于将功率半导体设备的接触焊盘附接到电路板上,并且其中接触焊盘中的相邻接触焊盘被多个间隙中的一个间隙间隔开;以及将电路板和功率半导体设备加热以使绝缘衬底固化,并且将接触焊盘与迹线附接。

89.示例17.根据示例16所述的方法,还包括:将电路板放置在包括本体和盖并且将盖附接的外壳中,外壳将功率半导体设备和电路板气密地密封。

90.示例18.根据示例16或17中任一项所述的设备,其中功率半导体设备和电路板被气密地密封在90%n2和10%he的气氛中。

91.示例19.根据示例16至18中任一项所述的设备,还包括:在电路板上的迹线之间沉积釉料。

92.示例20.根据示例16至19中任一项所述的设备,其中将功率半导体设备放置在电路板和绝缘衬底之上包括:使用焊料将接触焊盘附接到迹线。

93.虽然已参考例示性实施例描述了本发明,但是该描述并不旨在被解释为限制性的。参考说明书,本领域技术人员将清楚例示性实施例以及本发明的其他实施例的各种修改和组合。因此,所附权利要求旨在涵盖任何这样的修改或实施例。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。