1.本发明有关于一电子装置,特别是有关于用于软硬件协同工作的电子装置及方法。

背景技术:

2.随着人工智能(ai)的兴起,异构计算和虚拟化技术变得越来越重要,与虚拟化技术相关的地址重映射单元(remapping hardware)在计算器系统中变得不可或缺。地址重映射单元的两个主要功能为处理直接内存访问重映射(dma remapping),以及中断重映射(interrupt remapping)。为了提高转换效率,地址重映射单元将内存中的页表内容存入其内部的高速缓存(cache)。

3.当软件需要重置系统而需要将高速缓存内的原内容无效化时,由于映射关系发生了转变,需要在状态改变前将已经被重映射单元处理过的指令传送至处理器(cpu)(这些指令以旧的映射关系执行),然后再报告状态转换完成或高速缓存无效化完成。数据引流(draining)就是指重映射单元处理过但还存在于外部装置的队列中未完成,并且等待软件处理完成的指令。若引流指令的执行不彻底,可能会对系统造成不可恢复的影响。

技术实现要素:

4.依据本发明实施例的电子装置,包括一重映射硬件、一处理器,及一北桥集成电路。重映射硬件将虚拟地址转换为对应的实体地址。处理器执行一软件,用于对重映射硬件进行配置。北桥集成电路将实体地址传送给处理器。当软件变更对重映射硬件的配置时,重映射硬件输出一数据引流(draining)指令。当北桥集成电路于一第一时间点接收数据引流指令,北桥集成电路搁置第一时间点之后尚未执行的指令,直到于一第二时间点执行完成第一时间点之前正在执行的指令为止,并且于第二时间点,输出一应答指令给重映射硬件。第二时间点晚于第一时间点。重映射硬件依据应答指令,通知处理器数据引流指令的执行已完成。

5.如上所述的电子装置,还包括一外部装置,传送虚拟地址给重映射硬件。当外部装置于第一时间点接收数据引流指令,外部装置搁置该第一时间点之后尚未执行的指令,直到于一第三时间点执行完成该第一时间点之前正在执行的指令为止。于第三时间点,外部装置输出一第二应答指令给重映射硬件。第三时间点晚于第一时间点。重映射硬件直到接收到应答指令及第二应答指令,才通知处理器数据引流指令的执行已完成。

6.如上所述的电子装置,其中,在软件变更对重映射硬件的配置之后,并且在重映射硬件输出数据引流指令之前,重映射硬件检查没有尚未执行完成的另一数据引流指令。

7.如上所述的电子装置,其中,北桥集成电路通过一直接内存访问(dma)指令,将实体地址传送给处理器,并且处理器送回一确认指令给北桥集成电路作为响应。

8.如上所述的电子装置,其中,北桥集成电路包括一计数器。当北桥集成电路于第一时间点接收数据引流指令,北桥集成电路执行于第一时间点之前正在执行的指令,计数器

对第一时间点之前正在执行的指令进行计数,并且对来自处理器的响应于第一时间点之前正在执行的指令的确认指令进行计数。

9.如上所述的电子装置,其中,当北桥集成电路每执行于第一时间点之前正在执行的指令中的一个,计数器的计数加1。当北桥集成电路每接收到来自处理器响应于第一时间点之前正在执行的指令中的一个的确认指令,计数器的计数减1。当计数器的计数归零,则北桥集成电路输出应答指令给重映射硬件。

10.如上所述的电子装置,其中,当软件变更对重映射硬件的配置时,处理器输出一配置指令给重映射硬件,使得重映射硬件依据配置指令对应地输出数据引流指令给北桥集成电路及外部装置。

11.如上所述的电子装置,其中,重映射硬件包括一缓存器。缓存器至少包括一第一子缓存器及一第二子缓存器。第一子缓存器及第二子缓存器对应于相同的配置指令。处理器通过改变第一子缓存器的状态告知重映射硬件配置指令已下达。重映射硬件通过改变第二子缓存器的状态告知处理器关联于配置指令的数据引流指令已执行完成。

12.依据本发明实施例的改善软硬件协同工作的方法,适用于具有一重映射硬件、一处理器,及一北桥集成电路的一电子装置,处理器执行一软件,用于对重映射硬件进行配置;方法包括:软件改变对重映射硬件的配置;重映射硬件检查没有尚未执行完成的一先前数据引流(draining)指令;重映射硬件输出一数据引流指令给该北桥集成电路;北桥集成电路于一第一时间点接收数据引流指令;北桥集成电路搁置第一时间点之后尚未执行的指令,直到于一第二时间点执行完成第一时间点之前正在执行的指令为止;北桥集成电路于第二时间点输出一应答指令给重映射硬件,第二时间点晚于第一时间点;重映射硬件依据应答指令,通知处理器数据引流指令的执行已完成。

13.如上所述的方法,当电子装置还包括一外部装置时,方法还包括:重映射硬件输出数据引流指令给外部装置;外部装置于第一时间点接收数据引流指令;外部装置搁置第一时间点之后尚未执行的指令,直到于一第三时间点执行完成第一时间点之前正在执行的指令为止;于第三时间点,外部装置输出一第二应答指令给重映射硬件,第三时间点晚于第一时间点;重映射硬件直到接收到应答指令及第二应答指令,才通知处理器数据引流指令的执行已完成。

14.如上所述的方法,当北桥集成电路于第一时间点接收数据引流指令,方法还包括:北桥集成电路执行于第一时间点之前正在执行的指令;北桥集成电路对第一时间点之前正在执行的指令进行计数;北桥集成电路对来自处理器的响应于第一时间点之前正在执行的指令的一确认指令进行计数。

15.如上所述的方法,当北桥集成电路于第一时间点接收数据引流指令,方法还包括:当北桥集成电路每执行于第一时间点之前正在执行的指令中的一个,将计数值加1;当北桥集成电路每接收到来自处理器响应于第一时间点之前正在执行的指令中的一个的确认指令,将计数值减1;当计数值归零,北桥集成电路输出应答指令给重映射硬件。

附图说明

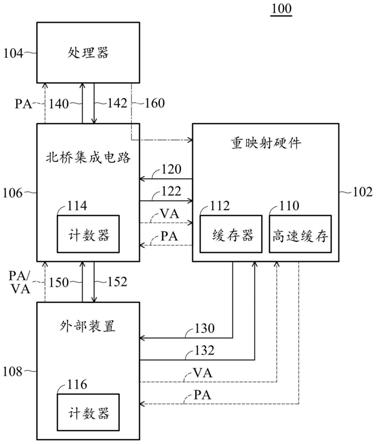

16.图1为本发明实施例的电子装置100的示意图。

17.图2为本发明实施例的图1的电子装置100执行一数据引流(draining)指令的信号

时序图。

18.图3为本发明实施例的图1的重映射硬件102及处理器104通过缓存器做彼此通知的信号时序图。

19.图4为本发明实施例的图1的重映射硬件102接收来自处理器104的多个配置指令的信号时序图。

20.图5为本发明实施例的适用于图1的重映射硬件102、处理器104、北桥集成电路106的改善软硬件协同工作的方法的流程图。

21.图6本发明实施例的适用于图1的重映射硬件102、处理器104、北桥集成电路106、外部装置108的基于图5的改善软硬件协同工作的方法的流程图。

22.图7为本发明实施例的图5的步骤s508的详细流程图。

具体实施方式

23.本发明参照附图进行描述,其中遍及附图上的相同参考数字标示了相似或相同的组件。上述附图并没有依照实际比例大小描绘,其仅仅提供对本发明的说明。一些发明的型态描述于下方作为图解示范应用的参考。这意味着许多特殊的细节,关系及方法被阐述来对这个发明提供完整的了解。无论如何,拥有相关领域通常知识的人将认识到若没有一个或更多的特殊细节或用其他方法,此发明仍然可以被实现。

24.以其他例子来说,众所皆知的结构或操作并没有详细列出以避免对这发明的混淆。本发明并没有被阐述的行为或事件顺序所局限,如有些行为可能发生在不同的顺序亦或同时发生在其他行为或事件之下。此外,并非所有阐述的行为或事件都需要被执行在与现有发明相同的方法之中。

25.图1为本发明实施例的电子装置100的示意图。如图1所示,电子装置100包括一重映射硬件102、一处理器104、一北桥集成电路106,以及一外部装置108。在一些实施例中,重映射硬件102可将虚拟地址转换为实体地址。重映射硬件102包括一高速缓存110。高速缓存110储存着记录虚拟地址与实体地址的对应关系的一映射表。在一些实施例中,电子装置100可为例如笔记本电脑、桌面计算机、平板计算机、智能行动装置、或工作站服务器。

26.举例来说,外部装置108打算读取电子装置100中的一内存(未图示)内的数据。首先,外部装置108输出虚拟地址va给重映射硬件102。重映射硬件102依据高速缓存110中的映射表,将来自外部装置108的虚拟地址va转换为实体地址pa,并且将实体地址pa传送回外部装置108。接着,外部装置108将实体地址pa传送至北桥集成电路106,并且北桥集成电路106将实体地址pa转传送给处理器104。之后,处理器104将实体地址传送给一内存控制器(未图示),使得内存控制器得以将内存中对应于实体地址pa的数据读出。

27.在一些实施例中,外部装置108打算将一数据写入于电子装置100的内存中,并且外部装置108与重映射硬件102之间并无直接接口。因此,外部装置108可将虚拟地址va率先输出给北桥集成电路106,北桥集成电路106再将来自外部装置108的虚拟地址va传送给重映射硬件102。同样地,重映射硬件102依据高速缓存110内的映射表,将虚拟地址va转换为实体地址pa。接着,重映射硬件102将实体地址pa传送给北桥集成电路106。北桥集成电路遂将实体地址pa传送给处理器104。之后,处理器104将实体地址pa传送给内存控制器,使得内存控制器可将数据写入于内存的实体地址pa之中。

28.处理器104执行一软件,用于对重映射硬件102进行配置。在一些实施例中,当软件变更对重映射硬件102的配置时,处理器104会输出一配置指令160给重映射硬件102,使得重映射硬件102对应地输出一数据引流(draining)指令(例如数据引流指令120、130)给与其相连接的部件,例如北桥集成电路106及外部装置108。

29.当北桥集成电路106于一第一时间点接收到来自重映射硬件102的数据引流指令120,北桥集成电路106会搁置第一时间点之后尚未执行的指令,直到于一第二时间点执行完成第一时间点之前正在执行的指令为止。第二时间点晚于第一时间点。同理,当外部装置108于第一时间点接收到来自重映射硬件102的数据引流指令130,外部装置108会搁置第一时间之后尚未执行的指令,直到于一第三时间点执行完成第一时间点之前正在执行的指令为止。第三时间点晚于第一时间点。

30.在一些实施例中,当北桥集成电路106于第二时间点执行完成第一时间点之前正在执行的指令,北桥集成电路106会输出一应答指令122给重映射硬件102。同理,当外部装置108于第三时间点执行完成第一时间点之前正在执行的指令,外部装置108会输出一应答指令132给重映射硬件102。

31.重映射硬件102在收到应答指令122及应答指令132之后,遂通知处理器104数据引流指令120、130的执行已完成。之后,重映射硬件102可更新高速缓存110内的映射表所记录虚拟地址及实体地址的对应关系,用于依据软件的新配置执行指令。当高速缓存110内的映射表已更新,则北桥集成电路106及外部装置108遂可继续执行于第一时间点之后尚未执行的指令。

32.简单来说,重映射硬件102直到搜集到所有与其相连接的部件所回复的应答指令(例如应答指令122、132)后,才可通知处理器104所有部件的数据引流指令的执行皆已完成。

33.由于北桥集成电路106及外部装置108于同一时间只能执行一个数据引流指令,因此,在软件变更对重映射硬件102的配置之后,并且在重映射硬件102输出新的数据引流指令之前,重映射硬件102会检查是否有尚未执行完成的另一数据引流指令。换句话说,重映射硬件102会检查是否已经接收到来自所有部件的应答指令来判断是否有尚未执行完成的另一数据引流指令。当重映射硬件102已接收到来自所有部件的应答指令,则重映射硬件102判断另一数据引流指令已经完成,并且确认没有尚未完成的另一数据引流指令。之后,重映射硬件102才会输出新的数据引流指令给北桥集成电路106及外部装置108。

34.在一些实施例中,当北桥集成电路106于第一时间点接收到来自重映射硬件102的数据引流指令120,北桥集成电路106会执行于第一时间点之前正在执行的指令。例如,北桥集成电路106于第一时间点之前正在通过一直接内存访问(dma)指令140将实体地址传送给处理器104,并且处理器104送回一确认指令142给北桥集成电路106作为响应。

35.相同地,当外部装置108于第一时间点接收到来自重映射硬件102的数据引流指令130,外部装置108会执行于第一时间点之前正在执行的指令。例如,外部装置108于第一时间点之前正在通过一直接内存访问(dma)指令150将实体地址传送给处理器104(经过北桥集成电路106的转传),并且处理器104送回一确认指令152给外部装置108作为响应。在一些实施例中,直接内存访问指令140、150可为一dma读取指令,或一dma写入指令,但本发明不限于此。

36.在一些实施例中,北桥集成电路106包括一计数器114。当北桥集成电路106于第一时间点接收数据引流指令120,计数器114对第一时间点之前正在执行的指令(例如直接内存访问指令140)进行计数,并且对来自处理器104的响应于第一时间点之前正在执行的指令的确认指令(例如确认指令142)进行计数。

37.详细来说,假设北桥集成电路106于第一时间点之前正在执行的指令有10个指令,每当北桥集成电路106继续执行10个指令中的1个,则计数器114的计数值加1。每当北桥集成电路106接收到来自处理器104响应于10个指令中的1个的确认指令,则计数器114的计数值减1。当计数器114的计数值归零,则北桥集成电路106输出应答指令122给重映射硬件102。

38.同理,在一些实施例中,外部装置108包括一计数器116。当外部装置108于第一时间点接收数据引流指令130,计数器116对第一时间点之前正在执行的指令进行计数,并且对来自处理器104的响应于第一时间点之前正在执行的指令的确认指令进行计数。

39.相同地,假设外部装置108于第一时间点之前正在执行的指令有5个指令,每当外部装置108继续执行5个指令中的1个,则计数器116的计数值加1。每当外部装置108接收到来自处理器104响应于5个指令中的1个的确认指令,则计数器116的计数值减1。当计数器116的计数值归零,则外部装置108输出应答指令132给重映射硬件102。在一些实施例中,外部装置108为高速外设互连接口(pci-e)装置,但本发明不限于此。

40.图2为本发明实施例的图1的电子装置100执行一数据引流(draining)指令的信号时序图。同时参考图1及图2,当软件变更对重映射硬件102的配置时,处理器104输出配置指令160给重映射硬件102。重映射硬件102于时间点t1接收到来自处理器104的配置指令160,驱使重映射硬件102于时间点t1时对应地输出数据引流指令120给北桥集成电路106,及输出数据引流指令130给外部装置108。重映射硬件102于时间点t2接收到来自北桥集成电路106的应答指令122,而得知北桥集成电路106已完成数据引流指令120的执行。因此,重映射硬件102将数据引流指令120的电压从高电平变更为低电平,表示数据引流指令120的执行已完成。

41.同理,重映射硬件102于时间点t3接收到来自外部装置108的应答指令132,而得知外部装置108已完成数据引流指令130的执行。因此,重映射硬件102将数据引流指令130的电压从高电平变更为低电平,表示数据引流指令130的执行已完成。北桥集成电路106在时间点t1至时间点t2之间执行数据引流程序。外部装置108在时间点t1至时间点t3之间执行数据引流程序。

42.由于重映射硬件102必须等待北桥集成电路106及外部装置108都完成数据引流程序(也就是,接收到应答指令122及应答指令132)后,才会通知处理器104。因此,就电子装置100而言,其执行数据引流程序(即图2的draining_process)的期间为从时间点t1至时间点t3。

43.在一些实施例中,处理器104依据软件对重映射硬件102的重新配置对应地输出配置指令160给重映射硬件102。配置指令160可包括一dma重映射功能开启/关闭指令、一dma保护存储器检查功能开启/关闭指令、一输入/输出转换后备缓冲区(input/output translation lookaside buffer:iotlb)高速缓存无效化指令、一中断重映射功能开启/关闭指令,以及一中断重映射入口(interrupt remapping entry cache:irec)高速缓存无效

化指令。

44.换句话说,只要重映射硬件102从处理器104接收到上述dma重映射功能开启/关闭指令、dma保护存储器检查功能开启/关闭指令、iotlb高速缓存无效化指令、中断重映射功能开启/关闭指令,及irec高速缓存无效化指令,则重映射硬件102就会对应地向北桥集成电路106发出数据引流指令120,及向外部装置108发出数据引流指令130。

45.图3为本发明实施例的图1的重映射硬件102及处理器104通过缓存器做彼此通知的信号时序图。同时参考图1及图3,重映射硬件102还包括一缓存器112。在一些实施例中,缓存器112包括子缓存器te及子缓存器tes(未图示)。子缓存器te及子缓存器tes对应于dma重映射功能开启/关闭指令。处理器104通过改变子缓存器te的状态告知重映射硬件102其dma重映射功能开启/关闭指令已下达。重映射硬件102通过改变子缓存器tes的状态告知处理器104关联于dma重映射功能开启/关闭指令的数据引流指令已执行完成。

46.举例来说,如图3所示,处理器104于时间点t4将子缓存器te的状态由低电平变更为高电平,也就是处理器104于时间点t4传送dma重映射功能开启指令给重映射硬件102。重映射硬件102读取子缓存器te而得知其状态已经改变,因此于时间点t5时向北桥集成电路106及外部装置108发出数据引流指令(例如数据引流指令120、130)。北桥集成电路106及外部装置108在时间点t5至时间点t6之间执行数据引流程序。重映射硬件102于时间点t6时已收到来自北桥集成电路106及外部装置108的应答指令(例如应答指令122、132),因此数据引流程序draining_process的电压在时间点t6时由高电平变为低电平。同时,重映射硬件102于时间点t6时将子缓存器tes的状态由低电平变更为高电平。处理器104读取子缓存器tes而得知其状态已经改变,使得软件于时间点t6时知道关联于dma重映射功能开启指令的数据引流指令已执行完成。

47.同理,如图3所示,处理器104于时间点t7将子缓存器te的状态由高电平变更为低电平,也就是处理器104于时间点t7传送dma重映射功能关闭指令给重映射硬件102。重映射硬件102读取子缓存器te而得知其状态已经改变,因此于时间点t8时向北桥集成电路106及外部装置108发出数据引流指令。北桥集成电路106及外部装置108在时间点t8至时间点t9之间执行数据引流程序。重映射硬件102于时间点t9时已收到来自北桥集成电路106及外部装置108的应答指令,因此数据引流程序draining_process的电压在时间点t9时由高电平变为低电平。同时,重映射硬件102于时间点t9时将子缓存器tes的状态由高电平变更为低电平。处理器104读取子缓存器tes而得知其状态已经改变,使得软件于时间点t9时知道关联于dma重映射功能关闭指令的数据引流指令已执行完成。

48.在一些实施例中,缓存器112包括子缓存器epm及子缓存器prs(未图示)。当配置指令160为dma保护存储器检查功能开启/关闭指令,则处理器104通过改变子缓存器epm的状态告知重映射硬件102其dma保护存储器检查功能开启/关闭指令已下达。重映射硬件102通过改变子缓存器prs的状态告知处理器104关联于dma保护存储器检查功能开启/关闭指令的数据引流指令已执行完成。

49.在一些实施例中,当配置指令160为iotlb高速缓存无效化指令,则处理器104直接传送一iotlb无效化指令给重映射硬件102,使得重映射硬件102对应地向北桥集成电路106及外部装置108发送数据引流指令。重映射硬件102直接传送一中断事件给处理器104,使得软件得知关联于iotlb高速缓存无效化指令的数据引流指令已执行完成。

50.在一些实施例中,缓存器112包括子缓存器ire及子缓存器ires(未图示)。当配置指令160为中断重映射功能开启/关闭指令,则处理器104通过改变子缓存器ire的状态告知重映射硬件102其中断重映射功能开启/关闭指令已下达。重映射硬件102通过改变子缓存器ires的状态告知处理器104关联于中断重映射功能开启/关闭的数据引流指令已执行完成。

51.在一些实施例中,当配置指令160为irec高速缓存无效化指令,则处理器104直接传送一irec无效化指令给重映射硬件102,使得重映射硬件102对应地向北桥集成电路106及外部装置108发送数据引流指令。重映射硬件102直接传送一中断事件给处理器104,使得软件得知关联于irec无效化指令的数据引流指令已执行完成。

52.图4为本发明实施例的图1的重映射硬件102接收来自处理器104的多个配置指令的信号时序图。同时参考图1及图4,重映射硬件102于时间点t10接收到来自处理器104的配置指令160_1,因此对应地输出数据引流指令给北桥集成电路106及外部装置108,使得北桥集成电路106及外部装置108于时间点t10开始执行数据引流程序(也就是,draining_process的电压于时间点t10时由低电平变为高电平)。

53.接着,重映射硬件102于时间点t11接收到来自处理器104的另一配置指令160_2,并且于时间点t12接收到来自处理器104的另一配置指令160_3。如图4示,由于在时间点t11及时间点t12时,北桥集成电路106及外部装置108仍在执行对应于配置指令160_1的数据引流程序,重映射硬件102检测到仍有未完成的数据引流指令,因此重映射硬件102只能等待对应于配置指令160_1的数据引流程序完成后,于时间点t13再传送对应于配置指令160_2的数据引流指令给北桥集成电路106及外部装置108。

54.当对应于配置指令160_2的数据引流程序完成后,重映射硬件102才会再传送对应于配置指令160_3的数据引流指令给北桥集成电路106及外部装置108。简单来说,北桥集成电路106及外部装置108在同一时间仅能执行一个数据引流指令的操作。

55.图5为本发明实施例的适用于图1的重映射硬件102、处理器104、北桥集成电路106的改善软硬件协同工作的方法的流程图。如图5所示,在步骤s500中,软件(即处理器104)首先改变对重映射硬件的配置。在步骤s502中,重映射硬件102检查并没有尚未执行完成的一先前数据引流指令。接着,在步骤s504中,重映射硬件102输出一数据引流指令(例如数据引流指令120)给北桥集成电路106。在步骤s506中,北桥集成电路106于一第一时间点接收数据引流指令。

56.再者,在步骤s508中,北桥集成电路106搁置第一时间点之后尚未执行的指令,直到于一第二时间点执行完成第一时间点之前正在执行的指令为止。在步骤s510中,北桥集成电路106于第二时间点输出一应答指令(例如应答指令122)给重映射硬件102,第二时间点晚于第一时间点。最后,在步骤s512重映射硬件依据应答指令,通知处理器104数据引流指令的执行已完成。

57.图6本发明实施例的适用于图1的重映射硬件102、处理器104、北桥集成电路106、外部装置108的基于图5的改善软硬件协同工作的方法的流程图。如图6所示,本发明的改善软硬件协同工作的方法除了包括图5的步骤s500~s510,还包括在步骤s600中,重映射硬件102输出数据引流指令(例如数据引流指令130)给外部装置108。在步骤s602中,外部装置108于第一时间点接收数据引流指令。

58.在步骤s604中,外部装置108搁置第一时间点之后尚未执行的指令,直到于一第三时间点执行完成第一时间点之前正在执行的指令为止。接着,在步骤s606中,于第三时间点,外部装置108输出一第二应答指令(例如应答指令132)给重映射硬件102,第三时间点晚于第一时间点。最后,在步骤s608中,重映射硬件102直到接收到应答指令及第二应答指令,才通知处理器104数据引流指令的执行已完成。

59.图7为本发明实施例的图5的步骤s508的详细流程图。如图7所示,在步骤s700中,北桥集成电路106执行于第一时间点之前正在执行的指令。在步骤s702中,北桥集成电路106对第一时间点之前正在执行的指令进行计数。在步骤s704中,当北桥集成电路106每执行于第一时间点之前正在执行的指令中的一个,将计数值加1。

60.接着,在步骤s706中,北桥集成电路106对来自处理器104的响应于第一时间点之前正在执行的指令的一确认指令进行计数。在步骤s708中,当北桥集成电路106每接收到来自处理器104响应于第一时间点之前正在执行的指令中的一个的确认指令,将计数值减1。最后,在步骤s710,当计数值归零,北桥集成电路106输出应答指令(例如应答指令122)给重映射硬件102。

61.本发明的用于改善软硬件协同工作的电子装置及方法加大io虚拟化硬件的可靠性,能够一定程度上保护系统的数据。在iov设备面临虚拟化软件改变系统状态或者修改页表内容时,硬件更能够平缓过度。本发明所执行的数据引流(draining)程序,具有以下优点:一、不影响其他正常功能的效能;二、完整的数据引流过程而不遗漏任何的指令;三、增加了处理器响应于dma指令的确认指令(例如确认指令142、152),用于确认数据引流程序是否完成。现有技术中的处理器并不会对dma指令进行响应,而是直接将dma指令转传送而出(例如传送至内存控制器)。

62.四、重映射硬件与北桥集成电路(或外部装置)之间的数据引流程序是由握手信号(例如,数据引流指令120对应于应答指令122,以及数据引流指令130对应于应答指令132)所完成;五、重映射硬件只在特定时候发出特定的数据引流指令(例如,当配置指令160为dma重映射功能开启/关闭指令、dma保护存储器检查功能开启/关闭指令、iotlb高速缓存无效化指令、中断重映射功能开启/关闭指令,或irec高速缓存无效化指令之时)。

63.虽然本发明的实施例如上述所描述,我们应该明白上述所呈现的只是范例,而不是限制。依据本实施例上述示范实施例的许多改变是可以在没有违反发明精神及范围下被执行。因此,本发明的广度及范围不该被上述所描述的实施例所限制。更确切地说,本发明的范围应该要以以下的申请专利范围及其相等物来定义。

64.尽管上述发明已被一或多个相关的执行来图例说明及描绘,等效的变更及修改将被依据上述规格及附图且熟悉这领域的其他人所想到。此外,尽管本发明实施例的一特别特征已被相关的多个执行之一所示范,上述特征可能由一或多个其他特征所结合,以致于可能有需求及有助于任何已知或特别的应用。

65.除非有不同的定义,所有本文所使用的用词(包含技术或科学用词)是可以被属于上述发明的技术中拥有一般技术的人士做一般地了解。我们应该更加了解到上述用词,如被定义在众所使用的字典内的用词,在相关技术的上下文中应该被解释为相同的意思。除非有明确地在本文中定义,上述用词并不会被解释成理想化或过度正式的意思。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。