1.本发明涉及网络设备,尤其但不排他地涉及接收端处理。

背景技术:

2.在计算机网络中,每个节点(例如,交换机或端点)通常都有自己的实时时钟。在许多应用中,希望不同节点的实时时钟精确地同步。然而,由于在节点之间分配时钟同步消息所涉及的延迟和抖动,可能难以实现这种同步。

3.精确时间协议(ptp)被认为是解决此问题的方案。该协议使网络节点能够使用节点和主设备之间的消息传递来确定其各自时钟的偏移,以达到纳秒级的精度。为了测量时钟偏移时的最大精度,通常使用基于硬件的时间戳,例如,weibel和bechaz在2004年ieee 1588大会(2004年9月28日)上的“implementation and performance of time stamping techniques(时间戳技术的实现和性能)”中所述,将其通过引用并入本文。ptp硬件时钟(phc)是根据ptp格式运行的硬件时钟(例如,包括振荡器和计数器)。phc被同步到网络中的主机。

4.成功运行ptp协议通常需要接收到的分组的准确时间戳,以便时间戳点不受网络负载或接收节点的cpu负载的影响。因此,网络接口控制器(nic)或其他网络节点中的硬件时间戳通常比软件时间戳更好,后者可能会遭受cpu负载误差的影响,而硬件时间戳则更为准确和稳定。

5.现在描述示例,同步。在第一步中,同步频率。主设备在时间t1发送同步消息,该消息在时间t2到达从设备。主设备在时间t3发送同步消息,该消息在时间t4到达从设备。从设备根据以下计算漂移:

6.[t4

‑

t2

–

(t3

‑

t1)]/(t3

‑

t1)。

[0007]

然后,从设备可以基于漂移来调整其时钟,以同步其时钟的频率。

[0008]

然后,主设备在时间t5发送另一同步消息,该消息在时间t6由从设备接收。然后,从设备在时间t7发送延迟请求消息。然后,主设备在时间t8发送另一消息,该消息包括主设备接收到延迟请求的时间。从设备可以将往返时间计算为等于:

[0009]

t8

‑

t5

–

(t7

‑

t6)。

[0010]

因此,从主设备到从设备的单向延迟由以下给出:

[0011]

[t8

‑

t5

–

(t7

‑

t6)]/2。

[0012]

然后,主设备在时间t9发送另一消息。当从设备在t10接收到消息时,从设备知道相位为t10加上单向延迟。

[0013]

kagan的美国专利8,370,675描述了一种时钟同步的方法,该方法包括计算实时时钟电路的本地时钟时间与参考时钟时间之间的偏移值,并将该偏移值加载到与实时时钟电路相关的寄存器中。然后将本地时钟时间与寄存器中的值相加,以给出与参考时钟同步的本地时钟时间的调整值。

技术实现要素:

[0014]

根据本公开的实施方式,提供了一种网络设备,包括:网络接口端口,其被配置为通过分组数据网络从网络节点接收数据符号,至少一些符号包括在数据分组中;以及控制器电路,包括物理层(phy)电路,所述物理层电路包括接收phy管线电路,其被配置为处理接收到的数据符号,以及计数器,其被配置为维持指示所述接收phy管线电路中的数据符号的数量的计数器值。

[0015]

进一步根据本公开的实施方式,所述接收phy管线电路被配置为识别所述数据分组之一的帧开始定界符;以及计算所识别的帧开始定界符的时间戳。

[0016]

更进一步根据本公开的实施方式,所识别的帧开始定界符的数据分组包括填充有第一crc码的循环冗余校验(crc)字段,其中所述控制器电路被配置为检查所述第一crc码,响应于所述数据分组,计算第二crc码,所述第二crc码比所述第一crc码更短以及将所述第二crc码和计算出的时间戳插入到所述crc字段中,以代替所述第一crc码。

[0017]

另外,根据本公开的实施方式,所识别的帧开始定界符的数据分组包括从所述分组数据网络中的主时钟接收的时间同步消息。

[0018]

此外,根据本公开的实施方式,该设备包括硬件时钟,其被配置为维持时钟值,其中所述接收phy管线电路被配置为根据给定的符号时序来处理所接收的数据符号的到达,以及响应于基于所述计数器值和所述符号时序的调整而减少的时钟值,计算所识别的帧开始定界符何时进入所述接收phy管线电路的时间戳,并且所述控制器电路被配置为将计算出的时间戳分配给所识别的帧开始定界符的数据分组之一。

[0019]

进一步根据本公开的实施方式,所述控制器电路被配置为响应于所计算出的时间戳和所述硬件时钟的当前时钟值来计算扩展时间戳;以及生成包括所述扩展时间戳的控制消息。

[0020]

仍进一步根据本公开的实施方式,所述接收phy管线电路被配置为响应于所述计数器值除以所述符号的符号频率来计算所述调整。

[0021]

另外,根据本公开的实施方式,所述接收phy管线电路被配置为响应于所述计数器值乘以所述符号的符号周期来计算所述调整。

[0022]

此外,根据本公开的实施方式,所述接收phy管线电路被配置为以非恒定延迟来处理所述符号,使得所述符号中的不同的相应符号在各自不同的时间长度内驻留在所述接收phy管线电路中。

[0023]

进一步根据本公开的实施方式,所述计数器被配置为:响应于进入所述接收phy管线电路的所述符号中的一些符号,递增所述计数器值;以及响应于离开所述接收phy管线电路的所述符号中的一些符号,递减所述计数器值。

[0024]

仍进一步根据本公开的实施方式,所述接收phy管线电路被配置为响应于事件以及符号的给定数量设置所述计数器值,所述事件指示所述接收phy管线电路中的符号的给定数量。

[0025]

另外,根据本公开的实施方式,所述事件包括在所述接收phy管线电路中实现块锁定。

[0026]

此外,根据本公开的实施方式,所述事件包括:在所述接收phy管线电路中实现对前向纠错fec块的锁定;以及所述给定的数量是所述fec块的大小。

[0027]

进一步根据本公开的实施方式,所述计数器被配置为响应于在所述接收phy管线电路中消耗的所述符号中的一些符号来使所述计数器值递减。

[0028]

仍进一步根据本公开的实施方式,所述接收phy管线电路被配置为如果所述消耗符号仍在所述接收phy管线电路中,则响应于所述消耗符号沿着所述接收phy管线电路何时到达所述计数器使所述计数器值递减。

[0029]

另外,根据本公开的实施方式,所述接收phy管线电路被配置为在所述接收phy管线电路中的相应位置处将相应的控制信号插入到所述接收phy管线电路中,在所述相应位置处从所述接收phy管线电路去除所述消耗符号中的相应符号。

[0030]

根据本公开的另一实施方式,还提供一种包括网络设备的计算机系统,该计算机系统包括网络接口端口,其被配置为通过分组数据网络从网络节点接收数据符号,至少一些符号包括在数据分组中;硬件时钟,其被配置为维持时钟值;以及控制器电路,所述控制器电路包括物理层(phy)电路,所述物理层电路包括接收phy管线电路,其被配置为:根据给定的符号时序来处理所接收的数据符号的到达;以及识别所述数据分组之一的帧开始定界符,以及计数器,用于维持指示所述接收phy管线电路中的数据符号数量的计数器值,其中所述接收phy管线电路被配置为响应于基于所述计数器值和所述符号时序的第一调整而减少的时钟值,计算所识别的帧开始定界符何时进入所述接收phy管线电路的时间戳,并且所述控制器电路被配置为将计算出的时间戳分配给所识别的帧开始定界符的数据分组之一,所识别的帧开始定界符的数据分组包括从所述分组数据网络中的主时钟接收的时间同步消息,以及包括处理器的主机设备,所述处理器被配置为运行软件指令以:接收所述时间同步消息并响应于所述时间同步消息计算对所述硬件时钟的时钟值的第二调整,其中所述硬件时钟被配置为响应于计算出的第二调整而调整所述时钟值。

[0031]

此外,根据本公开的实施方式,所述计数器被配置为响应于进入所述接收phy管线电路的所述符号中的一些符号,递增所述计数器值;以及响应于离开所述接收phy管线电路的所述符号中的一些符号,递减所述计数器值。

[0032]

进一步根据本公开的实施方式,所述接收phy管线电路被配置为响应于事件以及符号的给定数量设置所述计数器值,所述事件指示所述接收phy管线电路中的符号的给定数量。

[0033]

仍进一步根据本公开的实施方式,所述计数器被配置为响应于在所述接收phy管线电路中消耗的所述符号中的一些来使所述计数器值递减。

[0034]

另外,根据本公开的实施方式,所述接收phy管线电路被配置为:如果所述消耗符号仍在所述接收phy管线电路中,则响应于何时所述消耗符号将沿着所述接收phy管线电路到达所述计数器使所述计数器值递减。

[0035]

根据本公开的又一个实施方式,还提供了一种联网方法,包括:通过分组数据网络从网络节点接收数据符号,至少一些符号包括在数据分组中,并维持时钟值;根据给定的符号时序来处理所接收的数据符号的到达,识别所述数据分组之一的帧开始定界符,维持指示接收phy管线电路中的数据符号数量的计数器值,响应于基于所述计数器值和所述符号时序的调整而减少的时钟值,计算所识别的帧开始定界符何时进入所述接收phy管线电路的时间戳,并将计算出的时间戳分配给所识别的帧开始定界符的数据分组之一。

附图说明

[0036]

通过以下结合附图的详细描述,将会理解本发明,其中:

[0037]

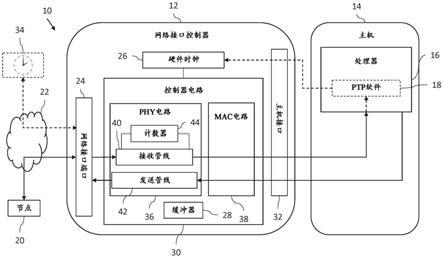

图1是根据本发明的实施方式构造和操作的计算机系统的框图;

[0038]

图2是图1的系统中的phy接收管线电路系统处理符号的框图;

[0039]

图3是图1的系统中phy接收管线电路消耗符号的框图;

[0040]

图4是包括图1的系统中的计数器重置方法中的步骤的流程图;

[0041]

图5a和图5b是包括图1的系统中的时间戳计算方法中的步骤的流程图;

[0042]

图6是包括图1的系统中将计算出的时间戳分配给数据分组的方法中的步骤的流程图;

[0043]

图7是示出图6的方法的框图;

[0044]

图8是包括图1的系统中扩展计算出的时间戳的方法中的步骤的流程图;

[0045]

图9是示出图8的方法的框图;

[0046]

图10是图1的系统中的硬件时钟的框图;以及

[0047]

图11是包括图1的系统中的时间同步方法中的步骤的流程图。

具体实施方式

[0048]

如前所述,成功运行ptp协议通常需要接收到的分组的准确时间戳,以便时间戳点不受网络负载或ptp分组的中央处理单元(cpu)处理的影响。因此,网络接口控制器(nic)或其他网络节点中的硬件时间戳通常比软件时间戳更好,软件时间戳可能会遭受cpu负载错误。

[0049]

在许多应用中,甚至硬件时间戳也可能无法提供更高的精度(例如,最高可达皮秒),这是因为硬件处理不是在单一步骤中处理分组,而是沿着长而复杂的管线处理,这通常会延迟大约1微秒。

[0050]

因此,为了消除由长而复杂的管线引起的错误,期望在发生缓冲和延迟之前,尽可能地接近管线的开始计算时间戳。在设备的接收端,管线的起点通常在物理层(phy)中。

[0051]

由于phy处理接收到的符号而不在分组级别进行处理,因此在phy的早期加盖时间戳具有挑战性。仅稍后在phy中,在已经发生延迟之后,才可以识别用于识别分组的开始的帧定界符(sfd)。ieee1588标准将分组的时间戳定义为该分组的srd的时间戳。然而,即使可以在phy中识别分组的开始,分组的性质,例如ptp分组与其他分组的相对性质也是未知的。此外,在phy层中,由于在通道偏移、加扰和前向纠错(fec)编码之前接收原始位,因此符号的到达时间不容易计算。

[0052]

另一方面,如果在分组成帧后执行时间戳记,则准确性会受到影响,这是因为管线的延迟可能不是恒定的,并且由于物理编码层(pcs)标记、fec奇偶校验、fec存储和转发以及管线中的任何缓冲而可能遭受高抖动。

[0053]

一些网络设备(例如,nic或交换机)可以包括恒定延迟的phy管线。因此,具有恒定延迟phy管线的设备的解决方案是基于从本地时钟给定的当前时间减去phy管线的恒定延迟来计算phy管线末端处的sfd时间戳。

[0054]

但是,其他网络设备包括可变延迟phy管线,这会导致高性能并提供较低的延迟。但是,对于这种可变延迟设备,上述时间戳方法在计算时间戳时可能无法提供足够的准确

性。

[0055]

本发明的实施方式通过提供一种网络设备来解决上述问题,该网络设备使用计数器来计算接收phy管线中的时间戳,该计数器维持管线中数据符号的数量的计数器值。在识别出sfd之后,可以基于当前时间(由本地时钟给定)和sfd的数据符号在管线中所花费的时间,向phy管线的末端计算sfd的时间戳。尽管管线延迟可以是可变的,但是根据给定的符号时序,例如根据由网络设备操作的通信协议规定的符号率来处理(例如,输入到管线中)每个数据符号的到达。因此,由计数器值给定的管线中的符号数量以及给定的符号时序可用于计算管线中sfd的数据符号所花费的时间。然后,可以基于当前时间减去管线中sfd的数据符号花费的时间来计算时间戳。因此,时间戳是在phy层中计算的,通常这是在网络设备的处理管线中获得准确延迟信息的最后机会。

[0056]

phy层不解析分组,例如,不识别ptp分组。然后在网络设备中的phy层之后识别分组之后,可以将时间戳添加到与所识别的sfd相关联的分组。在一些实施方式中,时间戳被添加到每个sfd,从而每个分组被准确地加上时间戳。因此,当在处理的较后阶段识别出ptp分组时,每个ptp分组都具有准确的时间戳。在一些实施方式中,诸如循环冗余校验(crc)字段的现有分组字段可以用于存储时间戳。可以检查crc字段中的现有crc码,并且如果检查成功,则可以计算替换的较短crc码。然后,替换的crc码可以与计算出的时间戳一起存储在crc字段中。

[0057]

在一些实施方式中,所计算的时间戳可以仅包括与sfd进入管线相关联的时间的最低有效位(lsb)。与sfd进入管线相关联的时间的最高有效位(msb)可以存储在其他位置。在稍后的阶段,可以使用存储的值来扩展计算出的时间戳。可以将扩展的时间戳添加到控制消息中,以转发到主机,例如,用于精确地处理ptp同步消息。在一些实施方式中,不需要msb被显式地保存,因为基于计算时间戳与扩展时间戳之间的延迟足够短的假设本地时钟的时间(当扩展时间戳时)将包括msb。

[0058]

对于进入phy管线的数据符号,该计数器递增;对于离开phy管线至媒体访问控制(mac)电路的数据符号,该计数器递减。但是,维持管线中数据符号数量的准确计数并不是容易的事。这是由于各种因素引起的,包括诸如服务位(例如,标记,fec奇偶校验等)的数据符号在phy管线中被消耗并且没有退出phy管线。消耗的数据符号由计数器识别并解决。如果消耗的数据符号此时仍在phy管线中,则根据消耗的数据符号离开phy管线的时间,对消耗的数据符号使计数器递减。可以在phy管线中的相应位置处插入相应的控制信号,从该位置,相应消耗的符号从phy管线中被去除。

[0059]

另一因素是在实现块锁定,phy管线接收符号之前知道何时以及如何重置计数器,但是通常直到实现块锁定之后才从管线释放符号。块锁定定义为完成链接过程,该过程可能包括锁定到传入的位流,与块开始和结束位置对齐以及在多个通道上倾斜。因此,在块锁定之前运行计数器可以容易导致计数器超限和/或无意义的计数器值。因此,当可能知道管道为空时,计数器通常不会从启动状态运行。相反,响应于识别与phy管线中的符号的数量的已知值(或该值的良好估计)相关联的事件,计数器被重置。当已知phy管线中的符号数量等于或非常接近与fec锁定相关联的fec块的已知大小时,一个这样的事件是实现fec锁定。

[0060]

系统描述

[0061]

通过引用结合到本文中的文件应被认为是本技术的组成部分,除了在这些结合文

件中以与本说明书中明确或隐含的定义相抵触的方式定义任何术语之外,应该仅考虑本说明书的定义。

[0062]

现在参考图1,其是根据本发明的实施方式构造和操作的计算机系统10的框图。计算机系统10包括连接到主机计算机14的网络设备12(例如,nic)。主机计算机14包括处理器16,以执行各种处理任务,可选地包括运行ptp软件18,将参考图10和图11更详细地描述。实际上,处理器16的一些或全部功能可以组合在单个物理组件中,或者替代地,使用多个物理组件来实现。这些物理组件可以包括硬连线或可编程设备,或两者的组合。在一些实施方式中,处理器16的至少一些功能可以在适当的软件的控制下由可编程处理器执行。该软件可以例如通过网络以电子形式下载到设备。替代地或附加地,软件可以存储在有形的,非暂时性的计算机可读存储介质中,例如光学,磁性或电子存储器中。

[0063]

在一些实施方式中,网络设备12和主机计算机14的功能可以组合在任何合适的网络设备中,例如,包括运行ptp软件的cpu的网络交换机。

[0064]

网络设备12包括网络接口端口24,硬件时钟26,缓冲器28,控制器电路30和主机接口32。

[0065]

网络接口端口24被配置为通过分组数据网络22从网络节点20接收数据符号。至少一些符号被包括在数据分组中。在一些实施方式中,网络接口端口24被配置为从主时钟设备34接收ptp同步消息中包括的数据符号。

[0066]

硬件时钟26被配置为根据诸如协调世界时(utc)的任何合适的时间标准来维持时钟值。参考图10和图11更详细地描述硬件时钟26。缓冲器28被配置为存储由网络设备12的各个元件使用的数据。主机接口32被配置为在网络设备12和主机计算机14之间传输数据。主机接口32可以包括任何合适的接口,例如但不限于外围组件互连快速(pcie)接口。

[0067]

控制器电路30包括物理层(phy)电路36和mac电路38。phy电路36被配置为在物理层处理数据符号。mac电路38被配置为在接收和发送管线(未示出)中的数据链路层处处理分组。控制器电路30可以执行其他转发和处理功能。

[0068]

phy电路36包括接收phy管线电路40和发送管线电路42,用于分别处理接收到的数据符号和要发射的数据符号。phy电路36还包括计数器44,以维持指示接收phy管线电路40中的数据符号的数量的计数器值。参考图2至图5b更详细地描述接收phy管线电路40。

[0069]

现在参考图2,其是在图1的系统10中处理数据符号46的接收phy管线电路40的框图。图2示出了在左侧进入phy管线电路40在右侧离开管线的数据符号46。计数器44耦合到接收phy管线电路40,并且被配置为响应于符号46(从网络接口端口24(图1))进入接收phy管线电路40而递增计数器值,并响应于符号46离开接收phy管线电路40(朝向mac电路38(图1))而递减计数器值。

[0070]

图2示出了被识别为sfd 48的数据符号46之一。接收phy管线电路40通常被配置为检测每个sfd,甚至可以丢弃在mac电路38中的那些sfd。可以在接收phy管线电路40中的最后阶段执行sfd的检测。数据符号46进入接收phy管线电路40的符号率是恒定的并且是已知的。因此,在接收phy管线电路系统40的末端,sfd48的数据符号46已经在接收phy管线电路40中花费的时间t与如由计数器44维持的计数器值给出的当前在管线中的数据符号46的数量成比例。因为已知符号率,可以响应于当前计数器值和符号率来计算时间t。时间t可以用于计算所识别的sfd 48进入接收phy管线电路系统40的时间,如参考图5a和图5b更详细地

描述的。

[0071]

现在参考图3,其是消耗图1的系统10中的符号50的接收phy管线电路40的框图。由接收phy管线电路系统40处理进入接收phy管线电路40的一些数据符号46并且朝mac电路38(图1)离开接收phy管线电路系统40。其他符号46进入接收phy管线电路40,并且在接收phy管线电路40内被消耗,并且不朝mac电路38离开接收phy管线电路40。一些消耗的符号50在图3中以示例的方式示出。如下面更详细地描述的,消耗的符号50被控制信号52代替。消耗的符号50的示例是服务位(例如,标记、fec奇偶校验位等)。可以基于其他数据的存在来检测消耗的符号50。例如,当检测到fec块时,接收phy管线电路40知道存在被去除的奇偶符号,因此接收phy管线电路40将例如通过将控制信号52添加到接收phy管线电路40来补偿被去除的fec奇偶符号。标记可以是物理层符号,这些物理层符号由接收phy管线电路40消耗,并且不转发到mac电路38。

[0072]

当控制信号52到达接收phy管线电路40的末端时,控制信号52将被计数为离开接收phy管线电路40的符号,并且计数器值将相应地递减。

[0073]

因此,接收phy管线电路40被配置为,如果消耗的符号50此时仍在接收phy管线电路40中,则响应于消耗的符号50何时将沿着接收phy管线电路40到达计数器44而递减计数器值。在一些实施方式中,接收phy管线电路40被配置为在接收phy管线电路40中的相应位置处将相应的控制信号52插入到接收phy管线电路40中,在该位置处从接收phy管线电路40中去除了相应消耗的符号50。计数器44被配置为响应于在接收phy管线电路40中被消耗的符号50来递减计数器值。

[0074]

现在参考图4,其是包括图1的系统10中的计数器重置方法中的步骤的流程图60。因为在实现块锁定之前,接收phy管线电路40接收符号46,但是通常不从接收phy管线电路40释放符号46直到实现块锁定之后,所以知道何时以及如何重置计数器44(图3)是有意义的。因此,在块锁定之前运行计数器44很容易导致计数器超限和/或无意义的计数器值,因为计数器在块锁定之前不会递减。因此,当可以知道接收phy管线电路40为空时,计数器44通常不从启动状态运行。取而代之的是,响应于识别与接收phy管线电路40中的符号46的数量的已知值(或该值的良好估计)相关联的事件而重置计数器44。一种这样的事件是当为了实现fec锁定,识别了一些标记并且累积了整个fec块以检查fec块的奇偶校验时实现fec锁定。因此,在实现fec锁定时,已知接收phy管线电路40中的符号数量等于或非常接近累积在接收phy管线电路40中的fec块的已知大小。另一种此类事件是当可以估计接收phy管线电路40的每个通道中有多少个数据符号时,实现块锁定。然后,针对该事件将计数器44重置为接收phy管线电路40中符号46的已知或估计数量。通常,按照协议,某些事件可以很好地估计接收phy管线电路40内部的位数。

[0075]

因此,接收phy管线电路40被配置为检测(框62)指示以下情况的事件(例如,在接收phy管线电路40中实现块锁定,或者在接收phy管线电路40中实现fec块的锁定):在接收phy管线电路40中符号46的给定数量(例如,fec块的大小),并且响应于检测到事件来设置(框64)计数器值,并且响应于与检测到的事件相关联的接收phy管线电路40中符号46的给定(已知或估计)数量来设置计数器值)。

[0076]

图5a和图5b是包括图1的系统10中的时间戳计算方法中的步骤的流程图70、81。现在参考图5a。还参考图3。

[0077]

接收phy管线电路系统40被配置为根据给定的符号时序来处理所接收的数据符号的到达。接收phy管线电路系统40被配置为在物理层处理数据符号46(框72)。接收phy管线电路系统40被配置为以非恒定延迟来处理符号46,使得不同的相应符号46在接收phy管线电路系统40中停留相应不同的时间长度。

[0078]

现在更详细地描述框72的步骤的子步骤。接收phy管线电路系统40被配置为从网络接口端口24(图1)接收数据符号46(框74)。接收phy管线电路40被配置为消耗一些数据符号46(框76)。接收phy管线电路40被配置为将相应的控制信号52在接收phy管线电路40中的相应位置处插入(框78)到接收phy管线电路40中,从该相应位置中将相应消耗的符号50从接收phy管线电路40中去除。以这种方式,接收phy管线电路40被配置为,如果消耗的符号仍在接收phy管线电路40中,则响应于消耗的符号50沿着接收phy管线电路40何时到达计数器44而递减计数器值。接收phy管线电路40被配置为(框80)将未从接收phy管线电路40消耗的数据符号46转发到mac电路38。

[0079]

框74至框80的步骤通常在同时和/或大约同时执行。例如,当数据符号46进入接收phy管线电路40时,其他数据符号46正被接收phy管线电路40处理和/或消耗,并且其他数据符号46正朝mac电路38(图1)离开接收phy管线电路40。

[0080]

现在参考图5b。还参考图3。接收phy管线电路40被配置为识别(框82)数据分组之一的sfd。接收phy管线电路40被配置为响应于当前时钟值(由硬件时钟26维持)并基于计数器值和符号时序的调整而减少,计算(框84)所识别的sfd何时进入接收phy管线电路40的时间戳。在一些实施方式中,接收phy管线电路40被配置为响应于计数器值除以符号46的符号频率来计算调整。在其他实施方式中,接收phy管线电路40被配置为响应于计数器值除以符号的符号周期来计算调整。

[0081]

接收phy管线电路40被配置为将时间戳保存(框86)到缓冲器28(图1)。随后从缓冲器28中检索时间戳,并将其添加到所识别的sfd的分组中,如参考图6和图7更详细地描述的。对随后的sfd重复框82

‑

86的步骤。

[0082]

时间戳可以由通过计算的调整(例如,基于计数器值和符号率)调整的当前时间的lsb表示。通过计算的调整来调整的当前时间的msb可以在稍后的阶段被添加到时间戳,如参考图8和图9更详细地描述的。通过计算的调整调整的当前时间的最高有效位(msb)可以存储在其他位置。在一些实施方式中,不需要msb被显式地保存,因为基于计算时间戳与扩展时间戳之间的延迟足够短的假设,硬件时钟26的当前时间(当在以后的阶段中扩展时间戳时)将包括msb。

[0083]

现在参考图6和图7,图6是包括图1的系统10中将计算出的时间戳分配给数据分组90的方法中的步骤的流程图88。

[0084]

当所识别的sfd退出接收phy管线电路40时,并且通常在进入mac电路38(图1)之前,控制器电路30(图1)被配置为从缓冲器28(图1)检索(框94)计算的时间戳100。控制器电路30被配置为将计算出的时间戳100分配(框96)给所识别的sfd的数据分组90。将时间戳添加到与已识别的sfd相关联的数据分组中的一个原因是为了允许带有精确时间戳的分组的全线速(线速)。

[0085]

为了在不扩展数据路径的情况下将时间戳100添加到数据分组90,可以将计算出的时间戳100添加到数据分组90的现有字段,例如crc字段92。例如,假定crc字段92具有32

位的长度并且计算的时间戳100具有26位的长度。然而,在一些实施方式中,crc字段92和计算出的时间戳100可以具有任何合适的长度。

[0086]

crc字段92填充有现有的crc码(例如32位)。因此,现有的crc码可以由较短的crc码98(例如6位)和计算出的时间戳100(例如26位)替换。

[0087]

因此,控制器电路30被配置为:检查(框102)现有的crc码;(使用任何合适的crc算法)响应于数据分组计算(框104)较短的替换crc码98;并将较短的替换crc码98和计算出的时间戳100插入crc字段92中,以替换现有的crc码。

[0088]

现在参考图8和图9,图8是包括在图1的系统10中扩展计算的时间戳100的方法中的步骤的流程图106。现在参考图9,其是示出图8的方法的框图。

[0089]

控制器电路30被配置为接收(框108)具有计算出的时间戳100(例如26位)的数据分组90(图7)。控制器电路30被配置为从硬件时钟26(图1)检索(框110)当前时钟值118。从检索到的当前时钟值118中选择当前时钟值118的msb(例如64位)(包括在数据分组90进入接收phy管线电路40时的时间的msb)。控制器电路30被配置响应于计算出的时间戳100和硬件时钟26的当前时钟值118的msb,计算(框112)扩展的时间戳120(例如80位)。控制器电路30被配置为生成(框114)包括扩展时间戳120的控制消息122,并将控制消息122提供(框116)到主机计算机14(图1)。

[0090]

框108

‑

116的以上步骤可以在控制器电路30中的任何合适的位置处执行。

[0091]

现在参考图10和图11,图10是图1的系统10中的硬件时钟26的框图。图11是包括图1的系统10中的时间同步方法中的步骤的流程图130。

[0092]

硬件时钟26可以包括振荡器124,锁相环126和寄存器128。振荡器124驱动锁相环126,该锁相环126提供对振荡器124提供的频率的调整。频率调整由锁相环126提供给寄存器128,该频率调整根据任何合适的标准,例如utc,维持当前时间。然后可以根据需要将当前时间从寄存器128提供给接收phy管线电路40和网络设备12的其他元件。

[0093]

由网络设备12处理的一些分组是从主时钟设备34(图1)接收的ptp同步消息或其他时间同步消息。消息由ptp软件18(图1)处理,如下面更详细描述的。

[0094]

主计算机14的处理器16(图1)被配置为运行ptp软件18的软件指令以:接收(框132)时间同步消息;响应于时间同步消息,计算(框134)对硬件时钟26的时钟值(例如,漂移)的调整138,并且将调整138提供(框136)给硬件的锁相环126。硬件时钟26的锁相环126被配置为响应于所计算的调整138来调整存储在寄存器128中的时钟值。

[0095]

为了清楚起见,在单独的实施方式的上下文中描述的本发明的各种特征也可以在单个实施方式中组合提供。相反,为简洁起见,在单个实施方式的上下文中描述的本发明的各种特征也可以单独地或以任何合适的子组合来提供。

[0096]

通过示例引用了上述实施方式,并且本发明不受以上已经具体示出和描述的内容的限制。相反,本发明的范围包括上述各种特征的组合和子组合,以及本领域技术人员在阅读前述说明后将想到的并且其在现有技术中未公开的变型和修改。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。