1.本发明属于兼容于cmos集成电路的技术领域,涉及一种适用于高集成低功耗cmos集成电路设计和制造技术的低导通电阻可重构计算芯片用晶体管及制造方法。

背景技术:

2.依赖工艺的进步,传统计算架构下的处理器性能可以不断提升,足以满足迅速增长的市场需求。随摩尔定律逐渐趋缓,依赖工艺提升性能的方式难以延续,探索新体系架构成为提高处理器性能的又一出路。可重构计算架构越来越受到重视。2015年起,可重构计算(cgra)应用在ai计算、神经网络计算场景,并设计了一系列ai芯片,同年《国际半导体技术路线图》将cgra作为未来最具前途非冯

·

诺依曼体系结构重点介绍。2017年,美国国防部高级研究计划局推出“电子复兴计划(eri)”,强调软件定义硬件架构,其本质就是软件和硬件均具可编程性的可重构计算架构。从2016年起,多家国际大公司纷纷积极引入可重构计算技术,计划推出新产品面向市场。cgra的架构具有天然可扩展性,通过算力扩展,其高能效,灵活性的特点会也非常适合云端市场。当前的可重构计算允许这几种从事模块级、逻辑门级甚至是晶体管级别的设计,对于晶体管级别的设计,可重构计算架构中的最小单元,即为mosfet场效应晶体管,其导通类型即n类型或p类型是在芯片工艺完成的时候就确定好的,对于可重构计算架构设计者,所需两种类型晶体管的比例可能存在巨大差异,所以制作导电类型可重构的晶体管,对于提高可重构计算架构芯片的晶体管级利用效率具有重要意义,一些基于源漏肖特基势垒的可重构晶体管被提出,其导电类型可以通过编程栅来定义,然而基于肖特基势垒的可重构晶体管,由于其源漏寄生电阻较大,在导通时很难产生较高电流,即导通时的导通电阻较高,不利于电信号的传输。

技术实现要素:

3.发明目的

4.本发明针对上述源漏寄生电阻大,导通电阻较高,导通时很难产生较高电流,不利于电信号传输的问题,研制了低导通电阻可重构计算芯片用晶体管及制造方法。

5.技术方案

6.低导通电阻可重构计算芯片用晶体管,包含衬底,衬底上方为掩埋氧化层,掩埋氧化层为绝缘材料层,掩埋氧化层的上方为本征硅、负掺杂源区、正掺杂源区、负掺杂漏区、正掺杂漏区、绝缘介质层、可重构隧穿绝缘层、栅电极绝缘层、可重构电荷存储层和栅电极;本征硅为半导体材料,本征硅的上表面和前后侧表面的中央部分与栅电极绝缘层相互接触;本征硅的上表面和前后侧表面的左右两侧与可重构隧穿绝缘层相互接触;本征硅的上表面和前后侧表面的位于栅电极绝缘层和可重构隧穿绝缘层之间的部分与绝缘介质层相互接触;负掺杂源区和正掺杂源区分别为掺有v族元素和iii族元素的半导体区域;负掺杂源区和正掺杂源区同时位于本征硅的左侧,并与本征硅的左侧表面相互接触;负掺杂源区的前侧表面和正掺杂源区的后侧表面与绝缘介质层相互接触;负掺杂源区的后侧表面和正掺杂

源区的前侧表面相互接触;负掺杂源区和正掺杂源区的上表面的左侧与源电极相互接触,形成反阻挡型欧姆接触;负掺杂源区和正掺杂源区的上表面的右侧与绝缘介质层相互接触;负掺杂漏区和正掺杂漏区分别为掺有v族元素和iii族元素的半导体区域;负掺杂漏区和正掺杂漏区同时位于本征硅的右侧,并与本征硅的右侧表面相互接触;负掺杂漏区的前侧表面和正掺杂漏区的后侧表面与绝缘介质层相互接触;负掺杂漏区的后侧表面和正掺杂漏区的前侧表面相互接触;负掺杂漏区和正掺杂漏区的上表面的右侧与漏电极相互接触,形成反阻挡型欧姆接触;负掺杂漏区和正掺杂漏区的上表面的左侧与绝缘介质层相互接触;绝缘介质层为绝缘介质材料;可重构隧穿绝缘层为厚度低于3纳米的绝缘介质材料;可重构隧穿绝缘层的上表面和前后侧表面与可重构电荷存储层左右两侧的下表面相互接触;可重构电荷存储层为多晶硅、氮化硅、氧化铝、金属、合金或金属硅化物中的一种;栅电极绝缘层为绝缘介质材料;栅电极绝缘层的上表面和前后侧表面与栅电极相互接触;可重构电荷存储层的上表面与可重构电极绝缘层的下表面相互接触;可重构电荷存储层的左右两侧的外表面和内表面与绝缘介质层相互接触;可重构电荷存储层呈倒“u”形,位于可重构隧穿绝缘层的上方;可重构电荷存储层通过绝缘介质层与可重构隧穿绝缘层与外界绝缘隔离;栅电极为多晶硅、氮化硅、氧化铝、金属、合金或金属硅化物中的一种;栅电极的上方表面,左右两侧外表面与绝缘介质层相互接触;可重构电极绝缘层为绝缘介质材料;可重构电极绝缘层的上表面与可重构电极相互接触;可重构电极绝缘层的厚度大于可重构隧穿绝缘层的厚度;可重构电极为多晶硅、金属、合金或金属硅化物中的一种;源电极为多晶硅、金属、合金或金属硅化物中的一种;源电极通过绝缘介质层与可重构电荷存储层、可重构电极相互绝缘隔离;漏电极为多晶硅、金属、合金或金属硅化物中的一种;漏电极通过绝缘介质层与可重构电荷存储层、可重构电极相互绝缘隔离。

7.优点及效果

8.1.低导通电阻:

9.本发明所述的低导通电阻可重构计算芯片用晶体管及制造方法,其导通电阻与基于cmos基础电路的n型晶体管或p型晶体管相当。对比基于源漏肖特基势垒的可重构晶体管,本发明所提出的低导通电阻可重构计算芯片用晶体管,当其工作在n型模式和p型模式时,其导通电阻远小于基于源漏肖特基势垒的可重构晶体管。

10.2.导电类型非易失性重构:

11.可通过可重构电极对可重构电荷存储层内写入正电荷或负电荷的方式来对本发明所述的低导通电阻可重构计算芯片用晶体管的导电类型进行非易失性重构。

附图说明

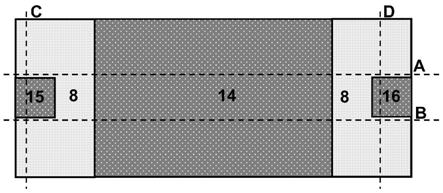

12.图1为本发明低导通电阻可重构计算芯片用晶体管的俯视图;

13.图2为本发明的沿图1虚线a的剖面图;

14.图3为本发明的沿图1虚线b的剖面图;

15.图4为本发明的沿图1虚线c的剖面图;

16.图5为本发明的沿图1虚线d的剖面图;

17.图6为本发明的步骤一的俯视图;

18.图7为本发明的步骤一的沿虚线a的剖面图;

19.图8为本发明的步骤二的俯视图;

20.图9为本发明的步骤二的沿虚线a的剖面图;

21.图10为本发明的步骤二的沿虚线b的剖面图;

22.图11为本发明的步骤二的沿虚线c的剖面图;

23.图12为本发明的步骤二的沿虚线d的剖面图;

24.图13为本发明的步骤二的沿虚线e的剖面图;

25.图14为本发明的步骤三的俯视图;

26.图15为本发明的步骤三的沿虚线a的剖面图;

27.图16为本发明的步骤三的沿虚线b的剖面图;

28.图17为本发明的步骤三的沿虚线c的剖面图;

29.图18为本发明的步骤四的俯视图;

30.图19为本发明的步骤四的沿虚线a的剖面图;

31.图20为本发明的步骤四的沿虚线b的剖面图;

32.图21为本发明的步骤四的沿虚线c的剖面图;

33.图22为本发明的步骤五的俯视图;

34.图23为本发明的步骤五的沿虚线a的剖面图;

35.图24为本发明的步骤五的沿虚线b的剖面图;

36.图25为本发明的步骤五的沿虚线c的剖面图;

37.图26为本发明的步骤六的俯视图;

38.图27为本发明的步骤六的的沿虚线a的剖面图;

39.图28为本发明的步骤六的的沿虚线b的剖面图;

40.图29为本发明的步骤六的的沿虚线c的剖面图;

41.图30为本发明的步骤七的俯视图;

42.图31为本发明的步骤七的沿虚线a的剖面图;

43.图32为本发明的步骤七的沿虚线b的剖面图;

44.图33为本发明的步骤七的沿虚线c的剖面图;

45.图34为本发明的步骤七的沿虚线d的剖面图;

46.图35为本发明的步骤七的沿虚线e的剖面图;

47.图36为本发明的步骤八的的俯视图;

48.图37为本发明的步骤八的沿虚线a的剖面图;

49.图38为本发明的步骤八的沿虚线b的剖面图;

50.图39为本发明的步骤八的沿虚线c的剖面图;

51.图40为本发明的步骤八的沿虚线d的剖面图;

52.图41为本发明的步骤八的沿虚线e的剖面图;

53.图42为本发明的步骤九的的俯视图;

54.图43为本发明的步骤九的沿虚线a的剖面图;

55.图44为本发明的步骤九的沿虚线b的剖面图;

56.图45为本发明的步骤九的沿虚线c的剖面图;

57.图46为本发明的步骤九的沿虚线d的剖面图;

58.图47为本发明的步骤九的沿虚线e的剖面图;

59.图48为本发明的步骤十的的俯视图;

60.图49为本发明的步骤十的沿虚线a的剖面图;

61.图50为本发明的步骤十的沿虚线b的剖面图;

62.图51为本发明的步骤十的沿虚线c的剖面图;

63.图52为本发明的步骤十一的的俯视图;

64.图53为本发明的步骤十一的沿虚线a的剖面图;

65.图54为本发明的步骤十一的沿虚线b的剖面图;

66.图55为本发明的步骤十一的沿虚线c的剖面图;

67.附图标记:1、衬底;2、掩埋氧化层;3、本征硅;4、负掺杂源区;5、正掺杂源区;6、负掺杂漏区;7、正掺杂漏区;8、绝缘介质层;9、可重构隧穿绝缘层;10、栅电极绝缘层;11、可重构电荷存储层;12、栅极电;13、可重构电极绝缘层;14、可重构电极;15、源电极;16、漏电极。

具体实施方式

68.下面结合附图对本发明做进一步的说明:

69.实施例

70.结合图1

‑

5,低导通电阻可重构计算芯片用晶体管,包含衬底1,衬底1上方设有掩埋氧化层2,掩埋氧化层2为绝缘材料层,掩埋氧化层2的上方设有本征硅3、负掺杂源区4、正掺杂源区5、负掺杂漏区6、正掺杂漏区7、绝缘介质层8、可重构隧穿绝缘层9、栅电极绝缘层10、可重构电荷存储层11和栅电极12;本征硅3为半导体材料,本征硅3的上表面和前后侧表面的中央部分与栅电极绝缘层10相互接触;本征硅3的上表面和前后侧表面的左右两侧与可重构隧穿绝缘层9相互接触;本征硅3的上表面和前后侧表面的位于栅电极绝缘层10和可重构隧穿绝缘层9之间的部分与绝缘介质层8相互接触;负掺杂源区4和正掺杂源区5分别为掺有v族元素和iii族元素的半导体区域;负掺杂源区4和正掺杂源区5同时位于本征硅3的左侧,并与本征硅3的左侧表面相互接触;负掺杂源区4的前侧表面和正掺杂源区5的后侧表面与绝缘介质层8相互接触;负掺杂源区4的后侧表面和正掺杂源区5的前侧表面相互接触;负掺杂源区4和正掺杂源区5的上表面的左侧与源电极15相互接触,形成反阻挡型欧姆接触;负掺杂源区4和正掺杂源区5的上表面的右侧与绝缘介质层8相互接触;负掺杂漏区6和正掺杂漏区7分别为掺有v族元素和iii族元素的半导体区域;负掺杂漏区6和正掺杂漏区7同时位于本征硅3的右侧,并与本征硅3的右侧表面相互接触;负掺杂漏区6的前侧表面和正掺杂漏区7的后侧表面与绝缘介质层8相互接触;负掺杂漏区6的后侧表面和正掺杂漏区7的前侧表面相互接触;负掺杂漏区6和正掺杂漏区7的上表面的右侧与漏电极16相互接触,形成反阻挡型欧姆接触;负掺杂漏区6和正掺杂漏区7的上表面的左侧与绝缘介质层8相互接触;绝缘介质层8为绝缘介质材料;可重构隧穿绝缘层9为厚度低于3纳米的绝缘介质材料;可重构隧穿绝缘层9的上表面和前后侧表面与可重构电荷存储层11左右两侧的下表面相互接触;可重构电荷存储层11为多晶硅、氮化硅、氧化铝、金属、合金或金属硅化物中的一种;栅电极绝缘层10为绝缘介质材料;栅电极绝缘层10的上表面和前后侧表面与栅电极12相互接触;可重构电荷存储层11的上表面与可重构电极绝缘层13的下表面相互接触;可重构电荷存储层11的左右两侧的外表面和内表面与绝缘介质层8相互接触;可重构电荷存储层11

呈倒“u”形,位于可重构隧穿绝缘层9的上方;可重构电荷存储层11通过绝缘介质层8与可重构隧穿绝缘层9与外界绝缘隔离;栅电极12为多晶硅、氮化硅、氧化铝、金属、合金或金属硅化物中的一种;栅电极12的上方表面,左右两侧外表面与绝缘介质层8相互接触;可重构电极绝缘层13为绝缘介质材料;可重构电极绝缘层13的上表面与可重构电极14相互接触;可重构电极绝缘层13的厚度大于可重构隧穿绝缘层9的厚度;可重构电极14为多晶硅、金属、合金或金属硅化物中的一种;源电极15为多晶硅、金属、合金或金属硅化物中的一种;源电极15通过绝缘介质层8与可重构电荷存储层11、可重构电极14相互绝缘隔离;漏电极16为多晶硅、金属、合金或金属硅化物中的一种;漏电极16通过绝缘介质层8与可重构电荷存储层11、可重构电极14相互绝缘隔离。

71.结合图1

‑

5,一种低导通电阻可重构计算芯片用晶体管的使用方法:

72.通过对可重构电极14相对于源电极15和漏电极16施加正电压,利用可重构隧穿绝缘层9在高场强下产生绝缘层隧穿效应,将负电荷写入可重构电荷存储层11,使可重构电荷存储层11对本征硅3的左右两端产生负的电场效应,在本征硅3的左右两端形成空穴堆积层,完成对低导通电阻可重构计算芯片用晶体管的p型模式编程;

73.在完成对低导通电阻可重构计算芯片用晶体管的p型模式编程后,通过对栅电极12施加负电压,在本征硅3中形成空穴沟道,使得电子可以从漏电极16,经由正掺杂漏区7、可重构电荷存储层11所控制的本征硅3的右侧区域、栅电极12所控制的本征硅3的中央区域、可重构电荷存储层11所控制的本征硅3的左侧区域、正掺杂源区5,最后由源电极15流出,使低导通电阻可重构计算芯片用晶体管处于p型导通状态;在完成对低导通电阻可重构计算芯片用晶体管的n型模式编程后,通过对栅电极12施加正电压,使低导通电阻可重构计算芯片用晶体管处于p型导截至状态;

74.通过对可重构电极14相对于源电极15和漏电极16施加负电压,利用可重构隧穿绝缘层9在高场强下产生绝缘层隧穿效应,将正电荷写入可重构电荷存储层11,使可重构电荷存储层11对本征硅3的左右两端产生正的电场效应,在本征硅3的左右两端形成电子堆积层,完成对低导通电阻可重构计算芯片用晶体管的n型模式编程;

75.在完成对低导通电阻可重构计算芯片用晶体管的n型模式编程后,通过对栅电极12施加正电压,在本征硅3中形成电子沟道,使得电子可以从源电极15,经由负掺杂源区4、可重构电荷存储层11所控制的本征硅3的左侧区域、栅电极12所控制的本征硅3的中央区域、可重构电荷存储层11所控制的本征硅3的右侧区域、负掺杂漏区6,最后由漏电极16流出,使低导通电阻可重构计算芯片用晶体管处于n型导通状态;在完成对低导通电阻可重构计算芯片用晶体管的n型模式编程后,通过对栅电极12施加负电压,使低导通电阻可重构计算芯片用晶体管处于n型导截至状态;

76.低导通电阻可重构计算芯片用晶体管的制造方法,在soi晶圆衬底上实现的制造步骤如下(不仅限于此方法):

77.步骤一:结合图6

‑

7,提供一个soi晶圆,最下方为衬底1,衬底的上面是掩埋氧化层2,掩埋氧化层2的上表面为半导体薄膜,通过光刻、刻蚀和淀积工艺,初步形成本征硅3;

78.步骤二:结合图8

‑

13,通过离子注入工艺,分别形成负掺杂源区4、正掺杂源区5、负掺杂漏区6和正掺杂漏区7;

79.步骤三:结合图14

‑

17,通过淀积工艺,在步骤二基础之上淀积绝缘介质层,再通过

平坦化处理至露出本征硅3,初步形成绝缘介质层8,再通过刻蚀工艺刻蚀掉本征硅3前后表面左右两侧的中央部分的绝缘介质层至露出掩埋氧化层2,进一步形成绝缘介质层8;

80.步骤四:结合图18

‑

21,通过淀积工艺,在步骤三基础之上淀积绝缘介质,再通过平坦化处理至露出本征硅3,初步形成可重构隧穿绝缘层9和栅电极绝缘层10;

81.步骤五:结合图22

‑

25,通过刻蚀工艺,在步骤四基础之上,刻蚀掉步骤四所形成的位于所形成的位于半导体薄膜3的前方部分的可重构隧穿绝缘层9前方的部分区域至露出掩埋氧化层2;刻蚀掉步骤四所形成的位于半导体薄膜3前方的部分的栅电极绝缘层10的前方部分区域至露出掩埋氧化层2;刻蚀掉步骤四所形成的位于所形成的位于半导体薄膜3的后方部分的可重构隧穿绝缘层9后方的部分区域至露出掩埋氧化层2;刻蚀掉步骤四所形成的位于半导体薄膜3的后方部分的栅电极绝缘层10后方的部分区域至露出掩埋氧化层2;

82.步骤六:结合图26

‑

29,通过淀积工艺,在步骤五基础之上淀积金属、合金、多晶硅或金属硅化物中的一种,再通过平坦化处理至露出半导体薄膜3,初步形成可重构电荷存储层11和栅电极12;

83.步骤七:结合图30

‑

35,通过淀积工艺,在步骤六基础之上淀积绝缘层,并通过刻蚀工艺刻蚀掉绝缘层的中央部分和左右两侧的中央部分至露出半导体薄膜3,再通过淀积工艺淀积绝缘层,再通过平坦化处理至露出绝缘介质层8,进一步形成可重构隧穿绝缘层9和栅电极绝缘层10;再通过刻蚀工艺刻蚀掉位于可重构隧穿绝缘层9的前方区域至露出步骤六所初步形成的可重构电荷存储层11和位于可重构隧穿绝缘层9的后方区域至露出步骤六所初步形成的可重构电荷存储层11;刻蚀掉位于栅电极绝缘层10的前方区域至露出步骤六所初步形成的栅电极12和位于栅电极绝缘层10的下方区域至露出步骤六所初步形成的栅电极12;再通过淀积工艺淀积金属、合金、多晶硅或金属硅化物中的一种,再通过平坦化处理至露出绝缘介质层8,进一步形成可重构电荷存储层11和栅电极12;

84.步骤八:结合图36

‑

41,通过淀积工艺,在步骤七基础之上淀积绝缘层,平坦化后再通过刻蚀工艺刻蚀掉位于步骤七所生成的可重构隧穿绝缘层9、栅电极绝缘层10以及可重构电荷存储层11和栅电极12上方的绝缘层,进一步形成绝缘介质层8,再通过淀积工艺淀积金属、合金、多晶硅或金属硅化物中的一种,平坦化至露出绝缘介质层8,进一步形成可重构电荷存储层11和栅电极12;

85.步骤九:结合图42

‑

47,通过淀积工艺,在步骤八基础之上淀积绝缘层,平坦化后再通过刻蚀工艺刻蚀掉位于步骤八所生成的可重构电荷存储层11上方的绝缘层,进一步形成绝缘介质层8,再通过淀积工艺淀积金属、合金、多晶硅或金属硅化物中的一种,平坦化至露出绝缘介质层8,进一步形成可重构电荷存储层11;

86.步骤十:结合图48

‑

51,通过淀积工艺,在步骤九基础之上淀积绝缘层,平坦化后再通过刻蚀工艺刻蚀掉位于步骤九所生成的可重构电荷存储层11上方,以及可重构电荷存储层11的两侧部分之间的绝缘层,进一步形成绝缘介质层8,再通过淀积工艺淀积金属、合金、多晶硅或金属硅化物中的一种,平坦化至露出绝缘介质层8,进一步形成可重构电荷存储层11;

87.步骤十一:结合图52

‑

55,通过淀积工艺,在步骤十基础之上淀积绝缘层,平坦化后再通过刻蚀工艺刻蚀掉位于步骤十所生成的可重构电荷存储层11上方的绝缘层,进一步形成绝缘介质层8,再通过淀积工艺淀积绝缘层,平坦化至露出绝缘介质层8,形成可重构电极

绝缘层13;再通过淀积工艺淀积绝缘层,平坦化后再通过刻蚀工艺刻蚀掉位于可重构电极绝缘层13上方的绝缘层,进一步形成绝缘介质层8,再通过淀积工艺淀积金属、合金、多晶硅或金属硅化物中的一种,平坦化至露出绝缘介质层8,形成可重构电极14;

88.步骤十二:结合图1

‑

5,通过刻蚀工艺,在步骤十一基础之上刻蚀掉绝缘介质层8左侧中间部分区域至露出负掺杂源区4、正掺杂源区5的左侧部分区域的上表面;刻蚀掉绝缘介质层8右侧中间部分区域至露出负掺杂漏区6、正掺杂漏区7的右侧部分区域的上表面;再通过淀积工艺,淀积金属、合金或金属硅化物中的一种,再通过平坦化处理至露出隔离绝缘介质8的上表面,形成源电极15和漏电极16。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。