一种快速找到wifi帧头的fpga实现方法及系统

技术领域

1.本发明涉及一种无线通信技术,尤其涉及一种快速找到wifi帧头的fpga实现方法及系统。

背景技术:

2.在wifi的接收过程中,在进行基带算法处理之前会有一个初步寻找帧头的操作。初步找到帧头的位置,主要目的节省后续做相关同步的时间。因为后面的同步做法是采用循环相关去做处理。接收到的wifi信号帧跟信号帧之间存在gap(信号中断),如图2所示的两个信号帧之间的空白间隔。

3.通常的做法是采用滑动窗平均的做法,有的甚至采用双滑动窗去处理。双滑动窗和单滑动窗平均的原理类似,它主要采用后窗减去前窗差分的方式找到峰值,利用峰值跟设定的门限值作为对比,超过门限值且达到最大值的时刻作为粗帧头的初步位置。相对于单滑动窗来讲,双滑动窗消耗的资源会更多。

4.对于上述查找帧头位置方式,fpga在运算过程中消耗的资源较多。同时随着查找精度的提高,滑动窗的长度要求变长,对应的逻辑资源消耗会更多。所以在逻辑资源比较紧张,或者时序比较紧张的情况下,该实现方案并非一个很好的选择。

技术实现要素:

5.为解决现有技术中的问题,本发明提供一种快速找到wifi帧头的fpga实现方法及系统,在能实现比滑动窗口更高精度的查找帧头的同时又能节省比较多的逻辑资源。

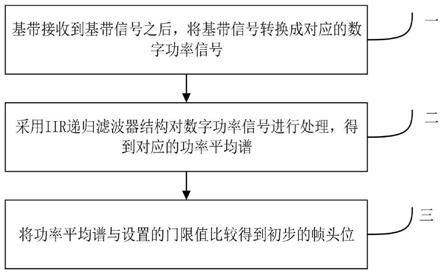

6.本发明快速找到wifi帧头的fpga实现方法,其特征在于:包括如下步骤:

7.步骤一:基带接收到基带信号之后,将基带信号转换成对应的数字功率信号;

8.步骤二:采用iir递归滤波器结构对数字功率信号进行处理,得到对应的功率平均谱;

9.步骤三:将功率平均谱与设置的门限值比较得到初步的帧头位,

10.所述iir递归滤波器结构的查分方程为:

[0011][0012]

其中,x(n),y(n)分别为系统在nts时刻对应的离散输入点以及输出点,y(n

‑

1)对应为延迟一个采样点的y(n),n为截位位宽,其中ts对应的采样时钟的周期。

[0013]

本发明作进一步改进,步骤二中,所述iir递归滤波器结构对数字功率信号进行处理的方法包括以下子步骤:

[0014]

a21:初始化系统的输出,并定义截位的位宽n;

[0015]

a22:用非阻塞赋值获取中间过程值截位n位,逻辑代码:a=(x(n)

‑

y(n))>>n;

[0016]

a23:用阻塞赋值获取中间值,使得a和y(n)的累加经过一个clk之后赋值给,逻辑代码:。

[0017]

a24:用非阻塞赋值得到最终输出结果。

[0018]

本发明作进一步改进,步骤a23中,赋值给s_y最终实现

[0019]

本发明作另一种改进,步骤二中,fpga实现过程用到一个乘法器,所述iir递归滤波器结构的查分方程转换为:

[0020]

本发明作进一步改进,所述iir递归滤波器结构对数字功率信号进行处理的方法包括以下子步骤:

[0021]

b21:初始化系统的输出y(0)=0,并定义截位的位宽n;

[0022]

b22:采用阻塞赋值获取中间值s_y_n_1,实现的函数为:x(n) (2

n

‑

1)

·

y(n

‑

1),逻辑代码实现:s_y_n_1<=y(n)*(2^n

‑

1) x(n);

[0023]

b23:采用非阻塞赋值,用截位的方式实现最终的除法操作逻辑代码实现:y(n)=s_y_n_1>>n,y(n)对应为输出的平均结果。

[0024]

本发明还提供一种实现所述所述的快速找到wifi帧头的fpga实现方法的系统,包括:

[0025]

数字功率转换模块:用于在基带接收到基带信号之后,将基带信号转换成对应的数字功率信号;

[0026]

处理模块:用于采用iir递归滤波器结构对数字功率信号进行处理,得到对应的功率平均谱;

[0027]

帧头位获取模块:将功率平均谱与设置的门限值比较得到初步的帧头位,

[0028]

所述iir递归滤波器结构的查分方程为:

[0029][0030]

其中,x(n),y(n)分别为系统在nts时刻对应的离散输入点以及输出点,y(n

‑

1)对应为延迟一个采样点的y(n),n为截位位宽,其中ts对应的采样时钟的周期。

[0031]

与现有技术相比,本发明的有益效果是:相对于滑动窗去实现查找帧头,本发明提供的fpga查找方式能够节省资源;对于滑动窗来讲,要求精度变高,对应的窗的长度会边长,消耗的资源会增加很多。而对于本发明提供的方式来讲,随着精度的变高,对应的资源并没有增加。

附图说明

[0032]

图1为本发明方法流程图;

[0033]

图2为单滑动窗数字功率信号示意图;

[0034]

图3为功率平均谱结构示意图;

[0035]

图4为采用iir递归滤波器结构的差分方程n=6的时候,对应的幅频响应图和相频示意图;

[0036]

图5为采用fir结构的差分方程n=63的时候,对应的幅频响应图和相频示意图。

具体实施方式

[0037]

下面结合附图和实施例对本发明做进一步详细说明。

[0038]

如图1所示,本发明快速找到wifi帧头的fpga实现方法,其特征在于:包括如下步骤:

[0039]

步骤一:在基带接收到iq的基带信号之后,将iq的信号通过i2 q2计算成对应的数字功率信号,如图2所示。

[0040]

步骤二:采用iir递归滤波器结构对数字功率信号进行处理,得到对应的功率平均谱,如图3所示,图3中的n为128,图3中横向的黑线代表设置的门限值;

[0041]

步骤三:通过将y(n)与设置的门限值比较得到初步的帧头位。

[0042]

优选的,步骤二中,本例iir递归滤波器结构的查分方程为:

[0043][0044]

对应的系统函数为:

[0045][0046]

其中,x(n),y(n)分别为系统在nts时刻对应的离散输入点以及输出点,y(n

‑

1)为y(n)对应延迟一个采样周期的值,n为截位位宽,其中ts对应的采样时钟的周期。x(n

‑

1)代表x(n)延迟一个采样点的输入。h(z)代表的是系统转移函数,要求整个系数是线性以及具备因果关系的。

[0047]

而对于常规做法是采用fir滤波器结构方式去实现粗帧头查找,对应的差分方程如下式:

[0048][0049]

对应的系统函数为:

[0050][0051]

两个系统函数对比:

[0052]

当采用iir(递归)结构的差分方程n=6的时候,对应的系统函数如图4所示,当fir结构的差分方程n=63的时候,对应的系统函数如图5所示。

[0053]

从这两幅图中的幅度频率响应图的对比来看,对于相同的归一化频率点,iir(递归滤波器)带外的抑制度要比fir(有限长单位冲激响应滤波器,又称非递归型滤波器)的要更大,例如在0.02π的归一化频点fir抑制度为

‑

6db,而iir的抑制度为

‑

12db。同样对于远端的高频分量抑制的效果iir要优于fir滤波器,所以对于平均效果来说,一阶iir系统比62阶

fir系统要更优一点。

[0054]

同时对于iir因为是无限冲击响应,在实际工程中需要考虑其计算结果的稳定性,例如对于数据一直做递归累加的话,很可能结果会出现不收敛,会存在溢出的风险。而本发明的系统函数极点在单元圆内,右边序列收敛域包括单位圆,所以是一个稳定的系统。然而在fpga上工程的做法需要考虑处理的累加位宽,同时从系统函数看,它的极点虽然在单位圆内,但也很接近单位圆。通常的做法需要给一个定时脉冲类似pp1s或者pp2s作为清零操作,防止溢出问题。但是对于实际的wifi接收信号来讲,接收到的信号帧跟信号帧之间会存在gap,而接收端来讲gap这一段对应的是噪底信号,幅度很低,可以认为是在做清零操作。所以针对本发明wifi查找帧头的过程不需要pp1s或者pp2s的清零操作,直接用gap纳入计算就可以,方法更加简单。

[0055]

作为本发明的一个实施例,fpga实现过程差分方程步骤如下:

[0056]

1)x(n),y(n)分别为系统的输入以及输出,y(n

‑

1)对应为延迟一个采样点的y(n);

[0057]

2)初始化系统的输出y(0)=0,并定义截位的位宽n;

[0058]

3)用非阻塞赋值获取中间过程值a,截位n位。对应函数实现为:逻辑代码实现:a=(x(n)

‑

y(n))>>n;

[0059]

4)用阻塞赋值获取中间值s_y,使得a和y(n)的累加经过一个clk之后赋值给s_y,最终实现逻辑代码实现:s_y<=a y(n);

[0060]

5)用非阻塞赋值得到最终输出结果y(n)。逻辑代码实现:y(n)=s_y;

[0061]

6)y(n)对应为输出的平均结果。

[0062]

作为本发明的另外一种实施例,本例fpga实现过程需要用到一个乘法器,所述差分方程转换成另外一种形式为:具体的实现过程为:

[0063]

1)x(n),y(n)分别为系统的输入以及输出,y(n

‑

1)对应为延迟一个采样点的y(n);

[0064]

2)初始化系统的输出y(0)=0,并定义截位的位宽n;

[0065]

3)采用阻塞赋值获取中间值s_y_n_1,实现函数操作的内容为:x(n) (2

n

‑

1)

·

y(n

‑

1),逻辑代码实现:s_y_n_1<=y(n)*(2^n

‑

1) x(n);

[0066]

4)采用非阻塞赋值,用截位的方式实现最终的除法操作逻辑代码实现:y(n)=s_y_n_1>>n;

[0067]

5)y(n)对应为输出的平均结果。

[0068]

第一种实施例只需要加法器就可以实现该功能,第二种实施例的实现方式多了一个乘法器。

[0069]

通过上述方法可知,本发明具有以下优势:

[0070]

1.相对于滑动窗去实现查找帧头,本文提供的粗帧头的fpga查找方式能够节省更

多的逻辑资源。

[0071]

2.对于滑动窗来讲,要求精度变高,对应的窗的长度会边长,消耗的资源会增加很多。而对于本文提供的基于fpga粗帧头查找方式来讲,随着精度的变高,对应的资源并没有增加。

[0072]

以上所述之具体实施方式为本发明的较佳实施方式,并非以此限定本发明的具体实施范围,本发明的范围包括并不限于本具体实施方式,凡依照本发明所作的等效变化均在本发明的保护范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。