1.本公开总体而言涉及图像数据处理领域,具体而言涉及一种用于图像数据同步的装置、方法及图像采集系统。

背景技术:

2.图像采集系统是智能设备中不可缺少的一部分。一个完整的图像采集系统一般包括cmos(complementary metal

‑

oxide semiconductor,互补金属氧化物半导体)传感器、帧格式解码单元、图像预处理单元、isp(image signal processing,图像信号处理)数据处理单元、图像存储、显示等单元。

3.在图像预处理单元中需要对图像数据进行同步处理,从而将图像数据从诸如mipi(mobile industry processor interface,移动产业处理器接口)之类的接口的时钟域同步到像素处理的时钟域。这里的图像数据同步的通常做法包括:先将图像数据写入行缓冲器(buffer),在像素处理时钟域读出图像数据,并将图像数据送入后级模块以进行处理。随着cmos传感器的分辨率及帧率的不断增加、接口速率的不断提高,图像数据的行周期(即,图像的每行像素数据所对应的时间长度)变得越来越短。因此,输入到行缓冲器的图像数据的速率变得越来越高,从而可能导致行缓冲器溢出。

4.为了避免行缓冲器溢出,需要提高行缓冲器的读出速率或提高行缓冲器的容量。然而,高读出时钟频率可能会增加芯片后端处理电路时序收敛的难度,同时可能会增加芯片的动态功耗。

技术实现要素:

5.为了解决上述问题,本公开提供了一种包括分组轮询读出的多个fifo(first input first output,先入先出)存储器的用于图像数据同步的装置和相关方法,用于实现高速率的图像数据同步。

6.根据本公开的第一方面,提供了一种用于图像数据同步的装置,包括:一个或多个数据缓存模块,每个数据缓存模块包括n个先入先出fifo存储器,被配置为以像素为单位在n个fifo存储器中写入图像数据的像素行,并且在读出使能控制信号的控制下从所述n个fifo存储器中读出图像数据,其中,n为不小于2的正整数;fifo读出控制模块,所述fifo读出控制模块被配置为:在图像数据输入速率低于第一阈值的情况下,生成读出使能控制信号使得以每个读出时钟周期内读出1个fifo存储器的方式从所述n个fifo存储器中轮询读出图像数据,以及在图像数据输入速率不低于所述第一阈值的情况下,生成读出使能控制信号使得以每个读出时钟周期内读出m个fifo存储器的方式从所述n个fifo存储器中轮询读出图像数据,其中,m为不小于2的正整数,并且m≤n;以及数据打包模块,所述数据打包模块被配置为打包从数据缓存模块读出的图像数据。

7.根据本公开的第二方面,提供了一种用于图像数据同步的方法,包括:以像素为单位在数据缓存模块中包括的n个先入先出fifo存储器中写入图像数据的像素行;利用fifo

读出控制模块生成读出使能控制信号;在读出使能控制信号的控制下从所述n个fifo存储器中读出图像数据,其中,n为不小于2的正整数;以及利用数据打包模块打包从数据缓存模块读出的图像数据;其中,从所述n个fifo存储器中读出图像数据包括:在图像数据输入速率低于第一阈值的情况下,以每个读出时钟周期内读出1个fifo存储器的方式从所述n个fifo存储器中轮询读出图像数据,以及在图像数据输入速率不低于所述第一阈值的情况下,以每个读出时钟周期内读出m个fifo存储器的方式从所述n个fifo存储器中轮询读出图像数据,其中,m为不小于2的正整数,并且m≤n。

8.根据本公开的第三方面,提供了一种图像采集系统,包括:cmos传感器;帧解码单元,用于将cmos传感器的输出信号解码为以像素为单位的图像数据;以及根据第一方面所述的装置,用于将来自帧解码单元的图像数据同步到像素处理时钟域。

9.通过以下参照附图对本公开的示例性实施例的详细描述,本公开的其它特征及其优点将会变得清楚。

附图说明

10.构成说明书的一部分的附图描述了本公开的实施例,并且连同说明书一起用于解释本公开的原理。

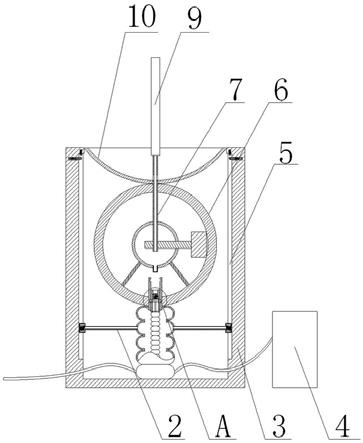

11.参照附图,根据下面的详细描述,可以更加清楚地理解本公开,其中:图1示出了根据本公开的实施例的用于图像数据同步的装置的示意图;图2示出了根据本公开的实施例的用于图像数据同步的装置的示意图;图3示出了根据本公开的实施例的用于图像数据同步的方法的流程图;图4示出了根据本公开的实施例的图像采集系统的示意图。

12.为了便于理解,在附图等中所示的各结构的位置、尺寸及范围等有时不表示实际的位置、尺寸及范围等。因此,公开并不限于附图等所公开的位置、尺寸及范围等。此外,附图不必按比例绘制,一些特征可能被放大以示出具体组件的细节。

具体实施方式

13.现在将参照附图来详细描述本公开的各种示例性实施例。应注意到:除非另外具体说明,否则在这些实施例中阐述的部件和步骤的相对布置、数字表达式和数值不限制本公开的范围。

14.以下对至少一个示例性实施例的描述实际上仅仅是说明性的,决不作为对本公开及其应用或使用的任何限制。也就是说,本文中的电路和方法是以示例性的方式示出,来说明本公开中的电路或方法的不同实施例,而并非意图限制。本领域的技术人员将会理解,它们仅仅说明可以用来实施本公开的示例性方式,而不是穷尽的方式。

15.对于相关领域普通技术人员已知的技术、方法和设备可能不作详细讨论,但在适当情况下,所述技术、方法和设备应当被视为授权说明书的一部分。

16.cmos传感器可以通过mipi接口将数据送入帧格式解码单元。帧格式解码单元可以按照mipi协议对帧格式进行解码,将以字节为单位排列的图像数据转换为以像素为单位的图像数据(简称为像素数据)逐行输出,通常为多像素数据同时输出。随后,解码单元可以将像素数据和接口时钟信号送入图像预处理单元。因此,需要将图像数据从接口时钟域同步

到像素处理时钟域的装置。

17.图1示出了根据本公开的实施例的用于图像数据同步的装置100的示意图。例如,同步装置100可以是耦合到帧格式解码单元的图像预处理单元的一部分,或者耦合在帧格式解码单元和图像预处理单元之间。同步装置100可以从帧格式解码单元接收图像数据和时钟信号,用于将图像数据从接口时钟域同步到像素处理时钟域。如图1所示,装置100包括数据缓存模块110、fifo读出控制模块120和数据打包模块130。其中,数据缓存模块110包括多个异步fifo存储器,这些fifo存储器可以被配置为写入图像数据,在fifo读出控制模块120输出的读出控制信号的控制下将图像数据读出,并传输到数据打包模块130以进行打包;fifo读出控制模块120可以被配置为生成多个读出控制信号,这些读出控制信号被分别输出到各个fifo存储器的读出使能引脚en_r,用于使能各个fifo存储器的读出操作;数据打包模块130可以被配置为接收从各个fifo存储器读出的图像数据并将其按照顺序打包输出。

18.在图1中示出的示例性实施例中,数据缓存模块110包括4个异步fifo存储器111至114。但是应理解的是,本公开不限于此,数据缓存模块110可以包括更多或更少的fifo存储器。fifo存储器111至114可以被配置为在一个写入时钟周期内同时共同写入图像的一行像素数据,即,每个fifo存储器同时分别写入1/4行像素数据。例如,假设图像的一行像素数据按顺序包括像素pixel 0、pixel 1、pixel 2、

……

、pixel 15,则在将该行像素数据写入数据缓存模块110时,同时将pixel 0至pixel 3写入第一fifo存储器111,pixel 4至pixel 7写入第二fifo存储器112,pixel 8至pixel 11写入第三fifo存储器113,pixel 12至pixel 15写入第四fifo存储器114。传输到各个fifo存储器的写入时钟引脚clk_w的写入时钟信号clk1可以是接口时钟域的时钟信号(诸如,以字节为单位的图像数据的时钟)。以mipi接口为例,写入时钟频率可以为(mipi接口的通道(lane)时钟频率/8)。异步fifo存储器111至114可以被配置为在读出时钟信号clk2和由fifo读出控制模块120输出的读出控制信号的控制下读出图像数据,其中,传输到各个fifo存储器的读出时钟引脚clk_r的读出时钟信号clk2是像素处理时钟域的时钟信号。

19.在本公开中,对于包括n个(n为不小于2的正整数)fifo存储器的数据缓存模块,每个fifo存储器的深度(即,fifo存储器能够存储的数据的数量)不小于(图像宽度/n)。例如,在图像尺寸为3840*2160像素,并且数据缓存模块包括4个fifo存储器的情况下,每个fifo存储器的最小深度为(3840/4)=960。在本公开中,每个fifo存储器的宽度(即,fifo存储器能够存储的数据的宽度)不小于图像的像素位宽。例如,在图像数据的像素位宽为12bit的情况下,每个fifo存储器的最小宽度为12bit。

20.fifo读出控制模块120可以被配置为根据图像数据输入速率生成相应的读出控制信号以使得异步fifo存储器111至114按照不同的轮询策略读出图像数据。在图像数据输入速率低于第一阈值的情况下,fifo读出控制模块120生成读出使能控制信号使得以每个读出时钟周期内(例如,在读出时钟沿)读出1个fifo存储器的方式从4个fifo存储器111至114中轮询读出图像数据,即,第一个读出时钟周期内从第一fifo存储器111中读出图像数据,第二个读出时钟周期内从第二fifo存储器112中读出图像数据,第三个读出时钟周期内从第三fifo存储器113中读出图像数据,第四个读出时钟周期内从第四fifo存储器114中读出图像数据,并如此循环。在图像数据输入速率不低于第一阈值的情况下,fifo读出控制模块

120生成读出使能控制信号使得以每个读出时钟周期内(例如,在读出时钟沿)读出2个fifo存储器的方式从4个fifo存储器111至114中轮询读出图像数据,即,第一个读出时钟周期内从第一fifo存储器111和第二fifo存储器112中同时读出图像数据,第二个读出时钟周期内从第三fifo存储器113和第四fifo存储器114中同时读出图像数据,并如此循环。换言之,在图像数据输入速率不低于第一阈值的情况下,以两个fifo存储器为一个fifo分组,每个读出时钟从一个fifo分组中读出图像数据。图像数据的输入速率可以被计算为(1/(行周期/图像宽度)),指示每秒输入的图像数据的像素数量。例如,对于图像尺寸为3840*2160像素并且行周期为7.41

µ

s的图像数据,其输入速率被计算为518mhz,指示每秒输入518m像素的图像。

21.以上所述的fifo存储器的分组方式、图像数据输入速率阈值等参数可以预先设置在fifo读出控制模块120中。图像数据输入速率阈值与同步装置100的后端处理电路(例如,isp数据处理单元)能够实现的最高频率相关联,并且可以根据轮询策略进行设置。例如,对于图1所示的同步装置100,在同步装置100的后端处理电路能够实现的最高频率为300mhz,并且轮询策略为图像数据输入速率低于第一阈值则一个时钟读出1个fifo存储器、不低于第一阈值则一个时钟读出2个fifo存储器的情况下,第一阈值可以被设置为不大于300mhz的值。例如,对于图1所示的同步装置100,在同步装置100的后端处理电路能够实现的最高频率为300mhz,并且轮询策略为图像数据输入速率低于第一阈值则一个时钟读出1个fifo存储器、不低于第一阈值且低于第二阈值则一个时钟读出2个fifo存储器、不低于第二阈值则一个时钟读出4个fifo存储器的情况下,第一阈值可以被设置为不大于300/2=150mhz的值,第二阈值可以被设置为不大于300mhz的值。

22.在根据本公开的实施例中,在图像数据输入速率进一步提高的情况下,可以采取同时读出所有fifo存储器的策略。对于图1中所示的装置100,fifo读出控制模块120可以被进一步配置为:在图像数据输入速率不低于第一阈值并且低于第二阈值的情况下,仍然按照上文所述的轮询读出策略,以两个fifo存储器为一个fifo分组,生成读出使能控制信号使得每个读出时钟从一个fifo分组中读出图像数据;在图像数据输入速率不低于第二阈值的情况下,生成读出使能控制信号使得每个读出时钟从所有fifo存储器中读出图像数据。

23.应理解的是,以上描述的仅仅是非限制性示例,数据缓存模块中包括的fifo存储器的数量以及相应的分组轮询的策略可以不限于此。

24.例如,对于包括6个fifo存储器的数据缓存模块,在图像数据输入速率低于第一阈值的情况下,可以以每个读出时钟周期内读出1个fifo存储器的方式从6个fifo存储器中轮询读出图像数据;在图像数据输入速率不低于第一阈值并且低于第二阈值的情况下,可以将6个fifo存储器分为3个fifo分组,每个分组包括2个fifo存储器,以每个读出时钟周期内读出一组fifo存储器(同时读出2个fifo存储器)的方式从3个fifo分组轮询读出图像数据;在图像数据输入速率不低于第二阈值并且低于第三阈值的情况下,可以将6个fifo存储器分为2个fifo分组,每个分组包括3个fifo存储器,以每个读出时钟周期内读出一组fifo存储器(同时读出3个fifo存储器)的方式从2个fifo分组轮询读出图像数据;在图像数据输入速率不低于第三阈值的情况下,可以以每个读出时钟周期内读出所有6个fifo存储器的方式读出图像数据。

25.例如,对于包括8个fifo存储器的数据缓存模块,在图像数据输入速率低于第一阈

值的情况下,可以以每个读出时钟周期内读出1个fifo存储器的方式从8个fifo存储器中轮询读出图像数据;在图像数据输入速率不低于第一阈值并且低于第二阈值的情况下,可以将8个fifo存储器分为4个fifo分组,每个分组包括2个fifo存储器,以每个读出时钟周期内读出一组fifo存储器(同时读出2个fifo存储器)的方式从4个fifo分组轮询读出图像数据;在图像数据输入速率不低于第二阈值并且低于第三阈值的情况下,可以将8个fifo存储器分为2个fifo分组,每个分组包括4个fifo存储器,以每个读出时钟周期内读出一组fifo存储器(同时读出4个fifo存储器)的方式从2个fifo分组轮询读出图像数据;在图像数据输入速率不低于第三阈值的情况下,可以以每个读出时钟周期内读出所有8个fifo存储器的方式读出图像数据。

26.在本公开的实施例中,fifo读出控制模块可以被进一步配置为根据各个fifo存储器的空标志位进行读出控制。在根据上文所述的轮询策略进行fifo存储器的读出的时候,如果根据策略需要读出其中一个fifo存储器并且该fifo存储器的空标志位指示该fifo存储器不为空,则从该fifo存储器读出图像数据;如果根据策略需要读出其中一个fifo存储器并且该fifo存储器的空标志位指示该fifo存储器为空,则不从该fifo存储器读出图像数据。

27.数据打包模块130可以被配置为按照fifo的轮询策略将数据顺序地打包输出。对于不同的轮询策略,输出数据的位宽相应地有所不同。例如,在每个读出时钟周期内读出1个fifo存储器的情况下,输出数据的位宽不小于像素位宽;在每个读出时钟周期内读出2个fifo存储器的情况下,输出数据位宽不小于(2

×

像素位宽);在每个读出时钟周期内读出4个fifo存储器的情况下,输出数据位宽不小于(4

×

像素位宽)。

28.对于图1中所示的数据缓存模块110包括4个fifo存储器的实施例,在图像数据输入速率低于第一阈值的情况下,数据打包模块130在每个读出时钟周期内从1个fifo存储器接收读出的图像数据,具体而言,顺序地打包从第一fifo存储器111中读出的图像数据、从第二fifo存储器112中读出的图像数据、从第三fifo存储器113中读出的图像数据、从第四fifo存储器114中读出的图像数据,并且如此循环。在图像数据输入速率不低于第一阈值并且低于第二阈值的情况下,数据打包模块130在每个读出时钟周期内从2个fifo存储器接收读出的图像数据,具体而言,例如,顺序地打包从第一fifo分组(包括第一fifo存储器111和第二fifo存储器112)中读出的图像数据、从第二fifo分组(包括第三fifo存储器113和第四fifo存储器114)中读出的图像数据,并且如此循环。

29.以上所述的装置能够有效地在像素处理时钟域的最大频率受限的情况下高速同步图像数据,避免数据溢出,降低对像素处理时钟域的时钟频率的要求。

30.例如,对于设计规格要求最大能够接收大小为8m并且帧率为60fps的图像数据的芯片,以及能够达到的最高频率为300mhz的芯片后端处理电路,在接收大小为8m并且帧率为60fps的高速图像数据时,图像的尺寸为3840*2160像素,帧率为60fps,像素位宽为12bit,mipi lane的速率为1782mbps(4 lane),图像数据的行周期为7.41

µ

s。若要行缓冲器不溢出,则行缓冲器的读出速率应不小于图像数据输入速率1/(7.41

µ

s/3840)=518mhz。然而,期望的最小读出频率518mhz高于芯片后端处理电路能够实现的最高频率300mhz。根据本公开的实施例,采用由4个深度为1024、宽度为16 bit的异步fifo存储器组成的行缓冲器,将4个fifo存储器分为两个fifo分组轮询读出,行缓冲器的读出时钟设为518mhz/2 =

259mhz即可保证行缓冲器数据不溢出。在接收大小为2m并且帧率为30fps的低速图像数据时,图像的尺寸为1920*1080像素,帧率为30fps,像素位宽为12bit,mipi lane的速率为222.75mbps(4 lane),图像数据的行周期为29.6

µ

s。若要行缓冲器不溢出,则行缓冲器的读出速率应不小于图像数据输入速率,即,1/(29.6

µ

s/1920)=64.8mhz。根据本公开的实施例,采用由4个深度为1024、宽度为16bit的异步fifo存储器组成的行缓冲器,每个读出时钟对一个fifo存储器轮询读出,行缓冲器的读出时钟设为64.8mhz即可保证fifo不溢出。

31.图2示出了根据本公开的实施例的用于图像数据同步的装置200的示意图。与如图1所示的实施例不同,图2所示的装置200包括两个数据缓存模块201、202以及输入数据选择模块203和输出数据选择模块204,其中,两个数据缓存模块201、202在输入数据选择模块203和输出数据选择模块204的控制下执行乒乓(ping

‑

pong)操作。

32.具体而言,输入数据选择模块203的输入为图像数据,其输出连接到两个数据缓存模块201、202以使能数据缓存模块201、202之一的写入操作,从而能够将输入的图像数据轮流写入到数据缓存模块201、202中被输入数据选择模块203使能的一个数据缓存模块。输出数据选择模块204的输出为从两个数据缓存模块201、202之一中读出的图像数据。输入数据选择模块203和输出数据选择模块204相互配合操作,使得在将图像数据写入两个数据缓存模块201、202中的一个数据缓存模块的同时从两个数据缓存模块201、202中的另一个数据缓存模块中读出图像数据。

33.在根据本公开的实施例中,输入数据选择模块203和输出数据选择模块204可以被配置为以一定的切换周期在两个数据缓存模块201、202之间切换以写入和读出图像数据。

34.在根据本公开的实施例中,输出数据选择模块204可以被配置为响应于输入数据选择模块203的切换而进行切换。具体而言,输出数据选择模块204可以被配置为在输入数据选择模块203切换为使能两个数据缓存模块201、202中的一个数据缓存模块的写入操作的情况下,切换为使能两个数据缓存模块201、202中的另一个数据缓存模块的读出操作。

35.应注意的是,除了图2中示出的模块之外,装置200还可以包括用于控制数据缓存模块201、202的读出操作的如前文所述的fifo读出控制模块,以及用于将读出的图像数据打包的打包模块。

36.在本公开的实施例中,数据缓存模块201、202可以共用一个fifo读出控制模块,并在该共用的fifo读出控制模块和输出数据选择模块204两者的控制下读出图像数据。例如,fifo读出控制模块可以如上文所述生成读出使能控制信号,数据缓存模块201、202中被输出数据选择模块204使能的一个数据缓存模块在读出使能控制信号的控制下读出图像数据。在本公开的实施例中,数据缓存模块201、202也可以各自具有相应的fifo读出控制模块,并在该相应的fifo读出控制模块和输入数据选择模块203两者的控制下读出图像数据,其中,这些 fifo读出控制模块可以采取相同的轮询策略。

37.在本公开的实施例中,数据缓存模块201、202可以共用一个打包模块,以将从数据缓存模块201、202读出的数据图像打包在一起。

38.图3示出了根据本公开的实施例的用于图像数据同步的方法的流程图。如图3所示,在s31处,可以以像素为单位在数据缓存模块中包括的n个先入先出fifo存储器中写入图像数据的像素行,其中,n为不小于2的正整数;在s32处,可以判断图像数据输入速率是否低于第一阈值;如果图像数据输入速率低于第一阈值,则在s33处,可以利用fifo读出模块

生成读出使能控制信号以控制从fifo存储器中读出数据,该控制信号使得以每个时钟周期读出1个fifo存储器的方式轮询,然后在s34处,可以以每个读出时钟周期内读出1个fifo存储器的方式从n个fifo存储器中轮询读出图像数据;如果图像数据输入速率不低于第一阈值,则在s35处,可以利用fifo读出模块生成读出使能控制信号以控制从fifo存储器中读出数据,该控制信号使得以每个时钟周期读出m个fifo存储器的方式轮询,然后在s36处,可以以每个读出时钟周期内读出m个fifo存储器的方式从n个fifo存储器中轮询读出图像数据,其中,m为不小于2的正整数,并且m≤n;在s34或s36处轮询读出图像数据之后,在s37处,可以利用数据打包模块打包从数据缓存模块读出的图像数据。

39.图4示出了根据本公开的实施例的图像采集系统400的示意图。如图4所示,图像采集系统400可以包括cmos传感器401、帧解码单元402以及图形数据同步装置403,帧解码单元402可用于将cmos传感器401的输出信号解码为以像素为单位的图像数据,图形数据同步装置403可用于将来自帧解码单元402的图像数据同步到像素处理时钟域,以便于后续处理。

40.本设计采用优化的像素数据同步方法,根据输入数据速率选取合适的fifo读出策略,实现数据从接口时钟域到像素处理时钟域的同步。低数据速率下,多个fifo存储器单个地轮询输出;高数据速率下,fifo存储器按照预设的编组轮询输出,降低像素预处理域的时钟频率,从而降低芯片在后端实现时时序收敛的难度。

41.在这里示出和讨论的所有示例中,任何具体值应被解释为仅仅是示例性的,而不是作为限制。因此,示例性实施例的其它示例可以具有不同的值。

42.如在此所使用的,词语“示例性的”意指“用作示例、实例或说明”,而不是作为将被精确复制的“模型”。在此示例性描述的任意实现方式并不一定要被解释为比其它实现方式优选的或有利的。而且,本公开不受在上述技术领域、背景技术、发明内容或具体实施方式中所给出的任何所表述的或所暗示的理论所限定。

43.还应理解,“包括/包含”一词在本文中使用时,说明存在所指出的特征、整体、步骤、操作、单元和/或组件,但是并不排除存在或增加一个或多个其它特征、整体、步骤、操作、单元和/或组件以及/或者它们的组合。

44.另外,在本公开的描述中,术语“第一”、“第二”、“第三”等仅用于描述目的,而不能理解为指示或暗示相对重要性和顺序。

45.本领域技术人员应当意识到,在上述操作之间的边界仅仅是说明性的。多个操作可以结合成单个操作,单个操作可以分布于附加的操作中,并且操作可以在时间上至少部分重叠地执行。而且,另选的实施例可以包括特定操作的多个实例,并且在其他各种实施例中可以改变操作顺序。但是,其它的修改、变化和替换同样是可能的。因此,本说明书和附图应当被看作是说明性的,而非限制性的。

46.虽然已经通过示例对本公开的一些特定实施例进行了详细说明,但是本领域的技术人员应该理解,以上示例仅是为了进行说明,而不是为了限制本公开的范围。在此公开的各实施例可以任意组合,而不脱离本公开的精神和范围。本领域的技术人员还应理解,可以对实施例进行多种修改而不脱离本公开的范围和精神。本公开的范围由所附权利要求来限定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。