1.本发明实施例涉及卫星技术领域,尤其涉及一种智能处理模组的软件上注系统和方法。

背景技术:

2.经过多年建设发展,我国遥感卫星进入空前发展时期,海量遥感探测数据为国民经济建设提供了日益丰富的数据资源。但是目前的空间遥感系统,受限于空间环境、载荷、体积、功耗等因素,不具备像地面设备一样的处理能力,仅具备信息采集的能力,由此导致三个比较突出的问题:

3.首先,传统卫星往往将计算任务下发地面处理,数据处理自动化程度低,信息提取的时效性差。然而,在空间智能化发展背景下,其处理任务载荷量大、种类繁多且具有时间敏感性,传统的模式无法满足未来瞬息万变、察打一体的联合作战需求。而基于提升通用处理器频率和核数来提高计算能力的传统方法往往会导致系统功耗上升,这对于功耗敏感的遥感信息计算系统来说已不再适用。因此,采用高能效的智能处理器势在必行。

4.其次,受限于星上数据处理能力,将某些特殊任务(如:人工智能训练任务)直接“搬运”到星上的方式尚不具备可行性,目前较符合当前系统能力的方式是“星地协同”。所谓星地协同,就是将历史数据的深度挖掘、基于遥感大数据的深度学习、神经网络模型训练等数据量大、运算量大、要求较高的处理任务部署在地面系统,将处理的结果(目标的特征参数、训练后的模型)上传至星上系统,卫星在轨对影像进行实时智能处理,生成情报信息并下传至用户,缩短信息传输链条,提高天基系统的智能化水平和情报支援的时效性。

5.此外,由于空间环境恶劣,智能处理器上的存储单元容易受到单粒子翻转的影响而出现软故障,导致智能处理器上存储的固件和应用程序等被破坏,从而出现上电故障、星上任务处理故障等问题。

6.传统的星上处理器可靠性设计通过对处理器外部加装屏蔽结构、选用航空级器件来避免处理器发生软故障,但是这些措施并不是完全没有风险的,仍有一些处理器上天之后不能正常工作的情况。而一旦处理器不能工作,地面控制中心就没有办法对处理器的软件进行修复,导致处理器无法进行任务。

技术实现要素:

7.本发明提供一种智能处理模组的软件上注系统和方法,采用地面上注的方法,从地面控制中心对智能处理模组各个部分的软件进行上注更新,能够处理智能处理模组上天后可能出现的所有软故障。

8.第一方面,本发明实施例提供了一种智能处理模组的软件上注系统,包括:

9.主控模块、第一存储装置以及智能处理模组;

10.所述主控模块与所述存储装置通信相连,用于接收地面控制中心上传的数据并存储至所述第一存储装置中;

11.所述主控模块还与所述智能处理模组通信相连,用于根据所述第一存储装置中存储的数据对所述智能处理模组的程序进行上注更新。

12.可选的,所述智能处理模组的软件程序包括单片机程序、第二存储装置中的固件程序以及第三存储装置中的系统镜像。

13.可选的,所述主控模块为fpga主控芯片。

14.可选的,所述第一存储装置的数量为三个。

15.第二方面,一种智能处理模组的系统上注方法,由本实施例中任一项所述的系统执行,包括:

16.s1、接收地面控制中心上传的数据并存储至第一存储装置中;

17.s2、根据所述第一存储装置中存储的数据对所述智能处理模组的程序进行上注更新。

18.可选的,各所述第一存储装置中存储的数据均相同,且所述第一存储装置包括三个部分,第一部分用于存储单片机程序,第二部分用于存储固件程序,第三部分用于存储系统镜像。

19.可选的,在步骤s2之前还包括:

20.对各所述第一存储装置中每一位的数据进行比较,确定数据完全相同的至少两个所述第一存储装置。

21.可选的,步骤s2包括:

22.s21、主控模块通过电源控制io控制所述智能处理模型进行上电;

23.s22、主控模块从所述第一存储装置的第一部分读取单片机程序,通过单片机串口与智能处理模组上的单片机进行通信,对单片机程序进行上注更新;

24.s23、主控模块从所述第一存储装置的第二部分读取固件程序,通过串口通信对智能处理模组上的第二存储装置的固件程序进行上注更新;

25.s24、主控模块和第一存储装置的第三部分模拟sd卡,根据所述第一存储装置第三部分存储的系统镜像对第三存储装置中的系统镜像进行上注更新。

26.本发明通过采用地面上注的方法,从地面控制中心对智能处理模组各个部分的软件进行上注更新,能够处理智能处理模组上天后可能出现的所有软故障。

附图说明

27.图1为本发明实施例提供的一种智能处理模组的软件上注系统的结构示意图;

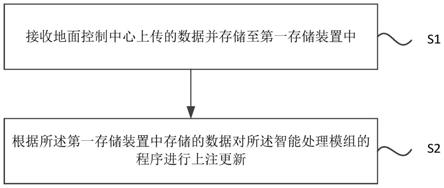

28.图2为本发明实施例提供的一种智能处理模组的系统上注方法的流程图;

29.图3为本发明实施例提供的一种单片机程序上注的流程图;

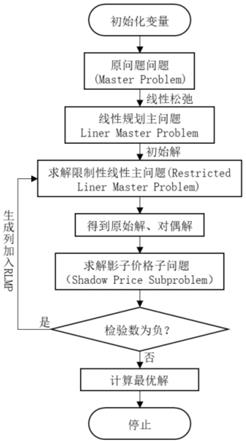

30.图4为本发明实施例提供的一种nor flash中的固件程序上注的流程图;

31.图5为本发明实施例提供的一种emmc系统镜像上注的流程图。

具体实施方式

32.下面结合附图和实施例对本发明作进一步的详细说明。可以理解的是,此处所描述的具体实施例仅仅用于解释本发明,而非对本发明的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与本发明相关的部分而非全部结构。

33.实施例

34.由于星上资源有限,所以数据量大、运算量大的深度学习训练任务需要在地面处理,训练完成的网络模型也需要通过在地面上注更新到星上智能处理模组上,实现网络模型的更新。卫星在轨通过智能处理模组进行实时的智能处理,并将处理结果下传至地面,通过上注和下传实现星地协同。

35.首先,本实施例提供一种智能处理模组的软件上注系统,包括主控模块、第一存储装置以及智能处理模组。可选的,本实施例中的第一存储装置为三块nor flash存储器,第一存储装置的数量为三个。

36.所述主控模块与所述存储装置通信相连,用于接收地面控制中心上传的数据并存储至所述第一存储装置中;所述主控模块还与所述智能处理模组通信相连,用于根据所述第一存储装置中存储的数据对所述智能处理模组的程序进行上注更新。

37.进一步参见图1,本实施例提供的智能处理模组的软件上注系统包括三块nor flash存储器,智能处理模组的软件程序包括三部分,分别为单片机程序、第二存储装置中的固件程序以及第三存储装置中的系统镜像。第二存储装置也选用nor flash作为存储器;上述第三存储装置为嵌入式多媒体控制器(embedded multi media card,emmc)。其中,单片机程序主要用于控制智能处理模组的上电工作。上电完成后,nor flash中的固件程序对智能处理模组的相关硬件设备进行初始化并引导emmc中的系统镜像。进一步的,也存储了智能处理模组执行相关任务所需要的应用程序。

38.因为现场可编程门阵列(field programmable gatearrays,fpga)具备丰富的逻辑资源,可进行片内冗余容错设计并广泛应用于航天领域,所以本实施例中的主控模块采用fpga主控芯片,将其作为地面控制中心和智能处理模组通信的桥梁。

39.具体的,fpga通过同步串行接口通信技术(byteperipheralinterface,bpi)总线与三块nor flash相连,用于存储地面控制中心上注的文件;通过通用型之输入输出端口(gpio,general

‑

purpose input/output)控制智能处理模组的电源、启动模式、单片机模式等;此外,还与智能处理模组通过多种接口互联,如串口、sdio、rapidio等。

40.继续参见图2,本发明实施例还提供一种智能处理模组的系统上注方法,包括以下步骤:

41.s1、接收地面控制中心上传的数据并存储至第一存储装置中。

42.作为优选,本实施例中的第一存储装置为3个,且各所述第一存储装置中存储的数据均相同,且所述第一存储装置包括三个部分,第一部分用于存储单片机程序,第二部分用于存储固件程序,第三部分用于存储系统镜像。

43.地面控制中心将需要上注的软件封装成数据包上注到卫星上,fpga接收到数据包后解析并将不同的数据存放在三块nor flash指定的位置,三块nor flash存储的数据完全相同。在对智能处理模组进行软件上注之前,fpga进行“三取二逻辑”,即通过对比三块nor flash中每一bit的数据是否相同,取至少两块相同的数据进行上注更新。“三取二逻辑”一方面可以保证地面控制中心上传数据的正确性,另一方面可以防止fpga nor flash中部分数据被打翻而导致上注程序出错。

44.s2、根据所述第一存储装置中存储的数据对所述智能处理模组的程序进行上注更新。

45.本实施例中,步骤s2包括:

46.s21、主控模块通过电源控制io控制所述智能处理模型进行上电。

47.s22、主控模块从所述第一存储装置的第一部分读取单片机程序,通过单片机串口与智能处理模组上的单片机进行通信,对单片机程序进行上注更新。

48.示例性的,单片机的上注流程参见图3。fpga上注智能处理模组单片机程序后控制单片机boot io切换至启动模式,单片机程序完成智能处理模组上电工作。

49.s23、主控模块从所述第一存储装置的第二部分读取固件程序,通过串口通信对智能处理模组上的第二存储装置的固件程序进行上注更新。

50.本实施例中,在智能处理模组上电工作后,智能处理模组需要运行nor flash中的固件程序,fpga通过flash串口对智能处理模组的nor flash进行上注更新,具体流程如图4所示。

51.s24、主控模块和第一存储装置的第三部分模拟sd卡,根据所述第一存储装置第三部分存储的系统镜像对第三存储装置中的系统镜像进行上注更新。

52.本实施例中,在更新完第二存储器的固件程序后,主控模块切换智能模组单元启动模式并重新上电。然后主控模块和第一存储装置第三部分模拟sd卡,并在在主控模块的控制下对第三存储装置中的系统镜像进行上注更新。具体的,智能处理模组nor flash完成上注更新后会自动加载nor flash中的固件程序,程序最终会进入u

‑

boot。u

‑

boot引导emmc中的linux镜像,emmc中程序的更新需要在sd卡中完成,而星载处理器保留sd卡槽和sd卡是不被允许的,会存在极大的风险。所以本实施中采用fpga nor flash来模拟sd卡。模拟sd卡能够在智能处理模组u

‑

boot下被识别,从而进行emmc程序的更新,更新完成后智能处理模组重启进入linux系统,linux下也可以识别到模拟sd卡。

53.模拟sd卡的系统框图5所示。图5的左侧sd host是sd卡主机,往往是读卡器、嵌入式微处理器等。sd host往往具有卡槽,通过标准的6线sd总线与sd卡相连。右侧的sd fakex和nor flash共同组成一个虚拟的sd卡。其中,nor flash仅仅负责提供sd卡的数据;sd fakex是一个verilog模块,负责对sd总线的命令进行解析和响应,并在sd

‑

host请求数据时,从nor flash中读取数据并传给sd host,即fpga通过sdio将数据传给智能处理模组。完成emmc程序上注更新后,智能处理模组重启后进入linux系统。

54.fpga通过上述操作实现智能处理模组所有程序的上注更新,智能处理模组开始正常工作。地面控制中心可将任务指令发给fpga,fpga通过指令串口将任务指令转发给智能处理模组进行处理。图像或视频数据经过星载摄像机或者其他星载设备传输给fpga,fpga通过rapid io高速接口传输给智能处理模组,智能处理模组根据任务指令对图像或视频输入进行处理,并将处理后的结果传给fpga,fpga下传至地面控制中心,从而实现“星地协同”。

55.注意,上述仅为本发明的较佳实施例及所运用技术原理。本领域技术人员会理解,本发明不限于这里所述的特定实施例,对本领域技术人员来说能够进行各种明显的变化、重新调整和替代而不会脱离本发明的保护范围。因此,虽然通过以上实施例对本发明进行了较为详细的说明,但是本发明不仅仅限于以上实施例,在不脱离本发明构思的情况下,还可以包括更多其他等效实施例,而本发明的范围由所附的权利要求范围决定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。